# UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY, LTD. and GLOBALFOUNDRIES U.S. INC.,

Petitioners,

v.

GODO KAISHA IP BRIDGE 1,

Patent Owner.

Case IPR2016-01376<sup>1</sup> Patent No. 6,197,696

PATENT OWNER GODO KAISHA IP BRIDGE 1'S NOTICE OF APPEAL

<sup>&</sup>lt;sup>1</sup> GlobalFoundries U.S. Inc.'s motion for joinder in Case IPR2017-00921 was granted.

Director of the United States Patent and Trademark Office c/o Office of the General Counsel United States Patent and Trademark Office P.O. Box. 1450 Alexandria, VA 22313-1450

Pursuant to 35 U.S.C. §§ 141, 142, and 319, and 37 C.F.R. §§ 90.2-90.3, notice is hereby given that Patent Owner Godo Kaisha IP Bridge 1 appeals to the United States Court of Appeals for the Federal Circuit from the Final Written Decision of the Patent Trial and Appeal Board ("Board") entered on January 17, 2018 (Paper 46) in IPR2016-01376, and from all underlying orders, decisions, rulings, and opinions regarding this *inter partes* review of U.S. Patent No. 6,197,696 B1 ("696 patent"). A copy of the Final Written Decision (Paper 46) is attached.

In accordance with 37 C.F.R. § 90.2(a)(3)(ii), Patent Owner further indicates that the issues on appeal include, but are not limited to, the following: (1) the Board's determination that claims 13 and 15 of the '696 patent have been shown to be unpatentable; (2) the Board's determination that Petitioner has demonstrated by a preponderance of the evidence that claims 13 and 15 of the '696 patent are unpatentable under 35 U.S.C. § 103(a) as obvious over U.S. Patent No. 6,140,226 to Grill et al. ("Grill") and U.S. Patent No. 5,592,024 to Aoyama et al. ("Aoyama") (3) the Board's consideration of the expert testimony, prior art, and other evidence in the record; (4) the Board's factual findings, conclusions of law or other determinations supporting or related to those issues; as well as (5) all other issues decided adversely to Patent Owner in any orders, decisions, rulings, and opinions.

Simultaneous with this submission, a copy of this Notice of Appeal is being filed with the PTAB through the E2E System. In addition, copies of the Notice of Appeal, along with the required docketing fee, are being filed with the Clerk's office for the United States Court of Appeals for the Federal Circuit.

Dated: March 20, 2018

Respectfully submitted,

By: /James L. Davis, Jr./

James L. Davis, Jr. Reg. No. 57,325 Andrew N. Thomases (Back-up counsel) Reg. No. 40,841 ROPES & GRAY LLP 1900 University Avenue, 6th Floor East Palo Alto, CA 94303-2284 P: 650-617-4000 / F: 617-235-9492 james.l.davis@ropesgray.com andrew.thomases@ropesgray.com

J. Steven Baughman (Back-up counsel) Reg. No. 47,414 Paul, Weiss, Rifkind, Wharton & Garrison LLP 2001 K Street, NW Washington, DC 20006-1047 P: 202-223-7340/F: 202-403-3740 sbaughman@paulweiss.com

Counsel for Patent Owner Godo Kaisha IP Bridge 1

# **CERTIFICATE OF FILING**

It is certified that, in addition to being filed electronically through the Patent

Trial and Appeal Board's E2E System, a copy of PATENT OWNER GODO

KAISHA IP BRIDGE 1'S NOTICE OF APPEAL has been filed by hand on March

20, 2018, with the Director of the United States Patent and Trademark Office, at

the following address:

Director of the United States Patent and Trademark Office c/o Office of the General Counsel 10B20, Madison Building East, 600 Dulany Street Alexandria, VA 22314-5793

Dated: March 20, 2018

Respectfully submitted,

/James L. Davis, Jr./ James L. Davis, Jr.

Counsel for Patent Owner Godo Kaisha IP Bridge 1

# **CERTIFICATE OF FILING**

It is certified that, a copy of PATENT OWNER GODO KAISHA IP

BRIDGE 1'S NOTICE OF APPEAL was filed electronically through the United

States Court of Appeals for the Federal Circuit's CM/ECF system March 20, 2018

and one paper copy delivered by hand on March 20, 2018, with the Clerk of the

Court of the Federal Circuit, at the following address:

Clerk of the Court 717 Madison Place, N.W. Room 401 Washington D.C. 20439

Dated: March 20, 2018

Respectfully submitted,

<u>/James L. Davis, Jr./</u> James L. Davis, Jr

Counsel for Patent Owner Godo Kaisha IP Bridge 1

# **CERTIFICATE OF SERVICE**

The undersigned certifies that a true and copy of the foregoing PATENT OWNER GODO KAISHA IP BRIDGE 1'S NOTICE OF APPEAL was served on March 20, 2018 in its entirety by causing the aforementioned document to be electronically mailed, pursuant to the parties' agreement, to the following attorneys of record:

Petitioner TSMC's Counsel of Record:

Darren M. Jiron Reg. No. 45,777 darren.jiron@finnegan.com E. Robert Yoches Reg. No. 30,120 bob.yoches@finnegan.com J. Preston Long Reg. No. 65,125 JP.Long@finnegan.com Joshua L. Goldberg Reg. No. 59,369 Joshua.Goldberg@finnegan.com FINNEGAN, HENDERSON, FARABOW, GARRETT & DUNNER, LLP **ATTN: Patent Administrator** Two Freedom Square, 11955 Freedom Drive Reston, VA 20190-5675

Petitioner Global Foundries' Counsel of Record:

Christopher Carroll WHITE & CASE, LLP 75 State Street Boston, MA 02109-1814 christopher.carroll@whitecase.com

Shamita Etienne-Cummings WHITE & CASE, LLP 701 Thirteenth Street NW Washington, DC 20005-3807 setienne@whitecase.com

Dated: March 20, 2018

Respectfully submitted,

<u>/James L. Davis, Jr./</u> James L. Davis, Jr Counsel for Patent Owner Godo Kaisha IP Bridge 1 Trials@uspto.gov 571-272-7822 Paper No. 46 Entered: January 17, 2018

#### UNITED STATES PATENT AND TRADEMARK OFFICE

#### BEFORE THE PATENT TRIAL AND APPEAL BOARD

TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY, LTD. and GLOBALFOUNDRIES U.S. INC., Petitioner,

v.

GODO KAISHA IP BRIDGE 1, Patent Owner.

> Case IPR2016-01376<sup>1</sup> Patent 6,197,696 B1

Before JUSTIN T. ARBES, MICHAEL J. FITZPATRICK, and JENNIFER MEYER CHAGNON, *Administrative Patent Judges*.

CHAGNON, Administrative Patent Judge.

FINAL WRITTEN DECISION Inter Partes Review 35 U.S.C. § 318(a) and 37 C.F.R. § 42.73

<sup>&</sup>lt;sup>1</sup> GlobalFoundries U.S. Inc.'s motion for joinder in Case IPR2017-00921 was granted.

# I. INTRODUCTION

We have jurisdiction to hear this *inter partes* review under 35 U.S.C. § 6. This Final Written Decision is issued pursuant to 35 U.S.C. § 318(a) and 37 C.F.R. § 42.73. For the reasons discussed herein, we determine that Petitioner has shown, by a preponderance of the evidence, that claims 13 and 15 ("the challenged claims") of U.S. Patent No. 6,197,696 B1 (Ex. 1001, "the '696 patent") are unpatentable.

# A. Procedural History

Taiwan Semiconductor Manufacturing Company, Ltd. ("Petitioner")<sup>2</sup> filed a Petition for *inter partes* review of claims 13 and 15 of the '696 patent. Paper 2 ("Pet."). Petitioner provided a Declaration of Bruce W. Smith, Ph.D., (Ex. 1002) to support its positions. Godo Kaisha IP Bridge 1 ("Patent Owner") filed a Preliminary Response to the Petition. Paper 6 ("Prelim. Resp."). Pursuant to our authorization (Paper 7), Petitioner filed a Reply to the Preliminary Response (Paper 9) and Patent Owner filed a Sur-Reply (Paper 10).

Pursuant to 35 U.S.C. § 314(a), on January 18, 2017, we instituted *inter partes* review to determine whether claims 13 and 15 are unpatentable

<sup>&</sup>lt;sup>2</sup> On August 8, 2017, we granted a motion for joinder filed by GlobalFoundries U.S. Inc. ("GlobalFoundries") in IPR2017-00921, and authorized GlobalFoundries to participate in this proceeding only on a limited basis. *See* Paper 29; Ex. 3003 (IPR2017-00921, Paper 10). Although the papers referenced herein were filed by Taiwan Semiconductor Manufacturing Company, Ltd., we refer to both entities as "Petitioner" throughout this Decision.

under 35 U.S.C. § 103(a) as obvious in view of Grill<sup>3</sup> and Aoyama.<sup>4</sup> *See* Paper 11 ("Inst. Dec."). Subsequent to institution, Patent Owner filed a Patent Owner Response (Paper 19, "PO Resp."), along with a Declaration of Alexander Glew, Ph.D., (Ex. 2009) to support its positions. Petitioner filed a Reply (Paper 26, "Reply") to the Patent Owner Response, along with a second Declaration of Dr. Smith (Ex. 1049) in support thereof.

Petitioner filed a Motion to Exclude (Paper 30, "Pet. Mot.") certain evidence submitted by Patent Owner. Patent Owner filed an Opposition (Paper 37), and Petitioner filed a Reply (Paper 41). Patent Owner filed Observations on the cross-examination of Dr. Smith (Paper 34), and Petitioner filed a Response thereto (Paper 35). Pursuant to our authorization, Patent Owner also filed a listing of portions of Petitioner's Reply that allegedly exceed the proper scope of a reply (Paper 36).

A combined oral hearing for IPR2016-01376, IPR2016-01377, IPR2016-01378, and IPR2016-01379 was held on September 12, 2017. A transcript of the hearing is included in the record. Paper 45 ("Tr.").

# B. Related Proceedings

The parties indicate that the '696 patent has been asserted in *Godo Kaisha IP Bridge 1 v. Broadcom Ltd.*, No. 2-16-cv-00134 (E.D. Tex. 2016). Paper 4, 2; Pet. 76. Three additional *inter partes* reviews challenge claims of the '696 patent. *See* Case IPR2016-01377; Case IPR2016-01378; Case IPR2016-01379; Pet. 74–75; Paper 4, 2–3.

<sup>&</sup>lt;sup>3</sup> U.S. Patent No. 6,140,226, filed July 30, 1998, issued Oct. 31, 2000 (Ex. 1005).

<sup>&</sup>lt;sup>4</sup> U.S. Patent No. 5,592,024, issued Jan. 7, 1997 (Ex. 1018).

#### C. The '696 Patent

The '696 patent relates to a "method for forming an interconnection structure in a semiconductor integrated circuit." Ex. 1001, 1:5–7. According to the '696 patent, "[a]n object of the present invention is providing a method for forming an interconnection structure in which an insulating film with a low dielectric constant can be formed by an ordinary resist application process." *Id.* at 3:2–5.

The '696 patent describes various embodiments of methods of forming an interconnection structure. *Id.* at [57]. The manufacturing process for a modified example of the sixth embodiment is depicted in Figures 33(a)–(c), 34(a)–(c), and 35(a)–(c). *Id.* at 29:62–32:9.

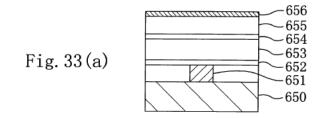

Figure 33(a) of the '696 patent is reproduced below.

Figure 33(a), reproduced above, is a cross-sectional view of a partially formed interconnection structure during a process step for forming the same. Ex. 1001, 9:60–63. As seen in Figure 33(a), silicon nitride film 652 is formed over first metal interconnects 651 (only one shown in Figure 33(a)), which are formed on semiconductor substrate 650. *Id.* at 30:1–3. First organic film 653, silicon dioxide film 654, second organic film 655, and titanium nitride film 656 are deposited sequentially. *Id.* at 30:6–16.

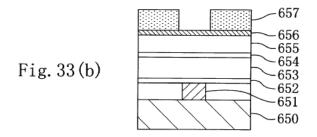

Figure 33(b) of the '696 patent, illustrating a subsequent step in the method of this embodiment, is reproduced below.

Figure 33(b), reproduced above, is a cross-sectional view of a partially formed interconnection structure during a process step for forming the same. *Id.* at 9:60–63. In this step, first resist pattern 657 is formed on titanium nitride film 656. *Id.* at 30:36–37. First resist pattern 657 includes openings for forming wiring grooves of the interconnection structure. *Id.*

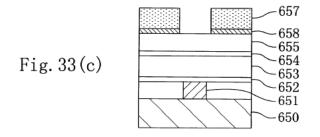

Figure 33(c) of the '696 patent, illustrating a subsequent step in the method of this embodiment, is reproduced below.

Figure 33(c), reproduced above, is a cross-sectional view of a partially formed interconnection structure during a process step for forming the same. Ex. 1001, 9:60–63. In this step, titanium nitride film 656 is dry-etched using first resist pattern 657 as a mask, thereby forming mask pattern 658. *Id.* at 30:38–40.

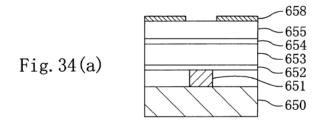

Figure 34(a) of the '696 patent, illustrating a subsequent step in the method of this embodiment, is reproduced below.

Figure 34(a), reproduced above, is a cross-sectional view of a partially formed interconnection structure during a process step for forming the same. *Id.* at 9:64–67. In this step, first resist pattern 657 is removed. *Id.* at 30:44–45.

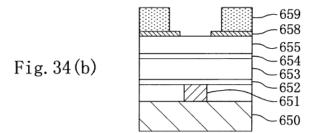

Figure 34(b) of the '696 patent, illustrating a subsequent step in the method of this embodiment, is reproduced below.

Figure 34(b), reproduced above, is a cross-sectional view of a partially formed interconnection structure during a process step for forming the same. Ex. 1001, 9:64–67. In this step, second resist pattern 659 is formed on mask pattern 658. *Id.* at 30:49–51. Second resist pattern 659 includes openings for forming contact holes of the interconnection structure. *Id.* In this embodiment, the openings in second resist pattern 659 are larger than the designed size of the contact holes "in respective directions vertical and parallel to the wiring grooves." *Id.* at 30:51–56.

6

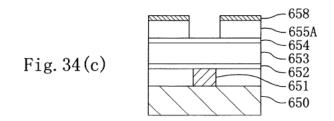

Figure 34(c) of the '696 patent, illustrating a subsequent step in the method of this embodiment, is reproduced below.

Figure 34(c), reproduced above, is a cross-sectional view of a partially formed interconnection structure during a process step for forming the same. *Id.* at 9:64–67. In this step, second organic film 655 has been dry-etched using both second resist pattern 659 and mask pattern 658 as a mask, thereby forming patterned second organic film 655A. *Id.* at 30:58–62. In this embodiment, second resist pattern 659 also is removed during this etching. *See id.* at 30:66–31:1.

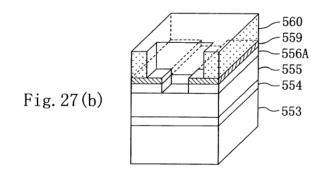

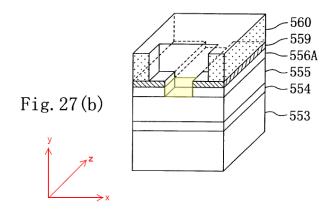

A three-dimensional depiction of etching using both second resist pattern 659 and mask pattern 658 as a mask is provided in the '696 patent with respect to the modified fifth embodiment in Figure 27(b). Figure 27(b) of the '696 patent is reproduced below.

Figure 27(b), reproduced above, is a perspective view of a partially formed interconnection structure during a process step for forming the same, according to the modified fifth embodiment. Ex. 1001, 9:40–42. Second

resist pattern 560 of Figure 27(b) is similar to second resist pattern 659 of Figure 34(b); mask pattern 559 of Figure 27(b) is similar to mask pattern 658 of Figure 34(b); and patterned second silicon dioxide film 556A of Figure 27(b) is similar to patterned second organic film 655A of Figure 34(c). Patterned second organic film 655A (element 556A in Figure 27(b)) is etched away only where the openings in the second resist pattern 659 (element 560 in Figure 27(b)) and mask pattern 658 (element 559 in Figure 27(b)) overlap. For illustration, we provide an annotated version of Figure 27(b) of the '696 patent below.

Figure 27(b) is a perspective view of a partially formed interconnection structure (Ex. 1001, 9:40–42), with the portion of the underlying insulating film that was removed during etching highlighted in yellow and an x-y-z axis added for reference. From the perspective of Figure 27(b), mask pattern 559 defines the areas for etching in the x-axis direction, and second resist pattern 560 defines the areas for etching in the z-axis direction.

According to the '696 patent, using larger openings in second resist pattern 659, as shown in Figure 34(b), allows "openings of the patterned second organic film 655A for forming contact holes [such that they are] self-aligned with the openings of the mask pattern 658 for forming wiring grooves," "even if the openings of the second resist pattern 659 for forming

8

contact holes have misaligned with the openings of the mask pattern 658 for forming wiring grooves." *Id.* at 31:54–60. This self-alignment occurs "because the openings of the patterned second organic film 655A for forming contact holes are formed in respective regions where the openings of the second resist pattern 659 for forming contact holes overlap with corresponding openings of the mask pattern 658 for forming wiring grooves." *Id.* at 31:60–67.

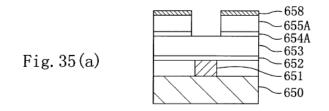

Figure 35(a) of the '696 patent, illustrating a subsequent step in the method of the modified sixth embodiment, is reproduced below.

Figure 35(a), reproduced above, is a cross-sectional view of a partially formed interconnection structure during a process step for forming the same. *Id.* at 10:1–4. In this step, silicon dioxide film 654 is dry-etched using patterned second organic film 655A as a mask, thereby forming patterned second silicon dioxide film 654A. *Id.* at 31:7–10; *see also id.* at Fig. 28(a) (showing a similar step of the modified fifth embodiment).

Figure 35(b) of the '696 patent, illustrating a subsequent step in the method of this embodiment, is reproduced below.

Figure 35(b), reproduced above, is a cross-sectional view of a partially formed interconnection structure during a process step for forming the same. Ex. 1001, 10:1–4. In this step, patterned second organic film 655A (Fig. 35(a)) is dry-etched using mask pattern 658 as a mask, and first organic film 653 (Fig. 35(a)) is dry-etched using patterned silicon dioxide film 654A as a mask. *Id.* at 31:12–15; *see also id.* at Fig. 29(a) (showing a similar step of the modified fifth embodiment). This etching forms patterned second organic film 655B having wiring grooves 660 and patterned first organic film 653A having contact holes 661. *Id.* at 31:15–17.

Figure 35(c) of the '696 patent, illustrating a subsequent step in the method of the modified sixth embodiment, is reproduced below.

Figure 35(c), reproduced above, is a cross-sectional view of an interconnection structure formed by the method of the modified sixth embodiment. *Id.* at 10:1–4. In this step, patterned silicon dioxide film 654A is dry-etched using mask pattern 658 as a mask, and silicon nitride film 652 is dry-etched using patterned first organic film 653A as a mask. *Id.* at 31:19–22. This etching step forms patterned silicon dioxide film 654B having wiring grooves and patterned silicon nitride film 652A having contact holes, and also exposes first metal interconnects 651 within contact holes 661. *Id.* at 31:22–26. Then, a metal film is deposited over the surface of the substrate to fill in contact holes 661 and wiring grooves 660, thus forming second metal interconnects 662 and contacts 663. *Id.* at 31:30–44.

D. Illustrative Claim

Of the challenged claims, claim 13 is independent, and claim 15 depends therefrom. Claim 13 of the '696 patent, reproduced below, is illustrative of the challenged claims:

13. A method for forming an interconnection structure, comprising the steps of:

a) forming a first insulating film over lower-level metal interconnects;

b) forming a second insulating film, having a different composition than that of the first insulating film, over the first insulating film;

c) forming a third insulating film, having a different composition than that of the second insulating film, over the second insulating film;

d) forming a thin film over the third insulating film;

e) forming a first resist pattern on the thin film, the first resist pattern having openings for forming wiring grooves;

f) etching the thin film using the first resist pattern as a mask, thereby forming a mask pattern out of the thin film to have the openings for forming wiring grooves;

g) removing the first resist pattern and then forming a second resist pattern on the third insulating film and the mask pattern, the second resist pattern having openings for forming contact holes;

h) dry-etching the third insulating film using the second resist pattern and the mask pattern as a mask, thereby patterning the third insulating film to have the openings for forming contact holes;

i) dry-etching the second insulating film using the patterned third insulating film as a mask, thereby patterning the second insulating film to have the openings for forming contact holes;

j) dry-etching the patterned third insulating film and the first insulating film using the mask pattern and the patterned second insulating film as respective masks, thereby forming wiring grooves and contact holes in the patterned third insulating film and the first insulating film, respectively; and

k) filling in the wiring grooves and the contact holes with a metal film, thereby forming upper-level metal interconnects and contacts connecting the lower- and upper-level metal interconnects together.

Ex. 1001, 34:58–36:10.

#### II. ANALYSIS

#### A. Principles of Law

To prevail in its challenges to the patentability of the claims, Petitioner must demonstrate by a preponderance of the evidence that the challenged claims are unpatentable. 35 U.S.C. § 316(e); 37 C.F.R. § 42.1(d). "In an [*inter partes* review], the petitioner has the burden from the onset to show with particularity why the patent it challenges is unpatentable." *Harmonic Inc. v. Avid Tech., Inc.*, 815 F.3d 1356, 1363 (Fed. Cir. 2016) (citing 35 U.S.C. § 312(a)(3) (requiring *inter partes* review petitions to identify "with particularity . . . the evidence that supports the grounds for the challenge to each claim")). This burden of persuasion never shifts to Patent Owner. *See Dynamic Drinkware, LLC v. Nat'l Graphics, Inc.*, 800 F.3d 1375, 1378–79 (Fed. Cir. 2015) (citing *Tech. Licensing Corp. v. Videotek, Inc.*, 545 F.3d 1316, 1326–27 (Fed. Cir. 2008)) (discussing the burdens of persuasion and production in *inter partes* review).

A claim is unpatentable for obviousness if, to one of ordinary skill in the pertinent art, "the differences between the subject matter sought to be patented and the prior art are such that the subject matter as a whole would have been obvious at the time the invention was made." *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 406 (2007) (quoting 35 U.S.C. § 103(a)). The question of obviousness is resolved on the basis of underlying factual determinations, including "the scope and content of the prior art are to be determined; differences between the prior art and the claims at issue are to be ascertained; and the level of ordinary skill in the pertinent art resolved."<sup>5</sup> *Graham v. John Deere Co.*, 383 U.S. 1, 17–18 (1966).

A patent claim "is not proved obvious merely by demonstrating that each of its elements was, independently, known in the prior art." *KSR*, 550 U.S. at 418. An obviousness determination requires finding "both 'that a skilled artisan would have been motivated to combine the teachings of the prior art references to achieve the claimed invention, and that the skilled artisan would have had a reasonable expectation of success in doing so."" *Intelligent Bio-Sys., Inc. v. Illumina Cambridge Ltd.*, 821 F.3d 1359, 1367– 68 (Fed. Cir. 2016) (citation omitted); *see KSR*, 550 U.S. at 418 (for an obviousness analysis, "it can be important to identify a reason that would have prompted a person of ordinary skill in the relevant field to combine the elements in the way the claimed new invention does"). A motivation to combine the teachings of two references can be "found explicitly or implicitly in market forces; design incentives; the 'interrelated teachings of multiple patents'; 'any need or problem known in the field of endeavor at the

<sup>&</sup>lt;sup>5</sup> Additionally, secondary considerations, such as "commercial success, long felt but unsolved needs, failure of others, etc., might be utilized to give light to the circumstances surrounding the origin of the subject matter sought to be patented. As indicia of obviousness or nonobviousness, these inquiries may have relevancy." *Graham*, 383 U.S. at 17–18. The record, however, lacks any such evidence.

time of invention and addressed by the patent'; and the background knowledge, creativity, and common sense of the person of ordinary skill." *Plantronics, Inc. v. Aliph, Inc.*, 724 F.3d 1343, 1354 (Fed. Cir. 2013) (citation omitted). Further, an assertion of obviousness "cannot be sustained by mere conclusory statements; instead, there must be some articulated reasoning with some rational underpinning to support the legal conclusion of obviousness." *KSR*, 550 U.S. at 418 (quoting *In re Kahn*, 441 F.3d 977, 988 (Fed. Cir. 2006)); *In re Nuvasive, Inc.*, 842 F.3d 1376, 1383 (Fed. Cir. 2016) (a finding of a motivation to combine "must be supported by a 'reasoned explanation" (citation omitted)).

# B. Level of Ordinary Skill in the Art

Petitioner asserts that a person of ordinary skill in the art would have possessed "(1) the equivalent of a Master of Science degree from an accredited institution in electrical engineering, materials science, physics, or the equivalent; (2) a working knowledge of semiconductor processing technologies for integrated circuits; and (3) at least two years of experience in related semiconductor processing analysis, design, and development. Additional graduate education could substitute for professional experience, and significant work experience could substitute for formal education." Pet. 27–28 (citing Ex. 1002 ¶ 141) (internal citations omitted). Dr. Glew testifies that "a person of ordinary skill in the art would have had a Bachelor's of Science degree in materials science engineering, electrical engineering, mechanical engineering, chemical engineering, or an equivalent degree, and at least two years of experience in semiconductor processing or equipment." Ex. 2009 ¶ 22.

We note the parties' proposals differ in the specific degree required (i.e., Master of Science vs. Bachelor's of Science); however, neither party argues this distinction makes a difference in analyzing the asserted ground or other issues in this proceeding. For clarity of the record, we adopt Petitioner's proposal regarding the level of ordinary skill in the art, as it is more specifically directed to the technology described in the '696 patent. In addition, given the disclosures in the '696 patent and cited prior art, we agree with Petitioner that a Master of Science degree (or equivalent) in the relevant area better reflects the level of education and training that an ordinarily skilled artisan would have possessed at the time than a Bachelor's degree, as Patent Owner contends. Our findings and conclusions, however, would be the same under either party's proposed level of ordinary skill in the art. The level of ordinary skill in the art in this case further is reflected by the prior art of record. See Okajima v. Bourdeau, 261 F.3d 1350, 1355 (Fed. Cir. 2001); In re GPAC Inc., 57 F.3d 1573, 1579 (Fed. Cir. 1995); In re Oelrich, 579 F.2d 86, 91 (CCPA 1978).

#### C. Claim Construction

In an *inter partes* review, claim terms in an unexpired patent are given their broadest reasonable construction in light of the specification of the patent in which they appear. *See* 37 C.F.R. § 42.100(b); *Cuozzo Speed Techs., LLC v. Lee*, 136 S. Ct. 2131, 2144–46 (2016). Pursuant to that standard, the claim language should be read in light of the specification, as it would be interpreted by one of ordinary skill in the art. *See In re Suitco Surface, Inc.*, 603 F.3d 1255, 1260 (Fed. Cir. 2010). We generally give claim terms their ordinary and customary meaning. *See In re Translogic*

*Tech., Inc.*, 504 F.3d 1249, 1257 (Fed. Cir. 2007) ("The ordinary and customary meaning 'is the meaning that the term would have to a person of ordinary skill in the art in question." (quoting *Phillips v. AWH Corp.*, 415 F.3d 1303, 1313 (Fed. Cir. 2005) (en banc))).

The claims, however, "should always be read in light of the specification and teachings in the underlying patent," and "[e]ven under the broadest reasonable interpretation, the Board's construction 'cannot be divorced from the specification and the record evidence." *Microsoft Corp. v. Proxyconn, Inc.*, 789 F.3d 1292, 1298 (Fed. Cir. 2015) (quoting *In re NTP, Inc.*, 654 F.3d 1279, 1288 (Fed. Cir. 2011)). In other words, "[u]nder a broadest reasonable interpretation, words of the claim must be given their plain meaning, unless such meaning is inconsistent with the specification and prosecution history." *TriVascular, Inc. v. Samuels*, 812 F.3d 1056, 1062 (Fed. Cir. 2016) (citing *Straight Path IP Grp., Inc. v. Sipnet EU S.R.O.*, 806 F.3d 1356, 1362 (Fed. Cir. 2015)). Any special definition for a claim term must be set forth in the specification with reasonable clarity, deliberateness, and precision. *See In re Paulsen*, 30 F.3d 1475, 1480 (Fed. Cir. 1994). However, limitations are not to be read from the specification into the claims. *See In re Van Geuns*, 988 F.2d 1181, 1184 (Fed. Cir. 1993).

1. Construction of "using the [designated layer] as a mask"

In the Institution Decision, we preliminarily construed the phrase "using the [designated layer] as a mask"<sup>6</sup> as "using the [designated layer] to

<sup>&</sup>lt;sup>6</sup> Claim 13 recites several steps of etching "using" various layers—for example, the first resist pattern [step f]/second resist pattern and the mask pattern [step h]/patterned third insulating film [step i]—"as a mask." As shorthand, we refer to the various layers as "the designated layer."

define areas for etching."<sup>7</sup> Inst. Dec. 11–15. We further determined that "to meet the limitation 'using the [designated layer] for etching,' the designated layer 'must actually be *used* to *define areas for etching*." *Id.* at 15 (quoting Prelim. Resp. 6 (emphasis Patent Owner's)). Patent Owner agrees with this construction—namely, that "'using' something 'as a mask' during etching means *using it to define areas for etching*." PO Resp. 8–9. Petitioner also applied this construction in this proceeding. *See* Tr. 6:7–18; *see also id.* at 19:10–16 (Petitioner's counsel: "No, no, we did not present a construction and we did not contest the Board's construction."). The parties do not dispute that "using the [designated layer] as a mask" means "using the [designated layer] to define areas for etching," and we discern no reason from the evidence presented to change this construction. We, therefore, maintain our preliminary construction for purposes of this Final Written Decision.

# 2. <u>Application of the Construction of "using the [designated layer]</u> <u>as a mask"</u>

In the Institution Decision, we also provided additional guidance as to what "using the [designated layer] to define areas for etching" encompasses. *See* Inst. Dec. 15–19. In this regard, we provided the following non-exhaustive examples:

[W]e do not consider a mask pattern that is entirely within a surrounding resist layer to be "used as a mask" within the meaning of claim 13.

*Id.* at 15–16.

<sup>&</sup>lt;sup>7</sup> The district court construed the phrase in the same manner in an Order dated November 9, 2016. Ex. 3002, 20–22.

We . . . are not persuaded that a layer, positioned between an overlying layer and the layer being etched and having an edge in line and flush with an edge of the overlying layer, is "used as a mask" within the meaning of claim 13. Instead, to be "used as a mask," the between layer would need to define an additional portion of the layer being etched that is to be shielded from etching.

*Id.* at 18 (citing Figures 25(c) and 27(b) of the '696 patent as an example of

"defin[ing] an additional portion . . . to be shielded from etching").

Our construction does not preclude, for example, a layer positioned between an overlying layer and the layer being etched from acting as a mask, within the meaning of claim 13, in an instance where the overlying layer also is removed during the etching, and thus, the between layer acts to shield the layer being etched during etching.

Id. at 18 n.7.

Patent Owner argues, pointing to this discussion, that "the Board . . . incorrectly added an *additional negative limitation* that 'a layer, positioned between an overlying layer and the layer being etched and having an edge in line and flush with an edge of the overlying layer' is <u>not</u> "used as a mask" within the meaning of claim 13." PO Resp. 9–10 (quoting Inst. Dec. 18) (emphasis Patent Owner's); *see also id.* at 10–18. Patent Owner presents several arguments regarding this allegedly improper "additional negative limitation."<sup>8</sup> Because the parties' arguments regarding the priority claim of

<sup>&</sup>lt;sup>8</sup> The Institution Decision does not add any negative limitations to the claim construction. Our construction of "using the [designated layer] as a mask" was simply "using the [designated layer] to define areas for etching." *See* Inst. Dec. 11–15. Patent Owner refers to our discussion of what the claim construction encompasses as an "additional negative limitation." For convenience, we mirror Patent Owner's language in discussing Patent Owner's arguments. However, as noted, we do not view the discussion

the '696 patent (*see infra* Section II.D.1) turn on the application of our claim construction, we address Patent Owner's arguments here for convenience.

# Whether the "additional negative limitation impermissibly excludes preferred embodiments" of the '696 Patent (PO Resp. 10)

Patent Owner argues:

The additional negative limitation improperly excludes three preferred embodiments (*i.e.*, the third embodiment, a modified version of the third embodiment, and a modified version of a fifth embodiment) because they each require using an overlying layer and an intermediate layer together as a mask, where the intermediate layer has an edge that is *in line and flush with* an edge of the overlying layer.

PO Resp. 10–11 (citing Ex. 1001, 10:19–20, 16:39–48, 18:59–20:49, 24:52–27:60; Ex. 2009 ¶¶ 50–62).

While we agree with Patent Owner that a construction that "exclud[es] a preferred embodiment . . . 'is rarely, if ever, correct'" (PO Resp. 10 (citing *On–Line Techs. v. Bodenseewerk Perkin–Elmer GmbH*, 386 F.3d 1133, 1138 (Fed. Cir. 2004))), we note also that *every* claim need not cover *every* preferred embodiment (*see, e.g., Cybersettle, Inc. v. Nat'l Arbitration Forum, Inc.*, 243 F. App'x 603, 608 (Fed. Cir. 2007) (nonprecedential) ("Although Cybersettle's characterization of the specification is accurate, its argument based on the specification is flawed. That is because our

found at pages 15 to 19 of the Institution Decision as adding a negative limitation, but rather as examples of factual circumstances in which a particular layer is or is not used to define areas for etching. In other words, the discussion to which Patent Owner refers as an "additional negative limitation," was merely additional guidance provided to the parties as to what "using the [designated layer] to define areas for etching" encompasses. *See id.* at 15–19.

interpretation of claim 1 does not exclude the discussed embodiments from the scope of the claimed invention, but only excludes those embodiments from the scope of that claim. Although claim 1 does not capture the discussed embodiments, other claims do.")). Further, there is no requirement that every feature disclosed in the specification be recited in the claims. *See Ventana Med. Sys., Inc. v. Biogenex Labs., Inc.*, 473 F.3d 1173, 1181–82 (Fed. Cir. 2006) ("Although the preferred embodiments also contain a 'direct dispensing' feature, the inventors were not required to claim this feature in the '861 patent and, indeed, did not do so.").

In any event, we disagree that our construction, or our application thereof with which Patent Owner disagrees, excludes the features of the embodiments identified by Patent Owner. Regarding the modified fifth embodiment, for example, claim 10 covers this embodiment. A chart comparing the modified fifth embodiment to claim 10 is provided below.<sup>9</sup> *See* Ex. 1001, 24:53–26:47.

| Claim 10                                                                             | Figures<br>Illustrating<br>Modified Fifth<br>Embodiment |

|--------------------------------------------------------------------------------------|---------------------------------------------------------|

| A method for forming an interconnection structure,<br>comprising the steps of:       |                                                         |

| a) forming a first insulating film [553] over lower-level metal interconnects [551]; | Fig. 24(a)                                              |

<sup>&</sup>lt;sup>9</sup> The bracketed numbers within the claim language identify the elements of the corresponding figures, as recited in the claims. They correspond to the identifications made in the description of the modified fifth embodiment, correlating the specific elements in the figures to the claim language. *See*, *e.g.*, Ex. 1001, 24:65–66 ("a first organic film 553 (first insulating film)").

| Claim 10                                                                                                                                                                                                                                             | Figures<br>Illustrating<br>Modified Fifth<br>Embodiment                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| b) forming a second insulating film [554], having a different composition than that of the first insulating film, over the first insulating film [557];                                                                                              |                                                                          |

| c) forming a third insulating film [555], having a different composition than that of the second insulating film, over the second insulating film [554];                                                                                             |                                                                          |

| d) forming a fourth insulating film [556], having a different composition than that of the third insulating film, over the third insulating film [555];                                                                                              |                                                                          |

| <ul><li>e) forming a thin film [557] over the fourth insulating film [556];</li><li>f) forming a first resist pattern [558] on the thin film</li></ul>                                                                                               | Fig. 24(b)                                                               |

| [557], the first resist pattern [558] having openings for forming wiring grooves;                                                                                                                                                                    | Fig. 24(c)                                                               |

| g) etching the thin film [557] using the first resist pattern [558] as a mask, thereby forming a mask pattern [559] out of the thin film to have the openings for forming wiring grooves;                                                            | 1'lg. 24(C)                                                              |

| h) removing the first resist pattern [558] and                                                                                                                                                                                                       | Fig. 25(a),<br>Fig. 27(a)                                                |

| then forming a second resist pattern [560] on the fourth<br>insulating film [556] and the mask pattern [559], the<br>second resist pattern [560] having openings for forming<br>contact holes;                                                       | Fig. 25(b), (seen<br>in Fig. 27(b),<br>after the etching<br>of step (i)) |

| <ul> <li>i) dry-etching the fourth insulating film [556] using the second resist pattern [560] and the mask pattern [559] as a mask, thereby patterning the fourth insulating film [556A] to have the openings for forming contact holes;</li> </ul> | Fig. 25(c),<br>Fig. 27(b)                                                |

| j) dry-etching the third insulating film [555] using the<br>patterned fourth insulating film [556A] as a mask,<br>thereby patterning the third insulating film [555A] to<br>have the openings for forming contact holes;                             | Fig. 26(a);<br>Fig. 28(a)                                                |

| Claim 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figures<br>Illustrating<br>Modified Fifth<br>Embodiment |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| <ul> <li>k) dry-etching the patterned fourth insulating film</li> <li>[556A] and the second insulating film [554] using the mask pattern [559] and the patterned third insulating film</li> <li>[555A] as respective masks, thereby forming wiring grooves in the patterned fourth insulating film [556B] and patterning the second insulating film to have the openings for forming contact holes [554A];</li> <li>b) dry atching the patterned third insulating film [555A]</li> </ul> | Fig. 26(b);<br>Fig. 28(b)                               |

| <ol> <li>dry-etching the patterned third insulating film [555A]<br/>and the first insulating film [553] using the mask pattern<br/>[559] and the patterned second insulating film [554A] as<br/>respective masks, thereby forming the wiring grooves<br/>[561] and the contact holes [562] in the patterned third<br/>insulating film and the first insulating film, respectively;<br/>and</li> </ol>                                                                                    | Fig. 26(c);<br>Fig. 29(a)                               |

| m) filling in the wiring grooves and the contact holes<br>with a metal film, thereby forming upper-level metal<br>interconnects [563] and contacts [564] connecting the<br>lower- and upper-level metal interconnects together.                                                                                                                                                                                                                                                          | Fig. 26(d);<br>Fig. 29(b)                               |

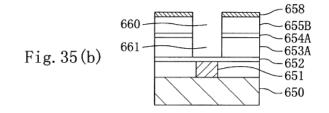

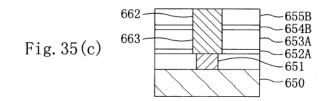

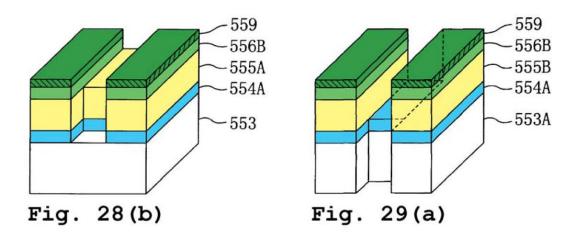

Patent Owner points to Figures 28(b) and 29(a) of the '696 patent, and provides annotated versions, reproduced below (PO Resp. 14<sup>10</sup>).

Figures 28(b) and 29(a), above, are perspective views of a partially formed interconnection structure. Ex. 1001, 9:43–48. As noted by Patent Owner, the Specification describes that, after the step shown in Figure 28(b),

the patterned second organic film 555A is dry-etched using the mask pattern 559 and the patterned second silicon dioxide film 556B as a mask, and the first organic film 553 is dry-etched using the patterned first silicon dioxide film 554A as a mask, thereby forming a patterned second organic film 555B having wiring grooves 561 and a patterned first organic film 553A having contact holes 562 as shown in FIGS. 26(c) and 29(a).

Ex. 1001, 26:22–29 (emphasis added); PO Resp. 13. Patent Owner argues that patterned second silicon dioxide film 556B (i.e., the claimed patterned fourth insulating layer with the wiring grooves formed therein) is not used as a mask, under our application of the construction, despite being described as

<sup>&</sup>lt;sup>10</sup> Patent Owner indicates that "[a]s illustrated [in the Patent Owner Response] layers being used as a mask for a certain step are indicated in green, [and] layers to be or having been etched for a certain step are indicated in yellow." PO Resp. 7 n.5 (citing Ex. 2009 ¶ 43 n.2).

such in the Specification. PO Resp. 13–14. The claim, however, does not recite this step in this manner. As noted in the chart above, in this embodiment, step (k) of claim 10 results in the structure shown in Figure 28(b). The step describing the etching of patterned second organic film 555A corresponds to step (l) of claim 10, and recites only "dry-etching the patterned third insulating film [555A]... using the mask pattern [559]... as [a] mask[]." The claim does not recite using the patterned fourth insulating layer with the wiring grooves formed therein (i.e., patterned second silicon dioxide film 556B) as a mask for etching the patterned third insulating film (i.e., patterned second organic film 555A). Thus, contrary to Patent Owner's assertion, our application of the construction does not exclude this embodiment.

Similarly, regarding the third embodiment and the modified third embodiment, the portions of the Specification that Patent Owner asserts are excluded from the claims under our application of the construction are not actually recited in any claim.

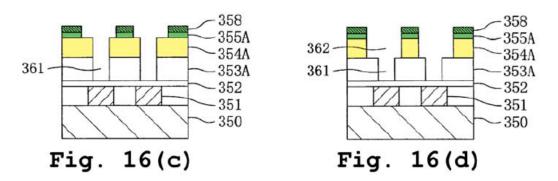

Regarding the modified third embodiment, Patent Owner points to Figures 16(c) and 16(d) of the '696 patent, and provides annotated versions, reproduced below (PO Resp. 12).

Figures 16(c) and 16(d), above, are cross-sectional views of a partially formed interconnection structure. Ex. 1001, 9:1–4. As noted by Patent Owner, the Specification describes that, after the step shown in Figure 16(c)

the patterned organic film 354A is dry-etched using the mask pattern 358 and the patterned second silicon dioxide film 355A having the openings for forming wiring grooves as a mask, thereby forming the wiring grooves 362.

Ex. 1001, 19:50–54 (emphasis added); PO Resp. 11–12. Mapping the modified third embodiment to claim 10, this description corresponds to claim step (1), which recites "dry-etching the patterned third insulating film [354A] . . . using the mask pattern [358] . . . as [a] mask[]." Notably, the claim does not recite using the patterned fourth insulating film (i.e., patterned second silicon dioxide film 355A) as a mask in this recited step. Mapping the modified third embodiment to claim 13,<sup>11</sup> this description corresponds to an unclaimed step between claim steps (j) and (k). Thus, again contrary to Patent Owner's assertion, our application of the construction, on this point, does not exclude the third modified embodiment.<sup>12</sup>

<sup>&</sup>lt;sup>11</sup> We note that for purposes of this discussion, we focus on the portions of the embodiment identified by Patent Owner as being excluded from the claim. By "mapping" this embodiment to the claims, we are not indicating an agreement with respect to Patent Owner's other arguments regarding priority, discussed below—namely that the modified third embodiment provides written description support for step (h) of claim 13.

<sup>&</sup>lt;sup>12</sup> Claims 1–9 each include steps requiring the presence of both the first resist pattern and second resist pattern in a single step (*see*, *e.g.*, claim 1, step (h), claim 8, step (h)). Because the modified third embodiment requires removal of the first resist pattern before formation of the second resist pattern (*see* Ex. 1001, 19:30–32), these claims cannot cover this embodiment.

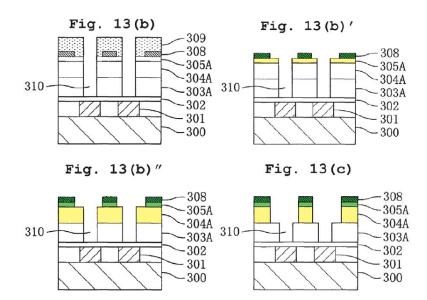

Regarding the third embodiment, Patent Owner points to Figures 13(b) and 13(c) of the '696 patent, and provides annotated versions (including intermediate steps not depicted in the '696 patent), reproduced below (PO Resp. 13).

Figures 13(b), 13(b)', 13(b)'' and 13(c), above, are cross-sectional views of a partially formed interconnection structure. Ex. 1001, 8:58–60. As noted by Patent Owner, the Specification describes that, after the step shown in Figure 13(b)

the patterned low-dielectric-constant SOG film 304A is dry-etched using the mask pattern 308 and the patterned second organic-containing silicon dioxide film 305A having the openings for wiring grooves as a mask, thereby forming the wiring grooves 311.

Ex. 1001, 17:34–40 (emphasis added); PO Resp. 12–13. Mapping the third embodiment to claim 10, this description corresponds to claim step (l), which recites "dry-etching the patterned third insulating film [304A]... using the mask pattern [308]... as [a] mask[]." Notably, the claim does not recite using the patterned fourth insulating film (i.e., patterned second silicon

dioxide film 305A) as a mask in this recited step. Mapping the third embodiment to claim 13, this description corresponds to an unclaimed step between claim steps (j) and (k). Thus, again contrary to Patent Owner's assertion, our application of the construction, on this point, does not exclude the third embodiment.<sup>13</sup>

Finally, we note that our determination in the Institution Decision that a layer that is shown in the drawings as "in line and flush with an edge of" an overlying layer does not necessarily act as a mask (see Inst. Dec. 17–18) is not inconsistent with the disclosure in the '696 patent. For example, with respect to Figures 16(c) and 16(d) of the modified third embodiment, the '696 patent expressly states that both layers identified by Patent Owner (i.e., layers 355A and 358) are used as a mask. See Ex. 1001, 19:50–54. Thus, the teaching in the '696 patent that layer 355A is used as a mask, in addition to layer 358, in etching layer 354A is not determined from the teachings of Figures 16(c) and 16(d) alone. See also Tr. 30:23-31:3 (Patent Owner's counsel noting that "the '696 specification expressly says 509 is a mask. It doesn't depict how 509 is a mask, but we know ... that there are threedimensional aspects of some of these objects . . . ." (emphasis added)). Similarly, throughout the Specification, whether or not a particular layer is used as a mask is not determined from the figures alone. Instead, in some instances, the Specification indicates *in the text* that certain between layers

<sup>&</sup>lt;sup>13</sup> Claims 1–9 each include steps requiring the presence of both the first resist pattern and second resist pattern in a single step (*see, e.g.*, claim 1, step (h), claim 8, step (h)). Because the third embodiment requires removal of the first resist pattern before formation of the second resist pattern (*see* Ex. 1001, 17:17–18), these claims cannot cover this embodiment.

are used as a mask, whereas in other instances, it does not.<sup>14</sup> The Specification of the '696 patent does not include any express definition of a "mask" that is inconsistent with our application of the claim construction.

Whether the "additional negative limitation is impermissibly narrower than the Phillips Standard" (PO Resp. 14)

Patent Owner argues that the "[broadest reasonable interpretation] 'cannot be narrower' than the construction under *Phillips*." PO Resp. 14 (citing *Facebook v. Pragmatus AV*, 582 F. App'x 864, 868–69 (Fed. Cir. 2014) (nonprecedential)). However, our construction is, in fact, identical to

<sup>&</sup>lt;sup>14</sup> Patent Owner also points, for example, to the description of Figures 6(a) to 6(b) as allegedly inconsistent with our application of the construction, arguing that layer 104A is identified in the Specification as a mask, and it is "flush with the sidewall on the right" in Figures 6(a) and 6(b). See Tr. 38:10–40:6. Patent Owner contends further that the Specification does not identify top layer 108 as a mask. Id. For the etch illustrated in these figures, the Specification describes that patterned organic-containing silicon dioxide film 104A has the openings for the contact holes (Ex. 1001, 13:25-27), and mask pattern 108 has the openings for the wiring grooves (id. at 12:66–13:4). The etch of silicon nitride film 102, depicted in Figures 6(a) and 6(b), forms the contact holes in that layer. Id. at 13:37–41. The description in the Specification that patterned organic-containing silicon dioxide film 104A is used as a mask for this etch is consistent with our application of the construction—in other words, layer 104A is expressly described as defining areas for etching (to create contact holes). This is yet another instance in which the Specification expressly describes a between layer (i.e., layer 104A) as a mask; the discussion does not, however, preclude layer 108 from also acting as a mask. See also Tr. 65:25-66:21 (Petitioner's counsel discussing the "context" of the description in the Specification). We also note, that this discussion relates to "problems" caused by the misalignment of the second resist pattern 109 with the first resist pattern 107." Ex. 1001, 12:44–46. In the non-misaligned embodiment (see id. at Figs. 2(c), 3(a)), layer 104A is not a flush middle layer during the etch of layer 102A.

that of the district court. *Compare* Ex. 3002, 22 (construing "using the [first resist pattern/second resist pattern and the mask pattern/patterned third insulating film] as a mask" to mean "using the [first resist pattern/second resist pattern and the mask pattern/patterned third insulating film] to define areas for etching"), *with* Inst. Dec. 15 (construing "using the [designated layer] as a mask" to mean "using the [designated layer] to define areas for etching"); *see* PO Resp. 14–15. Petitioner notes that the district court never applied the construction, as we must do in this proceeding, and, thus, Patent Owner has no basis to assert the district court would have applied the construction any differently. Reply 9. We agree.

# Whether the "additional negative limitation is inconsistent with the plain and ordinary meaning, understanding of a person of ordinary skill in the art[, and Dr. Smith's] prior publication" (PO Resp. 15)

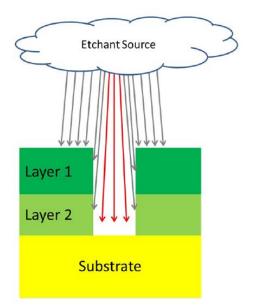

Finally, Patent Owner argues "the Board has taken a narrow view that considers only top surfaces of a layer and excludes sidewalls of a layer from defining areas for etching that is inconsistent with the term's plain and ordinary meaning." PO Resp. 15 (citing Inst. Dec. 15; Ex. 2009 ¶¶ 63–65). Patent Owner provides an illustration of a "multi-layer mask (composed of an intermediate layer having edges in line and flush with edges of a top layer)," reproduced below (*id.* at 15–16).

The figure, above, is an illustration provided by Patent Owner of a "multilayer mask." *Id.* According to Patent Owner, "although top surfaces of the top layer mask vertical flow of etchant, sidewalls of the top layer and the intermediate layer also mask horizontal flow of etchant, thereby collimating the flow of etchant to define areas of etching a substrate." *Id.* at 16 (citing Ex. 2009 ¶ 66). Patent Owner continues "[m]oreover, it is undisputed that Layer 1's bottom portion bordering the hole is part of the mask, and there is no meaningful difference between the function of the material bordering the hole at the top of Layer 2 from the material bordering the hole at the very bottom of Layer 1." *Id.* (citing Ex. 2009 ¶¶ 67–68); *see also* Tr. 36:15– 37:10 (Patent Owner's counsel arguing that, although only two layers are shown in the figure above, any number of flush sidewalls would act as a mask as long as the layer "comes in contact with the etchant, however minute").

In its Reply, Petitioner argues that the etching process at issue (i.e., reactive ion etching) is "highly directional with negligible lateral deviation."

Reply 4–5 (citing Ex. 1030, 25, 39, 41; Ex. 1031, 56; Ex. 1049 ¶ 11). According to Petitioner, Patent Owner's representation above is inaccurate. Petitioner notes that if non-vertical trajectories were included, the layer being etched would be undercut, as shown in Petitioner's revised representation reproduced below (Reply 5 (citing Ex. 1049 ¶ 12)).

The figure, above, is an illustration provided by Petitioner, showing a revision of Patent Owner's illustration of a "multi-layer mask." *Id.* According to Petitioner, undercutting does not occur during reactive ion etching in practice (*id.* (citing Ex. 1049 ¶ 12)), but instead reactive ion etching "result[s] in directional, anisotropic etching" (*id.* (quoting Ex. 1030, 41)). *See id.* at 5–6 (citing Ex. 1030, 40–41; Ex. 1049 ¶¶ 13–15). Thus, according to Petitioner, Patent Owner's "speculat[ion]" that "a buried layer blocks laterally traveling particles" during etching (*see* PO Resp. 16) is incorrect. Reply 4. According to Petitioner, such a buried layer "has nothing to do with the etch" and does not define an area for etching. *Id.*

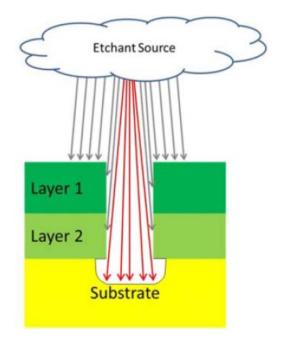

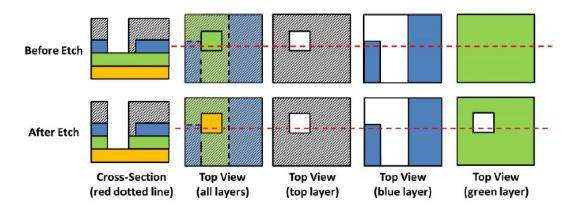

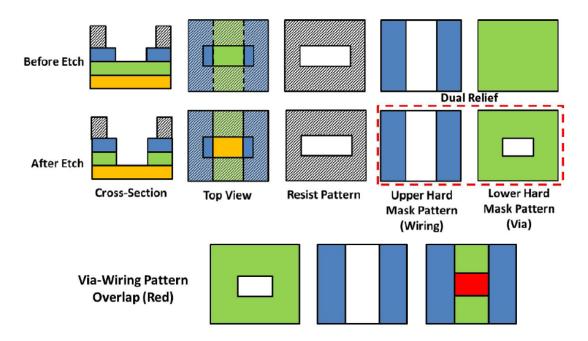

Petitioner provides an illustrative example, reproduced below (Reply 4; Ex. 1049 ¶ 29).

The figures above are an illustration of a mask, provided by Petitioner. As shown in these figures, the striped layer contains a via pattern, which is transferred into the green layer by the illustrated etch. *See* Reply 4 (citing Ex. 1049 ¶ 29). The blue layer, which under Patent Owner's argument would comprise a mask in the illustrated etch, contains a wiring pattern, and according to Petitioner "plays no role [in] defining the square-shaped via pattern, which is what a mask does." *Id.* (citing Ex. 1049 ¶ 29). In this example, the shape of the via etched into the green layer is defined by the opening in the striped (top) layer, and is not defined by the blue (buried) layer. Ex. 1049 ¶ 29.

We credit Dr. Smith's testimony regarding the anisotropic characteristics of reactive ion etching, finding it more consistent with the evidence of record. Ex. 1049 ¶¶ 11–15. While we recognize that no anisotropic etch will be perfectly vertical (*see* Tr. 33:6–34:10), Dr. Smith testifies that one of skill in the art would recognize that such an etch is vertical "[w]ithin the capability of measurement or within the requirements of manufacturing." Ex. 2040, 22:6–10; *see also id.* at 22:11–12 (further

noting "the word 'perfectly' [vertical] would have to be defined in that context"); Ex. 1030, 626–27 ("In ion-enhanced etching, both chemical and physical components are acting, but the profiles are not just a linear combination of isotropic chemical etching and anisotropic physical etching .... Instead, the profile for ion-enhanced etching is much more like the case for physical etching acting alone .... If the chemical component in the etch system is increased, the vertical etching is increased but not the lateral etching, which is not what would be expected from chemical etching.... Whatever the exact mechanism for ion-enhanced etching, .... directional enhancement will result in directional, anisotropic etching."); Reply 4–5. Further, Dr. Glew's testimony as to how a person of ordinary skill in the art would have read the claim language is not supported by evidence of record. See Ex. 2009 ¶¶ 63–68 (citing only the '696 patent and the generic dictionary definition of "mask" (Ex. 3001) referenced in the Institution Decision); 37 C.F.R. § 42.65(a) ("Expert testimony that does not disclose the underlying facts or data on which the opinion is based is entitled to little or no weight.").

Patent Owner also points to a prior publication of Dr. Smith discussing a "trilayer resist" that is allegedly inconsistent with his testimony in this proceeding. *See* PO Resp. 17 (citing, e.g., Ex. 2018, 642–43, 657). We find Petitioner's explanation of the "tri-layer resist process" more accurately reflects the understanding of one of skill in the art. Petitioner cites to several contemporary references in explaining that a "tri-layer resist process . . . begins with an intermediate hard mask layer (e.g., SiO2) sandwiched between a top photoresist layer and a bottom planarization/primary layer. The top resist layer is the mask for patterning

the intermediate layer, and afterward, the intermediate layer acts as the mask for etching the bottom layer. The intermediate layer is not a mask because of its sidewalls; it becomes a mask after eliminating the top resist layer . . . ." Reply 6–7 (internal citations omitted) (citing Ex. 1031, 41–42, 70, Fig. 17; Ex. 1032, 14, Fig. 11; Ex. 1033, Abstract, 2:28–35, 3:20–41; Ex. 1044, 4–6; Ex. 1045, 3; Ex. 1046, 2–3; Ex. 2010, 60:22–63:2; Ex. 2015, 8; Ex. 1049 ¶ 18); *see also* Ex. 1049 ¶¶ 16–19. We are not persuaded Dr. Smith's prior publication is inconsistent with his testimony on this point in this proceeding or with our application of the claim construction.

## 3. Conclusion as to Claim Construction

For all of the reasons set forth herein and in the Institution Decision, we construe "using the [designated layer] as a mask" to mean "using the [designated layer] to define areas for etching," and are not persuaded that a layer, depicted as being positioned between an overlying layer and the layer being etched and having an edge in line and flush with an edge of the overlying layer, is used as a mask within the meaning of claim 13, absent textual discussion describing the layer as such.

#### D. Whether Grill Qualifies as Prior Art

Each of the asserted grounds relies, at least in part, on Grill. *See* Pet. 36–74. Patent Owner argues that "Grill is not prior art." *See* PO Resp. 18–47. We, thus, at the outset determine the prior art status of Grill as to claims 13 and 15 of the '696 patent.

The application that issued as the '696 patent was filed on March 23, 1999. Ex. 1001, at [22]. The '696 patent claims priority to Japanese

Application No. 10-079371, filed on March 26, 1998 ("the Japanese priority application"<sup>15</sup>). *Id.* at [30].

Grill was filed on July 30, 1998 and issued on October 31, 2000. Ex. 1005, at [22], [45]. Grill also claims priority to U.S. Provisional Application No. 60/071,628, filed January 16, 1998 ("Grill provisional application"). *Id.* at [60].

Petitioner asserts that "[d]ue to its July 30, 1998, filing date, *Grill* is prior art to the '696 patent under [35 U.S.C.] § 102(e)" (Pet. 28), because, as Petitioner argues, the challenged claims are not entitled to the filing date of the Japanese priority application. *Id.* at 20–27. Petitioner additionally asserts that "*Grill* would still qualify as prior art under §102(e) even if the challenged claims were entitled" to the filing date of the Japanese priority application, because Grill itself is entitled to the earlier filing date of the Grill provisional application. *Id.* at 28.

Patent Owner argues that challenged claim 13 is entitled to the '696 patent's claimed priority date of March 26, 1998 (PO Resp. 20–31), and that Petitioner has not shown that Grill is entitled to the priority date of the Grill provisional application (*id.* at 31–47).

### 1. The '696 Patent's Claim to the Japanese Priority Application

"Under [35 U.S.C.] section 119, the claims set forth in a United States application are entitled to the benefit of a foreign priority date if the corresponding foreign application supports the claims in the manner required by section 112, ¶ 1." *In re Gosteli*, 872 F.2d 1008, 1010 (Fed. Cir. 1989); *see also K & K Jump Start/Chargers, Inc. v. Schumacher Elec. Corp.*,

<sup>&</sup>lt;sup>15</sup> Petitioner provided a certified translation of the Japanese priority application. Ex. 1014.

13 F. App'x 982, 983 (Fed. Cir. 2001) (nonprecedential) ("The later filed [U.S.] patent . . . is entitled to the filing date of the earlier filed [foreign] patent . . . if the earlier filed patent meets the written description test of 35 U.S.C. § 112, first paragraph.").

Petitioner points to several features of independent claim 13 that it contends are not supported in the Japanese priority application. Pet. 21–27. In particular, Petitioner asserts that the embodiments described in the Japanese priority application do not disclose steps (g), (h), or (i) of claim 13. *See id.* Patent Owner argues that the variant of the third embodiment described in the Japanese priority application fully supports claim 13 under 35 U.S.C. § 112, first paragraph. PO Resp. 20–31. In our Institution Decision, we preliminarily determined that the variant of the third embodiment described in the Japanese priority application did not provide sufficient support for step (h) of claim 13. *See* Inst. Dec. 22–25. The parties' dispute focuses on this limitation. Thus, we focus our discussion on step (h) of claim 13.

#### Claim 13, step (h)

Claim 13, step (h) recites "dry-etching the third insulating film using the second resist pattern and the mask pattern as a mask, thereby patterning the third insulating film to have the openings for forming contact holes."

Petitioner argues that the third, variant of the third, and fourth embodiments of the Japanese priority application do not disclose step (h) of claim 13. Pet. 23–25. Because Patent Owner's arguments focus on the variant of the third embodiment, we limit our discussion to this embodiment.

Patent Owner's argument that this claim step is disclosed in the Japanese priority application is as follows:

For example, [the Japanese priority application] discloses that the second resist pattern may be misaligned during fabrication. To address this misalignment, the underlying mask pattern is etched using the second resist pattern as a mask. As an effect of such etching, edges of the second resist pattern become *in line and flush with* the edges of the mask pattern. Accordingly, when the underlying third insulating film is subsequently patterned, both the second resist pattern and the mask pattern together define areas for the patterning—*i.e.*, they are both "used . . . as a mask," as claimed.

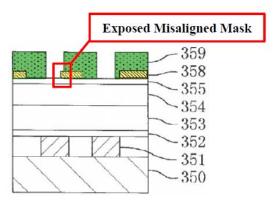

PO Resp. 24–25 (internal citations omitted) (citing Ex. 1014 ¶ 96; Ex. 2009 ¶ 87). Patent Owner provides a series of illustrations to support this point. *Id.* at 25–26. First, Patent Owner includes a modified version of Figure 16(a) of the Japanese priority application, reproduced below (*id.* at 25 (citing Ex. 1014 ¶ 96; Ex. 2009 ¶ 88)).

According to Patent Owner, the above figure illustrates Figure 16(a) in the case where "the mask pattern 358 is exposed to the openings of the second resist pattern 359 for the formation of contact holes because of the misalignment." *Id.* (citing Ex. 1014 ¶ 96; Ex. 2009 ¶ 89). Patent Owner

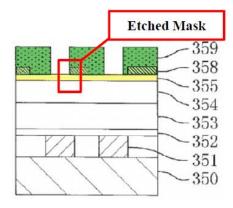

then provides another modified version of Figure 16(a) of the Japanese priority application, reproduced below (*id.* at 26 (citing Ex. 1014  $\P$  96; Ex. 2009  $\P$  89)).

According to Patent Owner, the above figure illustrates Figure 16(a) "[a]fter 'the mask pattern 358 is dry-etched using the second resist pattern 359 as a mask,' [such that] an edge of mask pattern 358 is *in line and flush with* an edge of second resist pattern 359." *Id.* at 25 (citing Ex. 1014 ¶ 96; Ex. 2009 ¶ 89).

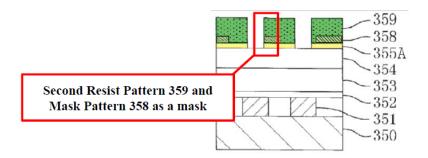

Patent Owner further includes another modified version of Figure 16(a) of the Japanese priority application, reproduced below (*id.* at 26 (citing Ex. 1014 ¶¶ 93, 96; Ex. 2009 ¶ 90)).

According to Patent Owner, the above figure illustrates Figure 16(a) after "[e]tching of the 'third insulating film [355]' is . . . done 'using the second

resist pattern [359] and the mask pattern [358] as a mask,' using the edges that are in line and flush." *Id.* (citing Ex. 1014 ¶¶ 93, 96; Ex. 2009 ¶ 90).

Patent Owner's arguments in this regard are premised on its assertion that "using the [designated layer] as a mask" encompasses a situation in which the modified mask pattern 358, having "edges that are in line and flush with" second resist pattern 359, is therefore used as a mask. For the reasons discussed above, we do not agree with Patent Owner that "us[ed]... as a mask" necessarily encompasses such a situation. *See supra* Section II.C.2.

We note that the application of our construction would not *preclude* layer 358 as shown in Patent Owner's modified Figure 16(a) from ever being a mask when etching layer 355, if it were in fact *described* as such. However, there is no such description in the Japanese priority application; instead, the corresponding discussion identifies *only* second resist pattern 359 as a mask for this etching step. See Ex. 1014 ¶ 96 ("If there is a concern that the second resist pattern 359 has been misaligned with the first resist pattern 357, then the mask pattern 358 should be dry-etched using the second resist pattern 359 as a mask before the second silicon dioxide film 355 is dry-etched using the second resist pattern 359 as a mask." (emphasis added)). Further, as noted by Petitioner (Reply 10–11), the corresponding discussion is, at best, ambiguous as to whether mask pattern 358 is "used as a mask" for etching layer 355. Ex. 1014 ¶ 96 ("That is to say, if the mask pattern 358 is exposed to the openings of the second resist pattern 359 for the formation of contact holes because of the misalignment of the second resist pattern 359 with the first resist pattern 357, then the mask pattern 358 is dry-etched using the second resist pattern 359 as a mask. In this manner,

the openings of the mask pattern 358 are expanded to include the openings for the formation of wiring grooves and contact holes." (emphasis added)). This disclosure is not sufficient to provide support under 35 U.S.C. § 112, first paragraph, for step (h) of claim 13. See Tronzo v. Biomet, Inc., 156 F.3d 1154, 1158 (Fed. Cir. 1998) ("For a claim in a later-filed application to be entitled to the filing date of an earlier application under 35 U.S.C. § 120 (1994), the earlier application must comply with the written description requirement of 35 U.S.C. § 112, ¶ 1 (1994). ... A disclosure in a parent application that merely renders the later-claimed invention obvious is not sufficient to meet the written description requirement; the disclosure must describe the claimed invention with all its limitations." (citing Lockwood v. American Airlines, Inc., 107 F.3d 1565, 1571-72 (Fed. Cir. 1997))); see also K & K Jump Start, 13 F. App'x at 984 ("In order for claim 1 of the [U.S.] patent to be entitled to the priority date of the [foreign] application, the test set forth in [Tronzo, 156 F.3d at 1158] must be satisfied.").

## 2. Conclusion as to Whether Grill Qualifies as Prior Art

Having considered the evidence in this record, we determine that at least step (h) of claim 13 is not supported by the Japanese priority application.<sup>16</sup> Accordingly, the effective filing date of the challenged claims is March 23, 1999, and Grill is available as prior art as to claims 13 and 15 of the '696 patent under 35 U.S.C. § 102(e).

<sup>&</sup>lt;sup>16</sup> Because we find that claim 13 is not supported by the Japanese priority application, we need not discuss the parties' arguments and evidence regarding whether or not Grill is entitled to the priority date of the Grill provisional application. Nor must we decide whether Petitioner's corresponding arguments and evidence submitted in the Reply are proper.

## E. Obviousness in View of Grill and Aoyama

Petitioner asserts that claims 13 and 15 are unpatentable under 35 U.S.C. § 103 as obvious in view of the combination of Grill and Aoyama. Pet. 52–74. Patent Owner argues that one of ordinary skill in the art would not have combined the references in the manner asserted by Petitioner. PO Resp. 47–73. For the reasons explained below, we determine that Petitioner has demonstrated, by a preponderance of the evidence, that claims 13 and 15 would have been obvious in view of Grill and Aoyama.

1. Scope and Content of the Prior Art

### **Overview of Grill**

Grill relates to "lithographic methods for forming a dual relief pattern in a substrate, and the application of such methods to fabricating multilevel interconnect structures in semiconductor chips by a Dual Damascene process." Ex. 1005, at [57].

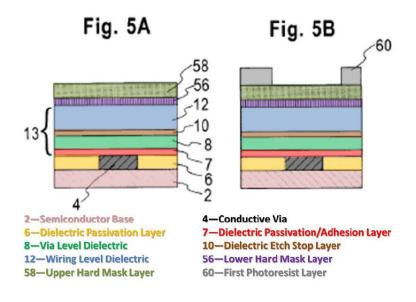

Grill describes various embodiments; one exemplary embodiment is depicted in Figures 5A–5H and 1J–1L. Petitioner provides annotated and colored versions of Figures 5A and 5B of Grill (Pet. 30), reproduced below.

Petitioner's annotated versions of Figures 5A and 5B of Grill, reproduced above, show cross-sectional views of partially formed structures during process steps in the method of an embodiment of Grill. Ex. 1005, 3:45–47. The structure of Figure 5A is formed, and then first photoresist layer 60 is formed and patterned, as shown in Figure 5B. *Id.* at 7:30–44.

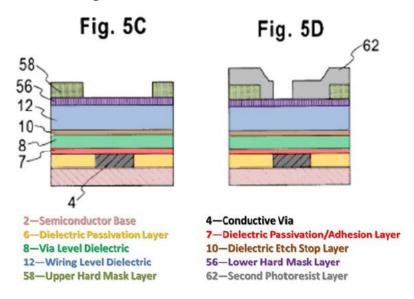

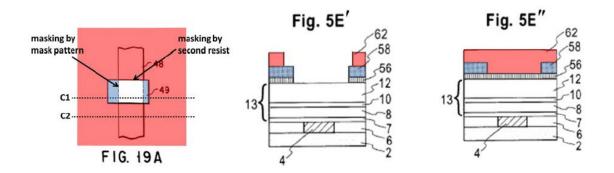

Petitioner provides annotated and colored versions of Figures 5C and 5D of Grill (Pet. 31), which illustrate subsequent steps in the method of this embodiment and are reproduced below.

Petitioner's annotated versions of Figures 5C and 5D of Grill, reproduced above, show cross-sectional views of partially formed structures during process steps in the method of an embodiment of Grill. Ex. 1005, 3:45–47. The pattern of photoresist pattern 60 is transferred into upper hard mask layer 58, as shown in Figure 5C. *Id.* at 7:45–50. Pattern 60 is removed and second photoresist layer 62 is formed and patterned, as shown in Figure 5D. *Id.* at 7:51–55.

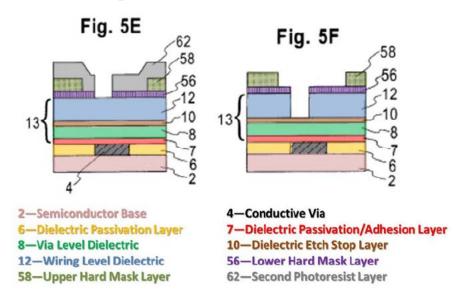

Petitioner provides annotated and colored versions of Figures 5E and 5F of Grill (Pet. 31), which illustrate subsequent steps in the method of this embodiment and are reproduced below.

Petitioner's annotated versions of Figures 5E and 5F of Grill, reproduced above, show cross-sectional views of partially formed structures during process steps in the method of an embodiment of Grill. Ex. 1005, 3:45–47. The pattern of photoresist pattern 62 is transferred into lower hard mask layer 56, as shown in Figure 5E. *Id.* at 7:57–61. The pattern is further transferred to wiring level dielectric layer 12, by an etch that also removes second photoresist layer 62, as shown in Figure 5F. *Id.* at 7:62–66.

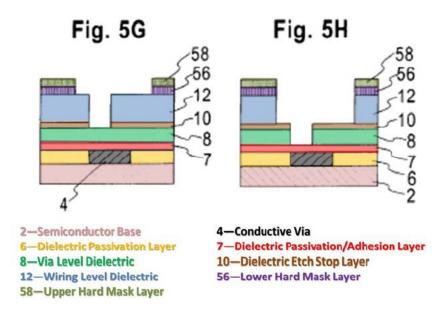

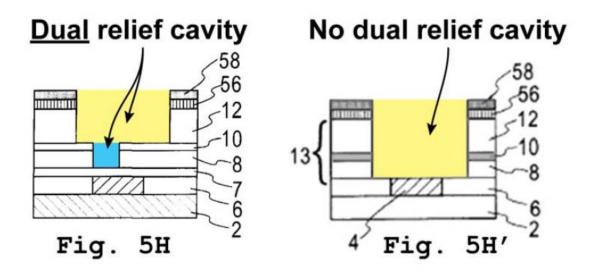

Petitioner provides annotated and colored versions of Figures 5G and 5H of Grill (Pet. 32), which illustrate subsequent steps in the method of this embodiment and are reproduced below.

Petitioner's annotated versions of Figures 5G and 5H of Grill, reproduced above, show cross-sectional views of partially formed structures during process steps in the method of an embodiment of Grill. Ex. 1005, 3:45–47. Exposed portions of lower hard mask layer 56 and etch stop layer 10 are removed by etching, as shown in Figure 5G. *Id.* at 7:67–8:2. A further etch removes exposed portions of dielectric layers 8 and 12, as shown in Figure 5H. *Id.* at 8:2–5.

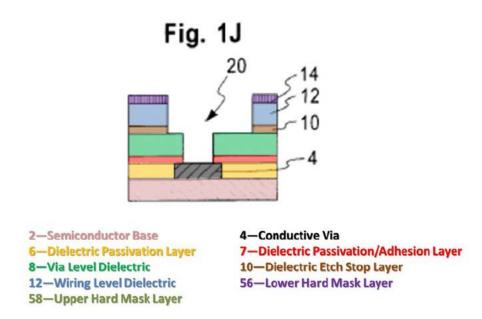

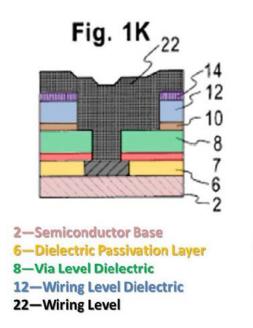

As noted in Grill, after completion of the step shown in Figure 5H, the structure may be completed as shown in Figures 1J through1L. *See id.* at 8:5–8. A final etch removes the exposed portions of optional dielectric layer 7, which also removes the exposed portions of etch stop 10, as shown in Figure 1J, an annotated and colored version of which is reproduced below (Pet. 32). Ex. 1005, 4:61–64, 8:5–8; Ex. 1002 ¶ 148.

Petitioner's annotated version of Figure 1J, reproduced above, shows a cross-sectional view of a partially formed structure during one step in a dual damascene process flow. Ex. 1005, 3:33–36. Petitioner provides annotated and colored versions of Figures 1K and 1L of Grill (Pet. 33), which illustrate subsequent steps in the method of this embodiment and are reproduced below.

4—Conductive Via 7—Dielectric Passivation/Adhesion Layer 10—Dielectric Etch Stop Layer 14/56—Hard Mask Layer

Petitioner's annotated versions of Figures 1K and 1L, reproduced above, show cross-sectional views of partially formed structures during process steps in a dual damascene process flow. Ex. 1005, 3:33–36. As seen in Figure 1K, cavity 20 (Fig. 1J) is filled with conductive material 22, which is then planarized by a chemical-mechanical polishing process, as shown in Figure 1L. *Id.* at 4:64–5:8, 8:5–8.

#### **Overview** of Aoyama

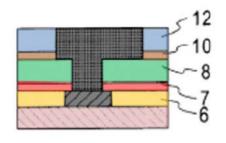

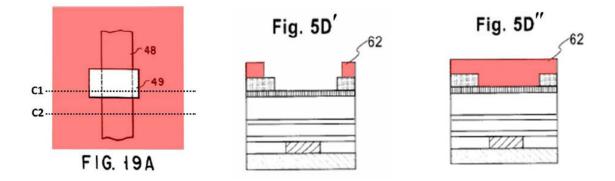

Aoyama teaches a dual damascene process in which the opening in a via resist pattern is wider than the wiring groove. Ex. 1018, 15:48–51, 16:3–5, Figs. 18A–18C, 19A–19B. Petitioner's annotated versions of Figures 18B, 19A, and 19B of Aoyama (Pet. 36) are reproduced below.

Figure 18B is a cross-sectional view of an intermediate structure formed at a process step for forming a through-hole according to an embodiment of Aoyama. Ex. 1018, 8:42–45. Figures 19A and 19B are plan views of the embodiment of Figure 18B. *Id.* at 8:46–48. As is highlighted in Petitioner's annotated figures, opening 49 in resist pattern 47 for forming through-hole 50 is wider than the wiring groove 48. *Id.* at 16:3–8, Figs. 18B, 19A.

According to Aoyama, this allows the through-hole to be formed having the same width as the wiring groove, even if resist pattern 47 is misaligned. *Id.* at 16:14–16, Fig. 19B.

## 2. <u>Whether the Grill/Aoyama Combination Teaches all</u> <u>Limitations of the Challenged Claims</u>

Claim 13 recites a "method for forming an interconnection structure." Grill is titled "Dual Damascene Processing for Semiconductor Chip Interconnects," and discloses "methods to fabricat[e] multilevel interconnect structures in semiconductor chips by a Dual Damascene process in which dual relief cavities formed in a dielectric are filled with conductive material to form the wiring and via levels." Pet. 37 (citing Ex. 1005, at [54], [57]); *id.* at 57. The following table provides a basic summary of Petitioner's mapping of the combination of Grill and Aoyama to the physical elements of claim 13.

| Claim 13                  | Grill & Aoyama                                                                                                 |

|---------------------------|----------------------------------------------------------------------------------------------------------------|

| lower-level interconnects | conductive via 4 of Grill                                                                                      |

| first insulating film     | dielectric etch stop layer 10 of Grill                                                                         |

| second insulating film    | wiring level dielectric 12 of Grill                                                                            |

| third insulating film     | lower hard mask layer 56 of Grill                                                                              |

| thin film                 | upper hard mask layer 58 of Grill                                                                              |

| mask pattern              | patterned upper hard layer 58 of Grill                                                                         |

| first resist pattern      | patterned first resist layer 60 of Grill                                                                       |