\_\_\_\_\_Case 2:00-cv-06756-B-CT

ORIGINA

Document 1 Filed 06/22/00 Page 1 of 76 Page ID #:929

GLENN W. TROST (State Bar No. 116203) 1 **COUDERT BROTHERS** 333 South Hope Street, 23rd Floor 2 Los Angeles, California 90071 tel: (213) 229-2900 3 fax: (213) 229-2999 4 DAVID E. KILLOUGH (SBN 110719) **O'MELVENY & MYERS LLP** 5 275 Battery Street San Francisco, California 94111-3305 6 tel: (415) 984-8700 7 fax: (415) 984-8701 SAMUEL H. WEINER 8 OSTROLENK, FABER, GERB & SOFFEN 1180 Avenue of the Americas 9 New York, NY 10036 tel: (212) 382-0700 10 fax: (212) 382-0888 11 Attorneys for Plaintiff International Rectifier Corporation 22 12 2 13 **UNITED STATES DISTRICT COURT** 14 **CENTRAL DISTRICT OF CALIFORNIA** 15 MMM(BQRx) 16 Case Non-067 **INTERNATIONAL RECTIFIER** 17 CORPORATION, **COMPLAINT FOR DAMAGES AND** 18 PLAINTIFF, **INJUNCTIVE RELIEF (PATENT INFRINGEMENT); DEMAND FOR JURY** 19 TRIAL VS. 20 ENTERED ON ICMS **IXYS CORPORATION, AND DOES 1-10,** 21 **DEFENDANTS.** JUN: 2 7 2000 22 23 C٧ 24 For its Complaint, plaintiff International Rectifier Corporation ("IR") avers as 25 follows: 26 27 28 Complaint

۰. ۲

×.,

· · ·

· · ·

La Sout

OBERAT

· · ·

.

06/22/00 LA 4-2 SIN Receipt # 061902 CASE # 00-6756 086900 Filing Fae Civil 510000 Special Fund F/F 90.00

CHECK TENDERED \$ \$150.00

se 2:00-cv-06756-R\_CT Document 1 Filed 06/22/00 Page 3 of 76 Page ID #:931

### **JURISDICTION AND VENUE**

1. The claims alleged below are brought under the Patent Laws of the United States, 35 U.S.C. §§ 1 et seq. This Court has jurisdiction over these claims pursuant to 28 U.S.C. §§ 1338(a). Venue is based on 28 U.S.C. §§ 1391(b), 1391(c), 1391(d) and 1400(b).

### PARTIES

2. IR is a corporation duly organized and existing under the laws of the State of 9 Delaware, with its corporate headquarters and principal place of business within the Central 10 District of California at 233 Kansas Street, El Segundo, California 90245.

12

17

11

. • \_

1

2

3

4

5

6

7

8

3. IR is informed and believes, and on that basis alleges, that defendant IXYS 13 Corporation ("IXYS") is a corporation organized under the laws of the State of Delaware, 14 doing business in this District, *inter alia*, through its Sales Representative, Select 15 Electronics, in Santa Ana, California. 16

4. The true names and/or culpabilities of defendant DOES 1-10 are unknown to IR 18 at this time. IR is informed and believes, and on that basis alleges, that DOES 1-10, as 19 more fully alleged below, as well as the other defendants, are legally responsible for the 20 occurrences, acts and wrongs alleged herein and for the damages to IR proximately caused 21 thereby. In particular, IR is informed and believes, and on that basis alleges, that IXYS<sup>5</sup> 22 relies on sales representatives and distributors, including DOES 1-10, to sell devices in this 23 District and elsewhere within the United States, where such devices practice one or more of 24 the claims (or are made by one or more of the claimed processes) of the patents identified 25 below. Such sales are direct infringements of the patents in suit. IR will amend this 26 Complaint to correctly identify any DOE defendant whose identity and culpability is made 27 known to IR. 28

> 2 Complaint

.4

1

2

3

4

5

6

7

8

9

### **FIRST CLAIM FOR RELIEF**

### (Against All Defendants For Patent Infringement, U.S. Patent No. 4,959,699)

5. IR is and has been the owner by mesne assignment of United States Letters Patent No. 4,959,699 (the "'699 patent"), which issued September 25, 1990 (Reexamination Certificates issued October 12, 1993 and January 19, 1999), for HIGH POWER MOSFET WITH LOW ON-RESISTANCE AND HIGH BREAKDOWN VOLTAGE. A copy of the '699 patent, together with its reexamination certificates, is attached hereto as Exhibit A.

6. IR is informed and believes, and on that basis alleges, that (a) IXYS has made, 10 used, sold or offered for sale in this District and elsewhere in the United States articles 11 (including, but not necessarily limited to, part numbers IXFX55N50, IXFH21N50, 12 IXFH35N30, and IXTH24N50) infringing the '699 patent (including, but not limited to, 13 Claim 1 of the '699 patent) and (b) DOES 1-10 have in this District and elsewhere in the 14 United States sold and offered for sale such articles. IR is further informed and believes, 15 and on that basis alleges, that this infringement will continue unless and until enjoined by 16 this Court. 17

18

19

20

21

23

24

25

26

27

28

7. IR has notified IXYS of its infringement, which has been and continues to be willful and deliberate. IR has been and continues to be damaged by the above-alleged infringement and will suffer irreparable harm until such time as that infringement is enjoined. 22

### **SECOND CLAIM FOR RELIEF**

## (Against All Defendants For Patent Infringement, U.S. Patent No. 5,008,725)

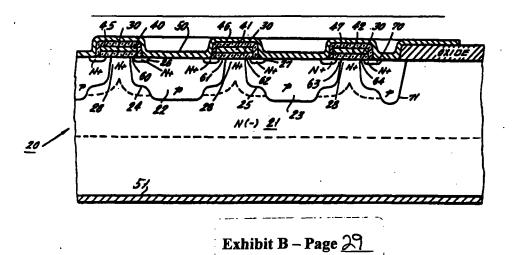

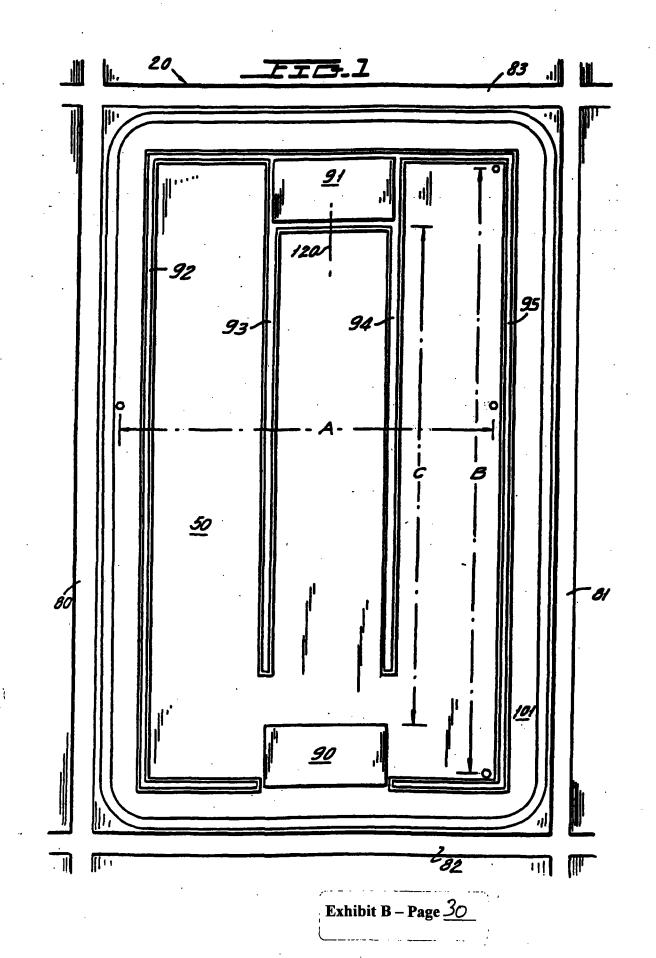

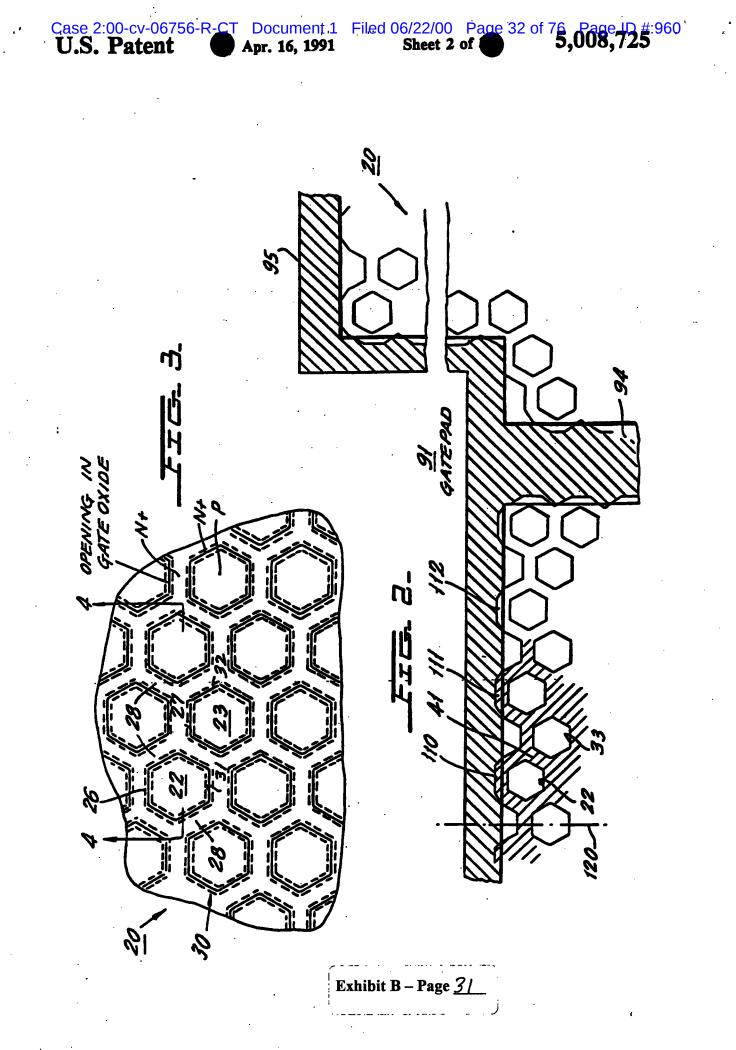

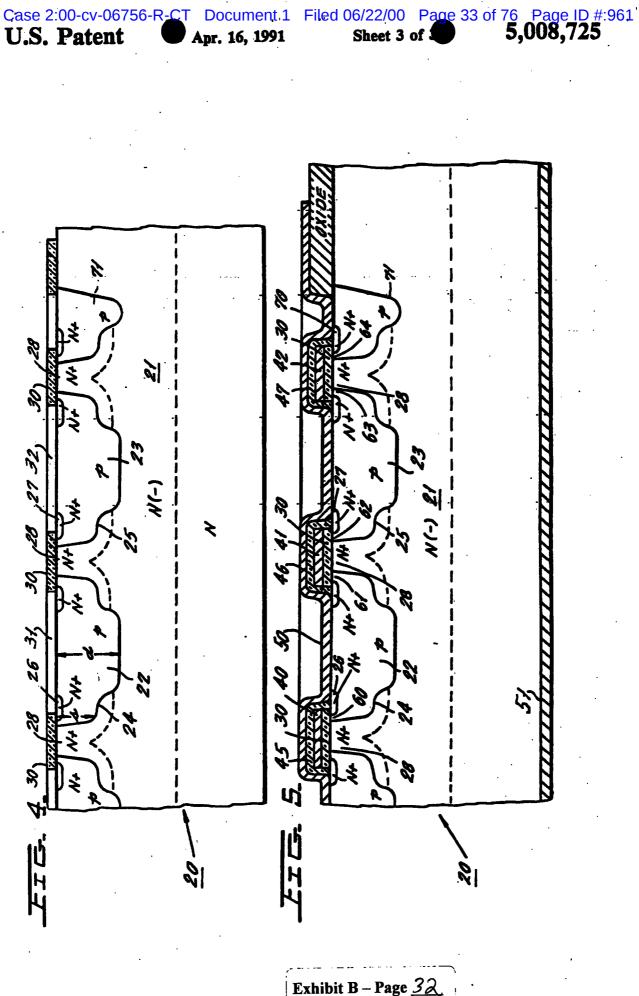

8. IR is and has been the owner by mesne assignment of United States Letters Patent No. 5,008,725 (the "'725 patent") which issued April 16, 1991 (Reexamination Gase 2:00-cv-06756-R-CT Document 1 Filed 06/22/00 Page 5 of 76 Page ID #:933 '

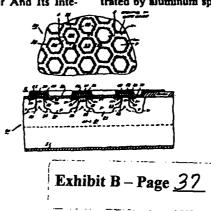

certificate issued January 12, 1993), for PLURAL POLYGON SOURCE PATTERN FOR 1 2 MOSFET. A copy of the '725 patent, together with its reexamination certificate, is attached hereto as Exhibit B. 3

4

9. IR is informed and believes, and on that basis alleges, that (a) IXYS has made, 5 used, sold or offered for sale in this District and elsewhere in the United States articles 6 (including, but not necessarily limited to, part numbers IXFX55N50, IXFH21N50, 7 IXFH35N30, and IXTH24N50) infringing the '725 patent (including, but not limited to, 8 Claims 3, 7 and 8 of the '725 patent) and (b) DOES 1-10 have in this District and elsewhere 9 in the United States sold and offered for sale such articles. IR is further informed and 10 believes, and on that basis alleges, that this infringement will continue unless and until 11 enjoined by this Court. 12

13

18

19

20

21

22

23

24

25

26

27

28

10. IR has notified IXYS of its infringement, which has been and continues to be 14 willful and deliberate. IR has been and continues to be damaged by the above-alleged 15 infringement and will suffer irreparable harm until such time as that infringement is 16 enjoined. 17

### **THIRD CLAIM FOR RELIEF**

(Against All Defendants For Patent Infringement, U.S. Patent No. 5,130,767)

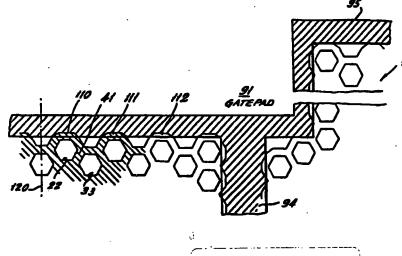

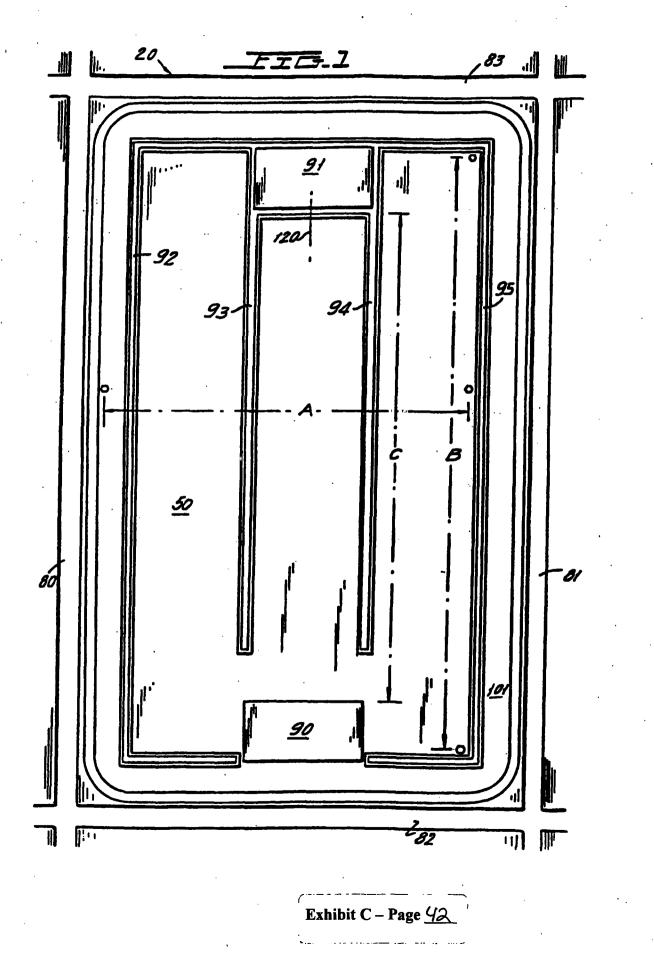

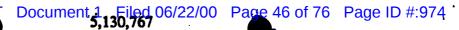

11. IR is and has been the owner by mesne assignment of United States Letters Patent No. 5,130,767 (the "'767 patent"), which issued July 14, 1992, for PLURAL POLYGON SOURCE PATTERN FOR MOSFET. A copy of the '767 patent is attached hereto as Exhibit C.

12. IR is informed and believes, and on that basis alleges, that (a) IXYS has made, used, sold or offered for sale in this District and elsewhere in the United States articles

se 2:00-cv-06756-R<u>-C</u>T Document 1 Filed 06/22/00 Page 6 of 76 Page ID #:934 ;

(including, but not necessarily limited to, part numbers IXFX55N50, IXFH21N50,

IXFH35N30, and IXTH24N50) infringing the '767 patent (including, but not limited to,

Claims 3, 5 and 7 of the '767 patent) and (b) DOES 1-10 have in this District and elsewhere

in the United States sold and offered for sale such articles. IR is further informed and

believes, and on that basis alleges, that this infringement will continue unless and until

enjoined by this Court.

13. IR has notified IXYS of its infringement, which has been and continues to be willful and deliberate. IR has been and continues to be damaged by the above-alleged infringement and will suffer irreparable harm until such time as that infringement is enjoined.

### FOURTH CLAIM FOR RELIEF

### (Against All Defendants For Patent Infringement, U.S. Patent No. 4,642,666)

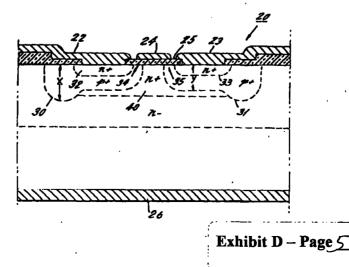

14. IR is and has been the owner by mesne assignment of United States Letters Patent No. 4,642,666 (the "'666 patent"), which issued February 10, 1987 (Reexamination Certificate issued October 27, 1998), for HIGH POWER MOSFET WITH LOW ON-RESISTANCE AND HIGH BREAKDOWN VOLTAGE. A copy of the '666 patent, together with its reexamination certificate, is attached hereto as Exhibit D.

15. IR is informed and believes, and on that basis alleges, that (a) IXYS has made, used, sold or offered for sale in this District and elsewhere in the United States articles (including, but not necessarily limited to, part numbers IXFX55N50, IXFH21N50, IXFH35N30, and IXTH24N50) infringing the '666 patent (including, but not limited to, Claim 1 of the '666 patent) and (b) DOES 1-10 have in this District and elsewhere in the United States sold and offered for sale such articles.

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

5 Complaint

16. IR notified IXYS of its infringement, which was willful and deliberate. IR has been damaged by the above-alleged infringement.

### **FIFTH CLAIM FOR RELIEF**

### (Against All Defendants For Patent Infringement, U.S. Patent No. 4,705,759)

17. IR is and has been the owner by mesne assignment of United States Letters Patent No. 4,705,759 (the "'759 patent"), which issued November 10, 1987, (Reexamination Certificate issued February 14, 1995), for HIGH POWER MOSFET WITH LOW ON-RESISTANCE AND HIGH BREAKDOWN VOLTAGE. A copy of the '759 patent, together with its reexamination certificate, is attached hereto as Exhibit E.

18. IR is informed and believes, and on that basis alleges, that (a) IXYS has made, used, sold or offered for sale in this District and elsewhere in the United States articles (including, but not necessarily limited to, part numbers IXFX55N50, IXFH21N50, IXFH35N30, and IXTH24N50) infringing the '759 patent (including, but not limited to, Claim 1 of the '759 patent) and (b) DOES 1-10 have in this District and elsewhere in the United States sold and offered for sale such articles. IR is further informed and believes, and on that basis alleges, that this infringement will continue unless and until enjoined by this Court.

19. IR has notified IXYS of its infringement, which has been and continues to be willful and deliberate. IR has been and continues to be damaged by the above-alleged infringement and will suffer irreparable harm until such time as that infringement is enjoined.

Wherefore, International Rectifier prays for judgment as follows:

26

27

28

1

2

3

4

5

6

7

8

**ب**

| 1  | 1.            | For a preliminary and permanent injunction against infringement of the '699   |

|----|---------------|-------------------------------------------------------------------------------|

| 2  | patent;       |                                                                               |

| 3  |               |                                                                               |

| 4  | 2.            | For an award of actual damages sustained by IR (but no less than a reasonable |

| 5  | royalty) as a | result of infringement of the '699 patent;                                    |

| 6  |               |                                                                               |

| 7  | 3.            | For a preliminary and permanent injunction against infringement of the '725   |

| 8  | patent;       |                                                                               |

| 9  |               |                                                                               |

| 10 | 4.            | For an award of actual damages sustained by IR (but no less than a reasonable |

| 11 | royalty) as a | result of infringement of the '725 patent;                                    |

| 12 |               |                                                                               |

| 13 | 5.            | For a preliminary and permanent injunction against infringement of the '767   |

| 14 | patent;       |                                                                               |

| 15 |               |                                                                               |

| 16 | 6.            | For an award of actual damages sustained by IR (but no less than a reasonable |

| 17 | royalty) as a | result of infringement of the '767 patent;                                    |

| 18 |               |                                                                               |

| 19 | 7.            | For an award of actual damages sustained by IR (but no less than a reasonable |

| 20 | royalty) as a | result of infringement of the '666 patent;                                    |

| 21 |               |                                                                               |

| 22 | 8.            | For a preliminary and permanent injunction against infringement of the '759   |

| 23 | patent;       |                                                                               |

| 24 |               |                                                                               |

| 25 | 9.            | For an award of actual damages sustained by IR (but no less than a reasonable |

| 26 | royalty) as a | result of infringement of the '759 patent;                                    |

| 27 |               |                                                                               |

| 28 | 10.           | For treble damages under 35 U.S.C. § 285;                                     |

|    | I             | i i i i i i i i i i i i i i i i i i i                                         |

|    |               | . 7                                                                           |

| Ģa       | se 2:00- | cv-06   | 756-R-CT     | Docume    | ent 1   | Filed 06/22/00 Page 9 of 76 Page ID #:937              |

|----------|----------|---------|--------------|-----------|---------|--------------------------------------------------------|

| 1        |          | 11.     | For IR's a   | attorneys | fees ar | nd costs incurred in prosecution of this action under, |

| 2        | inter al | lia, 35 | 5 U.S.C. § 2 | 285; and  |         | · · ·                                                  |

| 3        |          |         |              |           |         |                                                        |

| 4        |          | 12.     | For such     | other and | furthe  | r relief as this Court may deem just and proper.       |

| 5        | -        |         |              |           |         |                                                        |

| 6        | Dated:   | June    | e 22, 2000   |           | COU     | JDERT BROTHERS                                         |

| 7        |          |         |              |           | 0'М     | ELVENY & MYERS LLP                                     |

| 8        |          |         | ·            |           | OST     | ROLENK, FABER, GERB & SOFFEN                           |

| 9        |          |         |              |           |         | $n \sim 0$                                             |

| 10       |          |         |              |           | By:     | Ollin W. Turt                                          |

| 11       |          |         |              |           |         | Attorneys for Plaintiff International Rectifier        |

| 12       |          |         |              |           |         | Corporation                                            |

| 13       |          |         |              |           |         | · ·                                                    |

| 14       |          |         |              |           |         |                                                        |

| 15       |          |         |              |           |         |                                                        |

| 16       |          |         |              |           | •       |                                                        |

| 17       |          |         | . •          |           |         |                                                        |

| 18       |          |         |              |           |         |                                                        |

| 19<br>20 |          |         |              |           |         |                                                        |

| 20       |          |         |              |           |         |                                                        |

| 22       |          |         |              |           |         |                                                        |

| 23       |          |         |              |           |         |                                                        |

| 24       |          |         |              |           | ·       | · ·                                                    |

| 25       |          |         |              |           |         |                                                        |

| 26       |          |         |              |           | •       |                                                        |

| 27       |          |         |              |           |         |                                                        |

| 28       |          |         |              |           |         |                                                        |

|          |          |         |              |           |         |                                                        |

|          |          |         |              |           |         | 8<br>Complaint                                         |

| i,       |          |         |              |           |         |                                                        |

, i

| Ca         | se 2:00-c | xv-06756-R-CT     | Docume     | nț.1 F     | iled 06/22/00 Page   | 10 of 76 Page      | ID #:938  |

|------------|-----------|-------------------|------------|------------|----------------------|--------------------|-----------|

| 1          |           | •                 |            | DEM/       | AND FOR JURY T       | RIAL               |           |

| 2          |           |                   |            |            |                      |                    |           |

| 3          |           | Plaintiff Interna | tional Rec | tifier (   | Corporation hereby d | lemands trial by j | ury.      |

| 4          |           |                   |            |            | •                    |                    |           |

| 5          | Dated:    | June 22, 2000     |            | COU        | DERT BROTHERS        |                    |           |

| 6          |           |                   |            | <b>O'M</b> | ELVENY & MYERS       | S LLP              |           |

| 7          |           |                   |            | OST        | ROLENK, FABER, (     | GERB & SOFFE       | N         |

| · 8        |           |                   | •          |            |                      |                    |           |

| 9          |           |                   |            | By:        | Olern U              | U. Tur             |           |

| 10         |           |                   |            |            | Attorneys for Plain  | tiff International | Rectifier |

| 11         |           |                   |            |            | Corporation          |                    |           |

| 12         |           |                   |            |            |                      |                    |           |

| 13         |           |                   |            |            |                      |                    |           |

| 14         |           |                   |            |            |                      |                    |           |

| 15         |           | · .               |            |            |                      |                    |           |

| 16         |           |                   |            |            |                      |                    |           |

| 17         |           |                   |            |            |                      |                    |           |

| 18         |           |                   |            |            |                      | •                  |           |

| 19         |           |                   |            | ·          |                      |                    |           |

| 20         |           |                   |            |            |                      |                    |           |

| 21         |           |                   |            |            |                      |                    |           |

| 22         |           |                   |            |            |                      |                    |           |

| 23<br>· 24 |           |                   |            |            |                      |                    |           |

| 24<br>25   |           | •                 |            |            |                      |                    |           |

| 25         |           |                   |            |            |                      |                    |           |

| 20         |           | • •               |            |            |                      |                    |           |

| 27<br>28   |           |                   |            |            |                      |                    |           |

| 20         |           |                   |            |            |                      | ,                  |           |

|            |           |                   |            |            | 9<br>Complaint       |                    |           |

, **1**

# United States Part [19] Filed 06/22/00 Page 11 of 764,959,699 #:939

### Lidow et al.

### [54] HIGH POWER MOSFET WITH LOW ON-RESISTANCE AND HIGH BREAKDOWN VOLTAGE

- [75] Inventors: Alexander Lidow, Manhattan Beach; Thomas Herman, Redondo Beach, both of Calif.

- [73] Assignee: International Rectifier Corporation, El Segundo, Calif.

- [21] Appl. No.: 371,678

- [22] Filed: Jun. 22, 1989

### **Related U.S. Application Data**

- [60] Continuation of Ser. No. 90,664, Aug. 27, 1987, abandoned, which is a division of Ser. No. 456,813, Jan. 10, 1983, abandoned, which is a division of Ser. No. 232,713, Feb. 9, 1981, Pat. No. 4,376,286, which is a continuation of Ser. No. 951,310, Oct. 13, 1978, abandoned.

- [51] Int. CL<sup>5</sup> ..... H01L 29/68; H01L 29/10; H01L 27/02

- [58] Field of Search ...... 357/23.7, 23.8, 23.4, 357/41, 43, 86

### [56] References Cited

### U.S. PATENT DOCUMENTS

| 3,271,640          | 9/1966    | Moore .              |

|--------------------|-----------|----------------------|

| 3,319,311          | 5/1967    | Mutter .             |

| 3,458,781          | 7/1969    | Simon .              |

| 3 <b>,461,36</b> 0 | 8/1969    | Barson et al.        |

| (1                 | List cont | inued on next page.) |

### FOREIGN PATENT DOCUMENTS

| 2136509 11/1972  | Fed. Rep. of Germany . |

|------------------|------------------------|

| 5046081 8/1973   | Japan .                |

| 48-40814 12/1973 | Japan .                |

| 51-85381 7/1976  | Japan .                |

| 52-23277 2/1977  | Japan .                |

| 52-42080 4/1977  | Japan                  |

| 52-106688 9/1977 |                        |

|                  | •                      |

(List continued on next page.)

## [45] Date of Patent: Sep. 25, 1990

### OTHER PUBLICATIONS

I. Yoshida et al., "A High Power MOSFET with a Vertical Drain Electrode and a Meshed Gate Structure," IEEE Journal of Solid-State Circuits, vol. SC-11 #4, Aug. 1976, pp. 472-477.

J. Plummer et al., "A Monolithic 200-V CMOS Analog Switch," IEEE Journal of Solid-State Circuits, vol. SC-11 #6, Dec. 1976, pp. 809-817.

B. Scharf et al., "A MOS-Controlled Triac Device," 1978 IEEE International Solid-State Circuits Conference, San Francisco, Calif., Feb. 15-17, 1978, pp. 222-223.

K. Lisiak et al., "Optimization of Non-Planar Power MOS Transistors," IEEE Transactions on Electron Devices, vol. Ed-25 #10, Oct. 1978, pp. 1229-1234.

H. Sigg et al., "D-MOS Transistor for Microwave (List continued on next page.)

Primary Examiner—Rolf Hille

[57]

Assistant Examiner—Fetsum Abraham Attorney, Agent, or Firm—Ostrolenk, Faber, Gerb & Soffen

#### ABSTRACT

A high power MOSFET is disclosed in which two laterally spaced sources each supply current through respective channels in one surface of a semiconductor chip which are controlled by the same gate. The channels lead from the source electrodes to a relatively low resistivity region and from there to a relatively high resistivity epitaxially formed region which is deposited on a high conductivity substrate. The drain electrode may be either on the opposite surface of the chip or laterally displaced from and on the same side as the source regions. The epitaxially deposited semiconductor material immediately adjacent and beneath the gate and in the path from the sources to the drain has a relatively high conductivity, thereby to substantially reduce the on-resistance of the device without effecting the breakdown voltage of the device. The breakdown voltage of the device is substantially increased by forming a relatively deep p-type diffusion with a large radius in the n-type epitaxial layer beneath each of the sources.

### 24 Claims, 5 Drawing Sheets

Exhibit A – Page 10

連

Case 2:00-cv-06756-R-CT Document 1 Filed 06/22/00 Page 12 of 76 Page ID #:940 U.S. Patent Sep. 25, 1990 Sheet 1 of 4.959\_699

4,959,699

Exhibit A – Page 11

Case 2:00-cv-06756-R-CT Document 1 Filed 06/22/00 Page 13 of 76 Page ID #:941

U.S. Patent Sep. 25, 1990

Sheet 2 of 🗩

4,959,699

FF E 3\_ 53 51 50 54. 52 Ż 20 72+

Case 2:00-cv-06756-R-CT Document 1 Filed 06/22/00 Page 14 of 76 Page ID #:942 U.S. Patent Sep. 25, 1990 Sheet 3 of 5 4,959,699

Sheet 3 of 5

4,959,699

Exhibit A – Page 13

Exhibit A – Page <u>14</u>

Case 2:00-cv-06756-R-CI Document 1 Filed 06/22/00 Page 16 of 76 Page ID #:944

U.S. Patent Sep. 25, 1990

Sheet 5 of 9

4,959,699

FORWARD VOLTAGE (VOLTS)

5

### HIGH POWER MOSFET WITH LOW **ON-RESISTANCE AND HIGH BREAKDOWN** VOLTAGE.

This is a continuation of application Ser. No. 07/090.664 filed on Aug. 27, 1987, now abandoned, which is a division of application Ser. No. 456.813, filed Jan. 10, 1983 now abandoned which in turn, is a division of application Ser. No. 232,713, filed Feb. 9, 1981, now 10 U.S. Pat. No. 4,376,286, issued Mar. 8, 1983 which, in turn, is a continuation of application Ser. No. 951,310, filed Oct. 13, 1978, now abandoned.

### BACKGROUND OF THE INVENTION

This invention relates to MOSFET devices and more specifically relates to a novel structure for a MOSFET device which permits it to be used in high power applications with a relatively high reverse voltage and with an exceptionally low on-resistance. The major advan- 20 tage of the bipolar transistor over the MOSFET transistor is that the bipolar transistor has a very low on-resistance per unit conductive area. The MOSFET transistor has numerous advantages over the bipolar transistor including very high switching speed, very high gain and 25 lack of the secondary breakdown characteristics exhibited by a minority carrier device. However, because the MOSFET transistor has high on-resistance, its use in high power switching applications has been limited.

### BRIEF DESCRIPTION OF THE INVENTION

The present invention provides a novel high power MOSFET device which has a low forward resistance so that the device becomes more competitive with bipolar devices in a switching type application while retaining 35 all of the numerous advantages of the MOSFET over the bipolar device. In particular, with the present invention, the forward resistance per unit area of the device has been reduced by at least a factor of two, compared to the limiting resistance per unit area previously exist- 40 ing in a MOSFET-type device.

In one embodiment of the invention, two sources are placed on the same surface of a semiconductor wafer and are laterally spaced from one another. A gate electrode, deposited on a conventional gate oxide, is dis- 45 posed between the sources. Two p-type conduction channels are disposed beneath the gate and are spaced from one another by an n-type bulk region. Current from each source can flow through its respective channel (after the creation of the inversion layer defining the 50 channel), so that majority carrier conduction current can flow through the bulk region and across the wafer or chip to the drain electrode. The drain electrode may be on the opposite surface of the wafer or on a laterally displaced surface region from the source electrodes. 55 This configuration is made using the desirable manufacturing techniques of the D-MOS device, which permits precise alignment of the various electrodes and channels and permits use of extremely small channel lengths. While the above configuration may have been previ- 60 p(+) conductivity implant and diffusion step. ously described for a MOSFET signal-type device, the structure is not that of the commonly used signal MOS-FET.

The device is basically formed in an n(-) substrate which has the relatively high resistivity which is neces- 65 channel implant and diffusion step. sary to obtain the desired reverse voltage capability of the device. For example, for a 400 volt device, the n(-)region will have a resistivity of about 20 ohm-centime-

ters. However, this same necessary high resistivity characteristic has caused the on-resistance of the MOSFET device, when used as a power switch, to be relatively high.

In accordance with the present invention, it has been found that in the upper portion of the central bulk region to which the two inversion layers feed current in the path to the drain electrode, the central region immediately beneath the gate oxide can be a relatively low resistivity material formed, for example, by an n(+)diffusion in that channel region, without affecting the reverse voltage characteristics of the device.

More specifically, and in accordance with the invention, this common channel will have an upper portion 15 beneath the gate oxide and a lower bulk portion extending toward the drain electrode. The lower portion has the high resistivity desired to produce high reverse voltage ability, and will have a depth dependent on the desired reverse voltage for the device. Thus, for a 400 volt device, the lower n(-) region may have a depth of about 35 microns, while for a 90 volt device it will have a depth of about 8 microns. Other depths will be selected, depending on the desired reverse voltage of the device to provide the necessary thicker depletion region required to prevent punch-through during reverse voltage conditions. The upper portion of the common channel is made highly conductive (n+) to a depth of from about 3 to about 6 microns. It has been found that this does not interfere with the reverse voltage with-30 stand ability of the device. However, it decreases the on-resistance per unit area of the device by more than a factor of two. The resulting device becomes competitive with conventional high power bipolar switching devices since it retains all of the advantages of the MOSFET device over the bipolar device but now has the relatively low forward resistance which was the major characterizing advantage of the bipolar device.

In accordance with another feature of the present invention, the p-type region which defines the channel beneath the gate oxide has a relatively deeply diffused portion beneath the source so that the p-type diffusion region will have a large radius of curvature in the n(-)epitaxial layer forming the body of the device. This deeper diffusion or deeper junction has been found to improve the voltage gradient at the edge of the device and thus permits the use of the device with higher reverse voltages.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

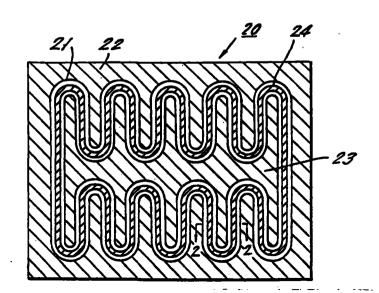

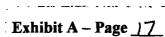

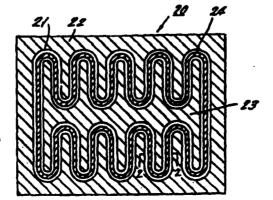

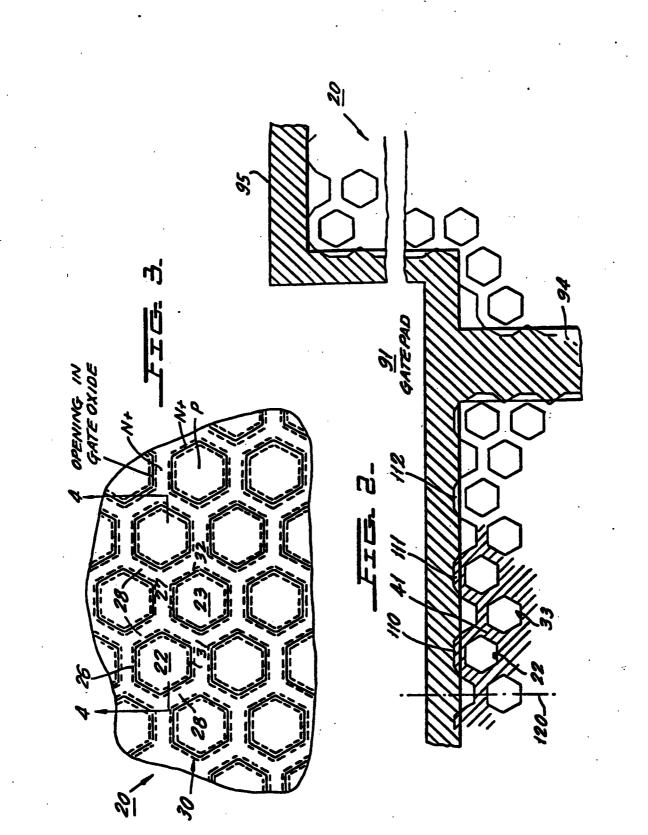

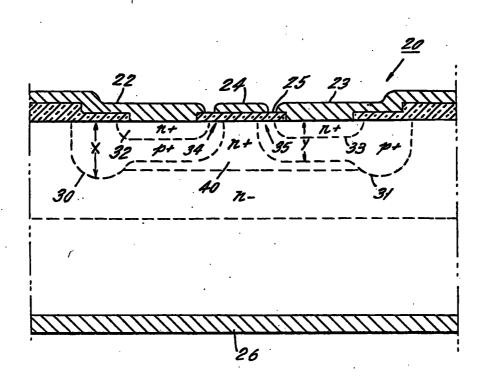

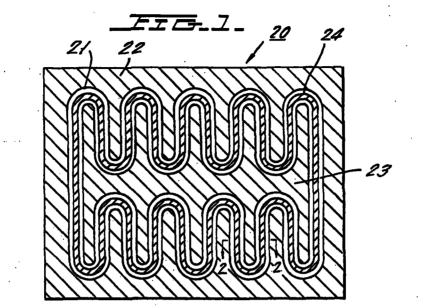

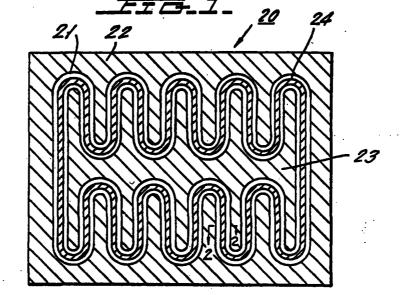

FIG. 1 is a plan view of a high power MOSFET chip which incorporates the present invention and particularly illustrates the metalizing patterns of the two sources and the gate.

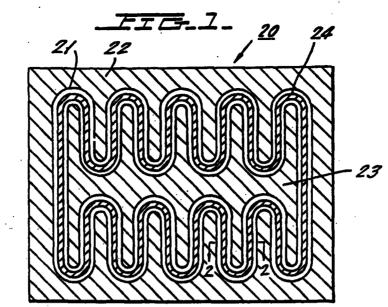

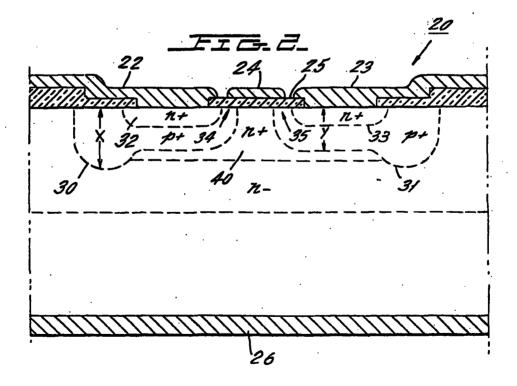

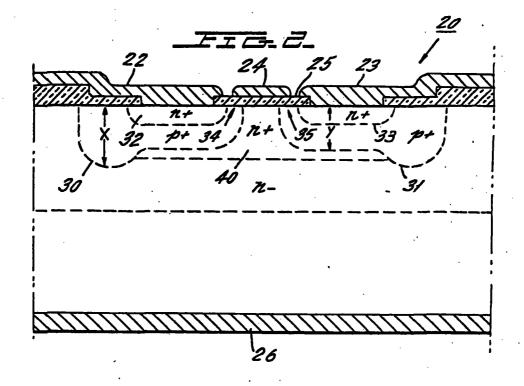

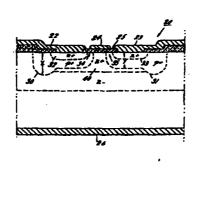

FIG. 2 is a cross-sectional view of FIG. 1 taken across the section line 2-2 in FIG. 1.

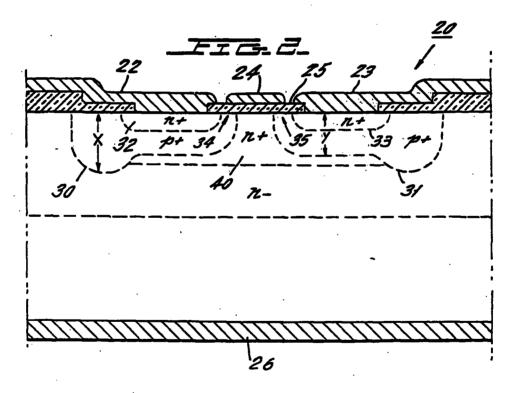

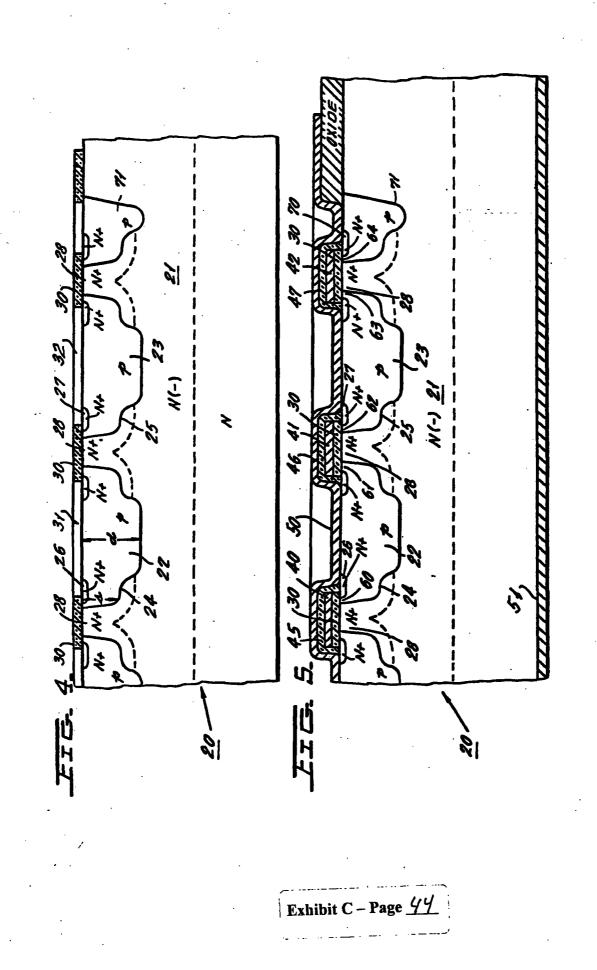

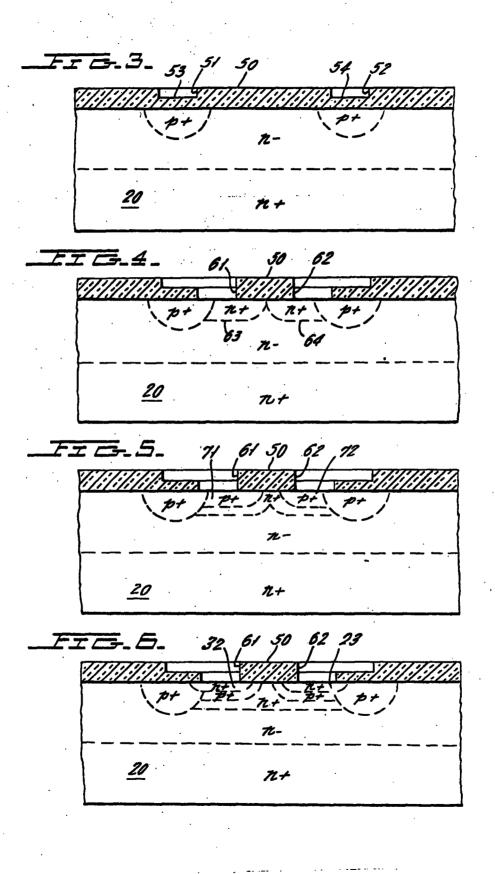

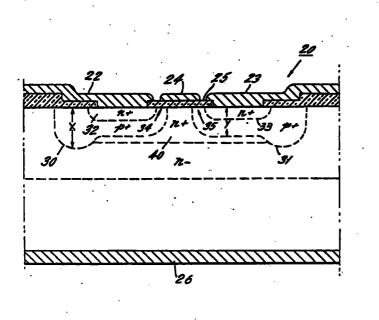

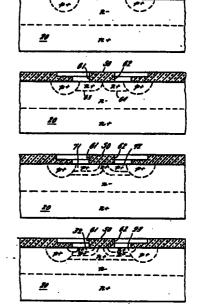

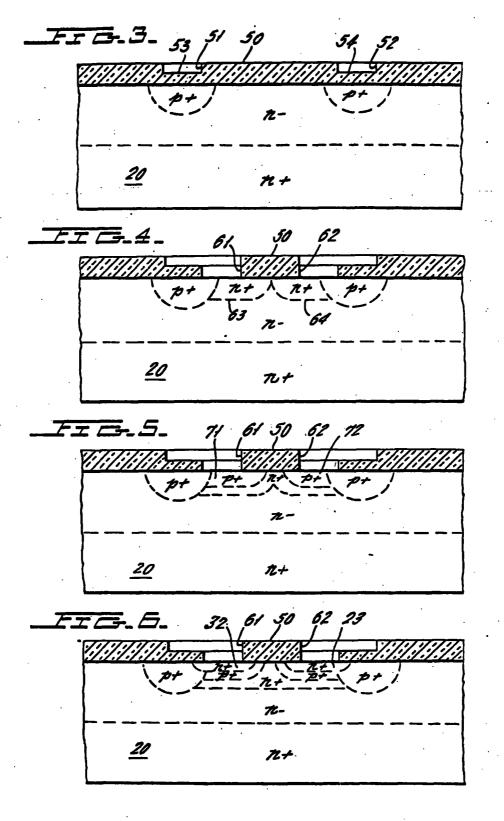

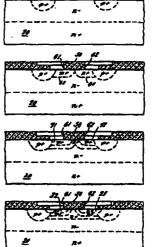

FIG. 3 is a cross-sectional view similar to FIG. 2 showing the initial step in the process of manufacture of the chip of FIGS. 1 and 2 and particularly shows the

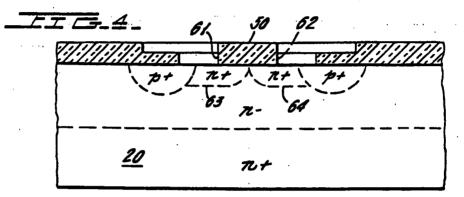

FIG. 4 shows the second step in the manufacturing process and shows the n(+) implant and diffusion step.

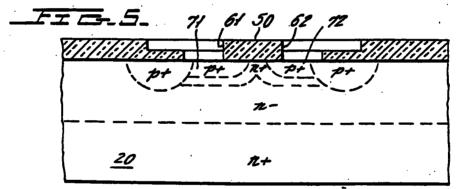

FIG. 5 shows a further step in the process of manufacture of the chip of FIGS. 1 and 2 and shows the

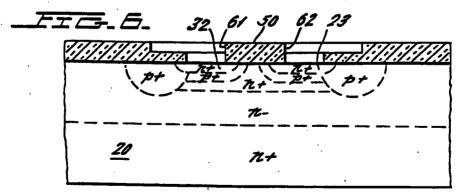

FIG. 6 shows a further step in the process of manufacture and illustrates the source predeposition and diffusion step. This precedes the last step in which the

Exhibit A – Page 16

3 gate oxide is cut for the metalization step which produces the device of FIG. 2.

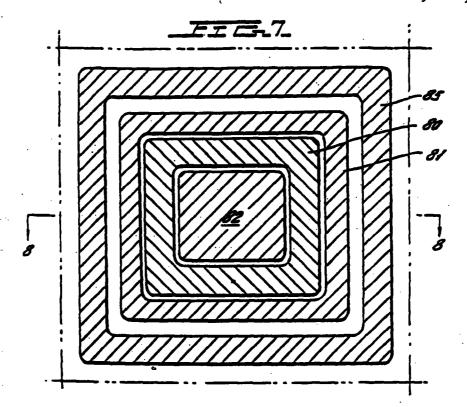

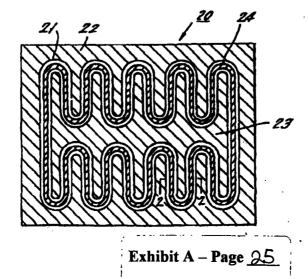

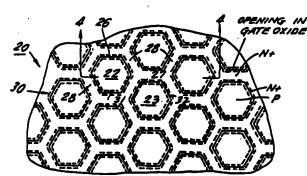

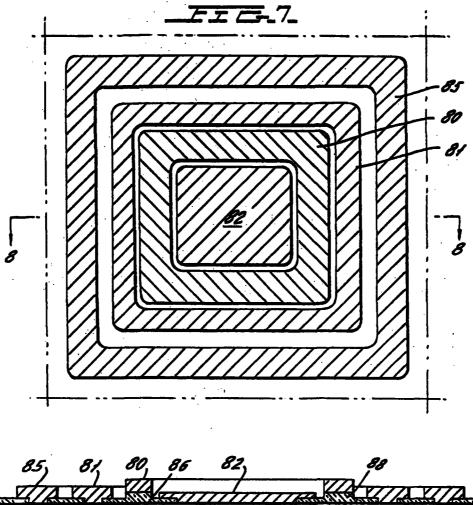

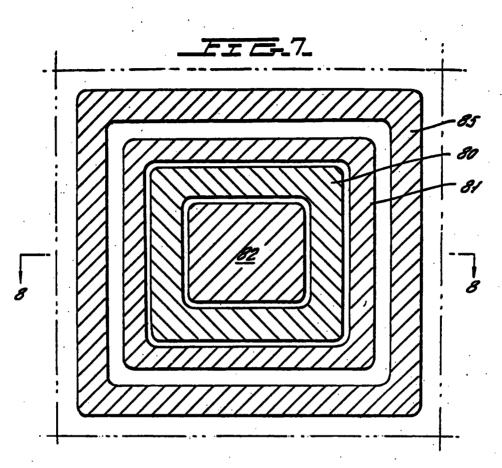

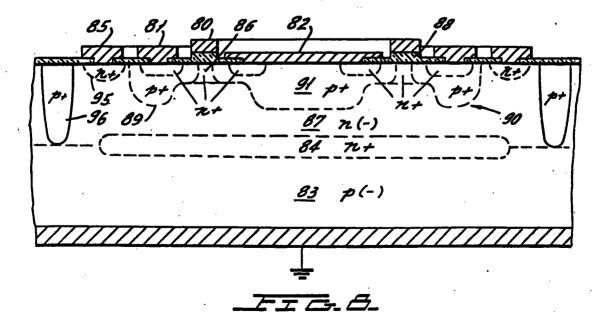

FIG. 7 is a plan view of the metalizing pattern of a second embodiment of the invention.

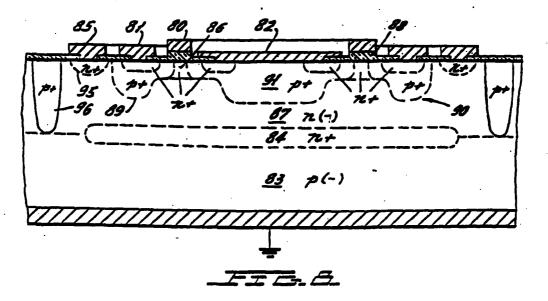

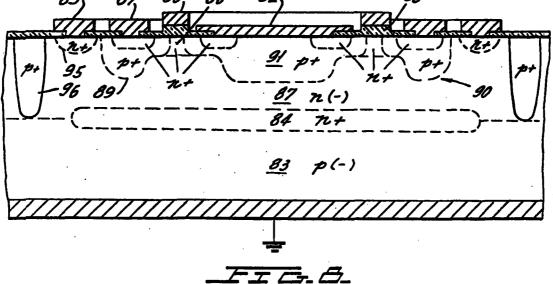

FIG. 8 is a cross-sectional view of FIG. 7 taken 5 across the section line 8-8 in FIG. 7.

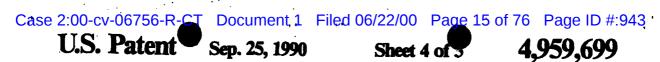

FIG. 8a is a view similar to FIG. 2 and shows a modified source contact configuration.

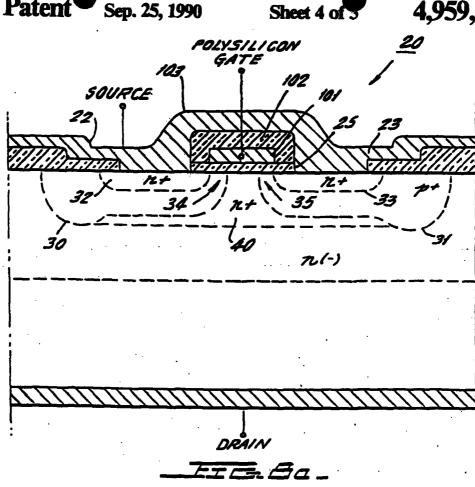

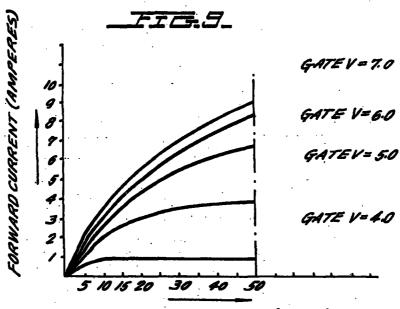

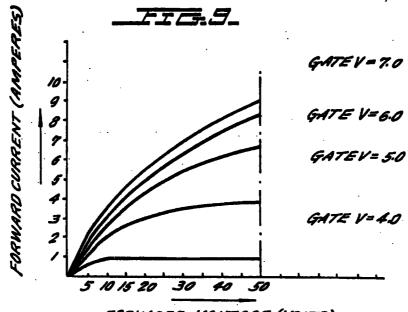

FIG. 9 shows the shape of forward-current characteristics of a device like that of FIG. 2 where the region 10 an elongated serpentine p(+) conductivity region be-40 beneath the oxide is n(-).

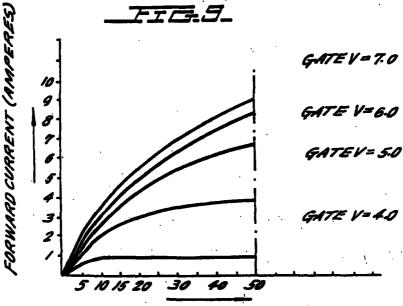

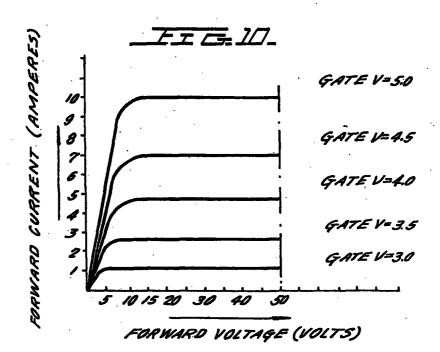

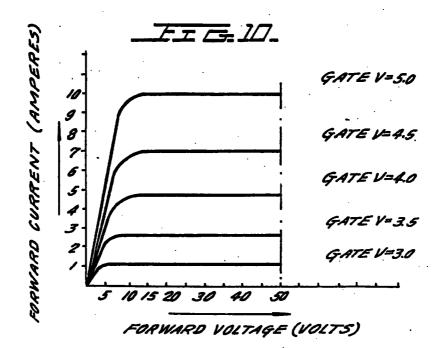

FIG. 10 shows the shape of the characteristic of a device identical to that of FIG. 2 where the region 40 has high n(+) conductivity.

### DETAILED DESCRIPTION OF THE DRAWINGS

A first embodiment of the novel MOSFET device of the present invention is shown in FIGS. 1 and 2 which show a chip of monocrystalline silicon 20 (or some 20 other suitable material), with the device electrodes following the serpentine path 21 best shown in FIG. 1 in order to increase the current-carrying area of the device. Other geometries could be used. The device illustrated has a reverse voltage of about 400 volts and an 25 on-resistance less than about 0.4 ohm with a channel width of 50 centimeters. Devices having reverse voltages of from 90 to 400 volts have been made. The 400 volt devices have carried pulse currents of 30 amperes. The 90 volt devices have had forward on-resistances of 30 about 0.1 ohm with a channel width of 50 centimeters and have carried pulse currents up to about 100 amperes. Higher and lower voltage devices can also be made with varying channel widths.

Presently known MOSFET devices have much 35 higher on-resistances than the above. For example, a 400 volt MOSFET comparable to that described below but made with prior art techniques would normally have an on-resistance much greater than about 1.5 ohms, as compared to an on-resistance less than about 40 0.4 ohm in a device made according to this invention. Moreover, the MOSFET switching device of the present invention will exhibit all of the desirable advantages of the MOSFET device, since it operates as a majority carrier device. These advantages include high switch- 45 ing speed, high gain and avoidance of the secondary breakdown characteristics which exist in minority carrier devices.

The device of FIGS. 1 and 2 has two source electrodes 22 and 23 which are separated by a metalized 50 gate electrode 24 which is fixed to but spaced from the semiconductor device surface by a silicon dioxide layer 25. The serpentine path followed by gate oxide 25 has a length of 50 centimeters and has 667 undulations, but is shown more simply in FIG. 1. Other channel widths 55 can be used. Source electrodes 22 and 23 can be laterally extended as shown to serve as field plates to help spread the depletion region created during reverse voltage conditions. Each of source electrodes 22 and 23 supply current to a common drain electrode 26 which is 60 fixed to the bottom of the wafer. The relative dimensions for the device, particularly in thickness, have been grossly exaggerated in FIG. 2 for purposes of clarity. The silicon chip or wafer 20 is formed on an n(+) substrate which may have a thickness of about 14 mils. An 65 n(-) epitaxial layer is deposited on substrate 20 and will have a thickness and resistivity depending on the desired reverse voltage. All junctions are formed in this

epitaxial layer which can have a relatively high resistivity. In the embodiment disclosed, the epitaxial layer has a thickness of about 35 microns and a resistivity of about 20 ohm-centimeters. For a 90 volt device, epitaxial layer 20 would be about 10 microns thick and would have a resistivity of about 2.5 ohm-centimeters. A channel width of 50 centimeters is also used to provide the desired current carrying capacity for the device.

In a preferred embodiment of the invention, there is neath each of the source electrodes 22 and 23 which thus extends around the serpentine path shown in FIG. 1. These p(+) regions are shown in FIG. 2 as the p(+)regions 30 and 31, respectively, and are similar to those 15 of the prior art except that the maximum p(+) region depth is greatly exaggerated in order to form a large radius of curvature. This allows the device to withstand higher reverse voltages. By way of example, the depth of regions 30 and 31 is preferably about 4 microns at the dimension X in FIG. 2 and about 3 microns at the dimension Y in FIG. 2.

By using D-MOS fabrication techniques, two n(+)regions 32 and 33 are formed beneath source electrodes 22 and 23, respectively, and define, with the p(+) regions 30 and 31, n-type channel regions 34 and 35, respectively. Channel regions 34 and 35 are disposed beneath the gate oxide 25 and can be inverted by the appropriate application of a biasing signal to the gate 24 in order to permit conduction from the source 22 and the source 23 through the inversion layers into the central region disposed beneath the gate 24 and then to the drain electrode 26. Channels 34 and 35 may each have a length of about 1 micron.

It has previously been thought necessary that the central n(-) region between channels 34 and 35 (and between p(+) regions 30 and 31) should have a high resistivity in order to permit the device to withstand high reverse voltages. However, the relatively high resistivity n(-) material is also a significant contributing factor to the high forward on-resistance of the device.

In accordance with the significant feature of the present invention, a significant portion of this central conducting region is made relatively highly conductive and consists of an n(+) region 40 disposed immediately beneath the gate oxide 25. The n(+) region 40 has a depth of about 4 microns and could range from about 3 microns to about 6 microns. While its exact conductivity is not known, and varies with depth, it is high relative to the n(-) region beneath it. More particularly, region 40 has a high conductivity which would be determined by a total ion implanted dose of from about  $1 \times 10^{12}$  to  $1 \times 10^{14}$  phosphorus atoms/cm<sup>2</sup> at 50 kV followed by a diffusion drive at from 1150° C. to 1250° C. for from 30 minutes to 240 minutes. It has been found that by making this region 40 relatively highly conductive n(+) material through a diffusion or other operation, the device characteristics are significantly improved and the forward on-resistance of the device is reduced by a factor greater than two. Moreover, it has been found that the provision of the high conductivity region 40 does not interfere with the reverse voltage characteristics of the device. Accordingly, by making the region beneath the gate oxide 25 and between channels 34 and 35 more highly conductive, the forward on-resistance of the ultimate high power switching device has been significantly reduced and the MOSFET device becomes far more competitive with an equiva-

lent junction-type device while still retaining all of the advantages of the MOSFET majority carrier operation.

In the above description of FIGS. 1 and 2, it has been assumed that the conduction channels 34 and 35 are of p(+) material and are, accordingly, inverted to an n- 5 type conductivity to provide a majority carrier conduction channel from sources 22 and 23 to the central region 40 upon the application of an appropriate gate voltage. Clearly, however, all of these conductivity types could be reversed so that the device could work 10 as a p-channel device rather than an n-channel device as disclosed.

One process by which the device of FIGS. 1 and 2 could be constructed is shown in FIGS. 3 to 6. Referring to FIG. 3, the base wafer 20 is shown as an n(+) 15 material having an n(-) epitaxially deposited region on top thereof. A thick oxide layer 50 is formed on wafer 20 and windows 51 and 52 are opened therein. The open windows 51 and 52 are exposed to a beam of boron atoms in an ion implanting apparatus to form p(+) 20 regions. Thereafter the implanted boron atoms are caused to diffuse deeper into the wafer to form the rounded p(+) concentration region shown in FIG. 3 which might have a depth of about 4 microns. During this diffusion operation, shallow oxide layers 53 and 54 25 grow over the windows 51 and 52.

As is next shown in FIG. 4, windows 61 and 62 are cut in the oxide layer 50 and an n(+) implant takes place to implant the n(+) regions 63 and 64 into the n(-) epitaxial layer. This n(+) implantation can be 30 carried out with a phosphorus beam. Thereafter, the implanted regions are subjected to a diffusion step to cause the regions 63 and 64 to expand and deepen to a depth of about 31 microns with a concentration determined by an implantation dose of  $1 \times 10^{12}$  to  $1 \times 10^{14}$  35 phosphorus atoms/cm<sup>2</sup> followed by a drive for 30 minutes to 4 hours at from 1150° C. to 1250° C. As will be later seen, regions 63 and 64 produce the novel n(+)region which substantially reduces the on-resistance of the device. 40

It should be noted that the n(+) regions 63 and 64 could, if desired, be epitaxially deposited and need not be diffused. Similarly, the resulting device being described herein could be manufactured by any desired process as would be apparent to those skilled in the art. 45

The next step in the process is shown in FIG. 5 and is the channel implantation and diffusion step in which the p(+) regions 71 and 72 are formed through the same windows 61 and 62 that were used for the n(+) implantation for regions 63 and 64. The p(+) regions 71 and 72 50 are formed by implanting with a boron beam to a dose of about  $5 \times 10^{13}$  to  $5 \times 10^{14}$  atoms/cm<sup>2</sup> followed by a diffusion drive for 30 to 120 minutes at 1150° C. to 1250° C.

Thereafter, and as shown in FIG. 6, steps are carried 55 out for the source predeposition and the diffusion of the source regions 32 and 33. This is carried out by a conventional and non-critical phosphorus diffusion step where the diffusion proceeds through the windows 61 and 62 so that the source regions 32 and 33 are automati-60 cally aligned relative to the other preformed regions. Thus, the wafer is placed in a furnace and exposed to POCl<sub>3</sub> suspended in a carrier gas for from 10 minutes to 50 minutes at a temperature of from 850° C. to 1000°.

When this step is completed, the basic junction configuration required in FIG. 2 is formed with short p(+)regions disposed beneath the oxide 50 to serve as the conducting channel for the ultimately constructed de-

vice and with an n(+) region filling the area between the channels 34 and 35 and between p(+) regions 30 and 31. The manufacturing process then continues from the step of FIG. 6 to the device shown in FIG. 2 wherein the oxide surfaces on top of the chip are suitably stripped and the metalizing patterns for contacts 22, 23 and 24 are formed to establish electrical contacts to the device. The drain contact 26 is applied to the device in a subsequent metalizing operation. Thereafter, the entire device may be appropriately coated with a suitable passivation coating and wire leads are connected to the source electrodes 22 and 23 and the gate 24. The device is then mounted within a suitable protective housing, with the drain electrode fixed to the housing or other conductive support which serves as a drain connection.

The device shown in FIGS. 1 and 2 utilizes a serpentine path for each of the source regions and gate regions and a drain on the surface of the wafer opposite to the source electrodes. Other configurations can be used. FIGS. 7 and 8 illustrate a planar configuration which is a simple rectangular arrangement having a ring-shaped gate 80 which is disposed between a first source electrode 81 of ring shape and a central source 82. The device as shown in FIG. 8 is contained within a base wafer of p(-) monocrystalline silicon 83 which may have a buried n(+) region 84 to reduce the lateral resistance of the various current paths of the device leading to the laterally displaced drain electrode 85 which surrounds source 81.

A ring-shaped n(+) region 86 is formed within the device as shown in FIG. 8 and, in accordance with the present invention, the ring-shaped region 86 is of much higher conductivity than the n(-) epitaxially deposited region 87 which contains all the junctions of the device. The ring-shaped region 86 extends from the region beneath the gate oxide 88 and adjoins the ends of the two conducting channels formed between the ring-shaped p(+) region 89 and the central p(+) region 91 disposed beneath the ring-shaped source 81 and central source 82, respectively.

It will also be noted in FIG. 8 that the outer periphery 90 of the p(+) ring 89 has a large radius to assist the device in withstanding high reverse voltages.

An n(+) region 95 in FIG. 8 is provided to ensure good contact to drain electrode 85. Drain electrode 85 is widely laterally spaced from source 81 (by greater than about 90 microns). The drain contact 85 is surrounded by a p(+) isolation diffusion 96 to isolate the device from other devices on the same chip or wafer.

In the arrangement of FIG. 8, like that of FIG. 2, current flow from sources 81 and 82 goes through the width of epitaxial region 87, through the region 86. The current then flows laterally outward and then up to the drain contact 85. As in the embodiment of FIG. 2, device resistance is greatly reduced by the relatively highly conductive region 86.

In carrying out the above invention, it should be noted that any type of contact material can be used to make the source and gate contacts. By way of example, aluminum could be used for the source electrodes while a polysilicon material can be used for the conductive gate 80 in FIG. 8 or the conductive gate 24 in FIG. 2.

Numerous other geometries can be used to make the device of the invention, including a plurality of pairs of straight, parallel source elements with respectively interposed gates and the like.

The source electrodes 22 and 23 have been shown as separate electrodes which can be connected to separate leads. Clearly, the sources 22 and 23 could be directly connected as shown in FIG. 8a where components similar to those of FIG. 2 have been given similar identi-5 fying numerals. In FIG. 8a, however, the gate electrode is a polysilicon layer 101 (in place of aluminum) deposited atop gate oxide 25. The gate 101 is then covered with oxide layer 102 and a conductive layer 103 connects the two sources 22 and 23 together to form a 10 single source conductor which is insulated from gate 101. Connection is made to the gate at some suitable edge portion of the wafer.

FIGS. 9 and 10 show the shape of measured curves which demonstrate the reduction in forward resistance <sup>15</sup> when the region 40 is made highly conductive (n+). In FIG. 9, the device tested had a region 40 which had the n(-) resistivity of the epitaxial region. Thus, the forward resistance is characteristically high at different 20 gate biases as shown in FIG. 9.

In the device of the invention where region 40 is of n(+) conductivity, there is a dramatic decrease in the on-resistance as shown in FIG. 10 for all gate voltages before velocity saturation of the electrons occurs.

Although the present invention has been described in <sup>25</sup> connection with a preferred embodiment thereof, many variations and modifications will now become apparent to those skilled in the art. It is preferred, therefore, that the present invention be limited not by the specific 30 disclosure herein, but only by the appended claims.

What is claimed is:

1. A high power metal oxide silicon field effect transistor device exhibiting relatively low on-resistance and relatively high breakdown voltage; said device com- 35 prising:

- a wafer of semiconductor material having first and second opposing semiconductor surfaces; said wafer of semiconductor material having a relatively lightly doped major body portion for receiv- 40 ing junctions and being doped with impurities of one conductivity type;

- at least first and second spaced base regions of the opposite conductivity type to said one conductivity type formed in said wafer and extending from 45 said first semiconductor surface to a first depth beneath said first semiconductor surface; the space between said at least first and second base regions defining a common conduction region of one conductivity type at a given first semiconductor sur- 50 face location:

- first and second source regions of said one conductivity type formed in each pair of said at least first and second base regions respectively at first and second first surface location to a depth less than said first 55 depth; the outer rim of each of said first and second source regions being laterally spaced along said first semiconductor surface from the lateral outer periphery of its said base region to define first and second channel regions along said first semicon- 60 ductor surface between each pair of said first and second source regions, respectively, and said common conduction region;

- source electrode means connected to said source regions;

- gate insulation layer means on said first surface, disposed at least on said first and second channel regions:

- gate electrode means on said gate insulation layer means and overlying said first and second channel regions;

- a drain conductive region remote from said common region and separated therefrom by said relatively lightly doped major body portion;

- a drain electrode coupled to said drain conductive region: and

- at least said first base region being a cellular polygonal region; said cellular polygonal region being surrounded by said common conduction region; said first source region having the shape of an annular ring disposed within said cellular polygonal first base region.

2. The device of claim 1 wherein said common conduction region is relatively highly doped compared to said relatively highly doped major body portion and extends from said given first semiconductor surface location to a depth greater than the depth of said source region, but less than said first depth of said first and second spaced base regions, whereby resistance to current flow at the junctures between said first and second surface channel regions and said common conduction region and between said common conduction region and said relatively lightly doped major body portion is reduced.

3. The device of claim 1 wherein said source electrode means comprises a single sheet of conductive material disposed over and contacting each of said source regions.

A high power metal oxide silicon field effect transistor device exhibiting relatively low on-resistance and relatively high: breakdown voltage; said device comprising:

- a wafer of semiconductor material having first and second opposing semiconductor surfaces; said wafer of semiconductor material having a relatively lightly doped major body portion for receiving junctions and being doped with impurities of one conductivity type;

- at least first and second spaced base regions of the opposite conductivity type to said one conductivity type formed in said wafer and extending from said first semiconductor surface to a first depth beneath said first semiconductor surface; the space between said at least first and second base regions defining a common conduction region of one conductivity type at a given first semiconductor surface location:

- first and second source regions of said one conductivity type formed in each pair of said at least first and second base regions respectively at first and second first surface locations and extending from said first and second first surface locations to a depth less than said first depth; the outer rim of each of said first and second source regions being laterally spaced along said first semiconductor surface from the lateral outer periphery of its said base region to define first and second channel regions along said first semiconductor surface between each pair of said first and second source regions, respectively, and said common conduction region;

- source electrode means connected to said source regions:

- gate insulation layer means on said first surface, disposed at least on said first and second channel regions:

Exhibit A – Page <u>19</u>

11

material disposed over and contacting each of said source regions.

15. The device of claim 8, wherein said common conduction region is relatively highly doped compared to said relatively lightly doped major body portion and 5 extends from said given first semiconductor surface location to a depth greater than the depth of said source region but less than said depth of said first and second base regions, whereby resistance to current flow at the junctures between said first and second surface channel 10 regions and said common conduction region and between said common conduction region and said relatively lightly doped major body portion is reduced.

16. The device of claim 7 wherein said source electrode means makes electrical contact to the surface of 15 said cellular polygonal region and the surface of said annular ring-shaped region.

17. The device of claim 8 wherein said source electrode means makes electrical contact to the surface of said cellular polygonal region and the surface of said 20 annular ring-shaped ring.

18. The device of claim 15 wherein said source electrode means makes electrical contact to the surface of said cellular polygonal region and the surface of said annular ring-shaped ring.

19. A high power metal oxide silicon field effect transistor device exhibiting relatively low on-resistance; said device comprising:

- a wafer of semiconductor material having first and second opposing semiconductor surfaces; said 30 wafer of semiconductor material having a relatively lightly doped major body portion for receiving junctions and being doped with impurities of one conductivity type;

- at least first and second spaced base regions of the 35 opposite conductivity type to said one conductivity type formed in said wafer and extending from said first semiconductor surface to a first depth beneath said first semiconductor surface; the space between said at least first and second base regions 40 defining a common conduction region of one conductivity type at a given first semiconductor surface location;

- first and second source regions of said one conductivity type formed in each pair of said at least first and 45 second base regions respectively at first and second first surface locations and extending from said first and second first surface locations to a depth less than said first depth; the outer rim of each of said first and second source regions being laterally 50 spaced along said first semiconductor surface from the lateral outer periphery of its said base region to define first and second channel regions along said first semiconductor surface between each pair of

said first and second source regions, respectively, and said common conduction region;

- source electrode means connected to said source regions;

- gate insulation layer means on said first surface, disposed at least on said first and second channel regions;

- gate electrode means on said gate insulation layer means and overlying said first and second channel regions:

- said wafer including a further region of opposite conductivity type adjoining said lightly doped major body portion; and

an electrode coupled to said further region.

20. The device of claim 19 wherein at least said first base region comprises a cellular polygonal region; said cellular polygonal region being surrounded by said common conduction region; said first source region having the shape of an annular ring disposed within said cellular polygonal first base region.

21. The device of claim 19 wherein said common conduction region is relatively highly doped compared to said relatively lightly doped major body portion and wherein said common conduction region extends from 25 said given first semiconductor surface location to a depth greater than the depth of said source region but less than said depth of said first and second base regions, whereby resistance to current flow in the path between said first and second surface channel regions and said 30 common conduction region and between said common conduction region and said relatively lightly doped major body portion is reduced.

22. The device of claim 19 wherein said source electrode means comprises a single sheet of conductive material disposed over and contacting each of said source regions.

23. The device of claim 19 wherein said source electrode means makes electrical contact to the surface of said cellular polygonal base region and the surface of said annular ring-shaped source region.

24. The device of claim 19 wherein each of said at least first and second spaced base regions of said opposite conductivity type have respective profiles which include relatively shallow depth regions extending from said common conduction region and underlying their said respective first and second source regions, and respective relatively deep, relatively large radius regions extending from said shallow depth regions which are laterally spaced from beneath said respective source regions on the side of said source regions which is away from said common conduction region; said shallow base regions partially underlying their respective source regions.

. . . . .

60

55

65

Exhibit A – Page 🐊

gate electrode means on said gate insulation layer means and overlying said first and second channel regions;

- a drain conductive region remote from said common region and separated therefrom by said relatively <sup>5</sup> lightly doped major body portion; and

- a drain electrode coupled to said drain conductive region;

- said common conduction region being relatively highly doped compared to said relatively lightly 10 doped major body portion and extending from said given first semiconductor surface location to a depth greater than the depth of said source region but less than said first depth of said first and second spaced base regions, whereby resistance to current <sup>15</sup> flow at the junctures between said first and second surface channel regions and said common conduction region and between said common conduction region and said relatively lightly doped major body 20 portion is reduced, wherein said source electrode means comprises a single sheet of conductive material disposed over and contacting each of said source regions.

5. The device of claim 2 wherein said source electrode means comprises a single sheet of conductive <sup>25</sup> material disposed over and contacting each of said source regions.

6. The device of claim 1 wherein said source electrode means makes electrical contact to the surface of 30 said cellular polygonal region and the surface of said annular region-shaped ring.

7. A three-terminal power metal oxide silicon field effect transistor device comprising:

- a wafer of semiconductor material having first and 35 second opposing semiconductor surfaces; said wafer of semiconductor material having a relatively lightly doped major body portion for receiving junctions and being doped with impurities of one conductivity type; 40

- at least first and second spaced base regions of the opposite conductivity type to said one conductivity type formed in said wafer and extending from said first semiconductor surface to a depth beneath said first semiconductor surface; the space between 45 said at least first and second base regions defining a common conduction region of one conductivity type at a given first semiconductor surface location;

- first and second source regions of said one conductivity type formed in each pair of said at least first and second base regions respectively at first and second first surface locations and extending from said first and second first surface locations to a depth less than said depth of said base regions; said first and 55 second source regions being laterally spaced along said first semiconductor surface from the facing respective edges of said common conduction region thereby to define first and second channel regions along said first semiconductor surface between each pair of said first and second source regions, respectively and said common conduction region;

- source electrode means connected to said source regions and comprising a first terminal;

- gate insulation layer means on said first surface, disposed at least on said first and second channel regions;

10

- gate electrode means on said gate insulation layer means, overlying said first and second channel regions and comprising a second terminal;

- a drain conductive region remove from said common region and separated therefrom by said relatively lightly doped major body portion;

- a drain electrode coupled to said drain conductive region and comprising a third terminal;

- each of said at least first and second spaced base regions of said opposite conductivity type having respective profiles which include relatively shallow depth regions extending from said common region and underlying their said respective first and second source regions, and respective relatively deep, relatively large radius regions extending from said shallow depth regions which are laterally spaced from beneath said respective source regions on the side of said source regions which is away from said common region;

- at least said first base region being a cellular polygonal region; said cellular polygonal region being surrounded by said common conduction region; said first source region having the shape of an annular ring disposed within said cellular polygonal first base region; said relatively shallow depth region of said first base region surrounding the outer periphery of said relatively deep portion of said first base region.

8. The device of claim 7 wherein said shallow base regions partially underlie their respective source regions.

9. The device of claim 7 wherein said common conduction region is relatively highly doped compared to said relatively lightly doped major body portion and extends from said given first semiconductor surface location to a depth greater than the depth of said source region but less than said depth of said first and second base regions, whereby resistance to current flow at the junctures between said first and second surface channel regions and said common conduction region and between said common conduction region and said relatively lightly doped major body portion is reduced.

10. The device of claim 8 wherein said common conduction region is relatively highly doped compared to said relatively lightly doped major body portion and extends from said given first semiconductor surface location to a depth greater than the depth of said source region but less than said depth of said first and second base regions, whereby resistance to current flow at the junctures between said first and second surface channel regions and said common conduction region and between said common conduction region and said relatively lightly doped major body portion is reduced.

11. The device of claim 7 wherein said source electrode means comprises a single sheet of conductive material disposed over and contacting each of said source regions.

12. The device of claim 8 wherein said source electrode means comprises a single sheet of conductive material disposed over and contacting each of said source regions.

The device of claim 9 wherein said source electrode means comprises a single sheet of conductive

material disposed over and contacting each of said source regions.

14. The device of claim 10 wherein said source electrode means comprises a single sheet of conductive

Exhibit A – Page 20

REEXAMINATION CERTIFICATE (2105th)

## United States Patent [19]

### Lidow et al.

# [11] **B1 4,959,699**

### [54] HIGH POWER MOSFET WITH LOW ON-RESISTANCE AND HIGH BREAKDOWN VOLTAGE

[76] Inventors: Alexander Lidow, Manhattan Beach; Thomas Herman, Redondo Beach, both of Calif.

#### **Reexamination Request:**

No. 90/002,515, Nov. 13, 1991

#### **Reexamination Certificate for:**

| Patent No.: | 4,959,699     |  |  |

|-------------|---------------|--|--|

| Issued:     | Sep. 25, 1990 |  |  |

| Appl. No.:  | 371,678       |  |  |

| Filed:      | Jun. 22, 1989 |  |  |

Certificate of Correction issued May 25, 1993.

#### **Related U.S. Application Data**

- [60] Continuation of Ser. No. 90,664, Aug. 27, 1987, abandoned, which is a division of Ser. No. 456,813, Jan. 10, 1983, abandoned, which is a division of Ser. No. 232,713, Feb. 9, 1981, Pat. No. 4,376,286, which is a continuation of Ser. No. 951,310, Oct. 13, 1978, abandoned.

- [51] Int. Cl.<sup>5</sup> ...... H01L 29/10; H01L 29/78; H01L 29/68; H01L 27/02

- [58] Field of Search ...... 357/23.4, 23.8

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| al               |

|------------------|

|                  |

| n et al 357/23.4 |

| kar .            |

| ard et al.       |

| ckson .          |

| сг.              |

| ctal.            |

| 1                |

|                  |

[45] Certificate Issued Oct. 12, 1993

### FOREIGN PATENT DOCUMENTS

| 51-85381 | 7/1976 | Japan |  |

|----------|--------|-------|--|

| 7.1066PR |        |       |  |

53-74385 7/1978 Japan .

### **OTHER PUBLICATIONS**

R. J. Duchynski, "Ion implantation for semiconductor devices", Solid State Technology, (Nov. 1977) pp. 53-58. J. D. Plummer, "Process physics: Implications for manufacturing of submicron silicon devices", Solid State Technology (Mar. 1986) pp. 61-66.

Introductions to Sessions 6, 12, 18 and 29, International Electron Devices Meeting (1989) *Technical Digest*, four pages.

J. J. Carroll et al., "Ellipsometry-LEED study of the absorption of oxygen on (011) tungsten", Surface Science, vol. 16 (1969) pp. 251-264.

(List continued on next page.)

#### Primary Examiner-J. Carroll

#### [57] ABSTRACT

A high power MOSFET is disclosed in which two laterally spaced sources each supply current through respective channels in one surface of a semiconductor chip which are controlled by the same gate. The channels lead from the source electrodes to a relatively low resistivity region and from there to a relatively high resistivity epitaxially formed region which is deposited on a high conductivity substrate. The drain electrode may be either on the opposite surface of the chip or laterally displaced from and on the same side as the source regions. The epitaxially deposited semiconductor material immediately adjacent and beneath the gate and in the path from the sources to the drain has a relatively high conductivity, thereby to substantially reduce the on-resistance of the device without effecting the breakdown voltage of the device. The breakdown voltage of the device is substantially increased by forming a relatively deep p-type diffusion with a large radius in the n-type epitaxial layer beneath each of the sources.

### B1 4,959,699

### Page 2

### **OTHER PUBLICATIONS**

J. L. Stone et al., "Recent advances in ion implantation-a state of the art review", Solid State Technology, (Jun. 1976) pp. 35-44.

J. Sansbury, "Applications of ion implantation in semiconductor processing", Solid State Technology, (Nov. 1976) pp. 31-37.

A High Power MOSFET with a Vertical Drain Electrode and a Meshed Gate Structure, Yoshida, et al., IEEE Journal of Solid State Circuits, vol. SC-11, No. 4 (Aug. 1976) pp. 472-477.

Power Handling Capability of MOSFET, Minoru Nagata, Japanese Journal of Applied Physics, vol. 16, Supp. 16-1, pp. 217-222 (1977).

IBM Technical Disclosure Bulletin, vol. 16, No. 11, pp.

3519-3520, Cady, et al. (Apr. 1974).

DSA MOS Transistor and Its Integrated Circuit, Japanese Journal of Applied Physics, vol. 16, Suppl. 16-1, pp. 163-166, Y. Haysashi, et al. (1977).

Optimization of Nonplanar Power MOS Transistors, IEEE Transactions on Electron Devices, vol. ED-25, No. 10, K. P. Lisiak, et al. (Oct. 1978) 6 pages.

Diffusion Self-Aligned MOST: A New Approach for High Speed Device, Proceedings of the 1st Conference on Solid State Devices, Tokyo, 1969 Supplement to the Journal of the Japan Society of Applied Physics, vol. 39, Y. Tarui, et al. (1970) 6 pages.

Japanese Take Two Steps Forward In MOST-Bipolar Compatibility, Electronics International (Oct. 13, 1969) 4 pages.

Exhibit A – Page &

### B1 4,959,699

### **REEXAMINATION CERTIFICATE** ISSUED UNDER 35 U.S.C. 307

1

### THE PATENT IS HEREBY AMENDED AS INDICATED BELOW.

. .

## 2 AS A RESULT OF REEXAMINATION, IT HAS BEEN DETERMINED THAT:

The patentability of claims 1 to 3 and 5 to 24 is con-5 firmed.

Claim 4 is cancelled.

15

10

# 20

25

35

40

45

50

30

55

65

60

Exhibit A - Page 24

## **REEXAMINATION CERTIFICATE (3706th)**

# United States Patent [19]

### Lidow et al.

### [54] HIGH POWER MOSFET WITH LOW ON-**RESISTANCE AND HIGH BREAKDOWN** VOLTAGE

[76] Inventors: Alexander Lidow, 4005 Strand Ave., Manhattan Beach, Calif, 90266; Thomas Herman, 1623 Herrin Dr., Redondo Beach, Calif. 90278

#### **Reexamination Requests:**

No. 90/003,490, Jul. 12, 1994 No. 90/003,900, Jul. 25, 1995

#### **Reexamination Certificate for:**

| Patent No.: | 4,959,699     |  |

|-------------|---------------|--|

| Issued:     | Sep. 25, 1990 |  |

| Appl. No.:  | 371,678       |  |

| Filed:      | Jun. 22, 1989 |  |

Recxamination Certificate B1 4,959,699 issued Oct. 12, 1993

Certificate of Correction issued May 25, 1993.

#### **Related U.S. Application Data**

- [60] Continuation of Ser. No. 90,664, Aug. 27, 1987, abandoned, which is a division of Ser. No. 456,813, Jan. 10, 1983, abandoned, which is a division of Ser. No. 232,713, Feb. 9, 1981, Pat. No. 4,376,286, which is a continuation of Ser. No. 951,310, Oct. 13, 1978, abandoned.

- 257/487; 257/653

#### [56] **References** Cited

#### U.S. PATENT DOCUMENTS

| Re. 33,209 | 5/1990  | Plummer         |

|------------|---------|-----------------|

| 3,619,740  | 11/1971 | Nakanuma et al  |

| 3,831,187  | 8/1974  | Neilson         |

| 4,072,975  | 2/1978  | Ishitani        |

| 4,145,700  | 3/1979  | Jambotkar       |

| 4,145,703  | 3/1979  | Blanchard et al |

| 4,148,047  | 4/1979  | Hendrickson     |

| 4,163,246  | 7/1979  | Agmura et al    |

### [11] B2 4,959,699

#### [45] Certificate Issued Jan. 19, 1999

US004959699B1

| 2/1980  | Tihanyi et al                                                                  |

|---------|--------------------------------------------------------------------------------|

|         | Plummer                                                                        |

| 6/1980  | Hance et al 257/341                                                            |

| 8/1980  | van Loon et al                                                                 |

| 11/1980 | Takemoto et al                                                                 |

|         | Lidow et al                                                                    |

| 7/1986  | Yoshida et al                                                                  |

| 2/1987  | Lidow et al                                                                    |

| 11/1987 | Lidow et al                                                                    |

| 7/1992  | Lidow et al                                                                    |

|         | 4/1980<br>6/1980<br>8/1980<br>11/1980<br>3/1983<br>7/1986<br>2/1987<br>11/1987 |

#### FOREIGN PATENT DOCUMENTS

| 1972 Japan.<br>1976 Japan.<br>1976 Japan.<br>1977 Japan.<br>1977 Japan. |

|-------------------------------------------------------------------------|

|                                                                         |

#### **OTHER PUBLICATIONS**

E. S. Oxner, Power FETs and Their Applications, Prentice-Hall, Inc., New Jersey (1982) pp. 67-71.

(List continued on next page.)

Primary Examiner-Stanley Miller

#### [57] ABSTRACT

A high power MOSFET is disclosed in which two laterally spaced sources each supply current through respective channels in one surface of a semiconductor chip which are controlled by the same gate. The channels lead from the source electrodes to a relatively low resistivity region and from there to a relatively high resistivity epitaxially formed region which is deposited on a high conductivity substrate. The drain electrode may be either on the opposite surface of the chip or laterally displaced from and on the same side as the source regions. The epitaxially deposited semiconductor material immediately adjacent and beneath the gate and in the path from the sources to the drain has a relatively high conductivity, thereby to substantially reduce the on-resistance of the device without effecting the breakdown voltage of the device. The breakdown voltage of the device is substantially increased by forming a relatively deep p-type diffusion with a large radius in the n-type epitaxial layer beneath each of the sources.

Case 2:00-cv-06756-R-C

B2 4,959,699

Page 2

#### OTHER PUBLICATIONS

K. Lisiak et al., "Optimization of Non-Planar Power MOS Transistors", IEEE Transactions on Electron Devices, vol. ED-25 (Oct. 1978) pp. 1229-1234.

S. M. Sze, Semiconductor Devices Physics and Technology, John Wiley & Sons, New York (1985) pp. 105-107.

B. J. Baliga et al., "Analytical Solutions for the Breakdown Voltage of Abrupt Cylindrical and Spherical Junctions", Solid-State Electronics, vol. 19 (1976) pp. 739-744.

S. M. Sze, Semiconductor Devices Physics and Technology, John Wiley & Sons, New York (1985) p. 203.

S. Krishna, "Secondary Breakdown in High Voltage MOS Transistors", Solid-State Electronics, vol. 20 (1977) pp. 875-878.

S. M. Sze, Semiconductor Devices Physics and Technology, John Wiley & Sons, New York (1985) pp. 401-402.

Full English Translation of Japan Kokai Patent Publication No. 51-134076 as per USPTO.

H. F. Gray et al., "Sleep and AES Applied to Solid State Devices and Materials" IEDM 74, (Dec. 1974) pp. 561-564. S. R. Combs et al., "Characterization and Modeling of Simultaneously Fabricated DMOS and VMOS Transistors", IEDM 76, (Dec. 1976) pp. 569-572.

Full English Translation of Japan Kokai Patent Publication No. 52-104878.

Certificate of Correction dated 25 May 1993 for US Patent No. 4,959,699.

D. B. Lee, "Anisotropic Btching of Silicon". Journal of Applied Physics, vol. 40, No. 11 (Oct. 1969) ppm 4569-4574.

M. J. Declercq et al., "Optimization of the Hydrazine-Water Solution for Anisotropic Etching of Silicon in Integrated Circuit Technology", J. Electrochem. Soc.: Solid-State Science and Technology, vol. 122, No. 4 (Apr. 1975) pp. 545-552.

Tarui et al., "Diffusion Self-Aligned MOST: A New Approach for High Speed Device." J. of Japan Society of Applied Physics, vol. 39, 1970, pp. 105-110.

Pocha et al., "A Computer-Aided Design Model for High-Voltage Double Diffused MOS (DMOS) Transistors," IEEE Journal of Solid-State Circuits, vol. SC-11, No. 5, (Oct. 1976, pp. 718-726.

Yoshida et al., "A High power MOSFET with a Vertical Drain Electrode and a Meshed Gate Structure," IEEE Journal of Solid-State Circuits, vol. SC-11, No. 4, Aug. 1976. pp. 472-477.

Plummer et al., "A Monolithic 200-V CMOS CMOS Analog Switch," IEEE Journal of Solid-State Circuits, vol. SC-11, No. 6, Dec. 1976, pp. 809-817.

Scharf et al., "A MOS-Controlled Triac Device," 1978 IEEE International Solid-State Circuits Conference, San Francisco, Calif., Feb. 15-17, 1978, pp. 222-223.

E. S. Oxner, Power FETs. and Their Applications, Prentice-Hall, Inc., New Jersey (1982) pp. 59-67.

Ł

Exhibit A – Page 26

Case 2:00-cv-06756-R-<u>CT</u>

### B2 4,959,699

15

### 1 **REEXAMINATION CERTIFICATE** ISSUED UNDER 35 U.S.C. 307

### THE PATENT IS HEREBY AMENDED AS INDICATED BELOW.

Matter enclosed in heavy brackets [ ] appeared in the patent, but has been deleted and is no longer a part of the patent; matter printed in italics indicates additions made to the patent.

#### AS A RESULT OF REEXAMINATION, IT HAS BEEN DETERMINED THAT:

Claim 4 was previously cancelled.