# IN THE UNITED STATES DISTRICT COURT FOR THE DISTRICT OF DELAWARE

ROUND ROCK RESEARCH, LLC,

Plaintiff,

v.

NINTENDO CO., LTD. and NINTENDO OF AMERICA INC.,

Defendants.

Civil Action No. 14-cv-1491-SLR-SRF

JURY TRIAL DEMANDED

# SECOND AMENDED COMPLAINT

Plaintiff Round Rock Research, LLC ("Round Rock"), for its Second Amended Complaint against Defendants Nintendo Co., Ltd. and Nintendo of America Inc. (collectively, "the Nintendo Defendants"), hereby alleges as follows:

# The Parties

1. Plaintiff Round Rock is a Delaware limited liability company with its principal place of business at 2001 Route 46, Waterview Plaza, Suite 310, Parsippany, NJ 07054.

2. Upon information and belief, defendant Nintendo Co., Ltd. ("Nintendo Co.") is a corporation organized and existing under the laws of Japan with its principal place of business at 11-1 Hokotate-cho, Kamitoba, Minami-ku, Kyoto, Japan 601-8501. Nintendo Co. is in the business of researching, designing, developing, manufacturing, and selling video game products including but not limited to consoles, handheld videogame systems, video games, accessories, and components of those products, for importation into the United States and sales in the United States, including in Delaware.

3. Upon information and belief, defendant Nintendo of America Inc. ("Nintendo of America") is a corporation organized under the laws of Washington, having a principal place of business at 4600 150th Avenue NE, in Redmond, Washington 98052. Nintendo of America has appointed The Corporation Trust Company at Corporation Trust Center, 1209 Orange Street in Wilmington, Delaware as its registered agent for service of process in the state of Delaware. Nintendo of America is in the business of importing, marketing, advertising, and selling video game products including consoles, handheld videogame systems, video games, and accessories in the United States, including in Delaware.

4. Nintendo of America is a wholly owned subsidiary of Nintendo Co.

# **Nature Of The Action**

5. This is a civil action for infringement of U.S. Patent Nos. 5,986,347 ("the '347 patent") (attached as Exhibit A), 6,147,405 ("the '405 patent") (attached as Exhibit B), 6,358,801 ("the '801 patent") (attached as Exhibit C), 6,455,935 ("the '935 patent") (attached as Exhibit D), 6,469,336 ("the '336 patent") (attached as Exhibit E), and 6,828,683 ("the '683 patent") (attached as Exhibit F) (collectively, the "Patents-in-Suit") under the Patent Laws of the United States, 35 U.S.C. § 1 *et seq*.

### Jurisdiction And Venue

6. This Court has jurisdiction over the subject matter of this action pursuant to 28 U.S.C. §§ 1331 and 1338(a) because this action arises under the patents laws of the United States, including 35 U.S.C. § 271 *et seq*.

7. This Court has personal jurisdiction over the Nintendo Defendants because, among other things, the Nintendo Defendants have committed, aided, abetted, contributed to,

and/or participated in the commission of patent infringement in violation of 35 U.S.C. § 271 in this judicial district and elsewhere that led to foreseeable harm and injury to Round Rock.

8. This Court also has personal jurisdiction over the Nintendo Defendants because, among other things, the Nintendo Defendants have established minimum contacts within the forum such that the exercise of jurisdiction over the Nintendo Defendants will not offend traditional notions of fair play and substantial justice. For example, the Nintendo Defendants have placed products that practice and/or embody the claimed inventions of the Patents-in-Suit into the stream of commerce with the reasonable expectation and/or knowledge that purchasers and users of such products were located within this district. In addition, the Nintendo Defendants have sold, advertised, marketed, and distributed products in this district that practice the claimed inventions of the Patents-in-Suit. The Nintendo Defendants derive substantial revenue from the sale of infringing products distributed within the district, and/or expect or should reasonably expect their actions to have consequences within the district, and derive substantial revenue from interstate and international commerce.

9. In addition, the Nintendo Defendants knowingly, actively induced and continue to knowingly actively induce infringement of one or more of the Patents-in-Suit within this district by making, using, offering for sale, and selling infringing products, as well as by contracting with others to use, market, sell, and offer to sell infringing products, all with knowledge of the asserted Patents-in-Suit, and their claims, with knowledge that their customers will use, market, sell, and offer to sell infringing products in this district and elsewhere in the United States, and with the knowledge and specific intent to encourage and facilitate infringing sales and use of the products by others within this district and the United States by creating and disseminating

promotional and marketing materials, instructional materials, and product manuals, and technical materials related to the infringing products.

10. Venue is proper in this district pursuant to 28 U.S.C. §§ 1391(b), 1391(c), and 1400(b), because the Nintendo Defendants are subject to personal jurisdiction in this district and have committed acts of infringement in this district.

# The Patents-In-Suit

11. United States Patent No. 5,986,347 ("the '347 patent"), titled "Processing Methods Of Forming Contact Openings And Integrated Circuitry," was duly and legally issued by the U.S. Patent and Trademark Office on November 16, 1999. A copy of the '347 patent is attached hereto as Exhibit A. Round Rock is the assignee of all rights, title, and interest in the '347 patent, and it possesses all rights to sue and recover for any current or past infringement of the '347 patent.

12. United States Patent No. 6,147,405 ("the '405 patent"), titled "Asymmetric, Double-Sided Self-Aligned Silicide And Method Of Forming the Same," was duly and legally issued by the U.S. Patent and Trademark Office on November 14, 2000. A copy of the '405 patent is attached hereto as Exhibit B. Round Rock is the assignee of all rights, title, and interest in the '405 patent, and it possesses all rights to sue and recover for any current or past infringement of the '405 patent.

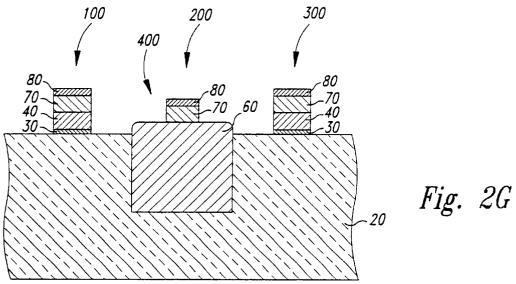

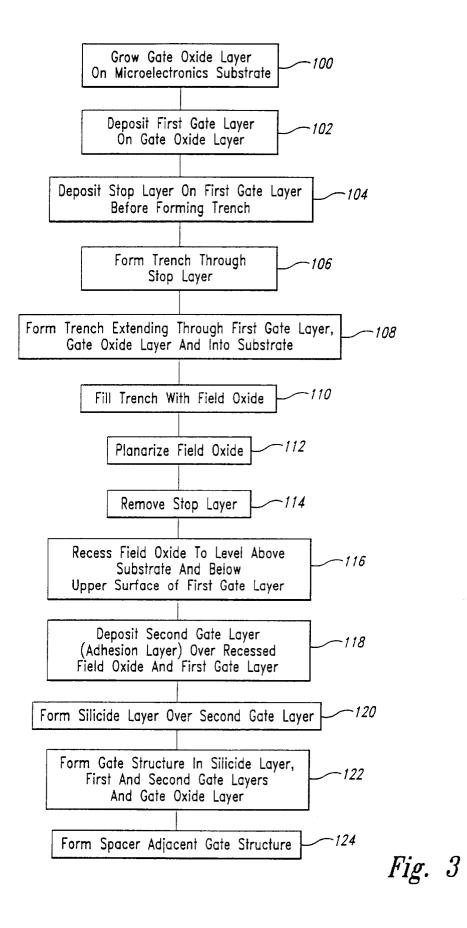

13. United States Patent No. 6,358,801 ("the '801 patent"), titled "Method And Apparatus For Trench Isolation Process With Pad Gate And Trench Edge Spacer Elimination," was duly and legally issued by the U.S. Patent and Trademark Office on March 19, 2002. A copy of the '801 patent is attached hereto as Exhibit C. Round Rock is the assignee of all rights,

title, and interest in the '801 patent, and it possesses all rights to sue and recover for any current or past infringement of the '801 patent.

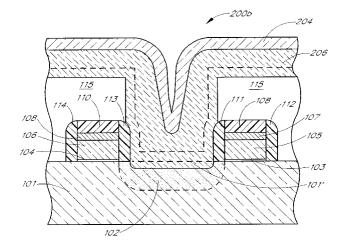

14. United States Patent No. 6,455,935 ("the '935 patent"), titled "Asymmetric, Double-Sided Self-Aligned Silicide," was duly and legally issued by the U.S. Patent and Trademark Office on September 24, 2002. A copy of the '935 patent is attached hereto as Exhibit D. Round Rock is the assignee of all rights, title, and interest in the '935 patent, and it possesses all rights to sue and recover for any current or past infringement of the '935 patent.

15. United States Patent No. 6,469,336 ("the '336 patent"), titled "Structure For Reducing Contact Aspect Ratios," was duly and legally issued by the U.S. Patent and Trademark Office on October 22, 2002. A copy of the '336 patent is attached hereto as Exhibit E. Round Rock is the assignee of all rights, title, and interest in the '336 patent, and it possesses all rights to sue and recover for any current or past infringement of the '336 patent.

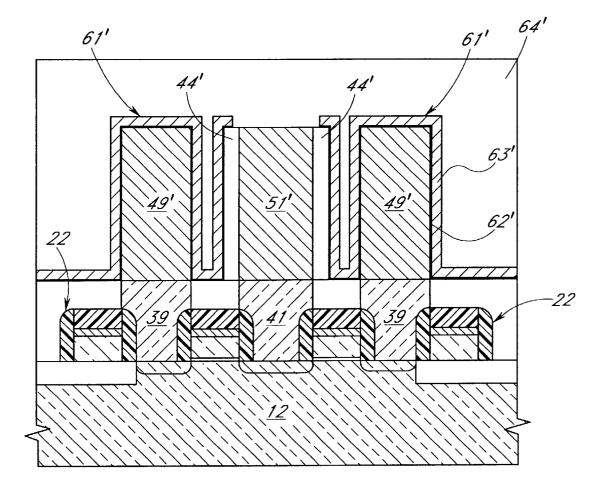

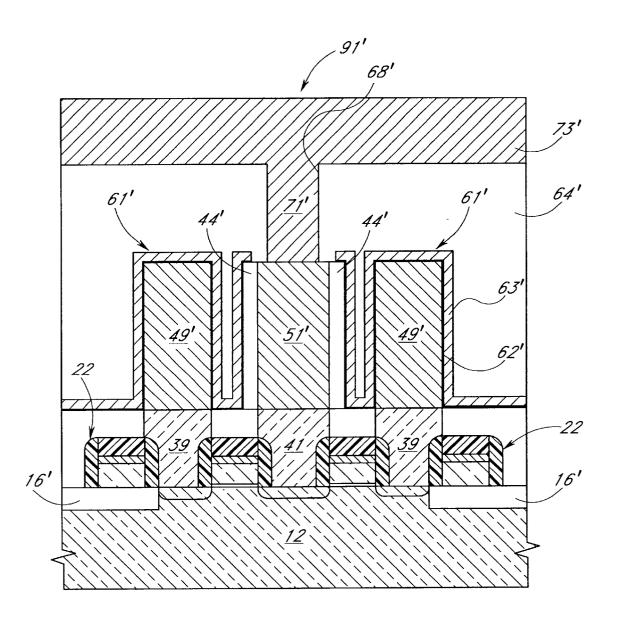

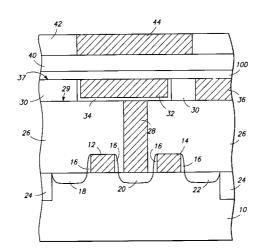

16. United States Patent No. 6,828,683 ("the '683 patent"), titled "Semiconductor Devices, And Semiconductor Processing Methods," was duly and legally issued by the U.S. Patent and Trademark Office on December 7, 2004. A copy of the '683 patent is attached hereto as Exhibit F. Round Rock is the assignee of all rights, title, and interest in the '683 patent, and it possesses all rights to sue and recover for any current or past infringement of the '683 patent.

# COUNT I

# Infringement of U.S. Patent No. 5,986,347

17. Paragraphs 1 through 16 are incorporated by reference as if fully stated herein.

18. The '347 patent is valid and enforceable.

19. The Nintendo Defendants have infringed, and continue to infringe, one or more claims of the '347 patent under 35 U.S.C. § 271(a), either literally and/or under the doctrine of

equivalents, by making, using, selling, and/or offering for sale in the United States, and/or importing into the United States, products encompassed by those claims, including for example, by making, using, selling, offering for sale, and/or importing into the United States all video game products incorporating unlicensed graphical processing units ("GPUs") or any other unlicensed semiconductor component manufactured using a 90nm or later (smaller) process (collectively, the "347 Infringing Products"). The '347 Infringing Products include, but are not limited to, the Nintendo Wii, the Nintendo Wii U, the Nintendo Wii Mini, and the Nintendo 3DS, consoles, systems, and remotes.

20. The Nintendo Defendants' customers (e.g., distributors, retailers, and online vendors) and Nintendo of America directly infringe one or more claims of the '347 patent under 35 U.S.C. § 271(a) by selling, offering to sell, or importing the '347 Infringing Products in or into the United States. The Nintendo Defendants have actively induced infringement of, and continue to actively induce infringement of, one or more claims of the '347 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by selling, importing, and/or offering for sale the '347 Infringing Products to its customers and/or Nintendo of America with the knowledge of the '347 patent and its claims, with knowledge that its customers and/or Nintendo of America will sell, offer to sell, and/or import into the United States the '347 Infringing Products, and with knowledge and specific intent to encourage and facilitate those infringing sales or imports of the '347 Infringing Products through distributing the products to retailers, distributors, and online vendors and creating and disseminating promotional and marketing materials, instructional manuals, product manuals and other technical materials related to the '347 Infringing Products.

21. The Nintendo Defendants have had knowledge of '347 patent and their infringement of that patent since at least December 11, 2014 through a letter sent by Round Rock concerning that infringement.

22. The Nintendo Defendants have infringed, and continue to infringe, at least claims 1, 2, 3, 4, 5, and/or 6 of the '347 patent.

23. Round Rock has been and continues to be damaged by the Nintendo Defendants' infringement of the '347 patent.

24. The Nintendo Defendants have willfully infringed, and continue to willfully infringe, the '347 patent despite having knowledge of the '347 patent at least through Round Rock's December 11, 2014 letter concerning their infringement.

25. The Nintendo Defendants' conduct in infringing the '347 patent renders this case exceptional within the meaning of 35 U.S.C. § 285.

### COUNT II

#### Infringement of U.S. Patent No. 6,147,405

26. Paragraphs 1 through 25 are incorporated by reference as if fully stated herein.

27. The '405 patent is valid and enforceable.

28. The Nintendo Defendants have infringed, and continue to infringe, one or more claims of the '405 patent under 35 U.S.C. § 271(a), either literally and/or under the doctrine of equivalents, by making, using, selling, and/or offering for sale in the United States, and/or importing into the United States, products encompassed by those claims, including for example, by making, using, selling, offering for sale, and/or importing into the United States all video game products incorporating unlicensed GPUs or any other unlicensed semiconductor components manufactured using a 90nm or later (smaller) process (collectively, the "'405

Infringing Products"). The '405 Infringing Products include, but are not limited to, the Nintendo Wii, the Nintendo Wii U, and the Nintendo Wii Mini, consoles, systems, and remotes.

29. The Nintendo Defendants' customers (e.g., distributors, retailers, and online vendors) and Nintendo of America directly infringe one or more claims of the '405 patent under 35 U.S.C. § 271(a) by selling, offering to sell, or importing the '405 Infringing Products in or into the United States. The Nintendo Defendants have actively induced infringement of, and continue to actively induce infringement of, one or more claims of the '405 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by selling, importing, and/or offering for sale the '405 Infringing Products to its customers and/or Nintendo of America with the knowledge of the '405 patent and its claims, with knowledge that its customers and/or Nintendo of America will sell, offer to sell, and/or import into the United States the '405 Infringing Products, and with knowledge and specific intent to encourage and facilitate those infringing sales or imports of the '405 Infringing Products through distributing the products to retailers, distributors, and online vendors and creating and disseminating promotional and marketing materials, instructional manuals, product manuals and other technical materials related to the '405 Infringing Products.

30. The Nintendo Defendants have had knowledge of '405 patent and their infringement of that patent since at least April 24, 2012 through a letter sent by Round Rock concerning that infringement.

31. The Nintendo Defendants have infringed, and continue to infringe, at least claims 1, 2, 3, 6, 7, 8, 9, 10 and/or 12 of the '405 patent.

32. Round Rock has been and continues to be damaged by the Nintendo Defendants' infringement of the '405 patent.

33. The Nintendo Defendants have willfully infringed, and continue to willfully infringe, the '405 patent despite having knowledge of the '405 patent at least through Round Rock's April 24, 2012 letter concerning their infringement.

34. The Nintendo Defendants' conduct in infringing the '405 patent renders this case exceptional within the meaning of 35 U.S.C. § 285.

# COUNT III

### Infringement of U.S. Patent No. 6,358,801

35. Paragraphs 1 through 34 are incorporated by reference as if fully stated herein.

36. The '801 patent is valid and enforceable.

37. The Nintendo Defendants have infringed, and continue to infringe, one or more claims of the '801 patent under 35 U.S.C. § 271(a) and/or 271(g), either literally and/or under the doctrine of equivalents, by making, selling, offering to sell, using, and/or importing into the United States, products made by a process described in those claims, including for example, by making, using, selling, offering for sale, and/or importing into the United States all video game products incorporating unlicensed GPUs or any other unlicensed semiconductor components manufactured using a 90nm or later (smaller) process (collectively, the "'801 Infringing Products"). The '801 Infringing Products include, but are not limited to, the Nintendo Wii, the Nintendo Wii U, the Nintendo Wii Mini, and the Nintendo 3DS consoles, systems, and remotes.

38. The Nintendo Defendants' customers (e.g., distributors, retailers, and online vendors) and Nintendo of America directly infringe one or more claims of the '801 patent under 35 U.S.C. § 271(a) and/or 271(g) by selling, offering to sell, or importing the '801 Infringing Products in or into the United States. The Nintendo Defendants have actively induced infringement of, and continue to actively induce infringement of, one or more claims of the '801

patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by selling, importing, and/or offering for sale the '801 Infringing Products to its customers and/or Nintendo of America with the knowledge of the '801 patent and its claims, with knowledge that its customers and/or Nintendo of America will sell, offer to sell, and/or import into the United States the '801 Infringing Products, and with knowledge and specific intent to encourage and facilitate those infringing sales or imports of the '801 Infringing Products through distributing the products to retailers, distributors, and online vendors and creating and disseminating promotional and marketing materials, instructional manuals, product manuals and other technical materials related to the '801 Infringing Products.

39. The Nintendo Defendants have had knowledge of '801 patent and their infringement of that patent since at least December 11, 2014 through a letter sent by Round Rock concerning that infringement.

40. Round Rock has been and continues to be damaged by the Nintendo Defendants' infringement of the '801 patent.

41. The Nintendo Defendants have infringed, and continue to infringe, at least claims1 and/or 2 of the '801 patent.

42. The Nintendo Defendants have willfully infringed, and continue to willfully infringe, the '801 patent despite having knowledge of the '801 patent at least through Round Rock's December 11, 2014 letter concerning their infringement.

43. The Nintendo Defendants' conduct in infringing the '801 patent renders this case exceptional within the meaning of 35 U.S.C. § 285.

### COUNT IV

# Infringement of U.S. Patent No. 6,455,935

- 44. Paragraphs 1 through 43 are incorporated by reference as if fully stated herein.

- 45. The '935 patent is valid and enforceable.

46. The Nintendo Defendants have infringed, and continue to infringe, one or more claims of the '935 patent under 35 U.S.C. § 271(a), either literally and/or under the doctrine of equivalents, by making, using, selling, and/or offering for sale in the United States, and/or importing into the United States, products encompassed by those claims, including for example, by making, using, selling, offering for sale, and/or importing into the United States all video game consoles incorporating unlicensed GPUs or any other unlicensed semiconductor components manufactured using a 90nm or later (smaller) process (collectively, the "'935 Infringing Products"). The '935 Infringing Products include, but are not limited to, the Nintendo Wii, the Nintendo Wii U, and the Nintendo Wii Mini consoles, systems, and remotes.

47. The Nintendo Defendants' customers (e.g., distributors, retailers, and online vendors) and Nintendo of America directly infringe one or more claims of the '935 patent under 35 U.S.C. § 271(a) by selling, offering to sell, or importing the '935 Infringing Products in the United States. The Nintendo Defendants have actively induced infringement of, and continue to actively induce infringement of, one or more claims of the '935 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by selling, importing, and/or offering for sale the '935 Infringing Products to its customers and/or Nintendo of America with the knowledge of the '935 patent and its claims, with knowledge that its customers and/or Nintendo of America will sell, offer to sell, and/or import into the United States the '935 Infringing Products, and with knowledge and specific intent to encourage and facilitate those infringing

sales or imports of the '935 Infringing Products through distributing the products to retailers, distributors, and online vendors and creating and disseminating promotional and marketing materials, instructional manuals, product manuals and other technical materials related to the '935 Infringing Products.

48. The Nintendo Defendants have had knowledge of '935 patent and their infringement of that patent since at least April 24, 2012 through a letter sent by Round Rock concerning that infringement.

49. The Nintendo Defendants have infringed, and continue to infringe, at least claims 1, 2, 3, 4, 6, 8, 9, and/or 10 of the '935 patent.

50. Round Rock has been and continues to be damaged by the Nintendo Defendants' infringement of the '935 patent.

51. The Nintendo Defendants have willfully infringed, and continue to willfully infringe, the '935 patent despite having knowledge of the '935 patent at least through Round Rock's April 24, 2012 letter concerning their infringement.

52. The Nintendo Defendants' conduct in infringing the '935 patent renders this case exceptional within the meaning of 35 U.S.C. § 285.

### COUNT V

#### Infringement of U.S. Patent No. 6,469,336

53. Paragraphs 1 through 52 are incorporated by reference as if fully stated herein.

54. The '336 patent is valid and enforceable.

55. The Nintendo Defendants have infringed, and continue to infringe, one or more claims of the '336 patent under 35 U.S.C. § 271(a), either literally and/or under the doctrine of equivalents, by making, using, selling, and/or offering for sale in the United States, and/or

importing into the United States, products encompassed by those claims, including for example, by making, using, selling, offering for sale, and/or importing into the United States all video game products incorporating the "Hollywood-1" GPU, the "Hollywood-2" GPU (also known as the Renesas D813302 GPU), and/or the "Latte" GPU (also known as the Renesas D813301 GPU), including but not limited to the Nintendo Wii, the Nintendo Wii U, and the Nintendo Wii Mini video game consoles (collectively, the "336 Infringing Products").

56. The Nintendo Defendants' customers (e.g., distributors, retailers, and online vendors) and Nintendo of America directly infringe one or more claims of the '336 patent under 35 U.S.C. § 271(a) by selling, offering to sell, or importing the '336 Infringing Products in the United States. The Nintendo Defendants have actively induced infringement of, and continue to actively induce infringement of, one or more claims of the '336 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by selling, importing, and/or offering for sale the '336 Infringing Products to its customers and/or Nintendo of America with the knowledge of the '336 patent and its claims, with knowledge that its customers and/or Nintendo of America will sell, offer to sell, and/or import into the United States the '336 Infringing Products, and with knowledge and specific intent to encourage and facilitate those infringing sales or imports of the '336 Infringing Products through distributing the products to retailers, distributors, and online vendors and creating and disseminating promotional and marketing materials, instructional manuals, product manuals and other technical materials related to the '336 Infringing Products.

57. The Nintendo Defendants have had knowledge of the '336 patent and their infringement of that patent since at least August 27, 2013 through email correspondence sent by Round Rock concerning that infringement.

58. The Nintendo Defendants have infringed, and continue to infringe, at least claims1 and 2 of the '336 patent.

59. Round Rock has been and continues to be damaged by the Nintendo Defendants' infringement of the '336 patent.

60. The Nintendo Defendants have willfully infringed, and continue to willfully infringe, the '336 patent despite having knowledge of the '336 patent at least through Round Rock's August 27, 2013 email correspondence concerning their infringement.

61. The Nintendo Defendants' conduct in infringing the '336 patent renders this case exceptional within the meaning of 35 U.S.C. § 285.

#### COUNT VI

# Infringement of U.S. Patent No. 6,828,683

62. Paragraphs 1-61 are incorporated by reference as if fully stated herein.

63. The '683 patent is valid and enforceable.

64. The Nintendo Defendants have infringed, and continue to infringe, one or more claims of the '683 patent under 35 U.S.C. § 271(a), either literally and/or under the doctrine of equivalents, by making, using, selling, and/or offering for sale in the United States, and/or importing into the United States, products encompassed by those claims, including for example, by making, using, selling, offering for sale, and/or importing into the United States all video game products incorporating unlicensed GPUs, processors, or any other unlicensed semiconductor components manufactured using a 90nm or later (smaller) process (collectively, the "'683 Infringing Products"). The '683 Infringing Products include, but are not limited to, the Nintendo Wii, the Nintendo Wii U, the Nintendo Wii Mini, the Nintendo 3DS XL, and the Nintendo 2DS consoles, systems, and remotes.

65. The Nintendo Defendants' customers (e.g., distributors, retailers, and online vendors) and Nintendo of America directly infringe one or more claims of the '683 patent under 35 U.S.C. § 271(a) by selling, offering to sell, or importing the '683 Infringing Products in the United States. The Nintendo Defendants have actively induced infringement of, and continue to actively induce infringement of, one or more claims of the '683 patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, by selling, importing, and/or offering for sale the '683 Infringing Products to its customers and/or Nintendo of America with the knowledge of the '683 patent and its claims, with knowledge that its customers and/or Nintendo of America will sell, offer to sell, and/or import into the United States the '683 Infringing Products, and with knowledge and specific intent to encourage and facilitate those infringing sales or imports of the '683 Infringing Products through distributing the products to retailers, distributors, and online vendors and creating and disseminating promotional and marketing materials, instructional manuals, product manuals and other technical materials related to the '683 Infringing Products.

66. The Nintendo Defendants have had knowledge of the '683 patent and their infringement of that patent since at least December 11, 2014 through a letter sent by Round Rock concerning that infringement.

67. The Nintendo Defendants have infringed, and continue to infringe, at least claims 27, 28, 30, 32, 33, 34, and/or 35 of the '683 patent.

68. Round Rock has been and continues to be damaged by the Nintendo Defendants' infringement of the '683 patent.

69. The Nintendo Defendants have willfully infringed, and continue to willfully infringe, the '683 patent despite having knowledge of the '683 patent at least through Round Rock's December 11, 2014 letter concerning their infringement.

70. The Nintendo Defendants' conduct in infringing the '683 patent renders this case exceptional within the meaning of 35 U.S.C. § 285.

# **Prayer For Relief**

WHEREFORE, Round Rock prays for judgment as follows:

A. That the Nintendo Defendants have directly and/or indirectly infringed each of the Patents-in-Suit;

B. That the Nintendo Defendants have willfully infringed each of the Patents-in-Suit;

B. That Round Rock be awarded all damages adequate to compensate it for the Nintendo Defendants' infringement of the Patents-in-Suit, such damages to be determined by a jury and, if necessary to adequately compensate Round Rock for the infringement, an accounting, and that such damages be trebled and awarded to Round Rock with pre-judgment and post-judgment interest;

C. That this case by declared an exceptional case within the meaning of 35 U.S.C. § 285 and that Round Rock be awarded the attorney fees, costs, and expenses that it incurs prosecuting this action; and

D. That Round Rock be awarded such other and further relief as this Court deems just and proper.

# **Demand For Jury Trial**

Plaintiff Round Rock hereby demands a trial by jury on all issues so triable.

Dated: January 14, 2016

Respectfully submitted,

# FARNAN LLP

/s/ Brian E. Farnan Brian E. Farnan (Bar No. 4089) 919 North Market Street 12th Floor Wilmington, DE 19801 (302) 777-0300 (Telephone) (302) 777-0301 (Facsimile) bfarnan@farnanlaw.com

Paul A. Bondor (admitted *pro hac vice*) Lauren M. Nowierski (admitted *pro hac vice*) Elizabeth Kimmel (admitted *pro hac vice*) Michael Rhodes (admitted *pro hac vice*) DESMARAIS LLP 230 Park Avenue New York, NY 10169 (212) 351-3400 (Telephone) (212) 351-3401 (Facsimile) pbondor@desmaraisllp.com Inowierski@desmaraisllp.com ekimmel@desmaraisllp.com

Counsel for Plaintiff Round Rock Research, LLC Case 1:14-cv-01491-SLR-SRF Document 78 Filed 01/27/16 Page 18 of 104 PageID #: 3976

# EXHIBIT A

Donohoe et al.

#### [54] PROCESSING METHODS OF FORMING CONTACT OPENINGS AND INTEGRATED CIRCUITRY

- [75] Inventors: Kevin G. Donohoe; Kirk D. Prall, both of Boise, Id.

- [73] Assignee: Micron Technology, Inc., Boise, Id.

- [21] Appl. No.: 09/107,930

- [22] Filed: Jun. 30, 1998

#### **Related U.S. Application Data**

- [62] Division of application No. 08/911,311, Aug. 14, 1997.

- [51] Int. Cl.<sup>6</sup> ..... H01L 23/48; H01L 29/46

- [52] U.S. Cl. ..... 257/774; 257/758; 257/760; 257/308

#### [56] **References Cited**

#### U.S. PATENT DOCUMENTS

| 4,488,166 | 12/1984 | Lehrer 257/774        |

|-----------|---------|-----------------------|

| 5,094,900 | 3/1992  | Langley 257/774       |

| 5,180,689 | 1/1993  | Liu et al 437/228     |

| 5,408,130 | 4/1995  | Woo et al 257/774     |

| 5,451,819 | 9/1995  | Koyama 257/774        |

| 5,468,342 | 11/1995 | Nulty et al 156/643.1 |

| 5,665,623 | 9/1997  | Liang et al 438/239   |

#### OTHER PUBLICATIONS

A. Shinohara et al., "A New Self–Aligned Contact Technology for LLD MOS Transistors", Extended Abstracts of the 17th Conference on Solid State Devices and Materials, Tokyo, Japan, 1985, pp. 12–15.

# [11] Patent Number: 5,986,347

# [45] **Date of Patent:** Nov. 16, 1999

Primary Examiner-Teresa M. Arroyo

Assistant Examiner—Hung Van Duong

Attorney, Agent, or Firm—Wells, St. John, Roberts, Gregory & Matkin P.S.

#### [57] ABSTRACT

Methods of forming contact openings over a node location and related integrated circuitry are described. In one aspect of the invention, a node location is formed within a semiconductive substrate adjacent an isolation oxide region. A layer of material is formed over the node location and a contact opening is etched through the layer of material to outwardly expose a node location planar upper surface. In one preferred implementation, the contact opening includes an inner surface portion which faces generally transversely away from the isolation oxide region and which defines an angle with the node location upper surface which is greater at a bottom of the contact opening than at a top of the contact opening. In another preferred implementation, the contact opening includes sidewall portions which define a profile which having a non-uniform degree of taper between the contact opening top and bottom. In another preferred implementation, the tapering of the contact opening is effectuated by modifying at least one etching parameter at an intermediate etching point and continuing the etching to outwardly expose the node location.

#### 7 Claims, 5 Drawing Sheets

U.S. Patent

Nov. 16, 1999

Sheet 4 of 5

U.S. Patent

Nov. 16, 1999

Sheet 5 of 5

5,986,347

5

15

# 1

#### PROCESSING METHODS OF FORMING CONTACT OPENINGS AND INTEGRATED CIRCUITRY

#### RELATED PATENT DATA

This patent resulted from a divisional application of U.S. patent application Ser. No. 08/911,311, filed Aug. 14, 1997, entitled "Processing Methods of Forming Contact Openings and Integrated Circuitry", naming Kevin G. Donohoe and Kirk D. Prall as inventors.

#### TECHNICAL FIELD

This invention relates to methods of forming contact openings and related integrated circuitry.

#### BACKGROUND OF THE INVENTION

Fabrication of integrated circuitry typically involves forming contact openings through an insulative layer to an elevationally lower substrate node location, such as a dif-<sup>20</sup> fusion region which constitutes part of a field effect transistor. Typically, field effect transistors are fabricated on a semiconductor wafer, with selected individual transistors being separated by isolation oxide or field oxide regions. As integrated circuitry dimensions grow smaller and smaller,<sup>25</sup> challenges are presented with respect to the formation of contact openings to substrate node locations.

For example, one type of integrated circuitry is a dynamic random access memory device which includes a plurality of 30 isolation oxide regions over which conductive word lines extend. Conductive word lines are usually covered or insulated with protective nitride caps and sidewalls. A thick layer of oxide typically overlies the word lines. A contact opening etch can be conducted selective relative to the protective caps and sidewalls to achieve self-alignment of the contact opening in a direction perpendicular to the line. However, because such word lines typically overlie isolation oxide regions, and because the insulative layer through which the contact opening is etched usually etches in the same manner as the material from which the isolation oxide regions are formed, e.g. when both are oxides, a problem arises insofar as undesirably etching into the isolation oxide region when the contact openings are formed.

This invention arose out of concerns associated with <sup>45</sup> improving the manner in which contact openings are formed in integrated device fabrication.

#### SUMMARY OF THE INVENTION

Methods of forming contact openings over a node loca- 50 tion and related integrated circuitry are described. In one aspect of the invention, a node location -is formed within a semiconductive substrate adjacent an isolation oxide region. A layer of material is formed over the node location and acontact opening is etched through the layer of material to 55 outwardly expose a node location planar upper surface. In one preferred implementation, the contact opening includes an inner surface portion which faces generally transversely away from the isolation oxide region and which defines an angle with the node location upper surface which is greater 60 at a bottom of the contact opening than at a top of the contact opening. In another preferred implementation, the contact opening includes sidewall portions which define a profile which has a non-uniform degree of taper between the contact opening top and bottom. In another preferred 65 implementation, the tapering of the contact opening is effectuated by modifying at least one etching parameter at an

2

intermediate etching point and continuing the etching to outwardly expose the node location.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Preferred embodiments of the invention are described below with reference to the following accompanying drawings.

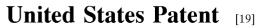

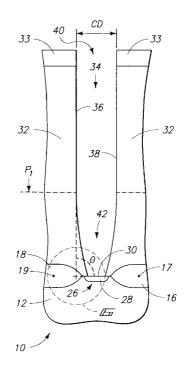

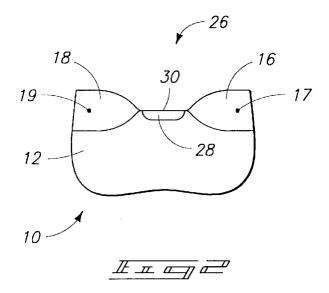

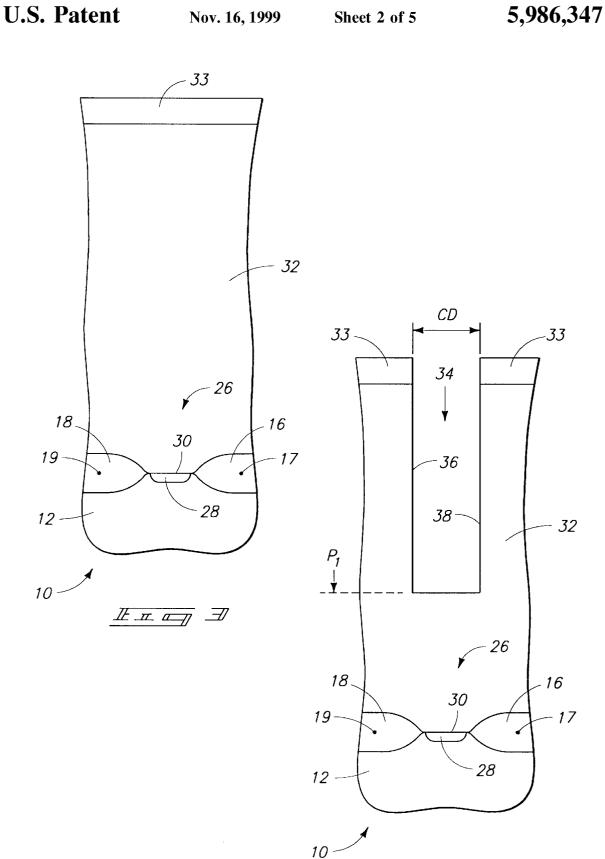

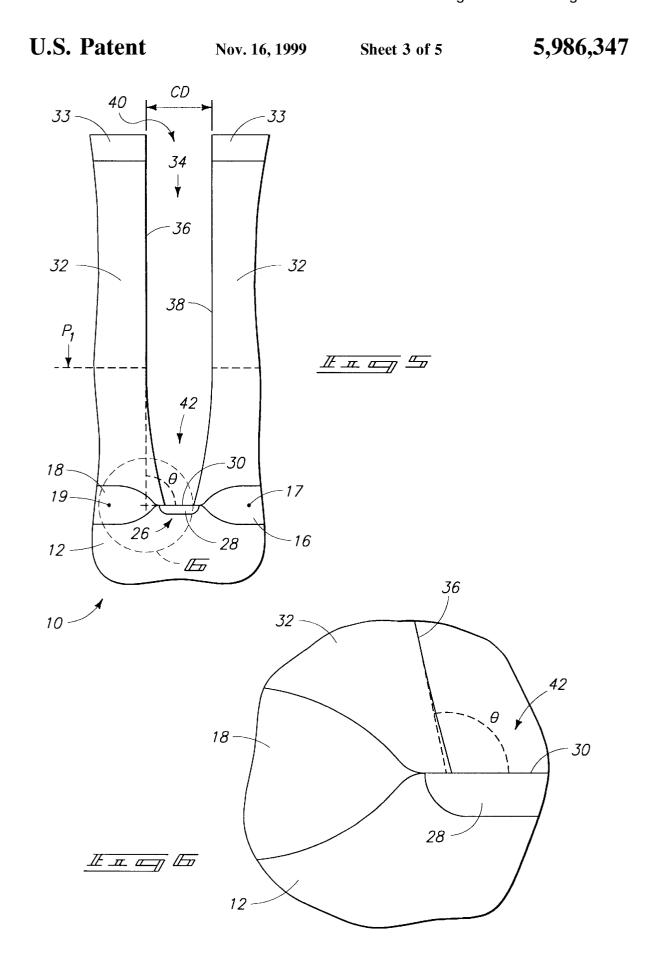

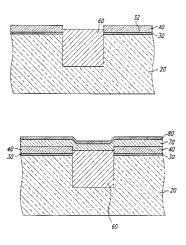

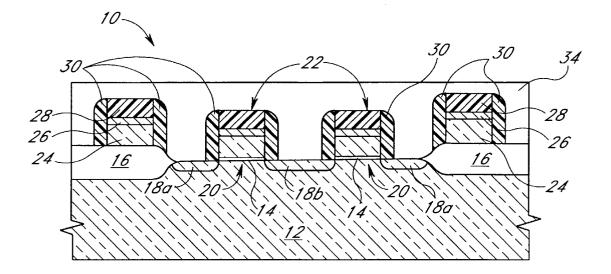

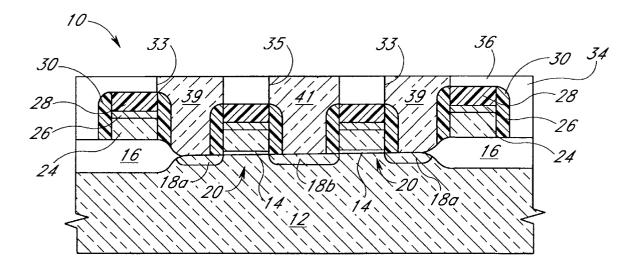

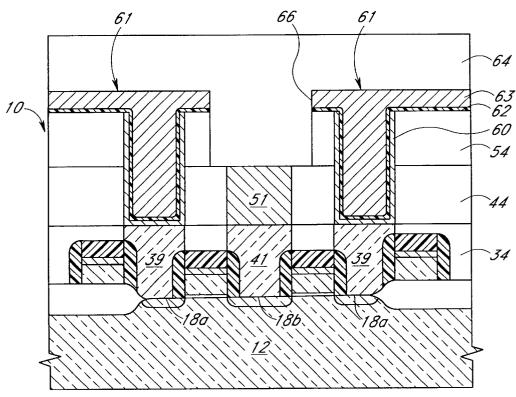

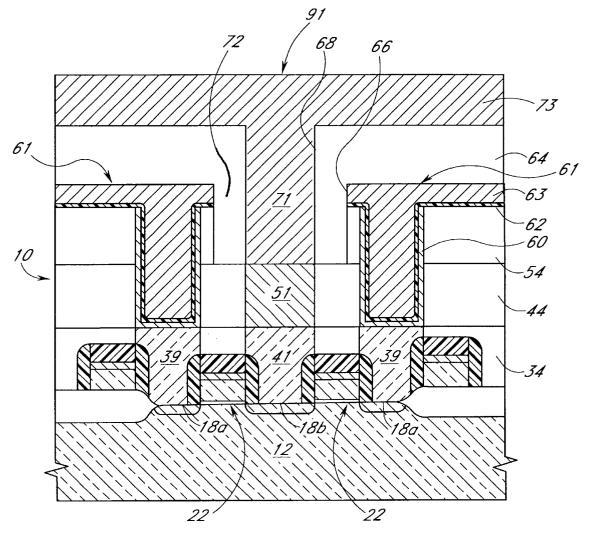

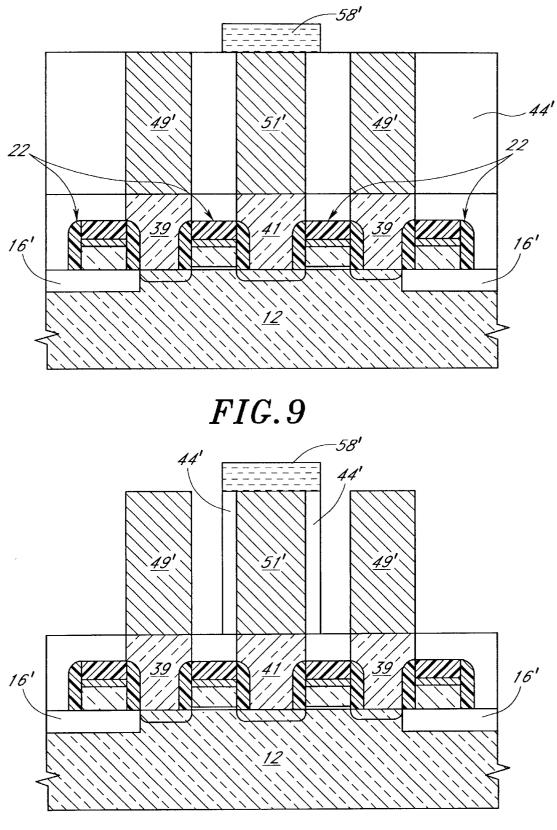

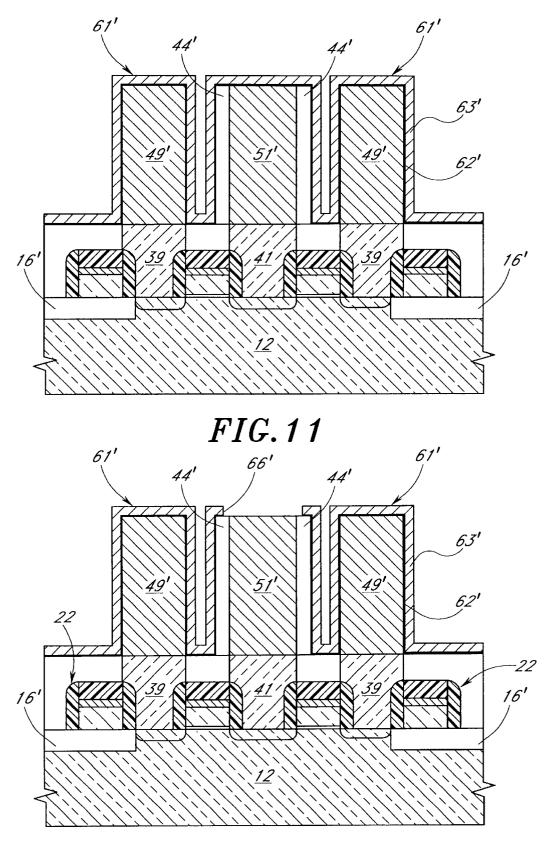

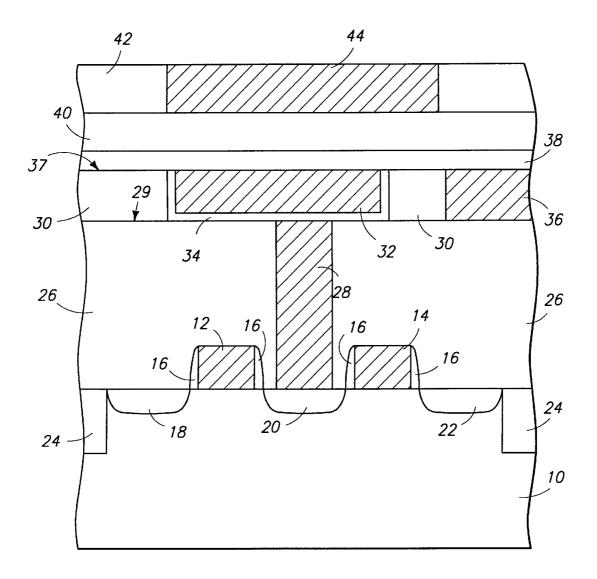

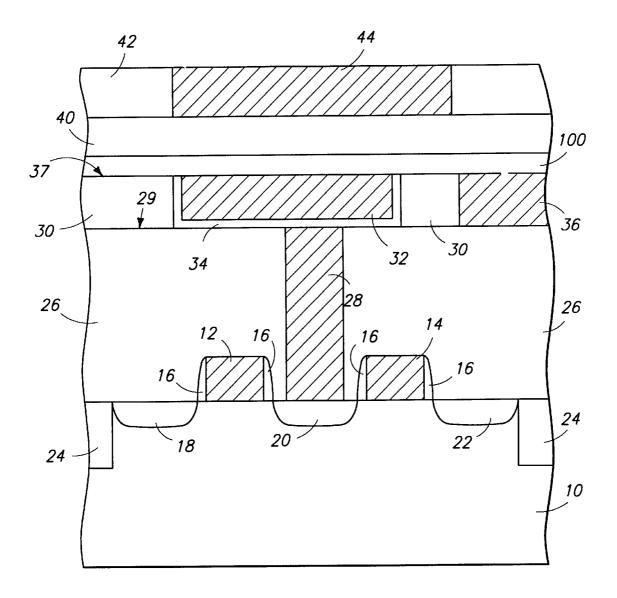

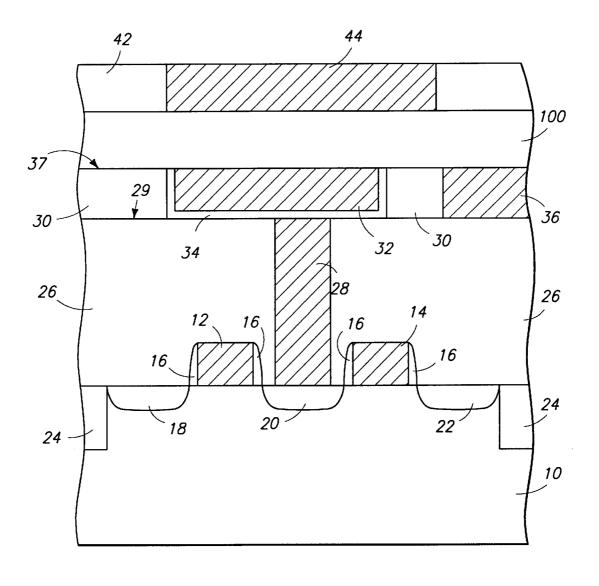

FIG. 1 is a plan view of a semiconductor wafer fragment  $_{10}$  at one processing step in accordance with the invention.

FIG. 2 is a view of the semiconductor wafer fragment taken along line 2-2 in FIG. 1.

FIG. **3** is a view of the FIG. **2** wafer fragment at a processing step subsequent to that shown by FIG. **2**.

FIG. **4** is a view of the FIG. **2** wafer fragment at a processing step subsequent to that shown by FIG. **3**.

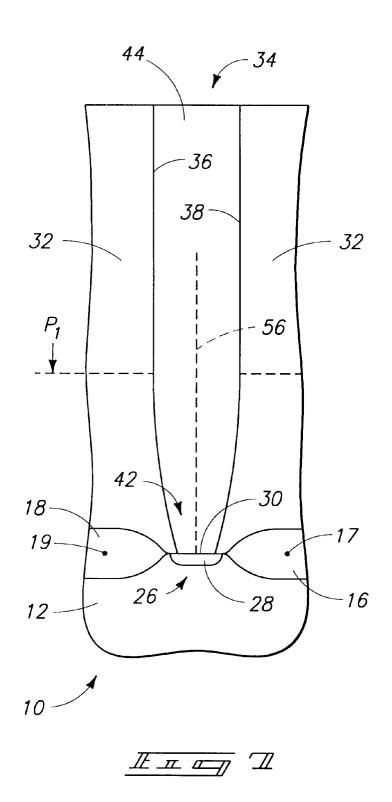

FIG. 5 is a view of the FIG. 2 wafer fragment at a processing step subsequent to that shown by FIG. 4.

FIG. 6 is a view of the FIG. 2 wafer fragment at a processing step subsequent to that shown by FIG. 5.

FIG. 7 is a view of the FIG. 2 wafer fragment at a processing step subsequent to that shown by FIG. 6.

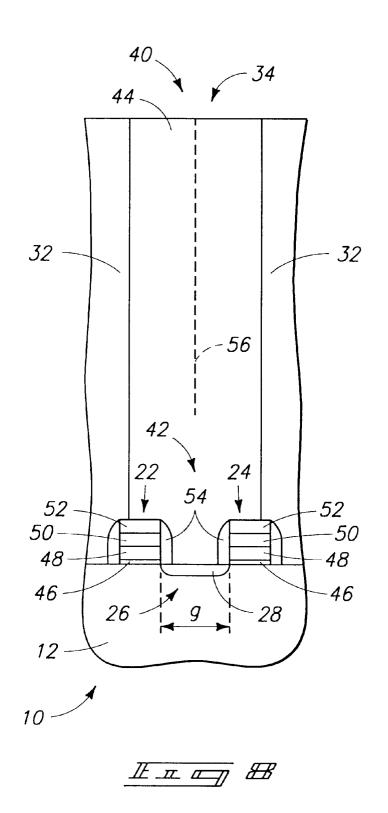

FIG. 8 is a view of the FIG. 1 wafer fragment taken along line 8—8 in FIG. 1 at a processing step subsequent to that shown by FIG. 6.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

This disclosure of the invention is submitted in furtherance of the constitutional purposes of the U.S. Patent Laws "to promote the progress of science and useful arts" (Article 1, Section 8).

Referring to FIGS. 1 and 2, a semiconductor wafer fragment in process is shown generally at 10 and comprises a semiconductive substrate 12. In the context of this document, the term "semiconductive substrate" is defined to mean any construction comprising semiconductive material,

including but not limited to, bulk semiconductive materials such as a semiconductive wafer (either alone or in assemblies comprising other materials thereon), and semiconductive material layers (either alone or in assemblies comprising other materials thereon), and semiconductive substrates ing structure, including, but not limited to, the semiconductive substrates described above. In the illustrated example, an 8-inch wafer was used as the substrate.

A plurality of isolation oxide regions 14, 16, 18, and 20 are formed within substrate 12. The isolation oxide regions are preferably formed through suitable oxidation of substrate 12 through LOCOS techniques. In the illustrated example, the isolation oxide regions are spaced apart over substrate 12 and are formed along longitudinal axes, individual respective axes for isolation regions 16, 18 being indicated at 17, 19. Isolation oxide regions 16, 18 constitute a pair of spaced apart isolation oxide regions whose respective longitudinal axes 17, 19 are generally or substantially parallel to one another.

Referring to FIGS. 1, 2, and 8, a pair of laterally spaced apart conductive lines 22, 24 are formed over substrate 12 and oriented generally transversely of longitudinal axes 17, 19. In the illustrated example, conductive lines 22, 24 overlie respective isolation oxide regions 16, 18. Such conductive lines typically include, as shown in FIG. 8, a thin oxide layer 46, conductive layers 48, 50 (typically comprising polysilicon and a silicide layer respectively), and a protective cap or capping layer 52. Sidewall spacers 54 are

30

also provided. Other conductive line constructions are possible. According to one implementation of the invention, caps 52 and spacers 54 comprise a nitride material which protects the conductive portions of the lines during a subsequent contact opening etch discussed in more detail below. In the illustrated and preferred embodiment, the conductive lines are formed to an elevational thickness of about 2000-3000 Angstroms (not including the elevational thickness of the nitride caps). The preferred nitride caps are formed to an elevational thickness of about 3000 Angstroms so that the total elevational thickness of the individual conductive lines with nitride caps is around about 5000-6000 Angstroms. Additionally, the gap g (FIG. 8) between lines 22, 24 is preferably around 2500 Angstroms or less

A node location 26 is formed within substrate 12 adjacent respective isolation oxide regions 16, 18 and adjacent respective conductive lines 22, 24. In the illustrated and preferred embodiment, node location 26 constitutes a diffusion region 28 (FIG. 2) having a generally planar upper 20 surface 30.

Referring to FIG. 3, a layer of material 32 is formed over substrate 12. Accordingly, layer 32 is formed over and outwardly of node location 26, isolation oxide regions 16, 18, and conductive lines 22, 24 (FIG. 1). A suitable material for layer 32 comprises borophosphosilicate glass (BPSG). An exemplary thickness is about 18,000 Angstroms. Alternately considered and in accordance with one implementation, layer 32 is formed to a thickness over the illustrated conductive lines (FIG. 8) of at least 3000 Angstroms, and preferably greater than 4000 Angstroms. A masking material layer 33, preferably comprising photoresist, is subsequently formed over the substrate.

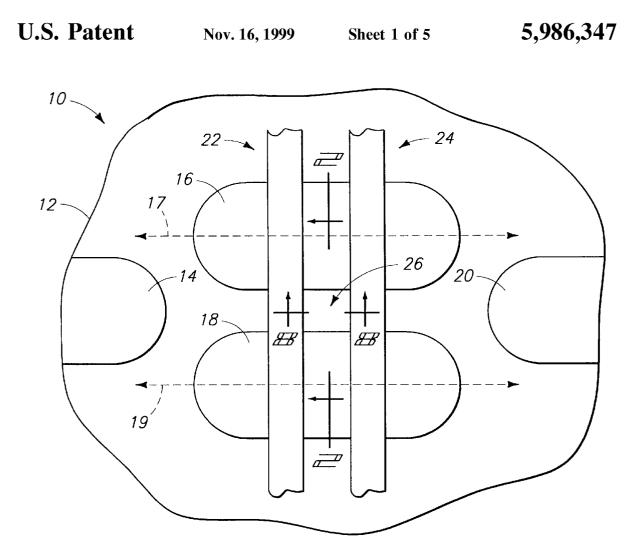

Referring to FIG. 4, photoresist layer 33 is patterned and opening is etched into layer 32 to an intermediate etching point  $P_1$ . The patterning of opening 34 defines an opening lateral width or critical dimension (CD). In the illustrated example, the patterned lateral width of the opening at this point in the etching (i.e. at or adjacent the top of opening 34) is about 0.4  $\mu$ m. The lateral width of the contact opening taken in a direction into the page which is transverse to conductive lines 22, 24 in FIG. 1 is about 0.7  $\mu$ m. Such a transverse lateral width is shown in FIG. 8. Intermediate between the beginning of the etching which forms the contact opening portion and node location 26. The etching of opening 34 defines respective contact opening sidewall portions 36, 38. In this example, the illustrated sidewall portions 36, 38 overlie respective isolation oxide regions 18, 50 16. The preferred etching of the contact opening is conducted in a LAM 9100 etcher and an exemplary etch or etching chemistry which is suitable for conducting this etch is one which is conducted in accordance with the following parameters: 1100 Watts (power applied to an external reactor 55 electrode), 1900 Watts (power applied to an internal wafer carrier), 43 CHF<sub>3</sub>, 20 C<sub>2</sub>HF<sub>5</sub>, 1 C<sub>2</sub>F<sub>6</sub> (units in sccm), 5 mTorr, and 35 seconds. Such etching parameters permit the illustrated opening to be formed to just proximate the nitride caps covering conductive lines 22, 24 (FIG. 1).

Referring to FIG. 5, and in the illustrated and preferred embodiment, at least one etching parameter is modified at or adjacent etching point P1 to taper selected individual contact opening sidewall portions 36, 38 generally transversely away from the nearest respective longitudinal axis 19, 17 of corresponding isolation oxide regions 18, 16. Such etch preferably outwardly exposes node location 26. An exem-

plary etch or etching chemistry which is suitable for conducting this etch is one which is conducted in accordance with the following parameters: 1000 Watts (power applied to the external reactor electrode), 2150 Watts (power applied to the internal wafer carrier), 20 CHF<sub>3</sub>, 90 C<sub>2</sub>HF<sub>5</sub>, 5 C<sub>2</sub>F<sub>6</sub> (units in sccm), 5 mTorr, and 45 seconds. Such etch is preferably increasingly selective to nitride and results in the illustrated tapering of the contact opening. In the preferred embodiment, the etching of the contact opening constitutes 10 etching the contact opening to taper the illustrated sidewall portions in the absence of individual contact opening sidewall contact with any substrate structure. In addition, the etching of the illustrated contact opening preferably does not meaningfully increase the patterned lateral width or CD of 15 the contact opening at or adjacent the top thereof. Accordingly, the illustrated and preferred contact opening has a lateral width dimension adjacent the contact opening top which is essentially equivalent to the original patterned lateral width dimension. Such etching of the contact opening constitutes etching a contact opening, at least of portion of which gradually tapers, without the etching increasing the patterned lateral width or critical dimension of the contact opening. Alternately considered, the patterned lateral width dimension or CD is generally maintained during the etching of the contact opening. Alternately considered, the contact opening has an initial lateral width dimension adjacent the contact opening top which is generally maintained during the etching of the contact opening. Such is different from known etching regimes in which photoresist erosion is utilized to increase the CD of the upper portion of a contact opening when forming the same.

Another exemplary etch or etching chemistry for the above-mentioned LAM 9100 etcher is a multiple-step process which is conducted in accordance with the following an opening 34 which constitutes a portion of a contact 35 parameters: Step 1-1100 Watts (power applied to the external reactor electrode), 1900 Watts (power applied to the internal wafer carrier), 61 CHF<sub>3</sub>, 11.5  $C_2HF_5$ , 1 CH<sub>2</sub>F<sub>2</sub> (units in sccm), 10 mTorr, and 7 seconds; Step 2–1100 Watts (power applied to the external reactor electrode), 900 Watts (power applied to the internal wafer carrier), 61 CHF<sub>3</sub>, 40 11.5 C<sub>2</sub>HF<sub>5</sub>, 1 CH<sub>2</sub>F<sub>2</sub>, 10 mTorr, and 18 seconds; Step 3-1000 Watts (power applied to the external reactor electrode), 1600 Watts (power applied to the internal wafer carrier), 49 CHF<sub>3</sub>; 23 C<sub>2</sub>HF<sub>5</sub>, 5 CH<sub>2</sub>F<sub>2</sub>, 5 mTorr, and 5 etching point P1 can be any intermediate etching point 45 seconds; Step 4-1000 Watts (power applied to the external reactor electrode), 2150 Watts (power applied to the internal wafer carrier), 49 CHF<sub>3</sub>, 23 C<sub>2</sub>HF<sub>5</sub>, 5 CH<sub>2</sub>F<sub>2</sub>, 5 mTorr, and 30 seconds; and Step 5-1000 Watts (power applied to the external reactor electrode), 1500 Watts (power applied to the internal wafer carrier), 49 CHF<sub>3</sub>, 34.5 C<sub>2</sub>HF<sub>5</sub>, 5 CH<sub>2</sub>F<sub>2</sub>, 2 mTorr, and 49 seconds. Other processes having more or less steps can be utilized. One such exemplary process utilizes two steps and is as follows: Step 1-1500 Watts (power applied to the external reactor electrode), 1400 Watts (power applied to the internal reactor electrode), 16 C<sub>2</sub>HF<sub>5</sub> (units in sccm), 50  $\mathrm{CHF}_3,$  1  $\mathrm{CH}_2\mathrm{F}_2,$  120 Argon, 5 mTorr, and 35 seconds; Step 2-1000 Watts (power applied to the external reactor electrode), 1375 Watts (power applied to the internal reactor electrode), 45 C<sub>2</sub>HF<sub>5</sub> (units in sccm), 35 CHF<sub>3</sub>, 20 CH<sub>2</sub>F<sub>2</sub>, 2 mTorr, and 80 seconds. As formed, contact open-60 ing 34 has a contact opening top 40 and a contact opening bottom 42 and an aspect ratio (contact opening height-towidth ratio) of from about 5-30, and preferably around 10. The preferred contact opening also has a degree of taper which is defined between contact opening top 40 and contact 65 opening bottom 42. As shown, the degree of taper is one which varies the width of the contact opening and preferably

results in a contact opening profile with a degree of concavity which is greater nearest contact opening bottom 42 than adjacent contact opening top 40. In the illustrated and preferred embodiment, the degree of taper arcuately varies, increasing as the contact opening reaches node location 26 proximate the bottom most portion of contact opening bottom 42. An exemplary contact opening width adjacent contact opening bottom 42 of FIG. 5 is around 0.2  $\mu$ m.

Alternately considered, contact opening 34 as shown in FIG. 5 defines a profile which lies in or along a plane which is taken through the contact opening and which is both generally transverse the isolation oxide regions' longitudinal axes 17, 19, (FIG. 1) and generally transverse the node location planar upper surface 30. Such profile is also taken through the contact opening and in a plane which is parallel to either of conductive lines 22, 24 (FIG. 1). Such profile, when viewed from top-to-bottom, includes a profile portion which tapers generally arcuately toward node location 26. The illustrated profile defines a non-uniform degree of taper between contact opening top 40 and contact opening bottom 20 42. The contact opening is preferably narrower at or adjacent contact opening bottom 42 than at or adjacent contact opening top 40. As formed, the contact opening profile is generally bowed arcuately inwardly proximate contact opening bottom 42.

Alternately considered and with reference to FIGS. 5 and 6, contact opening 34 includes a pair of inner surface portions which correspond to sidewall portions 36, 38. The inner surface portions face generally transversely away from the respective nearest of the isolation oxide regions' longitudinal axes 19, 17, and extend between contact opening top 40 and contact opening bottom 42. Inner surface portions 36, 38 define an angle with node location upper surface 30. A representative angle  $\theta$  is shown for inner surface portion 36 at two different locations relative to the contact opening. A 35 first location is shown in FIG. 5 and corresponds to the angle formed between inner surface portion 36 and node location planar surface 30 adjacent contact opening top 40. A second location is shown in FIG. 6 and corresponds to the angle formed between inner surface portion 36 and node location 40 planar surface 30 adjacent contact opening bottom 42. The angle  $\theta$  is greater adjacent contact opening bottom 42 (FIG. 6) than at or adjacent contact opening top 40 (FIG. 5). As shown in FIG. 5,  $\theta$  is generally around about 90°. As shown in FIG. 6, however,  $\theta$  is generally greater than 90°. Accordingly, the contact opening inner surface portions 36, 38 generally taper between the contact opening top and bottom and have generally arcuate bottom regions into the direction of node location upper surface 30. Such tapering regions 16, 18 when the contact opening is formed.

Referring to FIG. 7, a plug 44 of conductive material is formed or disposed within contact opening 34 and forms an electrical connection with node location 26.

and 8, a multi-directional, self-aligned contact opening 34 is formed over node location 26. According to one aspect of the invention, a first material 32 (FIG. 3) through which a contact opening is to be etched is formed over the substrate. Substrate 12 includes at least one substrate feature which 60 comprises a second material and over which first material 32 is formed. In a preferred implementation, the substrate feature comprises a conductive line such as exemplary line 22, or exemplary line pairs 22, 24. The second material is preferably different from first material 32 and accommo-65 dates and facilitates self-alignment of the contact opening in a first alignment direction. An exemplary first alignment

direction is illustrated in FIG. 8 and is defined, in part, by the plane of the page upon which FIG. 8 appears, and corresponds to line 8-8 in FIG. 1. Where first material 32 comprises an oxide material such as BPSG, the second material can comprise a nitride material such as the material which is utilized to form spacers 54 and/or caps 52. Exemplary oxides for first material 32 also include silicon suboxide  $(SiO_{<2})$  and SiO<sub>2</sub>. Exemplary nitride material for the second material includes  $Si_Z O_X N_v$ , such as  $Si_3 N_4$ . Other materials are, of course, possible.

Contact opening 34 is preferably etched through first material 32 to expose node location 26. As so etched, the contact opening has sidewalls which, in one implementation, include portions in the first alignment direction (FIG. 8) which comprise the second material from which spacers 54 are formed. FIG. 7 illustrates a second alignment direction which is different from the first alignment direction. The illustrated second alignment direction is defined, in part, by the plane of the page upon which FIG. 7 appears, and corresponds to line 2-2 in FIG. 1. The illustrated second alignment direction is generally transverse the first alignment direction. In accordance with one implementation, the etched contact opening includes a contact opening center 56 and selected portions of the contact opening curve inwardly toward the contact opening center in the second alignment direction of FIG. 7. In a preferred implementation, the selected portions of the contact opening which curve inwardly do so at an increasing rate as the contact opening reaches contact opening bottom 42. Bottom portions of the illustrated and preferred inwardly curved portions of FIG. 7 are disposed laterally adjacent the illustrated contact opening second material portions 54 of FIG. 8. It will be appreciated that contact openings having other profiles in the first and second directions can be formed. For example, referring to FIG. 8, a contact opening can be formed to have a profile which comprises portions of only one of the illustrated conductive lines. An exemplary contact opening could, accordingly, have one of its sidewalls formed along line 56.

In accordance with one implementation, the abovedescribed contact opening is etched utilizing a first set of etching parameters which enables at least a portion of the contact opening to be etched. At some point in the etching of the contact opening, at least one of the etching parameters 45 is changed and additional portions of the contact opening are etched. One effect of changing the etching parameters is that the above-described FIG. 7 contact opening selected portions taper or curve inwardly on themselves and toward contact opening center 56. Exemplary etching parameters effectively minimizes or eliminates etching into isolation 50 are discussed above in more detail. Hence, in accordance with the methodology described immediately above, a selfaligned contact opening which enables alignment in multiple directions is achieved.

The above described methodology has particular applica-Alternately considered, and with reference to FIGS. 1, 7, 55 tion in connection with the fabrication of integrated circuit memory devices, and in particular with 256M DRAM circuitry. In such case, the etching of the illustrated contact opening could constitute etching a bit line contact opening, a capacitor container opening, or some other opening to a substrate node location. Other areas of application are possible.

> In compliance with the statute, the invention has been described in language more or less specific as to structural and methodical features. It is to be understood, however, that the invention is not limited to the specific features shown and described, since the means herein disclosed comprise preferred forms of putting the invention into effect. The

40

45

invention is, therefore, claimed in any of its forms or modifications within the proper scope of the appended claims appropriately interpreted in accordance with the doctrine of equivalents.

We claim:

1. An integrated circuitry device comprising:

- a semiconductive substrate;

- a field isolation oxide region received within the substrate and having a longitudinal axis;

- a node location received within the substrate adjacent the field isolation oxide region and having a generally planar upper surface;

- a layer of insulating material disposed over the substrate;

- a contact opening to the node location received within the 15 layer of insulating material, the contact opening having a top and a bottom within the layer of insulating material and a contact opening inner surface portion within the layer of insulating material which faces generally transversely away from the isolation oxide 20 longitudinal axis and which extends between the top and bottom within the layer of insulating material, the contact opening inner surface portion joining with the generally planar upper surface of the node location and defining an angle with the node location generally 25 planar upper surface which is greater at the contact opening bottom within the layer of insulating material than at the contact opening top within the layer of insulating material; and

- conductive material disposed within the contact opening <sup>30</sup> and forming an electrical connection with the node location.

2. The integrated circuitry device of claim 1, wherein the contact opening inner surface portion generally tapers between the contact opening top and bottom. 35

**3**. The integrated circuitry device of claim **1**, wherein the contact opening inner surface portion is bowed inwardly proximate the node location upper surface.

4. The integrated circuitry device of claim 1 further comprising:

- a second field isolation oxide region received within the substrate and having a longitudinal axis which is generally parallel to the first mentioned longitudinal axis; and

- a second contact opening inner surface portion which faces generally away from the longitudinal axis of the second isolation oxide region and toward the first mentioned contact opening inner surface portion, the

8

second contact opening inner surface portion defining an angle with the node location upper surface which is greater at the contact opening bottom than at the contact opening top.

5. The integrated circuitry of claim 1, wherein there is only insulating material between the entirety of the conductive material within the contact opening and the field isolation oxide region.

6. An integrated circuitry device comprising:

- a semiconductive substrate;

- a field isolation oxide region received within the substrate and having a longitudinal axis;

- a node location received within the substrate adjacent the field isolation oxide region and having a generally planar upper surface;

- a single layer of insulating material disposed over the substrate;

- a contact opening to the node location received within the single layer of insulating material, the contact opening having a top and a bottom within the single layer of insulating material and a contact opening inner surface portion within the single layer of insulating material which faces generally transversely away from the isolation oxide longitudinal axis and which extends between the top and bottom within the single layer of insulating material, the contact opening inner surface portion joining with the generally planar upper surface of the node location and defining an angle with the node location generally planar upper surface which is greater at the contact opening bottom within the single layer of insulating material than at the contact opening top within the single layer of insulating material; and

- conductive material disposed within the contact opening and forming an electrical connection with the node location, and wherein there is no conductive line disposed between the entirety of the conductive material within the contact opening and the field isolation oxide region.

7. The integrated circuitry device of claim 6 further comprising a second field isolation oxide region received within the substrate and having a longitudinal axis and being spaced from the first-mentioned field isolation oxide region, and wherein there is no conductive material disposed between the entirety of the conductive material within the contact opening and the second field isolation oxide region.

\* \* \* \* \*

Case 1:14-cv-01491-SLR-SRF Document 78 Filed 01/27/16 Page 29 of 104 PageID #: 3987

# EXHIBIT B

# United States Patent [19]

# Hu

#### [54] ASYMMETRIC, DOUBLE-SIDED SELF-ALIGNED SILICIDE AND METHOD OF FORMING THE SAME

- [75] Inventor: Yongjun Jeff Hu, Boise, Id.

- [73] Assignee: Micron Technology, Inc., Boise, Id.

- [21] Appl. No.: 09/026,104

- [22] Filed: Feb. 19, 1998

- [51] Int. Cl.<sup>7</sup> ..... H01L 23/58; B32B 15/04

#### [56] References Cited

#### **U.S. PATENT DOCUMENTS**

| 4,521,952 | 6/1985 | Riseman 29/590       |

|-----------|--------|----------------------|

| 4,605,947 | 8/1986 | Price et al 29/78    |

| 4,994,402 |        | Chiu 437/41          |

| 5,032,233 | 7/1991 | Yu et al 204/192.28  |

| 5,043,300 | 8/1991 | Nulman 437/200       |

| 5,084,406 | 1/1992 | Rhodes et al 437/52  |

| 5,094,977 | 3/1992 | Yu et al 437/174     |

| 5,147,819 | 9/1992 | Yu et al 437/173     |

| 5,187,122 | 2/1993 | Bonis 437/200        |

| 5,196,360 |        | Doan et al 437/41    |

| 5,236,865 | 8/1993 | Sandhu et al 437/174 |

| 5,278,098 | 1/1994 | Wei et al 437/192    |

(List continued on next page.)

#### FOREIGN PATENT DOCUMENTS

60-10673 1/1985 Japan .

#### OTHER PUBLICATIONS

Jeong Soo Byun, Hak Nam Kim et al., "Formation of a large grain sized TiN layer using  $TiN_x$ , the epitaxial continuity at the Al/TiN interface ...", J. Appl. Phys. 78(3), Aug. 1, 1995, pp. 1719–1724.

# [11] **Patent Number:** 6,147,405

### [45] **Date of Patent:** Nov. 14, 2000

Jeong Soo Byun, "Epitaxial C49–TiSi<sub>2</sub> Formation on (100)Si Substrate Using TiN<sub>x</sub> and Its Electrical Characteristics as a Shallow Contact Metallization", J. Electrochem. Soc., vol. 143, No. 6, Jun. 1996, pp. 1984–1991.

Jeong S. Byun, Kwan G. Rha et al., "Epitaxial TiSi<sub>2</sub> Growth on Si(100) From Reactive Sputtered TiN<sub>x</sub> and Subsequent Annealing", Materials Research Soc. Proceedings, vol. 355, Pittsburgh, 1995, pp. 465–470 (No Month).

Jeong Soo Byun, Jun Ki Kim et al., "W as a Bit Line Interconnection in Capacitor–Over–Bit–Line (COB) Structured Dynamic Random Access Memory (DRAM) and Feasible Diffusion Barrier Layer", Jpn. J. Appl. Phys. vol. 35 (1996), pp. 1086–1089 (No Month).

Jeong Soo Byun, Chang Reol Kim et al., "TiN/TiSi<sub>2</sub> Formation Using TiN<sub>x</sub> Layer and Its Feasibilities in ULSI", Jpn. J. Appl. Phys. vol. 35 (1995), pp. 982–986 (No Month).

Primary Examiner—Deborah Jones

Assistant Examiner-Stephen Stein

Attorney, Agent, or Firm—Knobbe, Martens, Olson & Bear, LLP.

#### [57] ABSTRACT

Disclosed are structures and processes which are related to asymmetric, self-aligned silicidation in the fabrication of integrated circuits. A pre-anneal contact stack includes a silicon substrate, a metal source layer such as titanium-rich titanium nitride (TiN<sub>x</sub>), and a silicon layer. The metal nitride layer is deposited on the substrate by sputtering a target metal reactively in nitrogen and argon ambient. A N:Ar ratio is selected to deposit a uniform distribution of the metal nitride in an unsaturated mode (x<1) over the silicon substrate. The intermediate substrate structure is sintered to form a metal silicide. The silicidation of metal asymmetrically consumes less of the underlying silicon than the overlying silicon layer. The resulting structure is a mixed metal silicide/nitride layer which has a sufficient thickness to provide low sheet resistance without excessively consuming the underlying substrate. A metal nitride of maximum bulk resistivity within the unsaturated (metal-rich) realm is chosen for maximizing asymmetry in the silicidation.

#### 13 Claims, 10 Drawing Sheets

Case 1:14-cv-01491-SLR-SRF Document 78 Filed 01/27/16 Page 31 of 104 PageID #: 3989

# **6,147,405** Page 2

| U.S. PATENT DOCUMENTS |                     |           |        | Mogami 438/303         |

|-----------------------|---------------------|-----------|--------|------------------------|

| 5 341 016 8/1004      | Prall et al 257/412 | 5,656,546 | 8/1997 | Chen et al 438/586     |

|                       | Cheffings           | 5,756,394 | 5/1998 | Manning 438/618        |

|                       | Chin et al          | 5,856,237 | 1/1999 | Ku 438/683             |

|                       | Wuu et al           | 5,888,903 | 3/1999 | O'Brien et al 438/649  |

| · · ·                 | Wang et al 437/24   | 5,945,350 | 8/1999 | Violette et al 438/706 |

Nov. 14, 2000

Sheet 8 of 10

ATOMIC CONCENTRATION

Case 1:14-cv-01491-SLR-SRF Document 78 Filed 01/27/16 Page 40 of 104 PageID #: 3998

| <b>U.S. Patent</b> Nov. 14, 2000 | Sheet 9 of 10 | 6,147,405 |

|----------------------------------|---------------|-----------|

|----------------------------------|---------------|-----------|

FIG. 6A

Case 1:14-cv-01491-SLR-SRF Document 78 Filed 01/27/16 Page 41 of 104 PageID #: 3999

| U.S. Patent | U.S. | Patent |

|-------------|------|--------|

|-------------|------|--------|

Nov. 14, 2000

Sheet 10 of 10

## 6,147,405

FIG. 6B

6,147,405

30

35

50

60

65

#### ASYMMETRIC, DOUBLE-SIDED SELF-ALIGNED SILICIDE AND METHOD OF FORMING THE SAME

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to fabrication of semiconductor circuit devices. More particularly, the present invention is directed to self-aligned silicide structures and meth-10 ods of forming the same without excessive consumption of underlying silicon.

2. Description of Related Art

As is well known in processing integrated circuits, electrical contacts must be made among circuit nodes, such as 15 isolated device active regions formed within a single-crystal silicon substrate. As the contact dimensions of devices become smaller, the contact resistance and the sheet resistance of the contacts increase. In this regard, refractory metal suicides have been used for local interconnections to 20 provide low resistance electrical contacts between device active regions within the silicon substrate.

One common method of forming metal silicides is a self-aligned silicide process, often referred to as salicidation. 25 A thin layer of refractory metal, such as titanium, is deposited over a dielectric area and through contact openings formed on the dielectric area to contact underlying silicon circuit elements, such as source and drain active regions formed within a silicon substrate. The structure is generally annealed to form a silicide, such as titanium silicide (predominantly TiSi<sub>2</sub>) at a high temperature. During the anneal, the deposited titanium reacts with the silicon in the contact to form TiSi2 at the contact openings. Titanium which overlies the dielectric area does not form TiSi2, as the titanium does not contact any silicon. The process is referred to as "self-aligned" because the silicide is formed only where the metal layer contacts silicon, for example, through the contact openings. After the first annealing, the unreacted titanium may be removed in a wet etch, and a postsilicidation anneal is performed to lower the sheet resistance of the silicide to acceptable levels. The final annealing converts titanium silicide from the C49 phase to the lower resistance C54 phase. This self-aligned silicide is often referred to by the short form "salicide."

In the salicidation process, silicon from the contact regions of the substrate diffuses upward into the titanium layer. Similarly, titanium diffuses into the underlying active areas of the silicon substrate. Titanium and silicon react with each other to form a silicide thick enough to provide low sheet resistance. As a result, the doped active area of the silicon substrate becomes thinner due to the consumption of silicon during the reaction. The resultant silicide is said to intrude or sink into the substrate. Over-consumption of the underlying silicon can be problematic for any silicon circuit element, tending to cause voids, and thus device failures. Where contact is made to a shallow junction active area of a silicon substrate, salicide contacts of sufficient thickness cannot be formed without completely destroying a junction.

A need, therefore, exists for an interconnect and method of fabricating the same, which provides the advantages of salicide interconnects without excessive consumption of underlying silicon to which contact is made.

#### SUMMARY OF THE INVENTION

The aforementioned needs are satisfied by several aspects of the present invention.

In accordance with one aspect of the present invention, a method is provided for forming a self-aligned silicide contact on a silicon substrate. The method includes forming a contact window through an insulating layer over the silicon substrate, thereby exposing a portion of the silicon substrate. A metal nitride layer is deposited over the exposed portion of the silicon substrate. A silicon layer is formed over the metal nitride layer.

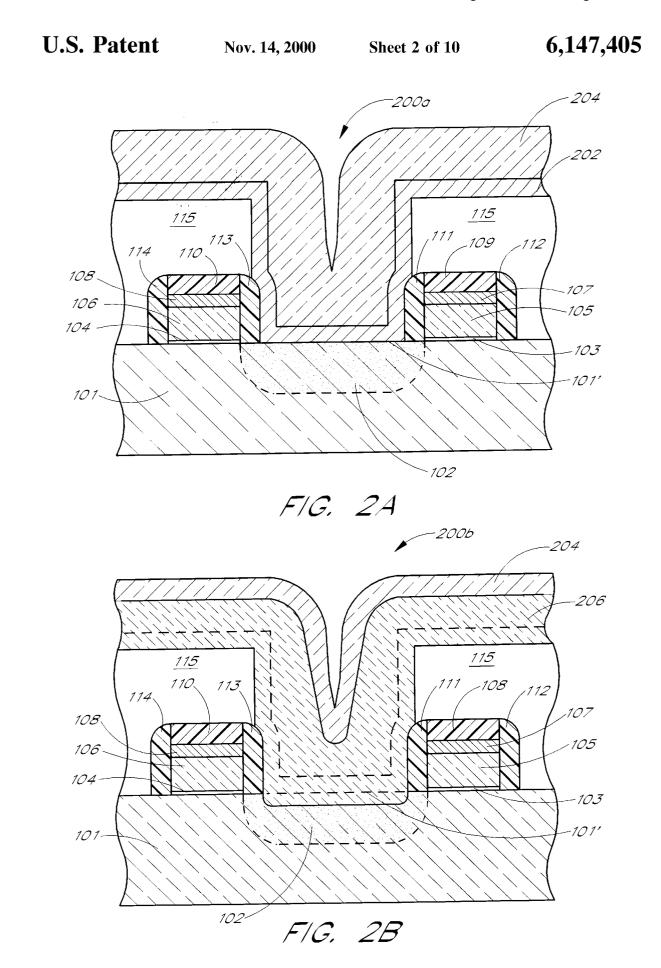

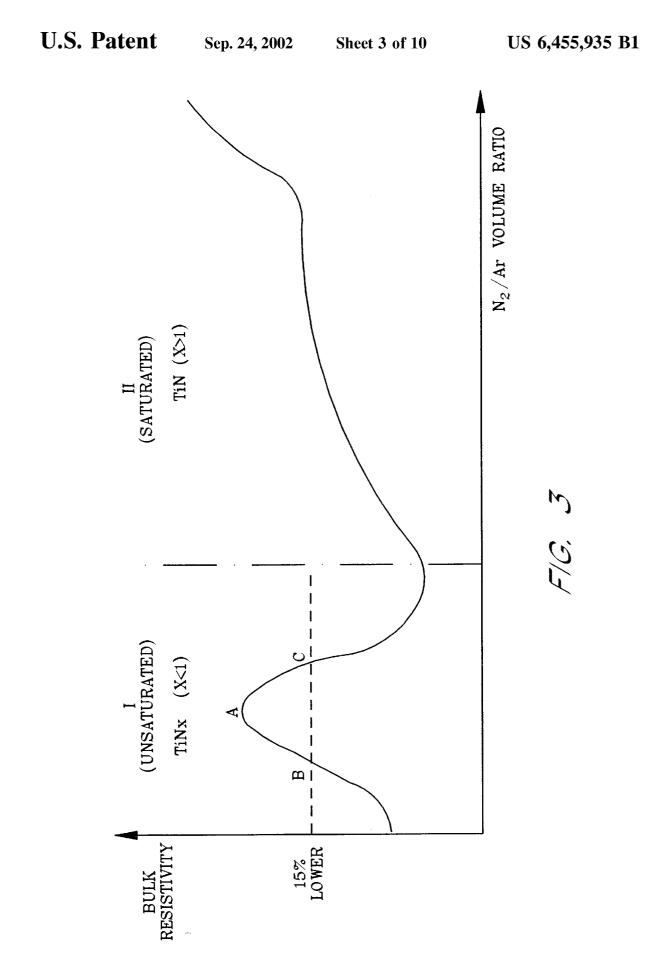

In accordance with another aspect of the present invention, a method is provided for forming a metal source layer, which incorporates a uniform distribution of an impurity and a metal, between silicon structures in an integrated circuit. The method includes selecting a sputtering ambient to maximize bulk resistivity for a metal-rich class of layers incorporating the impurity and the metal. A metallic target is sputtered in the selected ambient.

In accordance with another aspect of the present invention, a method is provided for forming a silicide interconnect over a silicon substrate. The method includes selecting a metal layer incorporating an impurity to a level below saturation. The metal layer has a bulk resistivity within about 15% of the maximal resistivity for unsaturated metal layers having the same metal and impurity. The selected layer is deposited over the silicon substrate, and the selected layer and the substrate ire sintered.

In accordance with another aspect of the present invention, a method is provided for forming a self-aligned silicide contact to a semiconductor substrate. The method includes opening a contact in an insulating layer to expose an active region of the substrate. A refractory metal source layer is deposited into the contact directly over the active region of the substrate. A silicon source layer is deposited directly over the refractory metal source layer. A silicidation is then performed to form the self-aligned silicide contact. The silicidation preferentially consumes silicon from the silicon source layer as compared to silicon from the substrate in a ratio of greater than about 1.2:1.

In accordance with another aspect of the present invention, an intermediate substrate assembly is provided. The assembly includes a silicon substrate, a metal nitride layer directly over the silicon substrate, and a silicon layer directly over the metal nitride layer. In accordance with a preferred embodiment, this intermediate assembly is sintered to form a silicide contact.

In accordance with another aspect of the present 45 invention, an integrated circuit is provided, including a silicon substrate, an insulating layer formed over the silicon substrate with a contact opening formed in the insulating layer, and a conductive contact directly contacting the silicon substrate within the contact opening. The contact includes metal silicide uniformly interspersed with metal nitride.

In accordance with another aspect of the present invention, an integrated circuit includes a silicon substrate and a self-aligned contact. The contact includes a metal 55 silicide, and the extends into the substrate below the upper surface of the substrate by an amount less than about 30% of the contact thickness.

In accordance with another aspect of the present invention, a self-aligned silicide contact is provided. The contact extends below a substrate surface into a shallow junction transistor active area, which has a junction depth of no more than about 1,000 Å. The contact extends below the substrate surface by no more than about 30% of the junction depth.

These and other features of the present invention will become more fully apparent from the following description and claims.

10

15

30

35

40

45

60

#### BRIEF DESCRIPTION OF THE DRAWINGS

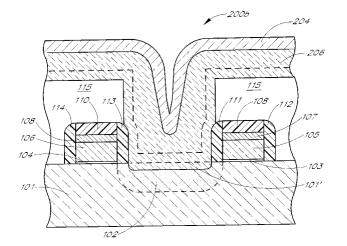

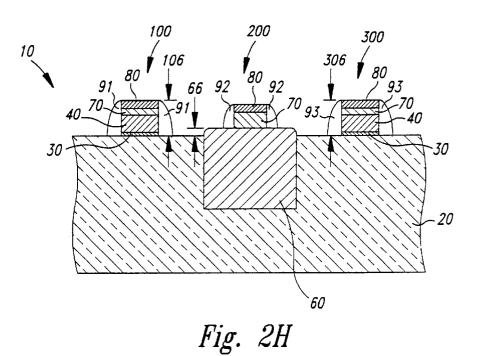

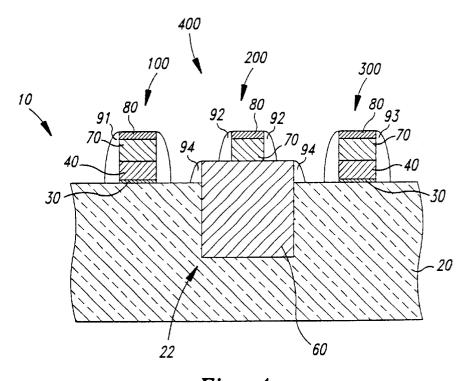

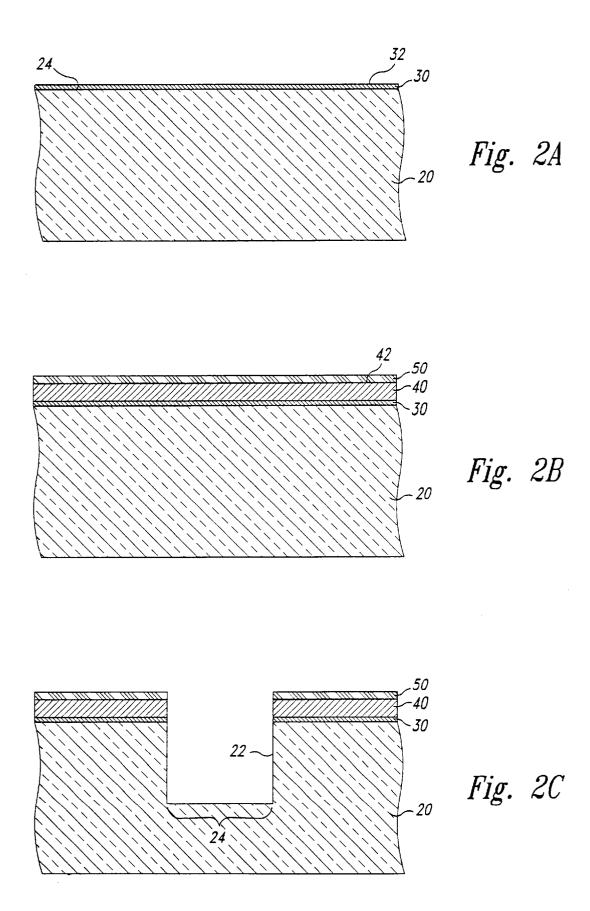

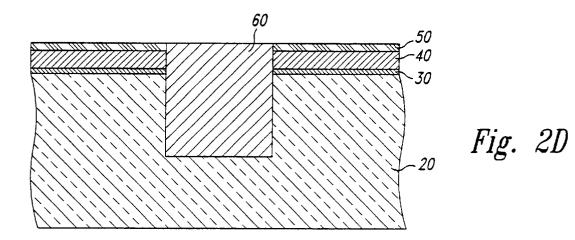

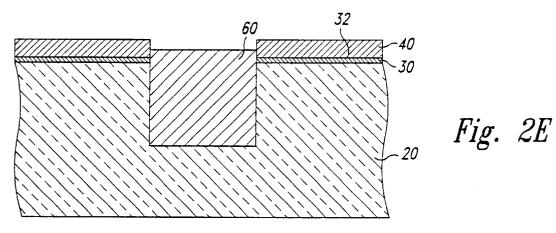

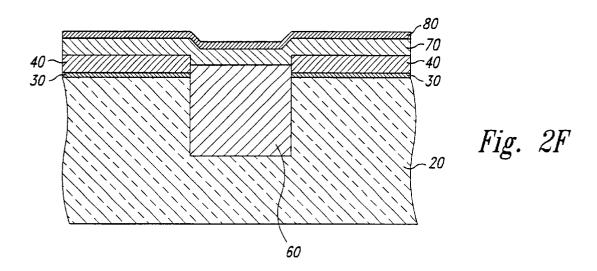

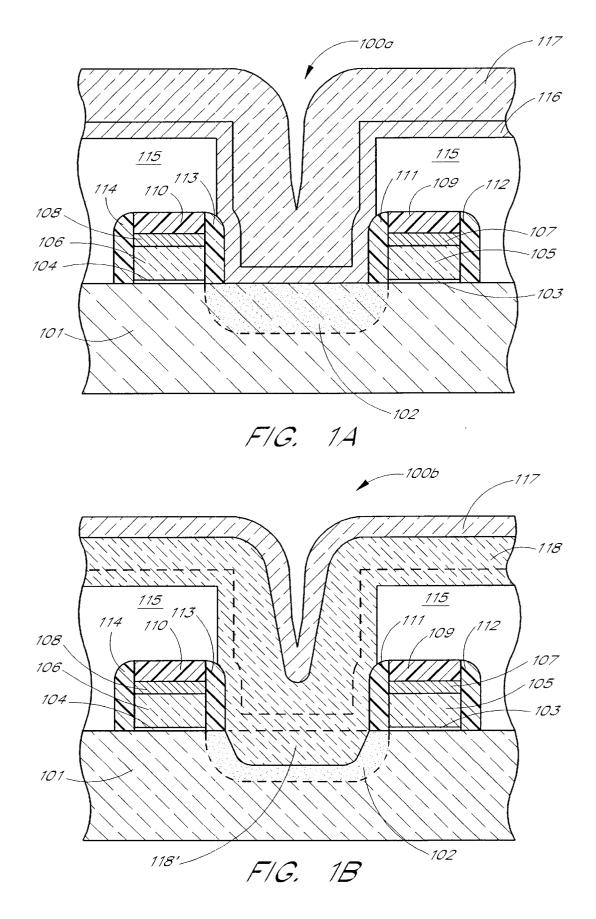

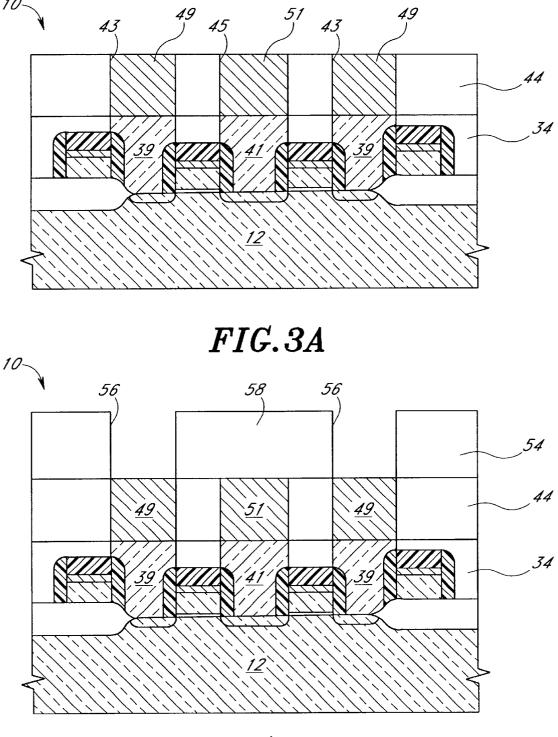

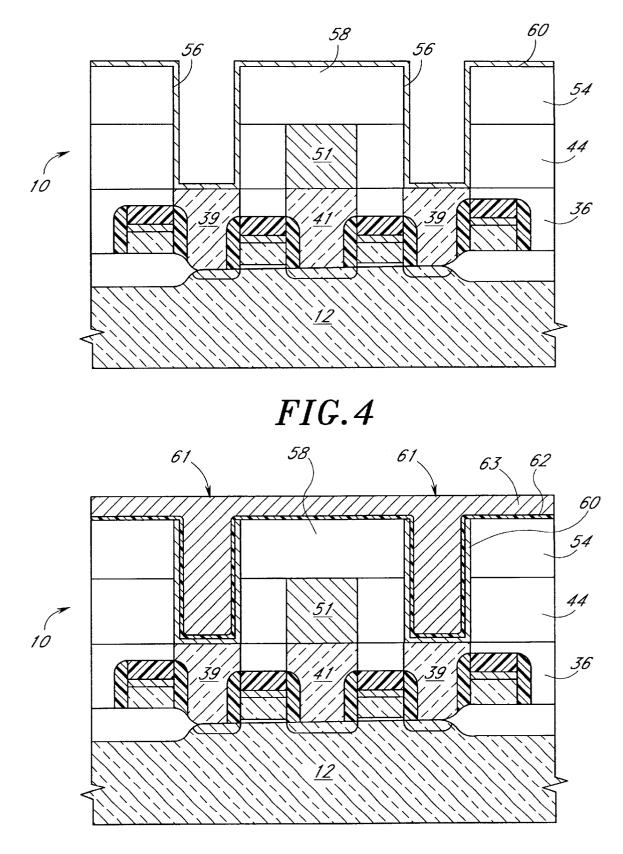

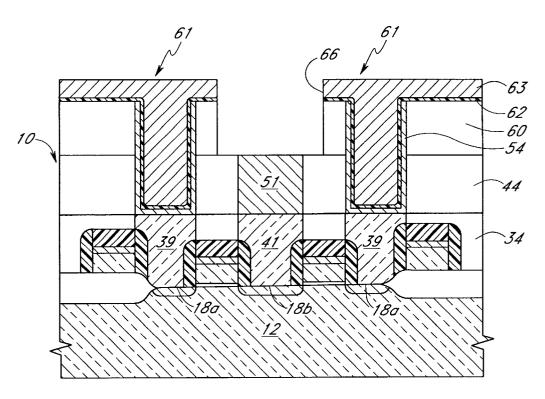

FIGS. 1A and 1B are partial schematic sectional views of an integrated circuit, illustrating a double-sided salicidation. FIGS. 1A and 1B respectively show silicon substrate subassemblies before annealing and after annealing.

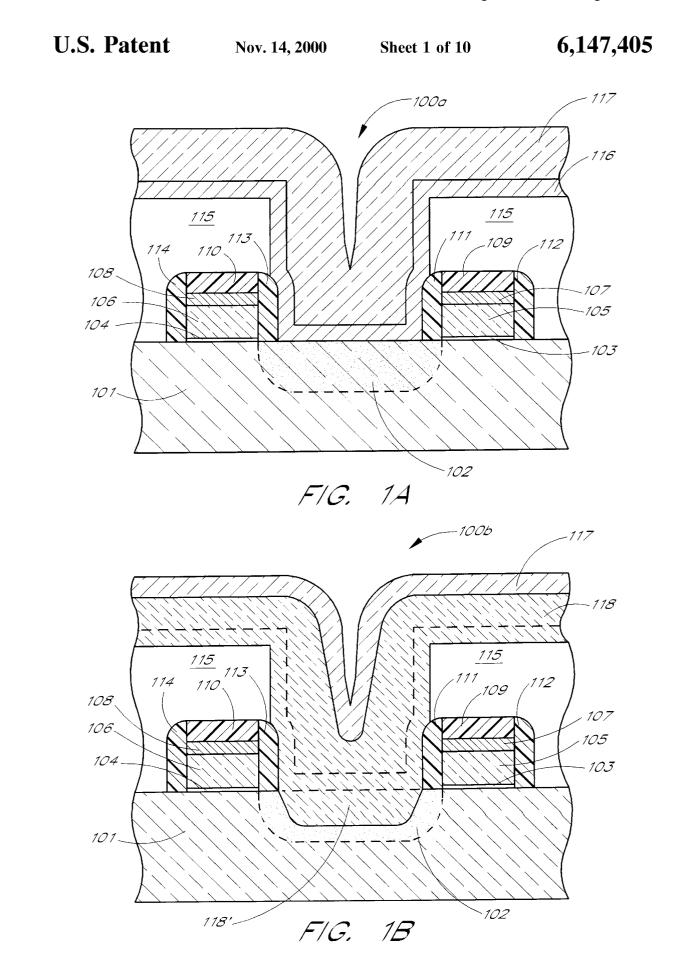

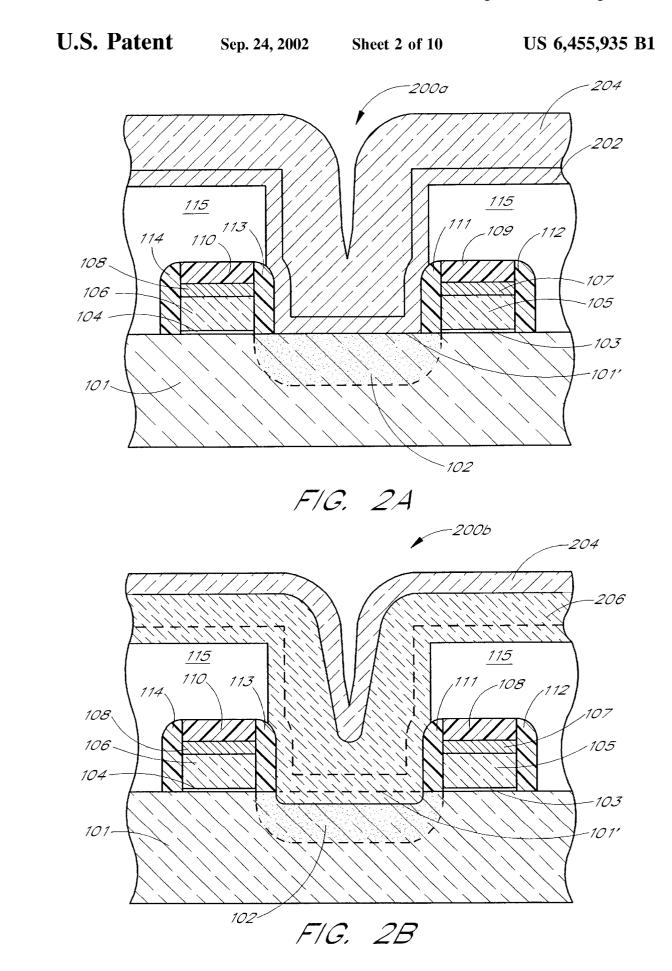

FIGS. 2A and 2B are partial schematic sectional views of an integrated circuit, illustrating self-aligned salicidation in accordance with a preferred embodiment of the present invention. FIGS. 2A and 2B, respectively, show silicon substrate assembly structures before annealing and after annealing.

FIG. 3 shows the bulk resistivity of a titanium nitride layer as a function of N<sub>2</sub>/Ar volume ratio in a reactive sputtering of Ti to form  $TiN_x$  at a given target power.

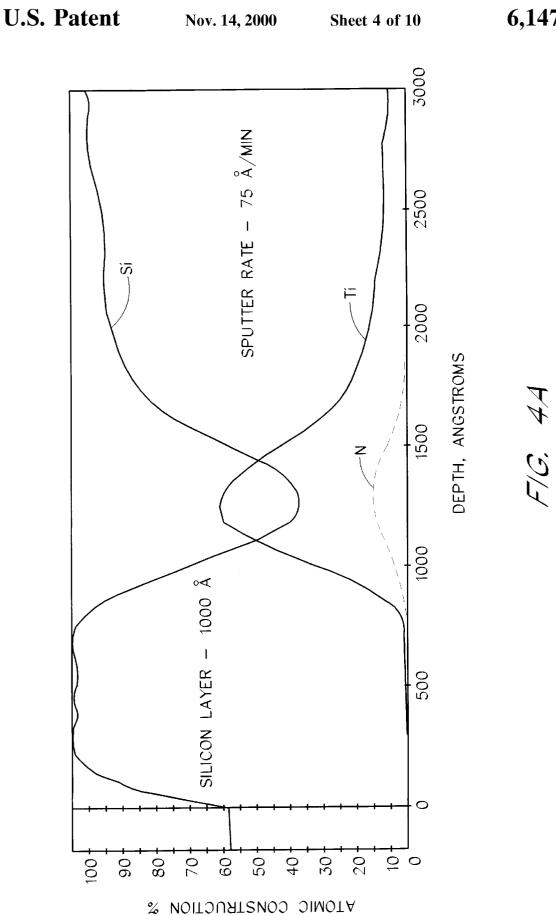

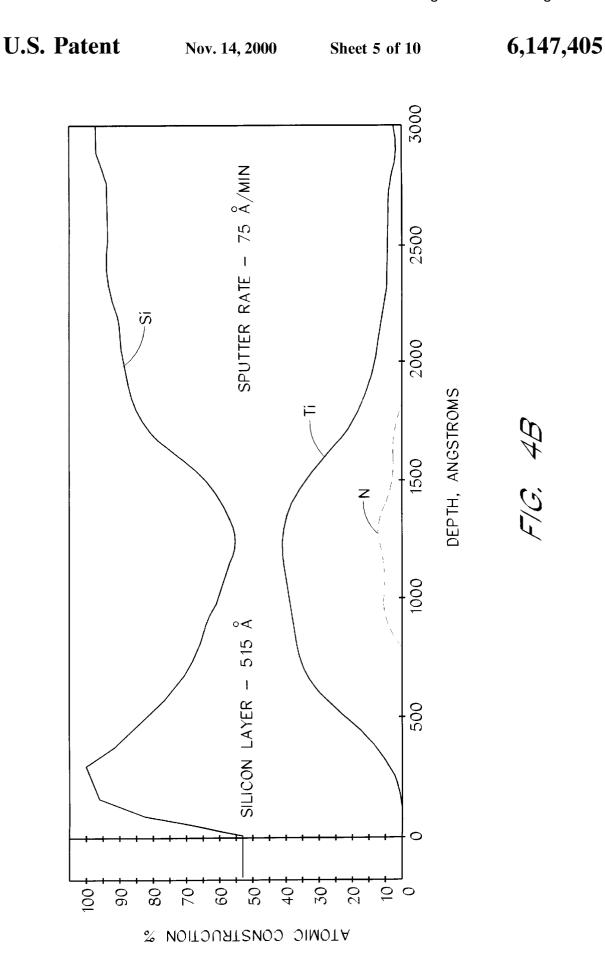

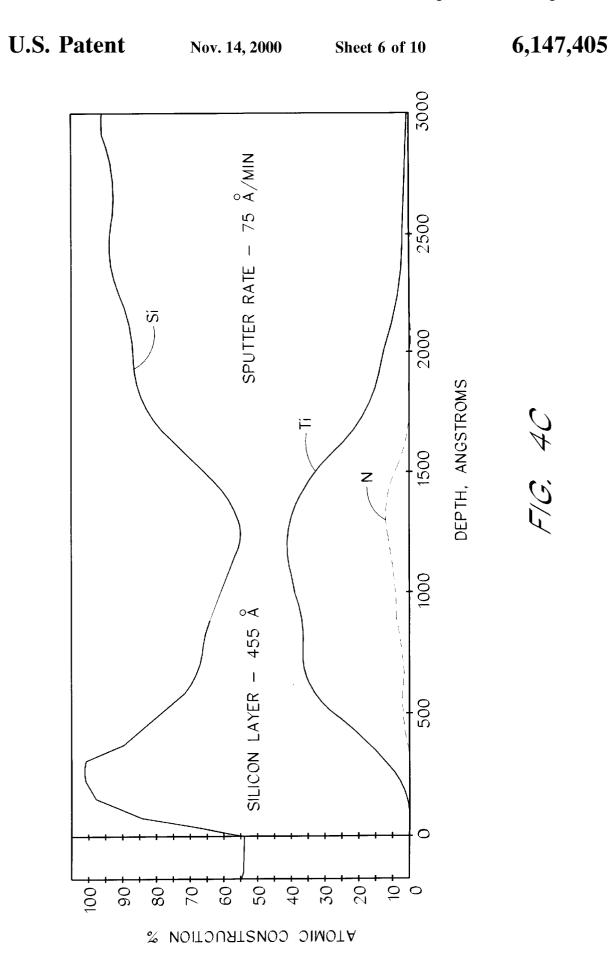

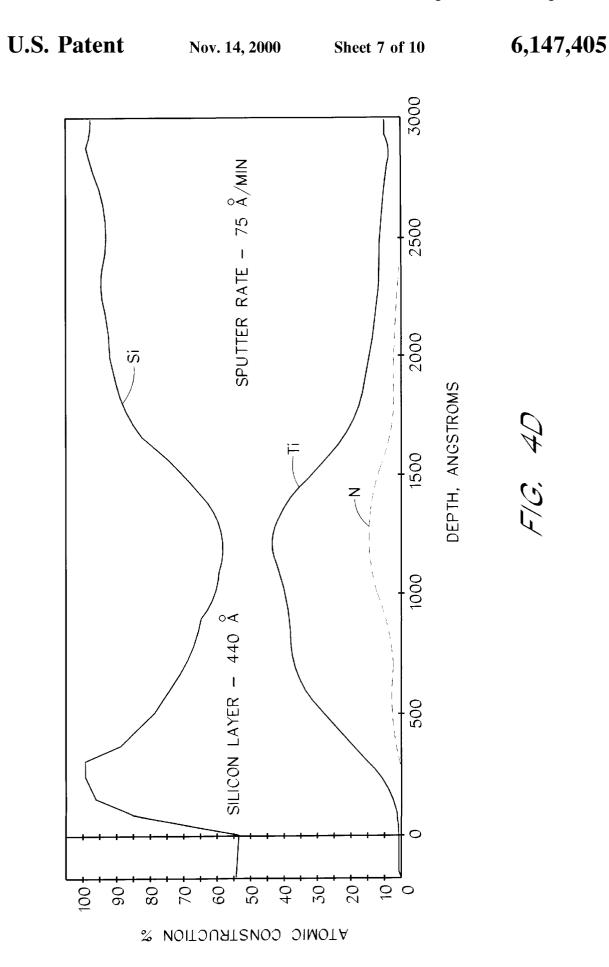

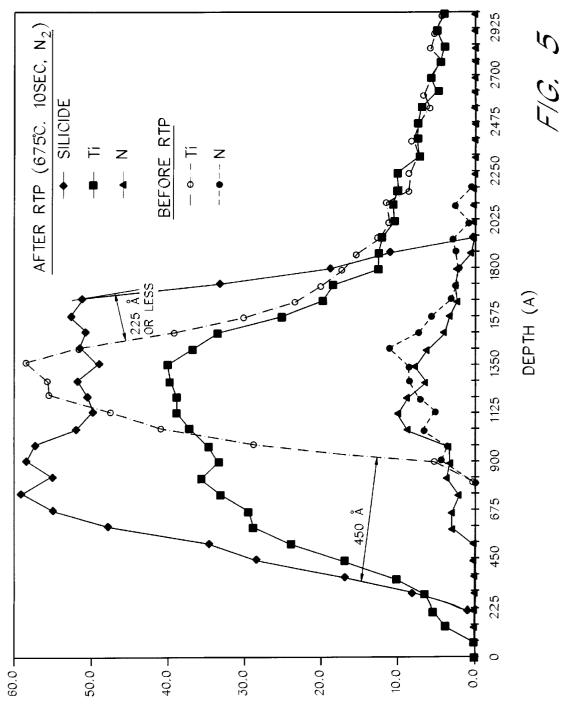

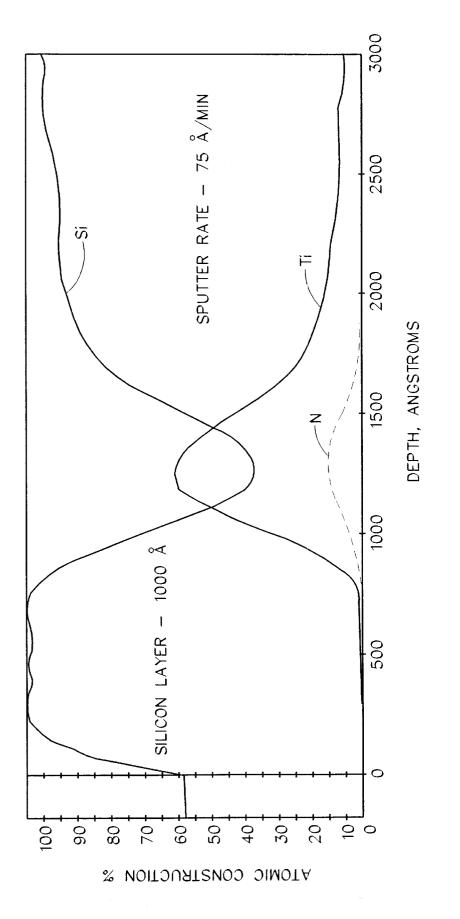

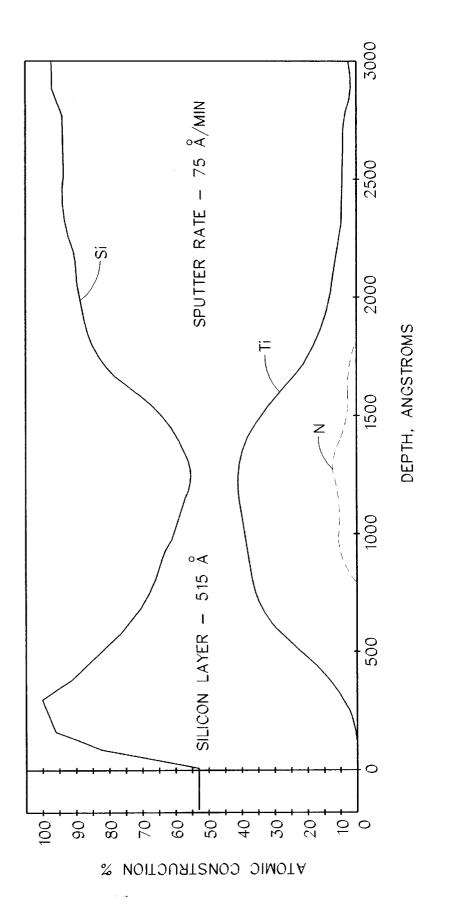

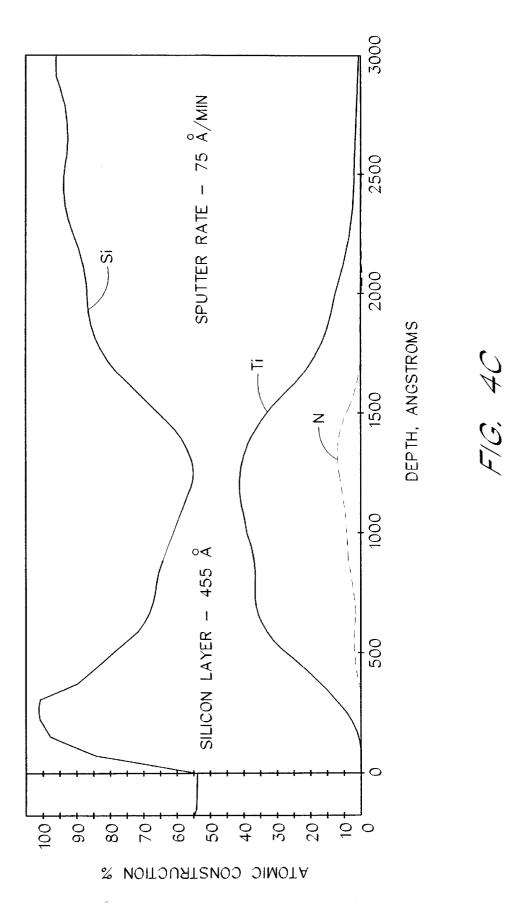

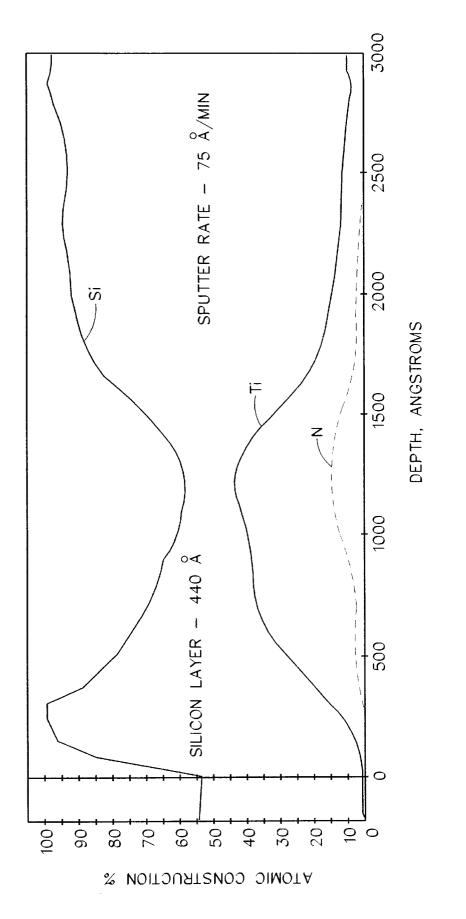

FIG. 4 shows X-ray photoelectron spectroscopic ("XPS") profiles of integrated circuits constructed in accordance with the preferred embodiment. FIG. 4A is a profile of an integrated circuit prior to annealing. FIGS. 4B, 4C, and 4D are profiles of integrated circuits annealed at different tem- 20 peratures.

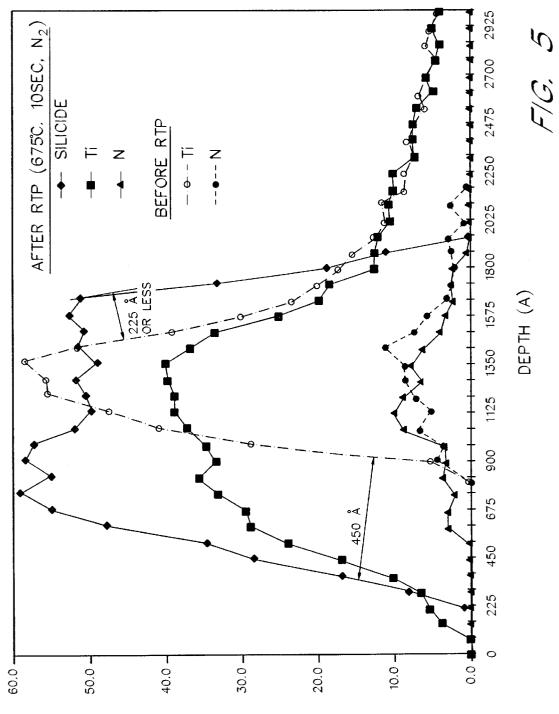

FIG. 5 shows XPS curve-fitting results of FIGS. 4A and **4**B.

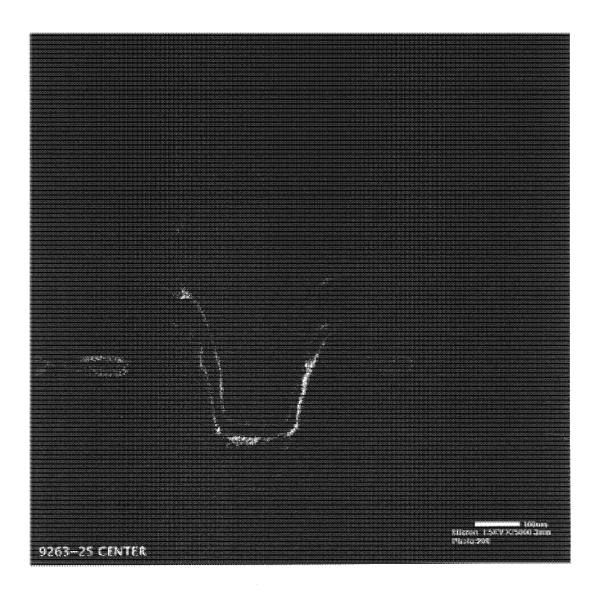

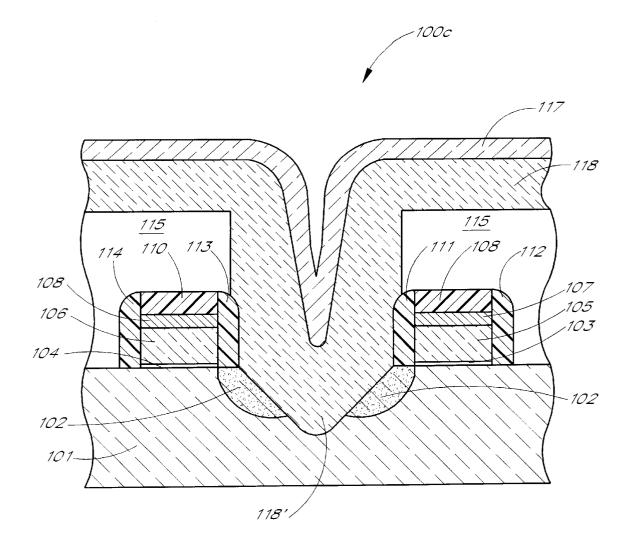

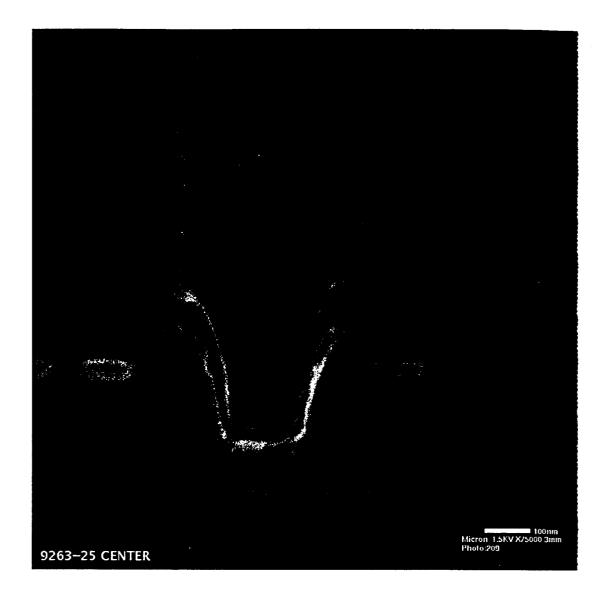

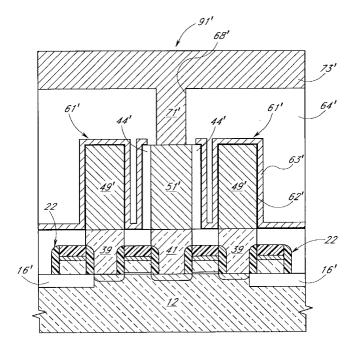

FIG. 6A shows a bit-line contact X-SEM result on an 25 actual device which was run though furnace reflow. FIG. 6B is a schematic sectional view of the integrated circuit of FIG. 1B after furnace reflow.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

While the preferred embodiments are illustrated in the context of self-alignied silicide (or "salicide") contacts to active regions in silicon substrates, it will be recognized by one of skill in the art of semiconductor fabrication that the invention will have application whenever electrical contact to silicon elements is desirable. For example, salicide can be used in forming contact to silicon interconnects, gate electrodes or plugs. Furthermore, the term "substrate," as used in the present application, refers to one or more semiconductor layers or structures which include active or operable portions of semiconductor devices.

In general, one method of reducing substrate (or "silicon electrical element") consumption in forming self-aligned silicide wiring is to supply additional silicon to the process. For example, an intermediate silicon layer can be introduced between the silicon substrate and the titanium layer. The intermediate silicon layer provides the titanium layer with some or all of the silicon required in the salicidation.

With intermediate silicon, however, the titanium layer 50 should be thick enough to consume all of the intermediate silicon in order for the silicide to be in contact with the underlying active area of the silicon substrate. Alternatively, the intermediate silicon layer must be doped to match the doping type of the contacted active region in order to ensure 55 ohmic contact, forming "raised" source/drain regions. Such doping can require an additional mask and all the attendant processing steps. In the fabrication of CMOS circuits, which utilize complementary n-channel and p-channel devices, contacts require two marks for doping the different regions which contact p+ drains and n+ drains, respectively. Each of these masks is expensive both to create for different chip designs and to use in production.

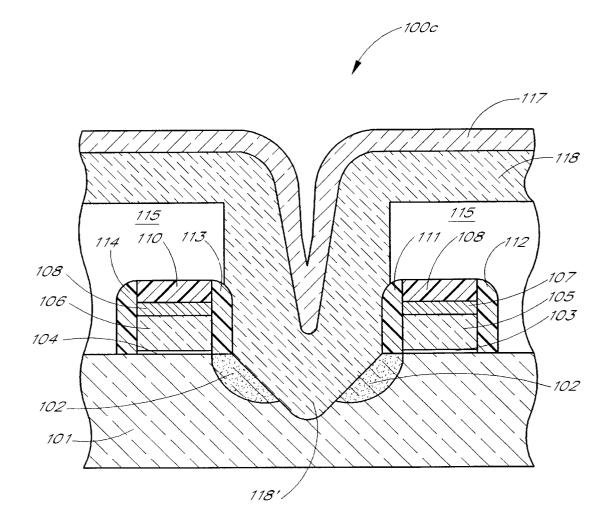

Supplemental silicon can also be introduced over a metallic layer to provide silicon required to form silicide. FIG. 65 deposited over the insulating layer 115 and the active area 1A, for example, illustrates a schematic sectional view of such a structure 100a formed on a silicon substrate 101. A

highly doped silicon active area 102 is defined below a substrate surface 101'. In the illustrated embodiment, the active area 102, which may comprise a transistor source or drain, has an ultrashallow junction of no more than about 1,000 Å.

Two structures, such as gate structures in MOS devices, lie over silicon substrate 101 adjacent the active area 102. Each of the gate structures has a thin gate oxide layer 103, 104, a polysilicon gate electrode layer 105, 106, a metallic layer 107, 108, and a protective cap layer 109, 110. Sidewall spacers 111, 112, 113, 114 protect the gate stacks, and an insulating layer 115 (e.g., BPSG) covers the gate structures and the silicon substrate 101. A window is opened onto the active area 102 through the insulating layer 115 in order to provide contact to the active area 102. The contact window thus is defined by the insulating layer 115, inner sidewall spacers 111, 113, and the active area 102. A titanium layer 116 and a polysilicon layer 117 are deposited, in that order, into the contact window and over the insulating layer 115. The deposition of polysilicon over titanium forms a sandwich-like structure inside the window, in which the metal layer 116 is interposed between the supplemental silicon (i.e., the polysilicon layer 117) and the active area 102 of the silicon substrate 101. This structure 100a allows titanium in the titanium layer 116 to diffuse into and consume silicon from both the underlying active area 102 and the overlying polysilicon layer 117 when it is annealed. This process can be referred to as "double-sided salicidation."

FIG. 1B, for example, shows a structure 100b which is the result of annealing the structure 100a of FIG. 1A. Over the insulating layer 115, only the overlying polysilicon 117 provides silicon for the reaction. Inside the contact window, on the other hand, the reaction proceeds in both directions. Titanium consumes silicon from both the overlying polysilicon layer 117 and the underlying active area 102 to form a silicon-rich titanium silicide 118' thick enough to present a low sheet resistance. While the titanium may diffuse at about a 10% higher rate in polysilicon than in monocrystalline silicon, the salicidation reaction is substantially symmetrical, consuming about the same amount of silicon from the substrate as from the overlying silicon 117.

While the double-sided salicidation reaction described above is preferable to conventional salicide, double-sided salicide is not without its problems. For example, chemical vapor deposition ("CVD"), the most common process for depositing polysilicon, does not easily form silicon over metallic layers, such as the titanium layer 116. This is due to the fact that the silicon does not easily nucleate on metal surfaces. Even if a silicon layer of suitable thickness can be formed over the titanium layer 116, double-sided salicidation may still consume too much of the silicon substrate 101, or result in too thin a silicide to provide a low enough sheet resistance.

FIG. 2 depicts schematic sectional views of a silicon substrate assembly structure in accordance with a preferred embodiment of the present invention. Referring to FIG. 2A, an intermediate structure 200a is illustrated, in which a contact window is opened through an insulating layer 115 to expose an active area 102 of a silicon substrate 101. As the gates structures and insulating layer can be similar to those of FIG. 1A, like reference numerals will be used to refer to like parts.

A metal source layer 202, having an impurity therein, is 102 through the contact window. Preferably, the impurity comprises nitrogen, and the metal source layer 202 com-

30

35

60

65