# IN THE UNITED STATES DISTRICT COURT FOR THE EASTERN DISTRICT OF TEXAS BEAUMONT DIVISION

| DR. URI COHEN                    | § |                      |

|----------------------------------|---|----------------------|

| Plaintiff,                       | § |                      |

|                                  | § |                      |

| V.                               | § |                      |

|                                  | § | Case No. 1:17-CV-189 |

| TAIWAN SEMICONDUCTOR             | § |                      |

| MANUFACTURING COMPANY, LTD.,     | § | Jury Demanded        |

| HUAWEI DEVICE USA, INC., HUAWEI  | § |                      |

| DEVICE (DONGGUAN) CO., LTD.,     | § |                      |

| HUAWEI DEVICE CO., LTD. AND      | § |                      |

| HISILICON TECHNOLOGIES CO., LTD. | § |                      |

|                                  | § |                      |

| Defendants                       | § |                      |

# PLAINTIFF'S FIRST AMENDED AND SUPPLEMENTED COMPLAINT

Dr. Uri Cohen brings this action against Taiwan Semiconductor Manufacturing Company, Ltd. ("TSMC"), Huawei Device USA, Inc., Huawei Device (Dongguan) Co., Ltd., Huawei Device Co., Ltd. and HiSilicon Technologies Co., Ltd. (collectively, "Huawei"), and alleges as follows:<sup>1</sup>

# THE PARTIES

1. Plaintiff Dr. Uri Cohen ("Plaintiff" or "Dr. Cohen") is a United States citizen, with a residence of 4147 Dake Ave., Palo Alto, CA 94306.

2. Defendant Taiwan Semiconductor Manufacturing Company Ltd. is a Taiwanese corporation and is headquartered at No. 8, Li-Hsin Rd. VI, Hsinchu, Taiwan 300, R.O.C. ("TSMC").

3. Defendant Huawei Device USA Inc. ("Huawei USA") is a Texas corporation with its principal place of business in Plano, Texas. Huawei USA distributes, markets, and sells mobile

<sup>&</sup>lt;sup>1</sup> Except where otherwise noted or apparent from context, any allegation against "Defendants," "TSMC," or "Huawei," is an allegation directed to every defendant subsumed within that name.

#### Case 1:17-cv-00189-RC Document 37 Filed 08/28/17 Page 2 of 36 PageID #: 182

devices, including smartphones in the United States. Upon information and belief, Defendant Huawei USA is authorized to do business in Texas and has a North American Headquarters for Marketing, Sales & Services located at 5700 Tennyson Parkway, Suite 500, Plano, Texas 75024. Huawei USA may be served through its registered agent CT Corporation System, 350 N. St. Paul Street, Suite 2900, Dallas, Texas 75201.

4. Defendant Huawei Device (Dongguan) Co., Ltd. ("Huawei Dongguan") is a Chinese company with a principal place of business at Building A, Cloud Park, Huacheng Road, Bantian, Longgang District, Shenzhen 518054, China. Huawei Dongguan is involved in the design, manufacture, and sale of mobile devices.

5. Defendant Huawei Device Co., Ltd. ("Huawei Device") is a Chinese company with a principal place of business at 8 Shitou Road, North Area, Shenzhen, 518129, China. Huawei Device is involved in the design, manufacture, and sale of mobile devices. Huawei Device's subsidiaries in the United States include Huawei Device USA, Inc..

6. Defendant HiSilicon Technologies Co., Ltd. ("HiSilicon") is a Chinese company with its principal place of business in Bantian, Longgang District, Shenzhen, People's Republic of China. On information and belief, HiSilicon is a subsidiary of Huawei China, and has a design division in Silicon Valley, U.S.A.

# JURISDICTION AND VENUE

7. This action arises under the patent laws of the United States, Title 35 United States Code, particularly §§ 271 and 281. This Court has jurisdiction over these claims for patent infringement under 28 U.S.C. §§ 1331 and 1338(a).

8. Personal jurisdiction exists generally over TSMC, Huawei USA, Huawei Device, Huawei Dongguan, and HiSilicon because those companies have sufficient minimum contacts

#### Case 1:17-cv-00189-RC Document 37 Filed 08/28/17 Page 3 of 36 PageID #: 183

with the forum as a result of business conducted within the State of Texas and within the Eastern District of Texas. For example, Huawei USA's main headquarters is located in this district; on information and belief TSMC has significant contacts with its customers and fellow market participants in the state and this District, including Huawei. Personal jurisdiction also exists specifically over TSMC and Huawei because those companies, directly or through subsidiaries or intermediaries, make, use, offer for sale, or sell products or services within the State of Texas and within the Eastern District of Texas that directly or indirectly infringe the patents-in-suit.

9. Venue is proper in this Court under Title 28 United States Code §§ 1391(b) and (c) and 1400(b) at least because TSMC and various of the Huawei entities are foreign corporations and subject to personal jurisdiction in this district and have regularly conducted business in this district, and because certain of the acts complained of herein occurred in this district. Furthermore, Huawei USA has its principal place of business in this district.

#### THE PATENTS

10. On February 11, 2003, U.S. Patent No. 6,518,668 entitled "Multiple Seed Layers for Metallic Interconnects" ("the '668 patent") was duly and legally issued. A true and correct copy of the '668 patent is attached as Exhibit 1.

11. Pursuant to 35 U.S.C. § 282, the '668 patent is presumed valid.

12. Dr. Cohen is the owner of the entire right, title, and interest in the '668 patent, including the right to sue and collect damages for past, present, and future infringement (to the extent those remedies are available to him).

13. On August 2, 2005, U.S. Patent No. 6,924,226 entitled "Methods for Making Multiple Seed Layers for Metallic Interconnects" ("the '226 patent") was duly and legally issued.A true and correct copy of the '226 patent is attached as Exhibit 2.

14. Pursuant to 35 U.S.C. § 282, the '226 patent is presumed valid.

15. Dr. Cohen is the owner of the entire right, title, and interest in the '226 patent, including the right to sue and collect damages for past, present, and future infringement (to the extent those remedies are available to him).

16. On April 3, 2007, U.S. Patent No. 7,199,052 entitled "Seed Layers for Metallic Interconnects" ("the '052 patent,") was duly and legally issued. A true and correct copy of the '052 patent is attached as Exhibit 3.

17. Pursuant to 35 U.S.C. § 282, the '052 patent is presumed valid.

18. Dr. Cohen is the owner of the entire right, title, and interest in the '052 patent, including the right to sue and collect damages for past, present, and future infringement (to the extent those remedies are available to him).

19. On October 16, 2007, U.S. Patent No. 7,282,445 entitled "Multiple Seed Layers for Interconnects" ("the '445 patent,") was duly and legally issued. A true and correct copy of the '445 patent is attached as Exhibit 4.

20. Pursuant to 35 U.S.C. § 282, the '445 patent is presumed valid.

21. Dr. Cohen is the owner of the entire right, title, and interest in the '445 patent, including the right to sue and collect damages for past, present, and future infringement (to the extent those remedies are available to him).

22. The '668 patent, '226 patent, '052 patent, and '445 patent will hereinafter be referred to collectively as the "patents-in-suit."

23. To the extent required, Dr. Cohen has complied with the marking provisions of 35U.S.C. § 287 and is thus entitled to past damages.

## DR. COHEN'S PRIOR COMMUNICATIONS WITH TSMC

#### Case 1:17-cv-00189-RC Document 37 Filed 08/28/17 Page 5 of 36 PageID #: 185

24. Dr. Cohen was first introduced to TSMC in October 2000. After getting in touch with Mr. Henry Lo of TSMC in Taiwan, Dr. Cohen was invited by TSMC to present his Seed Layers technologies to TSMC in Hsinchu, Taiwan. Dr. Cohen provided TSMC a presentation of his technologies on April 10, 2001. Among other things, Dr. Cohen explained to TSMC how it could use a chemical vapor deposition ("CVD") seed layer followed by a physical vapor deposition ("PVD") seed layer over a barrier layer to enable reliable void-free electrofill of openings narrower than 0.10 micron for TSMC's current and future generations of interconnects.

25. After the meeting in Hsinchu in April 2001, Dr. Cohen followed up a number of times with TSMC in subsequent months. Ultimately, TSMC declined at that time to collaborate with Dr. Cohen, or take a license to Dr. Cohen's patent-pending technologies.

26. In 2003, Dr. Cohen reached out again to TSMC, getting in touch with Dr. Rick Tsai, the president of TSMC at that time. Dr. Cohen had several communications with Dr. Tsai in which Dr. Cohen suggested to TSMC that it take a license to what Dr. Cohen referred to as his "Seed Layer Portfolio," and indicated that several patents had issued, including U.S. Patent No. 6,518,668 and a Taiwanese counterpart. Dr. Cohen explained to TSMC, among other things and as he had done before, that as geometries of semiconductor chips become smaller, Dr. Cohen's patented technology would become more relevant to TSMC's chip designs and methods of fabrication. Once again, TSMC declined to take a license to Dr. Cohen's patents.

27. On July 23, 2004, Dr. Cohen (through his counsel) sent a letter to Dr. Richard Thurston, TSMC's then-Vice President and General Counsel, drawing TSMC's attention once again to the '668 patent, among others, and providing TSMC a copy of the '668 patent. Included with that letter, Dr. Cohen provided TSMC a general description of the patented technology and patents pending in Dr. Cohen's Seed Layer Portfolio.

#### Case 1:17-cv-00189-RC Document 37 Filed 08/28/17 Page 6 of 36 PageID #: 186

28. Dr. Cohen also provided TSMC with claim charts explaining the manner in which certain of Dr. Cohen's claims would be infringed by specific forms of interconnects, including representative claim charts for the '668 patent. Having received no reply from Dr. Thurston, on October 12, 2004 Dr. Cohen sent another letter to Dr. Thurston, in which he strongly recommended that TSMC consider taking a license to Dr. Cohen's patents. He urged that even if TSMC did not yet use Dr. Cohen's patented technology, it soon likely would as its technology nodes moved to smaller geometries.

29. Thereafter, from 2004 through 2007, Dr. Cohen's counsel communicated with TSMC on numerous occasions concerning Dr. Cohen's patented technology.

30. For example, on May 1, 2006, Dr. Cohen's counsel sent a letter to Steven Slater, Esq., TSMC's outside counsel with the law firm Slater & Matsil, LLP, drawing TSMC's attention to the '226 patent, among others, and providing TSMC a copy of the '226 patent and explaining how TSMC would infringe the '226 patent if it employed certain processing methods.

31. That letter also identified to TSMC Dr. Cohen's U.S. Application No. 2007-0117379, which subsequently matured into the '052 patent.

32. TSMC denied again that it was infringing any of Dr. Cohen's patents, and in a letter dated October 6, 2006, explained:

We would like to leave the door open to licensing Dr. Cohen's patents in the future, should TSMC elect to adopt multiple layer seed processes that are relevant to Dr. Cohen's patent claims, but TSMC is not using such technology at the present time and has no current plans to do so.

33. In a letter dated June 29, 2007, Dr. Cohen's counsel directed TSMC's attention to, among others, claims 10, 17, 18, 26, 33, 34, 53, and 58, of the '052 patent.

34. As further evidence that TSMC has been well aware of Dr. Cohen's patented technology, TSMC has referenced Dr. Cohen's '668 patent in no less than 15 of its own patents

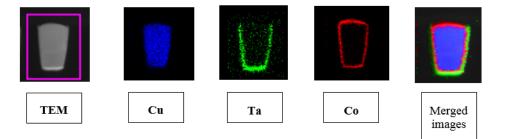

and patent applications, including U.S. Patent Nos. 6806192, 6943111, 7067409, 7215024, 7265038, 7378744, 8277619, and U.S. Patent Applications Nos. 20040147104, 20040157431, 20050029665, 20050110147, 20050250320, 20050263902, 20060216916, and 20070010080.

## BACKGROUND FACTS CONCERNING ACCUSED PRODUCTS

35. All preceding paragraphs are incorporated by reference as if fully set forth herein.

36. An integrated circuit is a set of electronic circuits integrated on semiconductor material, which is most often silicon. These are often referred to as "semiconductor devices" or "semiconductor chips." These semiconductor chips are used in electronics, computers, and smartphones, among other devices.

37. TSMC fabricates integrated circuits for a number of companies using its 20 and 16 nanometer node finFET process.

38. For example, TSMC fabricates the HiSilicon Kirin 950 and 955 chips (16nm) for Huawei for use in at least the Huawei P9 and Huawei Honor 8 Smartphones (the "Huawei Chips").

39. TSMC also fabricates the Apple A8 (20nm), Apple A9 (16nm), and Apple A10 (16nm) Applications Processors (and their variants, including the A8X and the A9X) for Apple (the "Apple Chips").<sup>2</sup>

40. TSMC similarly fabricates modems, CPUs, GPUs, FPGAs, and other chips for numerous other companies using its 16 and 20 nanometer finFET process (the "Other 16nm and 20nm Chips").

41. Though TSMC does not publicly disclose all of its customers for its 16nm and 20nm node processes, on information and belief the Other 16nm and 20nm Chips are functionally

<sup>&</sup>lt;sup>2</sup> The Apple Chips are incorporated into the Apple iPhone 6 and iPhone 7 generation smart phones and tablets.

## Case 1:17-cv-00189-RC Document 37 Filed 08/28/17 Page 8 of 36 PageID #: 188

identical to the Huawei Chips and the Apple Chips for purposes of this Complaint, are fabricated by TSMC using the same fabrication method, and have the same relevant structures.

42. For example, Dr. Cohen's reverse engineering analysis of the Apple Chips and the Huawei Chips (discussed further below) has revealed that those chips, fabricated at the same or similar nodes, contain the same relevant structures for purposes of this Complaint (including at least the metal layers).

43. Dr. Cohen's reverse engineering analysis of additional chips manufactured using TSMC's 16nm or 20nm nodes has revealed that those chips too contain the same relevant structures for purposes of this Complaint.

44. TSMC's 16 nanometer node interconnect technology is in all relevant ways identical to its 20 nanometer node interconnect technology, as they both share the same metal backend process.<sup>3</sup>

45. On information and belief, it is industry practice that when a large chip fabricator like TSMC adopts a certain process for a specific node (such as a process for applying seed layers for metallic interconnects), it uses that same process for all chips fabricated at that same node.

46. Therefore, on information and belief, all Other 16nm and 20nm Node Chips have identical relevant structures for purposes of this Complaint.

47. Hereinafter, the Huawei Chips, Apple Chips, and Other 16nm and 20nm Chips will be referred to collectively as the "Accused Chips."

<sup>&</sup>lt;sup>3</sup> http://www.tsmc.com/english/dedicatedFoundry/technology/16nm.htm; see also

http://www.dailytech.com/TSMC+Hypes+Its+Upcoming+10+nm+Process+Amid+Struggles+to+Hit+Volume+at+1 6+nm/article37298.htm ("TSMC's strategy to achieve 16 nm production is controversial, as it's built 'on top of' TSMC's 20 nm process. It uses 16 nm transistors. However, for the backplane it uses 20 nm interconnects (bonding pads, electrical contacts, insulating layers, and metal layers).").

48. The Accused Chips comprise integrated circuits that comprise multiple-seed-layer structures.

49. HiSilicon designs, develops, and supplies the Huawei Chips for incorporation into Huawei's mobile devices. Huawei incorporates the Huawei Chips it receives from HiSilicon into at least the Huawei P9 and Huawei Honor 8 Smartphones. HiSilicon works closely with TSMC

on the design of the Huawei Chips:

# TSMC 16FF+ Manufactured

As mentioned earlier, the Kirin 950 is HiSilicon's first TSMC 16FF+ manufactured mobile SoC. This also makes the Chinese vendor second in line after Apple's to release mobile silicon based on the new manufacturing node.

HiSilicon explains that along with Apple they've been the two main lead partners of [TSMC], and both parties have been working closely together to try to improve the design and to tune the process. In fact, the company revealed that first mass production (also commonly named as risk production) started as early as last January. Over the following months both companies cooperated to sort out bugs and imperfections in the design (chip revisions) to go up from 20% yield in the earliest runs to up to 80% yields and qualified mass production this last August.<sup>4</sup>

50. Apple designed the Apple Chips which are made by TSMC for Apple. With respect

to the design of its A8, Apple has explained:

iPod touch features an Apple-designed A8 chip built on 64-bit architecture. This desktopclass chip features GPU performance up to 10 times faster than the previous-generation iPod touch — so the graphics in your favorite games are more responsive and look more vivid than ever before — and CPU performance is up to six times faster. And you get the same great battery life, with up to 40 hours of music and 8 hours of video playback.<sup>5</sup>

The all-new A8 chip is our fastest yet. Its CPU and graphics performance are faster than on the A7 chip, even while powering a larger display and incredible new features. And because it's designed to be so power efficient, the A8 chip can sustain higher performance. . . . A8 uses an advanced 20-nanometer process. It's a remarkably small and efficient chip on which two billion transistors deliver incredible performance with up to 50 percent more energy efficiency than the A7 chip.<sup>6</sup>

<sup>&</sup>lt;sup>4</sup> http://consumer.huawei.com/en/press/media-coverage/hw-462408.htm

<sup>&</sup>lt;sup>5</sup> http://www.apple.com/ipod-touch/

<sup>&</sup>lt;sup>6</sup> http://www.apple.com/iphone-6/technology/

51. With respect to the design of its A9 chips, Apple has explained:

The A9 chip brings a new level of performance and efficiency to iPhone 6s. Not only a faster experience, but a better one. The A9 chip is capable of gaming console–class graphics performance that makes games and other apps much richer and more immersive.

... The A9 chip is our third-generation chip with 64-bit architecture. It sits at the cutting edge of mobile chips, improving overall CPU performance by up to 70 percent compared to the previous generation. And boosting graphics performance by up to a staggering 90 percent compared to the previous generation.<sup>7</sup>

52. TSMC uses its 16 nanometer node finFET process to fabricate the A9 and A10

processors.<sup>8,9</sup>

53. With respect to the design of its A10 chips, Apple has explained:

iPhone 7 is supercharged by the most powerful chip ever in a smartphone. It's not just faster than any previous iPhone — it's also more efficient. That's because the A10 Fusion chip uses an all-new architecture that enables faster processing when you need it, and the ability to use even less power when you don't. And with the longest battery life ever in an iPhone, you can work at twice the speed of iPhone 6 and still enjoy more time between charges.

With an all-new four-core design, the A10 Fusion chip's CPU has two high-performance cores and two high-efficiency cores. The high-performance cores can run at up to 2x the speed of iPhone 6, while the high-efficiency cores are capable of running at just one-fifth the power of the high-performance cores. That means you get the best performance and efficiency when you need it.<sup>10</sup>

54. Based in part on the allegations in paragraphs 49-53, above, as well as on other

reports of collaboration between TSMC and its customers, on information and belief TSMC also

cooperates with its customers for the Other 16nm and 20nm Chips, including by collaborating on

chip design, coauthoring papers and articles, etc.

<sup>&</sup>lt;sup>7</sup> http://www.apple.com/iphone-6s/technology/

<sup>&</sup>lt;sup>8</sup> http://www2.techinsights.com/l/8892/2015-09-28/zxx9c;

<sup>&</sup>lt;sup>9</sup> http://appleinsider.com/articles/16/07/11/apple-chip-builder-tsmc-expected-to-see-record-q3-on-a10-chips; https://en.wikipedia.org/wiki/Apple\_A10; http://appleinsider.com/articles/16/06/30/tsmc-expected-to-net-big-revenue-boost-on-apple-a10-chips-for-iphone-7

<sup>&</sup>lt;sup>10</sup> https://www.apple.com/iphone-7/

55. In 2010, in an article titled "A New Enhancement Layer to Improve Copper Interconnect Performance," and published in the IEEE International Technology Conference, TSMC reported that the use of cobalt as a seed/enhancement layer between a PVD tantalum barrier layer and a copper seed layer would improve copper wetting on the barrier layer, improve interconnect quality, electrical performance, reliability, and maximize gap fill in integrated circuits ("TSMC's IEEE Paper").<sup>11</sup>

56. To achieve this integrated circuit design in its 20 nanometer and 16 nanometer node technologies, as reported in TSMC's IEEE Paper, TSMC on information and belief utilizes equipment supplied to it by Applied Materials, Inc. ("AMAT"), including AMAT's Endura platform and Endura Volta System.

57. The Endura platform supports both Physical Vapor Deposition (PVD) and Chemical Vapor Deposition (CVD) processes,<sup>12</sup> including the Endura Volta System, which was introduced by AMAT on May 13, 2014.<sup>13</sup>

58. On information and belief, the method utilized by TSMC to manufacture the Accused Chips and the resulting structure of the Accused Chips themselves are consistent with the methods and structures as explained by TSMC in its IEEE Paper, and as depicted below.

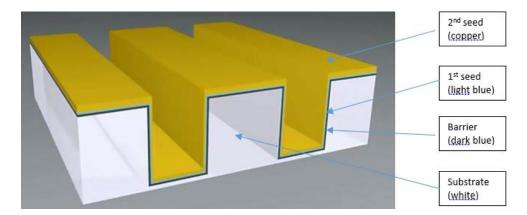

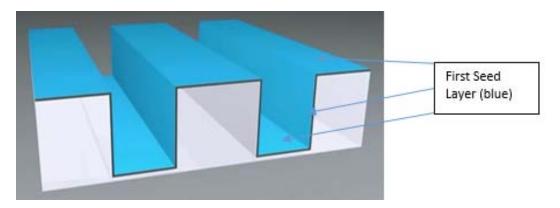

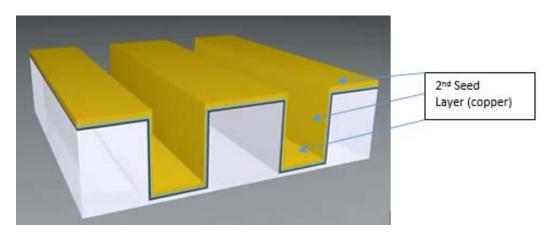

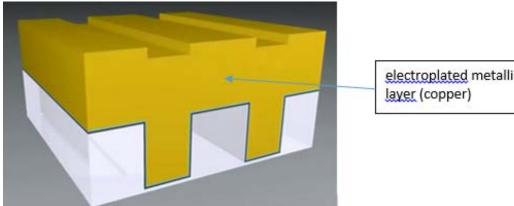

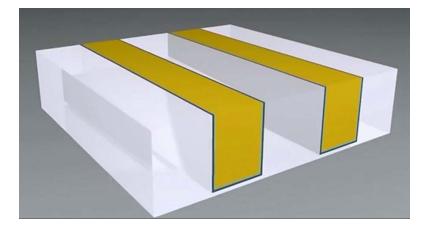

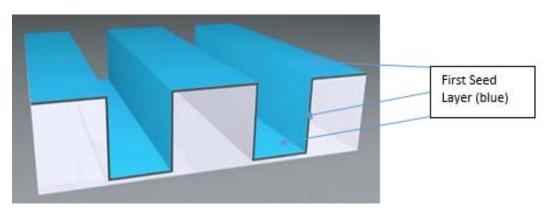

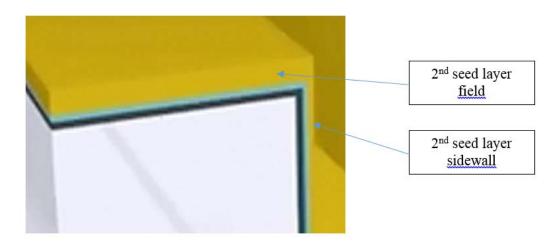

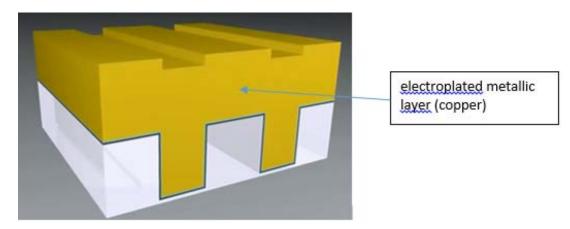

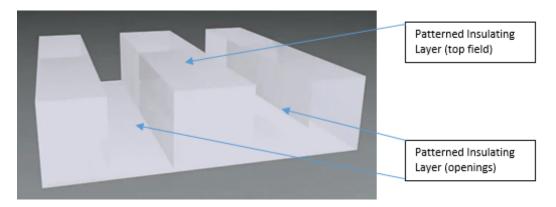

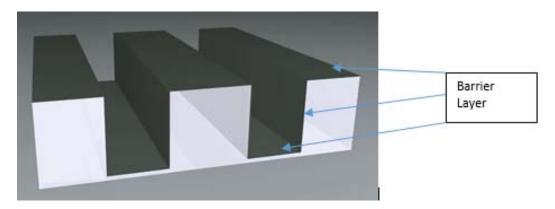

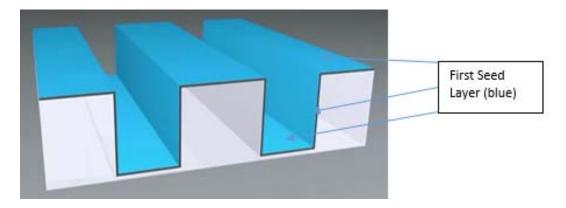

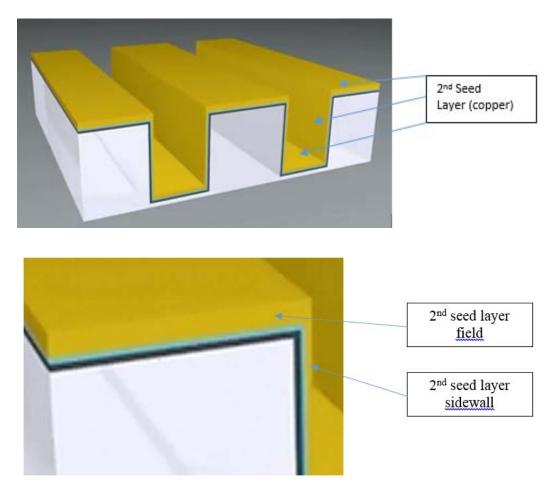

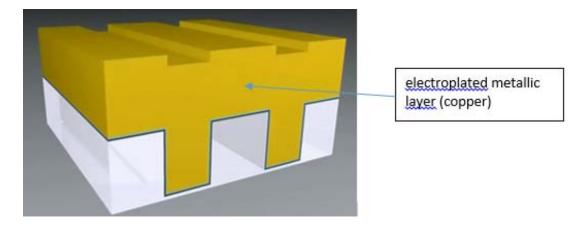

59. As shown here, the resulting 20 nanometer and 16 nanometer devices fabricated by TSMC contain a multiple seed layer structure comprising a patterned insulating layer formed on a substrate, a tantalum barrier layer over the substrate, a first seed layer comprising cobalt, a second

http://ieeexplore.ieee.org/xpl/login.jsp?tp=&arnumber=5510762&url=http%3A%2F%2Fieeexplore.ieee.org%2Fxpls %2Fabs\_all.jsp%3Farnumber%3D5510762

<sup>&</sup>lt;sup>12</sup> Id.

<sup>&</sup>lt;sup>13</sup> http://www.appliedmaterials.com/company/news/press-releases/2014/05/applied-materials-introduces-the-biggest-materials-change-to-interconnect-technology-in-15-years

seed layer comprising copper, and an electroplated metallic layer of copper disposed over the second seed layer:<sup>14</sup>

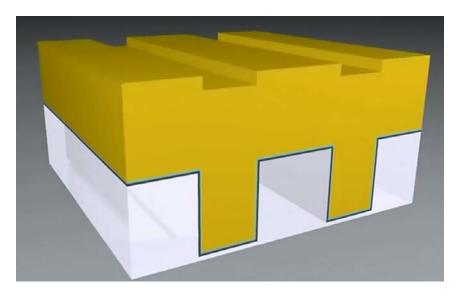

60. After the barrier, first seed layer and second seed layer are formed over the substrate, electroplated copper is disposed over the second seed layer over the openings and the field, as depicted below.

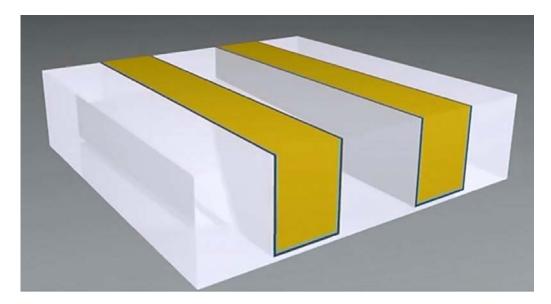

61. After the electroplated copper is disposed over the openings and the field, the electroplated copper overlying the field, the first and second seed layers overlying the field, and the barrier layer overlying the field are all substantially removed by a polishing technique. The resulting interconnect is as is depicted below.

<sup>&</sup>lt;sup>14</sup> See "Volta Animation," appliedschannel, https://www.youtube.com/watch?v=EcWdzKRK2dk.

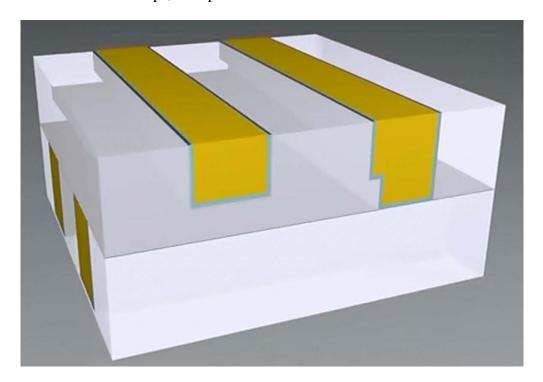

62. Multiple levels of interconnects are often stacked one on top of another, which is the case with the Accused Chips, as depicted below.

63. Confirming the existence of the structure depicted above in the Accused Chips, the images below depict actual cross-sections of interconnects in the Apple Chips and Huawei Chips obtained via reverse engineering.

64. The presence of a cobalt ("Co") seed layer in these cross-sections confirms the use in the Accused Chips of the multiple-seed-layer process described above.

65. The images are unable to depict a distinct copper seed layer on top of the cobalt seed layer because electroplating merges the copper seed layer with the electroplated copper, as illustrated in paragraphs 59-60 and 63, above.

66. However, on information and belief, achieving the copper metallization depicted in the cross-section images is accomplished by first applying a copper seed layer on top of the cobalt seed layer prior to electroplating, as illustrated in paragraphs 59 and 60.

# BACKGROUND INFORMATION CONCERNING DEFENDANTS' ACTS OF INFRINGEMENT

67. All preceding paragraphs are incorporated by reference as if fully set forth herein.

68. The Accused Chips meet or embody the limitations of the at least one claim of each of the patents-in-suit, as described further below in Counts I–IV.

69. The Defendants have infringed at least one claim of each of the patents-in-suit by making, using, selling, offering for sale within the United States and/or importing into the United States, the Accused Chips; or induced infringement of the same.

70. More specifically, on information and belief, Defendant TSMC makes the Huawei Chips for Huawei, then offers to sell and sells the Huawei Chips for use in the United States.

71. Huawei imports, offers to sell, and/or sells devices containing the Huawei Chips (such as the Huawei P9 and Huawei Honor 8 Smartphones) in the United States.

#### Case 1:17-cv-00189-RC Document 37 Filed 08/28/17 Page 15 of 36 PageID #: 195

72. On information and belief, Defendant TSMC makes the Apple Chips for Apple, then offers to sell and sells the Apple Chips for use in the United States.

73. Apple imports, offers to sell, and sells devices containing the Apple Chips (such as the Apple iPhone 6 and iPhone 6 Plus, iPhone 6S and iPhone 6S Plus, iPhone SE, iPad Touch, iPad Pro (12.9"), iPad Pro Mini (9.7"), iPhone 7 and iPhone 7 Plus) in the United States.

74. On information and belief, Defendant TSMC makes the Other 16nm and 20nm Chips for its other customers, then offers to sell and sells the Other 16nm and 20nm Chips for use in the United States.

75. TSMC's customers and their affiliates—including but not limited to Apple, Huawei, other equipment manufacturers, chip designers, and chipset makers—import, offer to sell, and/or sell devices containing the Other 16nm and 20nm Chips (including the Apple devices listed above, the Huawei devices listed above, and Huawei's Google Nexus 6P) in the United States.

76. On information and belief, Huawei uses devices containing the Accused Chips in the United States, during testing, demonstrations, and the like.

77. On information and belief, Apple uses devices containing the Accused Chips in the United States, during testing, demonstrations, and the like.

### A. DEFENDANTS' DIRECT INFRINGEMENT

## **1. TSMC'S Direct Infringement**

78. All preceding paragraphs are incorporated by reference as if fully set forth herein.

79. TSMC directly infringes at least one claim of each of the patents-in-suit, either literally or under the doctrine of equivalents, by selling and/or offering for sale within the United States the Accused Chips.

80. On information and belief, TSMC collaborates with its customers in the United States regarding the design of the Accused Chips.

81. On information and belief, TSMC conducts marketing efforts related to the Accused Chips in the United States.

82. On information and belief, TSMC engages in pricing and contractual negotiations regarding the Accused Chips with customers in the United States.

83. On information and belief, TSMC receives purchase orders for Accused Chips in the United States.

84. On information and belief, TSMC executes contracts for sale of the Accused Chips in the United States.

85. Many of the Accused Chips are ultimately sold, offered for sale, and used in devices within the United States.

86. On information and belief, TSMC knows that many of the Accused Chips it sells its customers will ultimately be sold, offered for sale, and used in devices within the United States.

## 2. Huawei's Direct Infringement

87. All preceding paragraphs are incorporated by reference as if fully set forth herein.

88. Huawei directly infringes at least at least one claim of each of the patents-in-suit under 35 U.S.C. 271(a) and 271(g), either literally or under the doctrine of equivalents, by making, using, selling, offering for sale within the United States, leasing, and/or importing into the United States, devices that incorporate the Accused Chips (including at least the Huawei P9, Huawei Honor 8, and Google Nexus 6P Smartphones).

89. The Accused Chips made by the processes claimed in the asserted process claims of the patents-in-suit are not materially changed by subsequent processes prior to importation, use, sale, or offer for sale in the United States by Huawei.

90. As demonstrated by the cross-section images and other information above, Dr. Cohen's patented multiple-seed-layer structure, and benefits thereof, remain discernible and intact in the Accused Chips as sold.

91. The Accused Chips made by the processes claimed in the asserted process claims of the patents-in-suit do not become a trivial or nonessential component of another product prior to importation, use, sale, or offer for sale in the United States by Huawei.

92. As demonstrated by the cross-section images and other information above, Dr. Cohen's patented multiple-seed-layer structure, and benefits thereof, remain discernible and intact in the Accused Chips as sold.

93. The Accused Chips, which include central processing units, graphics processing units, modems, etc., are essential to the operation of the electronic devices, chipsets, and other products the Accused Chips are incorporated into.

## **3.** Other TSMC Customers' Direct Infringement

94. All preceding paragraphs are incorporated by reference as if fully set forth herein.

95. TSMC's other customers—including Apple—who sell devices in the United States containing the Apple Chips or Other 16nm and 20nm Chips directly infringe at least one claim of each of the patents-in-suit under 35 U.S.C. 271(a) and 271(g), either literally or under the doctrine of equivalents, by making, using, selling, offering for sale within the United States, leasing, and/or importing into the United States, smart phones and other devices that incorporate the Accused Chips (including at least the Apple iPhone 6 and iPhone 6 Plus, iPhone 6S, 6S Plus, iPhone SE, iPad Touch, iPad Pro (12.9"), iPad Pro Mini (9.7"), iPhone 7 and iPhone 7 Plus).

96. The Accused Chips made by the processes claimed in the asserted process claims of the patents-in-suit are not materially changed by subsequent processes prior to importation, use, sale, or offer for sale in the United States by Apple.

97. As demonstrated by the cross-section images and other information above, Dr. Cohen's patented multiple-seed-layer structure, and benefits thereof, remain discernible and intact in the Accused Chips as sold.

98. The Accused Chips made by the processes claimed in the asserted process claims of the patents-in-suit do not become a trivial or nonessential component of another product prior to importation, use, sale, or offer for sale in the United States by TSMC's other customers.

99. As demonstrated by the cross-section images and other information above, Dr. Cohen's patented multiple-seed-layer structure, and benefits thereof, remain discernible and intact in the Accused Chips as sold.

100. The Accused Chips, which include central processing units, graphics processing units, modems, etc., are essential to the operation of the electronic devices, chipsets, and other products the Accused Chips are incorporated into.

## **B. DEFENDANTS' INDUCEMENT OF INFRINGEMENT**

## **1. TSMC's Inducement of Infringement**

101. All preceding paragraphs are incorporated by reference as if fully set forth herein.

102. TSMC has had actual knowledge of the '668 patent since as early as July 23, 2004, including representative claim charts and infringement analyses for the '668 patent.

103. Moreover, TSMC has referenced Dr. Cohen's '668 patent in no less than 15 patents and patent applications assigned to TSMC, including U.S. Patent Nos. 6,806,192, 6,943,111, 7,067,409, 7,215,024, 7,265,038, 7,378,744, 8,277,619, and U.S. Patent Applications Nos. 20040147104, 20040157431, 20050029665, 20050110147, 20050250320, 20050263902, 20060216916, and 20070010080. Additionally, TSMC has had actual knowledge of the '226 patent since as early as May 1, 2006, including representative claim charts and infringement analyses for the '226 patent.

104. Additionally, TSMC has had actual knowledge of the application that matured into the '052 patent (U.S. Application No. 2007-0117379) since as early as May 1, 2006, and then the '052 patent itself since as early as June 29, 2007.

105. Moreover, TSMC has referenced Dr. Cohen's '052 patent in at least two patents assigned to TSMC, including U.S. Patent Nos. 7,704,886 and 8,252,690.

106. Additionally, TSMC has had actual knowledge of the application that matured into the '445 patent (that is, U.S. Application No. 11/654,478) since as early as June 29, 2007.

107. Upon information and belief, TSMC knew of, or was willfully blind towards, its infringement of the patents-in-suit at least since it began fabricating Huawei Chips, Apple Chips and Other 16nm and 20nm Chips.

108. Since becoming aware of, or being willfully blind towards, its infringement of the patents-in-suit, TSMC has continued to intentionally, actively, and knowingly make, use, sell, offer to sell, and/or import one or more of the Accused Chips through its retailers, resellers, and distributors, as well as in other ways.

109. Since becoming aware of the patents-in-suit, TSMC's advertising, sales, and/or technical materials in relation to the Accused Chips have intentionally, actively, knowingly, and willfully contained and continue to contain instructions, directions, suggestions, and/or invitations that intentionally, actively, and knowingly invite, entice, lead on, influence, encourage, prevail on, move by persuasion, and/or cause the public, TSMC's distributors, retailers, and customers (including the related Huawei entities and Apple) to thereby directly infringe (via § 271(a) and/or § 271(g)) at least one claim of each of the patents-in-suit, either literally or under the doctrine of equivalents.

110. TSMC has collaborated with its customers, including Apple and Huawei, on the design of the Accused Chips. Since becoming aware of, or being willfully blind towards, its infringement of the patents-in-suit, TSMC was willfully blind or knew that the public's, the distributors', the retailers', and/or the customers' using, importing, selling, and/or offering to sell the Accused Chips directly infringe (via § 271(a) and/or § 271(g)), either literally or under the doctrine of equivalents, at least one claim of each of the patents-in-suit.

111. For at least these reasons, as well as others that may be revealed through discovery, TSMC is liable for inducing infringement (via § 271(a) and/or § 271(g)) of the patents-in-suit, either literally or under the doctrine of equivalents.

## 2. Huawei's Inducement of Infringement

112. All preceding paragraphs are incorporated by reference as if fully set forth herein.

113. Huawei has had actual knowledge of the patents in suit since at least as early of the filing or service of the Original Complaint in this case.

114. Huawei has had knowledge before at least some of its infringing acts that Dr. Cohen's patented processes were used to make Huawei Chips and Other 16nm and 20nm Chips.

115. Upon information and belief, Huawei knew of, or was willfully blind towards, its infringement of the patents-in-suit at least since the filing or service of the Original Complaint.

116. Since becoming aware of, or being willfully blind towards, its infringement of the patents-in-suit, Huawei has continued to intentionally, actively, and knowingly make, use, sell, offer to sell, and/or import one or more of the Huawei Chips and Other 16nm and 20nm Chips through its retailers, resellers, and distributors, as well as in other ways.

117. Since becoming aware of the patents-in-suit, Huawei's advertising, sales, and/or technical materials in relation to the Huawei Chips and Other 16nm and 20nm Chips have intentionally, actively, knowingly, and willfully contained and continue to contain instructions,

directions, suggestions, and/or invitations that intentionally, actively, and knowingly invite, entice, lead on, influence, encourage, prevail on, move by persuasion, and/or cause the public, Huawei's distributors, subsidiaries, retailers, and customers to thereby directly infringe (via § 271(a) and/or § 271(g)) at least one claim of each of the patents-in-suit, either literally or under the doctrine of equivalents.

118. For at least these reasons, as well as others that may be revealed through discovery, Huawei is liable for inducing infringement (via § 271(a) and/or § 271(g)) of the patents-in-suit, either literally or under the doctrine of equivalents.

## **COUNT I: INFRINGEMENT OF THE '668 PATENT**

119. All preceding paragraphs are incorporated by reference as if fully set forth herein.

120. The Defendants have infringed at least one claim of the '668 patent by performing the acts of infringement described above with respect to the Accused Chips.

121. Each of the Accused Chips is fabricated by TSMC using the same relevant fabrication method, and producing the same relevant chip structure, as explained in the Volta Animation, and as described in paragraphs 49-53 and 58-66 above. As such, the Accused Chips meet each limitation of at least one claim of the '668 patent.

122. By way of example and not limitation, each of the Accused Chips meets or embodies every limitation of claim 26 (dependent of claim 1) of the '668 patent:

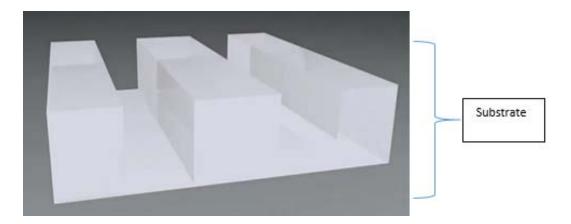

a. a substrate, as depicted below:

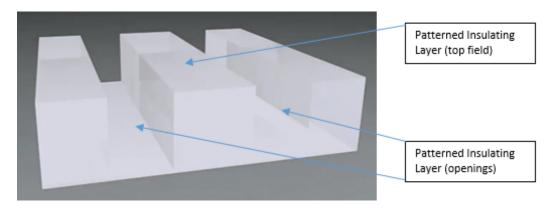

b. a patterned insulating layer formed on said substrate, said patterned insulating layer including at least one opening and a top field surface surrounding said at least one opening, as depicted below:

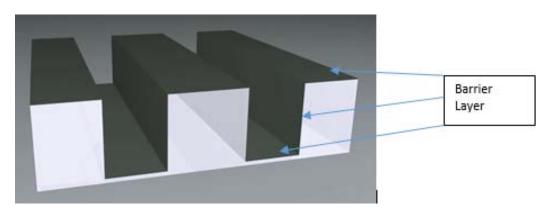

c. a barrier layer disposed over said patterned insulating layer including over inside surfaces of the at least one opening, as depicted below:

In the case of the Accused Chips, tantalum nitrite is used for the barrier layer and is applied through a PVD process.

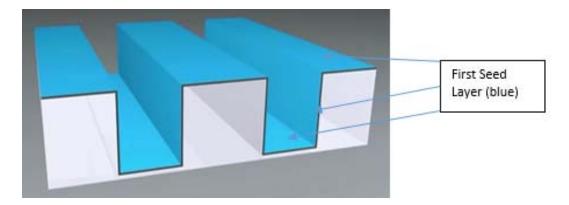

d. a first seed layer disposed over the barrier layer, said first seed layer comprising a substantially conformal seed layer whose thickness on the sidewalls of the opening (at about mid-depth) is about 25-100% of its thickness on the field, as depicted below:

A first conformal layer of cobalt is applied over the barrier layer through a CVD process.

Because it is a conformal layer and applied through a CVD process, the thickness of the cobalt layer on the sidewalls of the opening (at about mid-depth) is about 25-100% of its thickness on the field.<sup>15</sup>

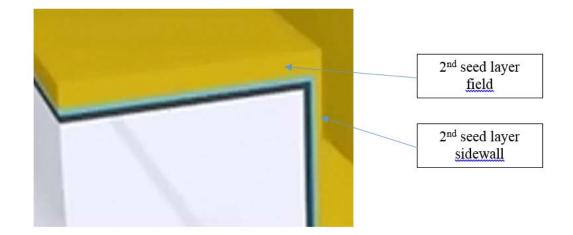

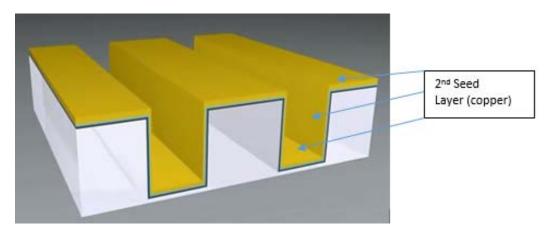

e. a second seed layer disposed over the first seed layer, said second seed layer comprising a substantially non-conformal seed layer whose thickness on the sidewalls of the opening (at about mid-depth) is less than about 25% of its thickness on the field, and wherein said second seed layer being thicker than said first seed layer over the field, as depicted below:

<sup>&</sup>lt;sup>15</sup> See generally "Conformal CVD Co Deposition for Enhancement of Cu Gapfill Application," ADMETA Conference 2008, Tokyo, Japan, Exhibit 5.

As is now well known in the art, at the geometries found in the accused chips, an optimized PVD copper seed layer at the 2x nanometer node and beyond will result in sidewall coverage at midpoint of about 13% to 15% of the thickness on the field, and certainly less than 25% of the thickness on the field.

> an electroplated metallic layer disposed over the second seed layer, wherein f. the electroplated metallic layer comprises a material selected from a group consisting of Cu, Ag, or alloys comprising one or more of these metals, as depicted below:

electroplated metallic

After the second substantially non-conformal seed layer is applied through a PVD process,

an electroplated metallic layer of copper is disposed over the second seed layer in the openings and on the field, filling the openings.

g. (claim 26) A metallic interconnect fabricated by using the multiple seed layer structure of claim 1, wherein the electroplated metallic layer overlying the opening and overlying the field, and the first and second seed layers overlying the field, and the barrier layer overlying the field, are substantially removed by a removal technique, said removal technique comprises one or more of a mechanical polishing technique, a chemical mechanical polishing technique, a wet etching technique, and a dry etching technique, as depicted below:

As explained in the Volta Animation, after copper is used to fill the openings and applied over the field through electroplating, the copper over the field and the barrier layer and first and second seed layers over the field are removed using a polishing technique.

# COUNT II: INFRINGEMENT OF THE '226 PATENT

116. All preceding paragraphs are incorporated by reference as if fully set forth herein.

117. The Defendants have infringed at least one claim of the '226 patent by performing the acts of infringement described above with respect to the Accused Chips.

118. Each of the Accused Chips is fabricated by TSMC using the same relevant fabrication method, and producing the same relevant chip structure, as explained in the Volta Animation, and as described in paragraphs 49-53 and 58-66 above. As such, the Accused Chips meet at least one claim of the '226 patent.

119. By way of example and not limitation, each of the Accused Chips meets or embodies every limitation of at least claim 1 of the '226 patent in that each of the Accused Chips is fabricated using a method as recited in claim 1 by:

a. depositing a substantially conformal seed layer over the field and inside surfaces of the at least one opening;

A substantially conformal layer of cobalt is deposited over the field and inside surfaces of

at least one opening layer through a CVD process.

b. depositing a substantially non-conformal seed layer over the substantially conformal seed layer, said substantially non-conformal seed layer being thicker than said substantially conformal seed layer over the field, wherein the substantially conformal and the substantially non-conformal seed layers do not seal the at least one opening; and

As depicted above and on information and belief, an optimized PVD copper seed layer at the 2x nanometer node and beyond will result in thickness over the field far greater than that of a substantially conformal CVD seed layer. Further, as depicted in the Volta Animation, the substantially conformal and the substantially non-conformal seed layers do not seal the at least one opening.

c. electroplating a metallic layer over the substantially non-conformal seed layer, wherein the electroplated metallic layer comprises a material selected from a group consisting of Cu, Ag, or alloys comprising one or more of these metals.

After the substantially non-conformal seed layer is applied through a PVD process, an electroplated metallic layer of copper (i.e. "Cu") is disposed over the substantially non-conformal seed layer.

# COUNT III: INFRINGEMENT OF THE '052 PATENT

120. All preceding paragraphs are incorporated by reference as if fully set forth herein.

121. The Defendants have infringed at least one claim of the '052 patent by performing the acts of infringement described above with respect to the Accused Chips.

122. Each of the Accused Chips is fabricated by TSMC using the same relevant fabrication method, and producing the same relevant chip structure, as explained in the Volta

Animation, and as described in paragraphs 49-53 and 58-66 above. As such, the Accused Chips meet at least one claim of the '052 patent.

123. By way of example and not limitation, each of the Accused Chips meets or embodies every limitation of at least claim 4 of the '052 patent in that each of the Accused Chips is fabricated using a method as recited in claim 4 by:

a. forming a patterned insulating layer on a substrate, the patterned insulating layer including at least one opening and a field surrounding the at least one opening, as depicted below;

b. depositing a barrier layer over the field and inside surfaces of the at least one opening, as depicted below;

c. chemical vapor depositing a first seed layer over the barrier layer, as depicted below;

A first seed layer is deposited by a CVD technique over the barrier layer.

d. physical vapor depositing a second seed layer over the first seed layer, wherein the second seed layer is thicker than the first seed layer over the field, as depicted below; and

A second seed layer is deposited by a PVD technique over the first seed layer. The second seed layer is thicker than the first seed layer over the field.

e. filling the at least one opening by electroplating a metallic layer comprising copper or a copper alloy over the two seed layers, as depicted below.

The openings are filled by electroplating copper over the two seed layers.

# COUNT IV: INFRINGEMENT OF THE '445 PATENT

# 124. All preceding paragraphs are incorporated by reference as if fully set forth herein.

125. The Defendants have infringed at least one claim of the '445 patent by performing the acts of infringement described above with respect to the Accused Chips.

126. Each of the Accused Chips is fabricated by TSMC using the same relevant fabrication method, and producing the same relevant chip structure, as explained in the Volta Animation, and as described in paragraphs 49-53 and 58-66 above. As such, the Accused Chips meet at least one claim of the '445 patent.

127. By way of example and not limitation, each of the Accused Chips meets or embodies every limitation of at least claim 18 of the '445 patent in that each of the Accused Chips is fabricated using a method as recited in claim 18 by:

a. utilizing a CVD chamber capable of depositing a CVD seed layer over the sidewalls of the at least one opening;

A CVD chamber is used to deposit a first seed layer over the sidewalls of at least one

opening.

b. utilizing a PVD chamber capable of depositing a PVD seed layer over the substrate;

A PVD chamber is used to deposit a second seed layer over the substrate.

c. configuring an automatic controller with recipe information, the recipe information including deposition sequence, process and timing parameters for operation of the CVD chamber and the PVD chamber;

On information and belief, use of the AMAT Volta system requires at least one automatic

controller containing recipe information which includes deposition sequence, process and timing

parameters for operation of the CVD chamber and the PVD chamber.

d. operating the automatic controller in accordance with the recipe information to cause the CVD chamber to deposit a CVD first seed layer over the field and the sidewalls of the at least one opening;

On information and belief, as shown in the Volta animation cited above, the said at least one automatic controller is operated in accordance with the recipe information to cause the CVD chamber to deposit a CVD first seed layer over the field and the sidewalls of the at least one opening.

> e. operating the controller in accordance with the recipe information to deposit in the PVD chamber a second seed layer over the first seed layer; and

On information and belief, as shown in the Volta animation cited above, the said at least one automatic controller is operated in accordance with the recipe information to cause the PVD chamber to deposit a second seed layer over the first seed layer and opening.

> f. operating the controller in accordance with the recipe information to stop the deposition of the first and second seed layers prior to sealing the at least one opening, thereby leaving enough room for electroplating inside the at least one opening.

On information and belief, as shown in the Volta animation cited above, the said at least one automatic controller is operated in accordance with the recipe information to stop the deposition of the first and second seed layers prior to sealing the at least one opening, thereby leaving enough room for electroplating inside the at least one opening.

# **DAMAGES**

128. The Defendants' acts of infringement of the patents-in-suit as alleged above have injured Dr. Cohen and thus Dr. Cohen is entitled to recover damages which in no event can be less than a reasonable royalty, including his costs, and pre-judgment and post-judgment interest pursuant to 35 U.S.C. § 284.

# WILLFUL INFRINGEMENT

# A. Willful Infringement by TSMC

129. TSMC has infringed the '668, '226, '052, and '445 patents despite an objectively high likelihood that its actions constituted infringement of these valid patents.

130. TSMC knew or should have known this objectively high likelihood, at least because TSMC was made aware of the patents-in-suit through Dr. Cohen's counsel.

131. On information and belief, after Dr. Cohen presented his patented technology to TSMC in person in 2001 and repeatedly reintroduced it in subsequent years (as described in paragraphs 24–34), TSMC deliberately copied or drew upon Dr. Cohen's patented technology in developing the Accused Chips.

132. On information and belief, TSMC deliberately misrepresented its intentions to Dr. Cohen in the course of discussing his patented technology and licensing overtures, including when TSMC stated in 2006 that it "would like to leave the door open to licensing Dr. Cohen's patents in the future, should TSMC elect to adopt multiple layer seed processes that are relevant to Dr. Cohen's patent claims . . . ."

133. TSMC's ongoing infringement of the patents-in-suit, copying, and misrepresentations subsequent to viewing Dr. Cohen's in-person presentation, receiving Dr. Cohen's multiple communications about the patents-in-suit, and declining to take a license to the patents-in-suit, constitutes egregious misconduct beyond typical infringement.

134. The infringement of the patents-in-suit alleged above has injured Dr. Cohen and thus, Dr. Cohen is entitled to recover damages adequate to compensate for TSMC's infringement, which in no event can be less than a reasonable royalty.

135. Because TSMC willfully infringed the patents-in-suit, Dr. Cohen is permitted under35 U.S.C. § 284 to recover treble the amount of actual damages sustained by the Plaintiff.

#### EXCEPTIONAL CASE

136. TSMC's acts, including at least their willful infringement, have made the present case exceptional pursuant to 35 U.S.C. § 285 and/or other applicable authority. Therefore, Dr. Cohen is entitled to attorneys' fees as the prevailing party.

#### **DEMAND FOR JURY TRIAL**

137. Dr. Cohen hereby demands a jury trial on all claims and issues triable of right by a jury.

## **PRAYER**

WHEREFORE, Dr. Cohen prays for entry of judgment in his favor against each and every defendant:

- A. Finding that Taiwan Semiconductor Manufacturing Company, Ltd. has infringed one or more claims of the '668 patent, one or more claims of the '226 patent, one or more claims of the '052 patent, and one or more claims of the '445 patent;

- B. Finding that Huawei Device USA Inc. has infringed one or more claims of the '668 patent, one or more claims of the '226 patent, one or more claims of the '052 patent, and one or more claims of the '445 patent;

- C. Finding that Huawei Device Co., Ltd. has infringed one or more claims of the '668 patent, one or more claims of the '226 patent, one or more claims of the '052 patent, and one or more claims of the '445 patent;

- D. Finding that Huawei Device (Dongguan) Co., Ltd. has infringed one or more claims of the '668 patent, one or more claims of the '226 patent, one or more claims of the '052 patent, and one or more claims of the '445 patent;

- E. Finding that HiSilicon Technologies Co., Ltd. has infringed one or more claims of the '668 patent, one or more claims of the '226 patent, one or more claims of the '052 patent, and one or more claims of the '445 patent;

- F. Awarding Dr. Cohen all allowable damages flowing from the defendants' infringement of the '668 patent, the '226 patent, the '052 patent, and the '445 patent, which can be no less than a reasonable royalty under 35 U.S.C. § 284;

- G. Finding that Taiwan Semiconductor Manufacturing Company, Ltd. has willfully infringed the '668 patent, the '226 patent, the '052 patent, and the '445 patent, and awarding Dr. Cohen all allowable damages for their willful infringement, including but not limited to an award of three times Dr. Cohen's actual damages pursuant to 35 U.S.C. § 284;

- H. Awarding Dr. Cohen his costs, and pre-judgment and post-judgment interest on his damages caused by the defendants' infringement of the '668 patent, the '226 patent, the '052 patent, and the '445 patent, and/or otherwise, as the Court may deem just;

- I. Declaring this case exceptional, in Dr. Cohen's favor, and awarding Dr. Cohen his attorneys' fees in this action pursuant to 35 U.S.C. § 285 and/or other applicable authority; and

- J. Granting Dr. Cohen such other and further legal and/or equitable relief that is just and proper under the circumstances.

Dated: August 28, 2017

Respectfully submitted,

<u>/s/ Bradley W. Caldwell</u> Bradley W. Caldwell Texas State Bar No. 24040630 Email: bcaldwell@caldwellcc.com Jason D. Cassady Texas State Bar No. 24045625 Email: jcassady@caldwellcc.com John Austin Curry Texas State Bar No. 24059636 Email: acurry@caldwellcc.com Christopher S. Stewart Texas State Bar No. 24079399 Email: cstewart@caldwellcc.com **CALDWELL CASSADY & CURRY** 2101 Cedar Springs Road, Suite 1000 Dallas, Texas 75201 Telephone: (214) 888-4848 Facsimile: (214) 888-4849

Christopher M. Faucett (Texas Bar No. 00795198) Matthew J.M. Prebeg (Texas Bar No. 00791465) **PREBEG, FAUCETT & ABBOTT PLLC** 8441 Gulf Freeway, Suite 307 Houston, Texas 77017 Telephone: (832) 742-9260 Facsimile: (832) 742-9261 Email: mprebeg@pfalawfirm.com Email: cfaucett@pfalawfirm.com

# **CERTIFICATE OF SERVICE**

The undersigned certifies that the foregoing document was filed electronically in compliance with Local Rule CV-5(a). As such, this document was served on all counsel who have consented to electronic service on this  $28^{th}$  day of August, 2017. Local Rule CV-5(a)(3)(A).

/s/ Bradley W. Caldwell Bradley W. Caldwell