## IN THE UNITED STATES DISTRICT COURT FOR THE NORTHEN DISTRICT OF TEXAS DALLAS DIVISION

| SUPER INTERCONNECT       | §                          |

|--------------------------|----------------------------|

| <b>TECHNOLOGIES LLC,</b> | Ş                          |

| Plaintiff,               | § JURY TRIAL DEMANDED<br>§ |

| N/                       | §<br>§ CIVIL ACTION NO.    |

| V.                       | § CIVIL ACTION NO          |

| ZTE CORPORATION AND      | s<br>§                     |

| ZTE USA, INC.,           | §                          |

|                          | §                          |

| Defendants.              | §                          |

## PLAINTIFF'S ORIGINAL COMPLAINT FOR PATENT INFRINGEMENT

Plaintiff Super Interconnect Technologies LLC ("Super Interconnect") files this Original Complaint against ZTE Corporation and ZTE USA, Inc. (collectively, "ZTE") for infringement of U.S. Patent No. 7,627,044 ("the '044 patent"), U.S. Patent No. 6,463,092 ("the '092 patent"), and U.S. Patent No. 7,158,593 ("the '593 patent").

## THE PARTIES

1. Super Interconnect Technologies LLC is a Texas limited liability company, located at 1701 Directors Blvd., Suite 300, Austin, Texas 78744.

2. On information and belief, ZTE Corporation is a corporation existing under the laws of China with its principal place of business at ZTE Plaza, Keji Road South, Hi-tech Industrial Park Nanshan, Shenzhen, Guangdong, 518057, China.

3. On information and belief, ZTE USA, Inc. is a corporation organized under the laws of New Jersey with its principal place of business located at 2425 North Central Expressway, Suite 800, Richardson, TX 75080. ZTE USA, Inc. may be served through its registered agent, Incorp Services, Inc., 815 Brazos, Suite 500, Richardson, TX 78701. On information and belief, ZTE USA, Inc. is a wholly-subsidiary of ZTE Corporation.

### JURISDICTION AND VENUE

4. This action arises under the patent laws of the United States, namely 35 U.S.C. §§ 271, 281, and 284-285, among others.

5. This Court has subject matter jurisdiction pursuant to 28 U.S.C. §§ 1331 and 1338(a).

6. Venue is proper in this judicial district as to ZTE Corporation because it is a foreign entity that may be sued in any judicial district under 28 U.S.C. § 1391(c).

7. Venue is proper in this judicial district as to ZTE USA, Inc. under 28 U.S.C. § 1400(b) because ZTE USA, Inc. has committed acts of infringement in this District and has a regular and established place of business in this District, located at 2425 North Central Expressway, Suite 800, Richardson, TX 75080.

8. ZTE is subject to personal jurisdiction pursuant to due process due at least to its substantial business in this State, including: (A) at least part of its infringing activities alleged herein; and (B) regularly doing or soliciting business, engaging in other persistent conduct, and/or deriving substantial revenue from goods sold and services provided to Texas residents. ZTE has conducted and regularly conducts business within the United States and this District. ZTE has purposefully availed itself of the privileges of conducting business in the United States, and more specifically in Texas and this District. ZTE has sought protection and benefit from the laws of the State of Texas by placing infringing products into the stream of commerce through an established distribution channel with the awareness and/or intent that they will be purchased by consumers in this District.

9. On information and belief, ZTE has significant ties to, and presence in, this District, making venue in this judicial district both proper and convenient for this action.

## <u>COUNT I</u>

## (INFRINGEMENT OF U.S. PATENT NO. 7,627,044)

10. Super Interconnect incorporates paragraphs 1 through 9 herein by reference.

11. Super Interconnect is the assignee of the '044 patent, entitled "Clock-Edge Modulated Serial Link with DC-Balance Control," with ownership of all substantial rights in the '044 patent, including the right to exclude others and to enforce, sue, and recover damages for past and future infringement. A true and correct copy of the '044 patent is attached as <u>Exhibit A</u>.

12. The '044 patent is valid, enforceable, and was duly issued in full compliance with Title 35 of the United States Code. The '044 patent issued from U.S. Patent Application No. 11/264,303.

13. To the extent any marking or notice was required by 35 U.S.C. § 287, Super Interconnect and all predecessors-in-interest to the '044 patent have complied with the requirements of that statute by providing actual or constructive notice to ZTE of its alleged infringement.

14. ZTE has and continues to directly and/or indirectly infringe (by inducing infringement and/or contributing to infringement) one or more claims of the '044 patent in this judicial district and elsewhere in the United States, including at least claims 1, 2, 8, 9, 10, 11, 12, 13, 14, 15 and 19, by, among other things, making, having made, using, offering for sale, selling, and/or importing electronic devices with Universal Flash Storage (UFS) that incorporate the fundamental technologies covered by the '044 patent. These products are referred to as the "'044 Accused Products." Examples of the '044 Accused Products include, but are not limited to, the Axon 7 smartphone.

## Case 3:18-cv-02932-M Document 1 Filed 11/02/18 Page 4 of 76 PageID 4

15. For example, the ZTE Axon 7 directly infringes claim 1 of the '044 patent, as shown in the below paragraphs.

16. An example of the ZTE Axon 7 is shown in the image below.

17. ZTE incorporates UFS 2.0 storage in the Axon 7, as shown in the image below.

| Memory                   |                                           |  |  |

|--------------------------|-------------------------------------------|--|--|

| Internal Memory<br>(ROM) | - 64 GB (4 GB RAM)<br>- 128 GB (6 GB RAM) |  |  |

| Internal Storage<br>Type | UFS 2.0 (Universal Flash Storage)         |  |  |

http://newst8.com/specifications/zte-axon-7-full-specification-and-features-8520852025

18. The citations below show that the ZTE Axon 7's UFS storage uses the MIPI M-PHY

protocol for physical layer communication between the UFS host and the UFS device.

## **UFS Implementation Detail**

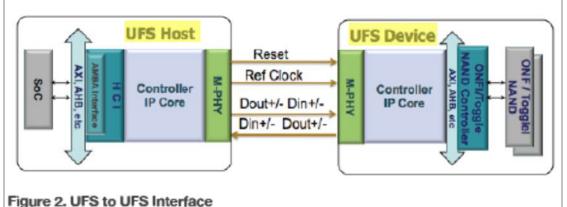

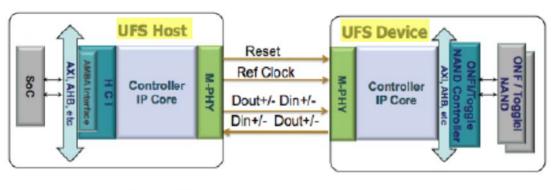

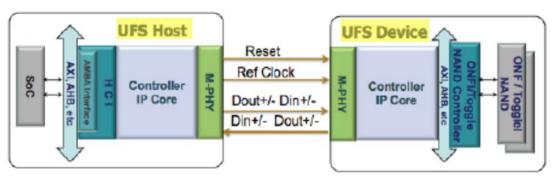

In the diagram below, the implementation of a UFS host or device is simplified to the M-PHY, digital (UniPro) core and the interface to either the Soc or the NAND Flash memory. We will examine each of these in detail.

Arasan Chip Systems Inc. White Paper, "Universal Flash Storage: Mobilize Your Data" at 6 (Oct. 2012).

## M-PHY VO

MIPI defines two types of M-PHY, type 1 and type 2. The UFS specification calls out type 1. M-PHY Type 1 uses NRZ signaling for HS and PWM signaling for LS, while type 2 uses NRZ signaling for both HS and LS.

UFS utilizes two speed modes, high-speed and low-speed. Low speed mode In Gear 1 is used upon power up or reset, then a transition occurs to high-speed gears for data transmission. The low speed gears and high-speed gears are listed here for your reference. UFS v1.1 has been ratified and supports HS Gear 2 running approximately @ 3Gbps per lane. The UFS spec also supports up to 4 lanes for higher throughput.

Id.

19. UFS hosts and devices, which are included in the '044 Accused Products, contain signal transmitters. These signal transmitters drive a DC-balanced differential signal for a communications channel. This signal is comprised of a pair of data signals: a positive (true) data signal and a negative (complement) data signal. These transmitters multiplex a pulse-width modulated clock signal, a data signal, and control signals to apply them to the communications channel.

## Case 3:18-cv-02932-M Document 1 Filed 11/02/18 Page 6 of 76 PageID 6

20. The '044 Accused Products thus include each and every limitation of claim 1 of the '044 patent; accordingly, they literally infringe this claim. ZTE directly infringes the '044 patent by making, using, offering to sell, selling, and/or importing the '044 Accused Products. ZTE is thereby liable for direct infringement.

21. During discovery and development of its infringement contentions, Plaintiff may provide additional theories under which ZTE infringes the '044 patent besides the example provided above, including for the same product and using the same components identified above, and nothing in the example above is meant to limit the infringement allegations of Plaintiff or limit the interpretations of the claims or their terms.

22. At a minimum, ZTE has known that the '044 Accused Products infringe the '044 patent at least as early as the service date of this Original Complaint.

23. Upon information and belief, since at least the above-mentioned date when ZTE was on notice of its infringement, ZTE has actively induced, under U.S.C. § 271(b), third-party manufacturers, distributors, importers and/or consumers that purchase or sell the '044 Accused Products that include all of the limitations of one or more claims of the '044 patent to directly infringe one or more claims of the '044 patent by making, having made, using, offering for sale, selling, and/or importing the '044 Accused Products. Since at least the notice provided on the above-mentioned date, ZTE does so with knowledge, or with willful blindness of the fact, that the induced acts constitute infringement of the '044 patent. Upon information and belief, ZTE intends to cause, and has taken affirmative steps to induce, infringement by these third-party manufacturers, distributors, importers, and/or consumers by, inter alia, creating advertisements that promote the infringing use of the '044 Accused Products, creating established distribution channels for the '044 Accused Products into and within the United States, manufacturing the '044

Accused Products in conformity with U.S. laws and regulations, distributing or making available instructions or manuals for these products to purchasers and prospective buyers, and/or providing technical support, replacement parts, or services for these products to these purchasers in the United States. For example, ZTE advertises, provides support for, and publishes a user manual for the Axon 7 on its own website at the following web address: https://www.zteusa.com/axon-7.

24. Super Interconnect has been damaged as a result of ZTE's infringing conduct described in this Count. ZTE is, thus, liable to Super Interconnect in an amount that adequately compensates Super Interconnect for ZTE's infringement, which, by law, cannot be less than a reasonable royalty, together with interest and costs as fixed by this Court under 35 U.S.C. § 284.

## <u>COUNT II</u> (INFRINGEMENT OF U.S. PATENT NO. 6,463,092)

25. Super Interconnect incorporates paragraphs 1 through 24 herein by reference.

26. Super Interconnect is the assignee of the '092 patent, entitled "System and Method for Sending and Receiving Data Signals Over A Clock Signal Line," with ownership of all substantial rights in the '092 patent, including the right to exclude others and to enforce, sue, and recover damages for past and future infringement. A true and correct copy of the '092 patent is attached as <u>Exhibit B</u>.

27. The '092 patent is valid, enforceable, and was duly issued in full compliance with Title 35 of the United States Code. The '092 patent issued from U.S. Patent Application No. 09/393,235.

28. To the extent any marking or notice was required by 35 U.S.C. § 287, Super Interconnect and all predecessors-in-interest to the '092 patent have complied with the requirements of that statute by providing actual or constructive notice to ZTE of its alleged infringement.

29. ZTE has and continues to directly and/or indirectly infringe (by inducing infringement and/or contributing to infringement) one or more claims of the '092 patent in this judicial district and elsewhere in the United States, including at least claims 1, 2, 5, 10, and 11 by, among other things, making, having made, using, offering for sale, selling, and/or importing electronic devices with Universal Flash Storage (UFS) that incorporate the fundamental technologies covered by the '092 patent. These products are referred to as the "'092 Accused Products." Examples of the '092 Accused Products include, but are not limited to, the ZTE Axon 7 smartphone.

30. For example, the ZTE Axon 7 directly infringes claim 1 of the '092 patent, as shown in the below paragraphs.

31. An example of the ZTE Axon 7 is shown in the image below.

32. ZTE incorporates UFS 2.0 storage in the Axon 7, as shown in the image below.

| Memory                   |                                           |

|--------------------------|-------------------------------------------|

| Internal Memory<br>(ROM) | - 64 GB (4 GB RAM)<br>- 128 GB (6 GB RAM) |

| Internal Storage<br>Type | UFS 2.0 (Universal Flash Storage)         |

http://newst8.com/specifications/zte-axon-7-full-specification-and-features-8520852025

33. The images below show that the ZTE Axon 7's UFS storage uses the MIPI M-PHY

protocol for physical layer communication between the UFS host and the UFS device.

## **UFS Implementation Detail**

In the diagram below, the implementation of a UFS host or device is simplified to the M-PHY, digital (UniPro) core and the interface to either the Soc or the NAND Flash memory. We will examine each of these in detail.

## Figure 2. UFS to UFS Interface

Arasan Chip Systems Inc. White Paper, "Universal Flash Storage: Mobilize Your Data" at 6 (Oct. 2012).

## M-PHY I/O

MIPI defines two types of M-PHY, type 1 and type 2. The UFS specification calls out type 1. M-PHY Type 1 uses NRZ signaling for HS and PWM signaling for LS, while type 2 uses NRZ signaling for both HS and LS.

UFS utilizes two speed modes, high-speed and low-speed. Low speed mode In Gear 1 is used upon power up or reset, then a transition occurs to high-speed gears for data transmission. The low speed gears and high-speed gears are listed here for your reference. UFS v1.1 has been ratified and supports HS Gear 2 running approximately @ 3Gbps per lane. The UFS spec also supports up to 4 lanes for higher throughput.

Id.

34. UFS hosts and devices, which are included in the '092 Accused Products, multiplex clock and data signals for transmission over a single communications channel. This clock signal is modulated based on the data to be transmitted before being combined with the output data stream.

## Case 3:18-cv-02932-M Document 1 Filed 11/02/18 Page 10 of 76 PageID 10

35. The '092 Accused Products thus include each and every limitation of claim 1 of the '092 patent; accordingly, they literally infringe this claim. ZTE directly infringes the '092 patent by making, using, offering to sell, selling, and/or importing the '092 Accused Products. ZTE is thereby liable for direct infringement.

36. During discovery and development of its infringement contentions, Plaintiff may provide additional theories under which ZTE infringes the '092 patent besides the example provided above, including for the same product and using the same components identified above, and nothing in the example above is meant to limit the infringement allegations of Plaintiff or limit the interpretations of the claims or their terms.

37. At a minimum, ZTE has known that the '092 Accused Products infringe the '092 patent at least as early as the service date of this Original Complaint.

38. Upon information and belief, since at least the above-mentioned date when ZTE was on notice of its infringement, ZTE has actively induced, under U.S.C. § 271(b), third-party manufacturers, distributors, importers and/or consumers that purchase or sell the '092 Accused Products that include all of the limitations of one or more claims of the '092 patent to directly infringe one or more claims of the '092 patent by making, having made, using, offering for sale, selling, and/or importing the '092 Accused Products. Since at least the notice provided on the above-mentioned date, ZTE does so with knowledge, or with willful blindness of the fact, that the induced acts constitute infringement of the '092 patent. Upon information and belief, ZTE intends to cause, and has taken affirmative steps to induce, infringement by these third-party manufacturers, distributors, importers, and/or consumers by, inter alia, creating advertisements that promote the infringing use of the '092 Accused Products, creating established distribution channels for the '092 Accused Products into and within the United States, manufacturing the '092

Accused Products in conformity with U.S. laws and regulations, distributing or making available instructions or manuals for these products to purchasers and prospective buyers, and/or providing technical support, replacement parts, or services for these products to these purchasers in the United States. For example, ZTE advertises, provides support for, and publishes a user manual for the Axon 7 on its own website at the following web address: https://www.zteusa.com/axon-7.

39. Super Interconnect has been damaged as a result of ZTE's infringing conduct described in this Count. ZTE is, thus, liable to Super Interconnect in an amount that adequately compensates Super Interconnect for ZTE's infringement, which, by law, cannot be less than a reasonable royalty, together with interest and costs as fixed by this Court under 35 U.S.C. § 284.

## <u>COUNT III</u> (INFRINGEMENT OF U.S. PATENT NO. 7,158,593)

40. Super Interconnect incorporates paragraphs 1 through 39 herein by reference.

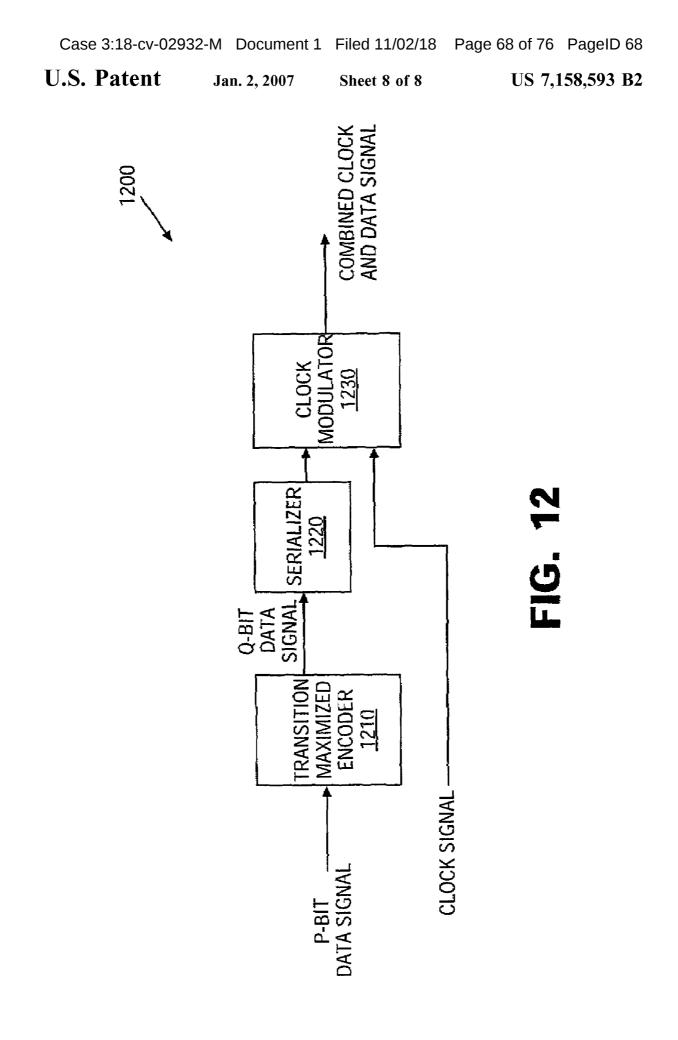

41. Super Interconnect is the assignee of the '593 patent, entitled "Combining a Clock Signal and a Data Signal," with ownership of all substantial rights in the '593 patent, including the right to exclude others and to enforce, sue, and recover damages for past and future infringement. A true and correct copy of the '593 patent is attached as <u>Exhibit C</u>.

42. The '593 patent is valid, enforceable, and was duly issued in full compliance with Title 35 of the United States Code. The '593 patent issued from U.S. Patent Application No. 10/099,533.

43. To the extent any marking or notice was required by 35 U.S.C. § 287, Super Interconnect and all predecessors-in-interest to the '593 patent have complied with the requirements of that statute by providing actual or constructive notice to ZTE of its alleged infringement. 44. ZTE has and continues to directly and/or indirectly infringe (by inducing infringement and/or contributing to infringement) one or more claims of the '593 patent in this judicial district and elsewhere in the United States, including at least claims 34 and 35, by, among other things, making, having made, using, offering for sale, selling, and/or importing electronic devices with Universal Flash Storage (UFS) that incorporate the fundamental technologies covered by the '593 patent. These products are referred to as the "'593 Accused Products." Examples of the '593 Accused Products include, but are not limited to, the ZTE Axon 7 smartphone.

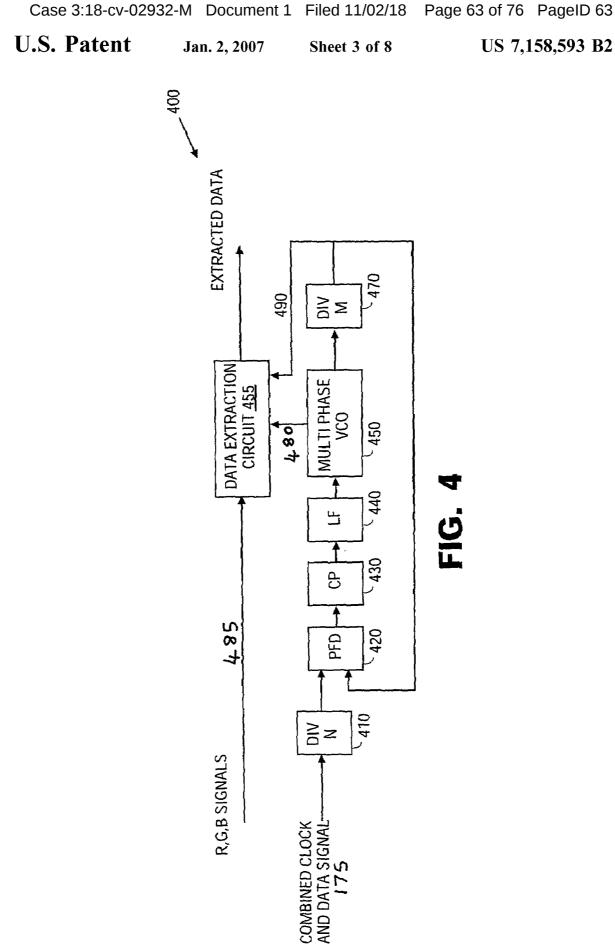

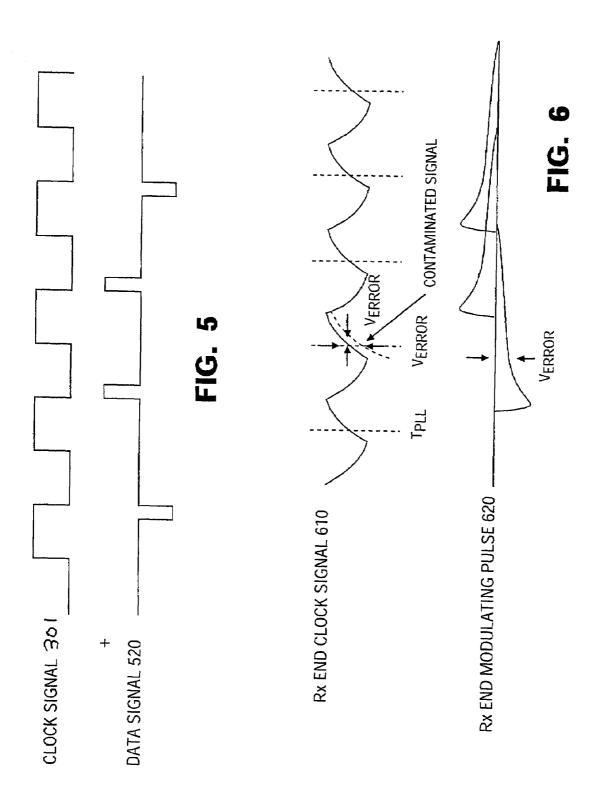

45. The ZTE Axon 7 directly infringes claim 34 of the '593 patent, as shown in the below paragraphs.

46. An example of the ZTE Axon 7 is shown in the image below.

47. ZTE incorporates UFS 2.0 storage in the Axon 7, as shown in the image below.

| Memory                   |                                           |

|--------------------------|-------------------------------------------|

| Internal Memory<br>(ROM) | - 64 GB (4 GB RAM)<br>- 128 GB (6 GB RAM) |

| Internal Storage<br>Type | UFS 2.0 (Universal Flash Storage)         |

http://newst8.com/specifications/zte-axon-7-full-specification-and-features-8520852025

48. The images below show that the ZTE Axon 7's UFS storage uses the MIPI M-PHY

protocol for physical layer communication between the UFS host and the UFS device.

## **UFS Implementation Detail**

In the diagram below, the implementation of a UFS host or device is simplified to the M-PHY, digital (UniPro) core and the interface to either the Soc or the NAND Flash memory. We will examine each of these in detail.

## Figure 2. UFS to UFS Interface

Arasan Chip Systems Inc. White Paper, "Universal Flash Storage: Mobilize Your Data" at 6 (Oct. 2012).

## M-PHY VO

MIPI defines two types of M-PHY, type 1 and type 2. The UFS specification calls out type 1. M-PHY Type 1 uses NRZ signaling for HS and PWM signaling for LS, while type 2 uses NRZ signaling for both HS and LS.

UFS utilizes two speed modes, high-speed and low-speed. Low speed mode In Gear 1 is used upon power up or reset, then a transition occurs to high-speed gears for data transmission. The low speed gears and high-speed gears are listed here for your reference. UFS v1.1 has been ratified and supports HS Gear 2 running approximately @ 3Gbps per lane. The UFS spec also supports up to 4 lanes for higher throughput.

Id.

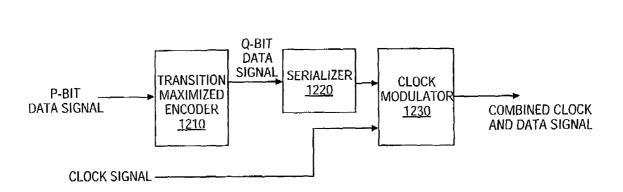

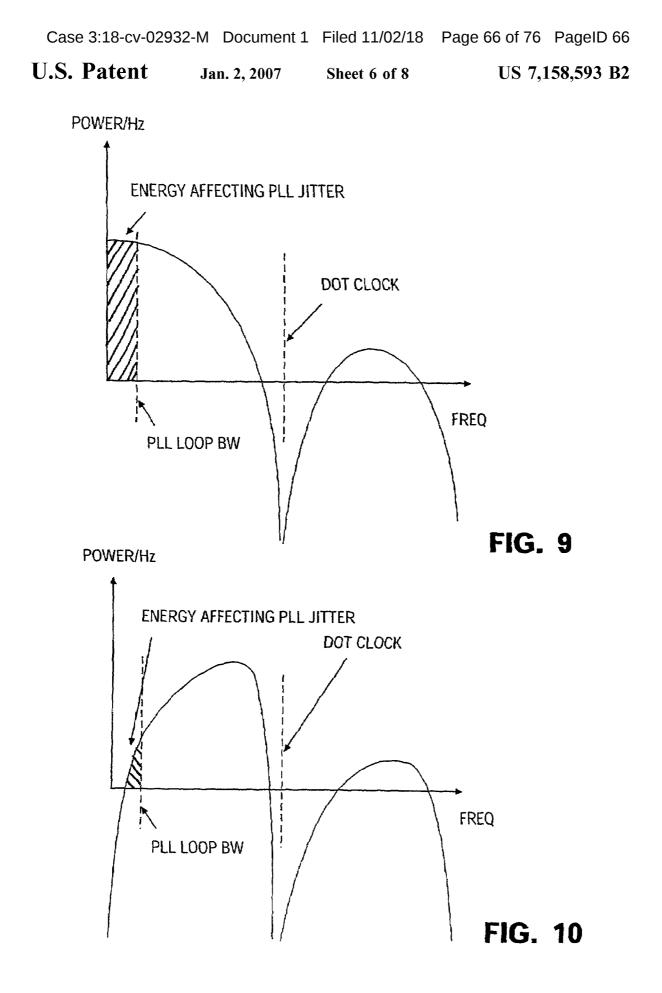

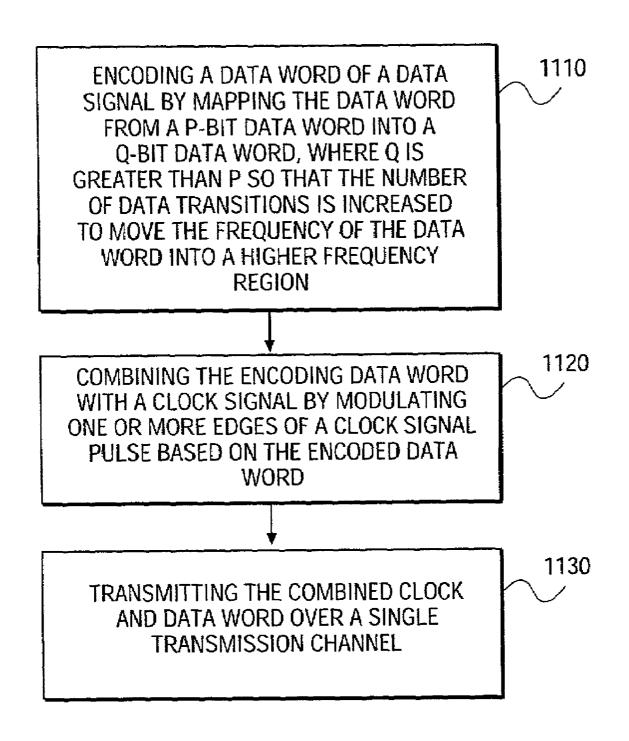

49. UFS hosts and devices, which are included in the '593 Accused Products, contain signal transmitters. These transmitters encode the data to be transmitted and further multiplex a pulse-width modulated clock signal, an encoded data signal, and control signals to apply them to

the communications channel. This encoding scheme shifts an energy spectrum of the combined clock and encoded data signal away from an effective loop bandwidth of a clock recovery block.

50. The '593 Accused Products thus include each and every limitation of claim 34 of the '593 patent; accordingly, they literally infringe this claim. ZTE directly infringes the '593 patent by making, using, offering to sell, selling, and/or importing the '593 Accused Products. ZTE is thereby liable for direct infringement.

51. During discovery and development of its infringement contentions, Plaintiff may provide additional theories under which ZTE infringes the '593 patent besides the example provided above, including for the same product and using the same components identified above, and nothing in the example above is meant to limit the infringement allegations of Plaintiff or limit the interpretations of the claims or their terms.

52. At a minimum, ZTE has known that the '593 Accused Products infringe the '593 patent at least as early as the service date of this Original Complaint.

53. Upon information and belief, since at least the above-mentioned date when ZTE was on notice of its infringement, ZTE has actively induced, under U.S.C. § 271(b), third-party manufacturers, distributors, importers and/or consumers that purchase or sell the '593 Accused Products that include all of the limitations of one or more claims of the '593 patent to directly infringe one or more claims of the '593 patent by making, having made, using, offering for sale, selling, and/or importing the '593 Accused Products. Since at least the notice provided on the above-mentioned date, ZTE does so with knowledge, or with willful blindness of the fact, that the induced acts constitute infringement of the '593 patent. Upon information and belief, ZTE intends to cause, and has taken affirmative steps to induce, infringement by these third-party manufacturers, distributors, importers, and/or consumers by, *inter alia*, creating advertisements

that promote the infringing use of the '593 Accused Products, creating established distribution channels for the '593 Accused Products into and within the United States, manufacturing the '593 Accused Products in conformity with U.S. laws and regulations, distributing or making available instructions or manuals for these products to purchasers and prospective buyers, and/or providing technical support, replacement parts, or services for these products to these purchasers in the United States. For example, ZTE advertises, provides support for, and publishes a user manual for the Axon 7 on its own website at the following web address: https://www.zteusa.com/axon-7.

54. Super Interconnect has been damaged as a result of ZTE's infringing conduct described in this Count. ZTE is, thus, liable to Super Interconnect in an amount that adequately compensates Super Interconnect for ZTE's infringement, which, by law, cannot be less than a reasonable royalty, together with interest and costs as fixed by this Court under 35 U.S.C. § 284.

### JURY DEMAND

Super Interconnect hereby requests a trial by jury pursuant to Rule 38 of the Federal Rules of Civil Procedure.

### PRAYER FOR RELIEF

Super Interconnect requests that the Court find in its favor and against ZTE, and that the Court grant ZTE the following relief:

- a. Judgment that one or more claims of the '044, '092, and '593 patents have been infringed, either literally and/or under the doctrine of equivalents, by ZTE and/or by others whose infringement has been induced by ZTE;

- b. Judgment that ZTE account for and pay to Super Interconnect all damages to and costs incurred by Super Interconnect because of ZTE's infringing activities and other conduct complained of herein;

- c. Judgment that ZTE account for and pay to Super Interconnect a reasonable, ongoing, post-judgment royalty because of ZTE's infringing activities and other conduct complained of herein;

- d. Judgment that ZTE's conduct warrants that the Court award treble damages pursuant to 35 U.S.C. § 284;

- e. Judgement that Super Interconnect be granted pre-judgment and post-judgment interest on the damages caused by ZTE's infringing activities and other conduct complained of herein;

- f. Judgment and an order finding this to be an exceptional case and requiring ZTE to pay the costs of this action (including all disbursements) and attorneys' fees as provided by 35 U.S.C. § 285; and

- g. That Super Interconnect be granted such other and further relief as the Court may deem just and proper under the circumstances.

Dated: November 2, 2018

Respectfully submitted,

## /s/Jeffrey R. Bragalone

Jeffrey R. Bragalone Texas Bar No. 02855775 T. William Kennedy Jr. Texas Bar No. 24055771 Brian P. Herrmann Texas Bar No. 24083174

## **Bragalone Conroy PC**

2200 Ross Avenue Suite 4500W Dallas, TX 75201 Tel: (214) 785-6670 Fax: (214) 785-6680 jbragalone@bcpc-law.com bkennedy@bcpc-law.com bherrmann@bcpc-law.com

# EXHIBIT A

Case 3:18-cv-02932-M Document 1

US007627044B2

## (12) United States Patent

### Kim et al.

### (54) CLOCK-EDGE MODULATED SERIAL LINK WITH DC-BALANCE CONTROL

- Inventors: Gyudong Kim, Sunnyvale, CA (US);

Won Jun Choe, Seoul (KR);

Deog-Kyoon Jeong, Seoul (KR); Jaeha Kim, Mountain View, CA (US);

Bong-Joon Lee, Seoul (KR); Min-Kyu Kim, Sunnyvale, CA (US)

- (73) Assignee: Silicon Image, Inc., Sunnyvale, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 605 days.

- (21) Appl. No.: 11/264,303

- (22) Filed: Oct. 31, 2005

### (65) **Prior Publication Data**

US 2007/0098112 A1 May 3, 2007

- (51) Int. Cl. *H04B 3/00* (20

### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 6,463,092 | B1   | 10/2002 | Kim et al.        |         |

|-----------|------|---------|-------------------|---------|

| 7,356,051 | B2 * | 4/2008  | Pasqualino et al. | 370/490 |

## (10) Patent No.: US 7,627,044 B2

## (45) **Date of Patent: Dec. 1, 2009**

| 7,363,575 1  | B2 *  | 4/2008 | Chung        | 714/759 |

|--------------|-------|--------|--------------|---------|

| 2004/0088633 | A1*   | 5/2004 | Lida et al   | 714/752 |

| 2004/0158873 | A1 *  | 8/2004 | Pasqualino   | 725/131 |

| 2005/0286643 | A1* 1 | 2/2005 | Ozawa et al. | 375/242 |

### OTHER PUBLICATIONS

Kyeongho Lee, et al., "1.04 GBd Low EMI Digital Video Interface System Using Small Serial Link Technique," *IEEE Journal of Solid-State Circuits*, vol. 33, No. 5, May 1998, pp. 816-823.

Wei-Hung Chen, et al., "A CMOS 400-Mb/s Serial Link for AS-Memory Systems Using a PWM Scheme," *IEEE Journal of Solid-State Circuits*, vol. 36, No. 10, Oct. 2001, pp. 1498-1505.

\* cited by examiner

Primary Examiner-Sam K Ahn

(74) Attorney, Agent, or Firm—Blakely Sokoloff Taylor & Zafman

### (57) ABSTRACT

A battery powered computing device has a channel configured as a single direct current balanced differential channel. A signal transmitter is connected to the channel. The signal transmitter is configured to apply clock edge modulated signals to the channel, where the clock edge modulated signals include direct current balancing control signals. A signal receiver is connected to the channel. The signal receiver is configured to recover the direct current balancing control signals.

#### 19 Claims, 8 Drawing Sheets

Dec. 1, 2009

Sheet 1 of 8

Dec. 1, 2009

U.S. Patent Dec. 1, 2009 Sheet 4 of 8 US 7,627,044 B2

FIG. 5

**U.S.** Patent

Dec. 1, 2009

Sheet 6 of 8

U.S. Patent De

Dec. 1, 2009

Sheet 7 of 8

US 7,627,044 B2

*FIG.* 7

FIG. 8A

U.S. Patent Dec. 1, 2009 Sheet 8 of 8 US 7,627,044 B2

FIG. 8C

### US 7,627,044 B2

10

60

### CLOCK-EDGE MODULATED SERIAL LINK WITH DC-BALANCE CONTROL

#### BRIEF DESCRIPTION OF THE INVENTION

This invention relates generally to the transmission of serial signals, such as in a transition minimized differential signaling system. More particularly, this invention relates to a clock-edge modulated serial link incorporating direct current (DC) balancing control signals.

### BACKGROUND OF THE INVENTION

Mobile devices, such as cellular phones, Personal Digital Assistants (PDAs) and portable game consoles continue to 15 grow in popularity. FIG. 1 illustrates an example of such a mobile device. In particular, FIG. 1 illustrates a mobile device 100 connected to a mobile display 102 via an interface 104. The mobile device 100 includes a central processing unit 106 and a graphic controller **108**. The mobile display **102** includes 20 a display controller 110 and a display 112, such as a liquid crystal display. A battery 114 powers the mobile device 100 and the mobile display 102. Low power design is critical in mobile applications of this type.

A conventional mobile device interface 104 uses parallel 25 channels with single-ended full-swing signaling. The channels are composed of many lines, for example, 22 lines with 18-bit video pixel data lines and control signal lines, such as dot-clock, data enable (DE), horizontal sync (HSYNC), vertical sync (VSYNC), and other display-specific configuration 30 settings. These signal lines consume power and space. In addition, they produce excessive electromagnetic radiation. To reduce the number of lines, a serial link with low-voltage swing differential signaling may be used. As known in the art, this type of signaling amplifies difference signals, while 35 may be configured in accordance with an embodiment of the rejecting common-mode signals.

Popular display interfaces, such as Low Voltage Differential Signaling (LVDS) and Digital Visual Interface (DVI) use 3 channels of serialized differential signals for 18-bit or 24-bit pixel color data. In addition, a separate channel is used for 40 modulation utilized in accordance with an embodiment of the clock transmission. In such an application, the voltage swing is reduced to about 400 mV.

In certain applications, such as a mobile display, relatively low video resolution is acceptable. In such a case, it is possible to use a single data channel. However, in this situation, 45 the prior art has relied upon a separate clock channel. Since the dedicated channel solely for clock transmission increases hardware costs and power, it would be desirable to remove the dedicated clock channel and use only a single channel for transmitting the clock, data and control signals. However, if 50 conventional network protocols, such as 802.3z Gigabit Ethernet are employed, a number of problems arise. For example, a local reference clock must be used at the receiver. This increases hardware costs and reduces flexibility in transmission bandwidth.

In view of the foregoing, it would be desirable to provide a low-power mobile device with a serial channel that supports clock, data and control signals, such as DC balancing control signals.

#### SUMMARY OF THE INVENTION

The invention includes a battery powered computing device with a channel configured as a single direct current balanced differential channel. A signal transmitter is con- 65 nected to the channel. The signal transmitter is configured to apply clock edge modulated signals to the channel, where the

clock edge modulated signals include direct current balancing control signals. A signal receiver is connected to the channel. The signal receiver is configured to recover the direct current balancing control signals.

The invention includes a signal transmitter. The signal transmitter has a channel node to interface with a single direct current balanced differential channel. Circuitry is connected to the channel node, the circuitry being configured to multiplex clock, data and control signals and apply them to the channel node. The clock signal is pulse width modulated to incorporate direct current balancing control signals.

The invention also includes a signal receiver. A channel node interfaces with a channel configured as a single direct current balanced differential channel. Circuitry is connected to the channel node. The circuitry is configured to de-multiplex clock, data and control signals from the channel node. The circuitry identifies direct current balancing control signals within a pulse width modulate clock signal.

The invention allows many parallel channels to be reduced to a single serial channel, which reduces power consumption. To further reduce power dissipation, the invention may be implemented with voltage-mode drivers. Still additional power reduction can be achieved by removing the source transmission channel termination and relying solely upon receiver side source transmission channel termination. The invention includes a delay-locked loop (DLL) data-recovery circuit that operates robustly in a high jitter environment.

### BRIEF DESCRIPTION OF THE FIGURES

The invention is more fully appreciated in connection with the following detailed description taken in conjunction with the accompanying drawings, in which:

FIG. 1 illustrates a mobile device and a mobile display that invention.

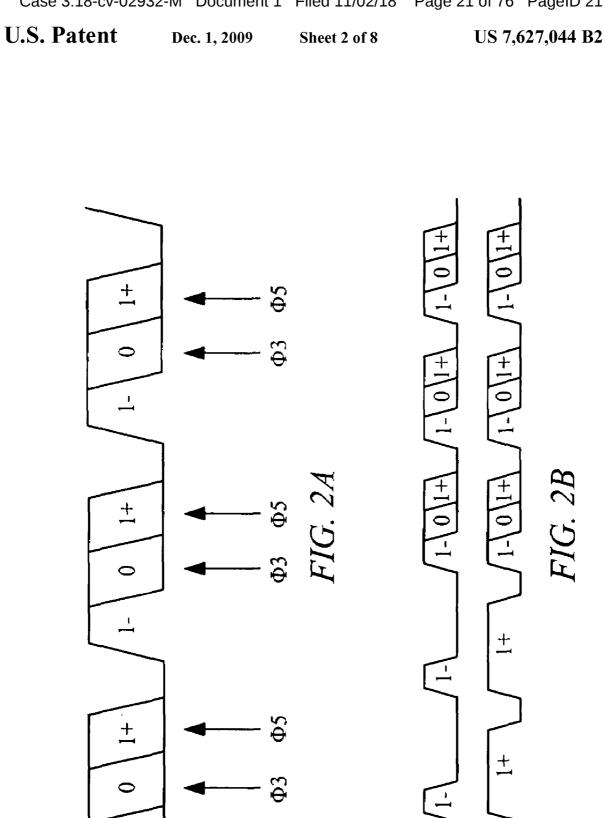

FIG. 2A illustrates DC-balanced clock-edge modulation in accordance with an embodiment of the invention.

FIG. 2B illustrates special character embedded clock-edge invention.

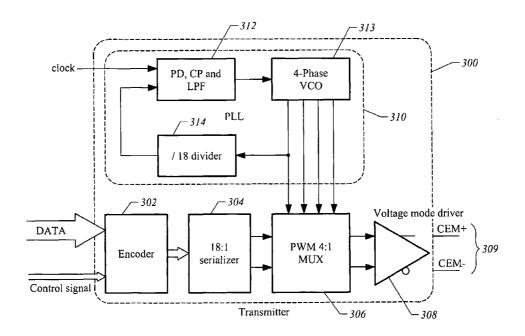

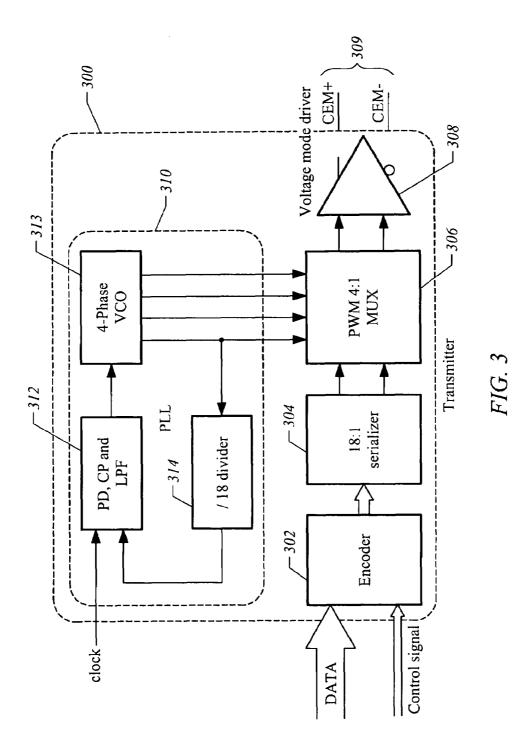

FIG. 3 illustrates a clock-edge modulated transmitter configured in accordance with an embodiment of the invention.

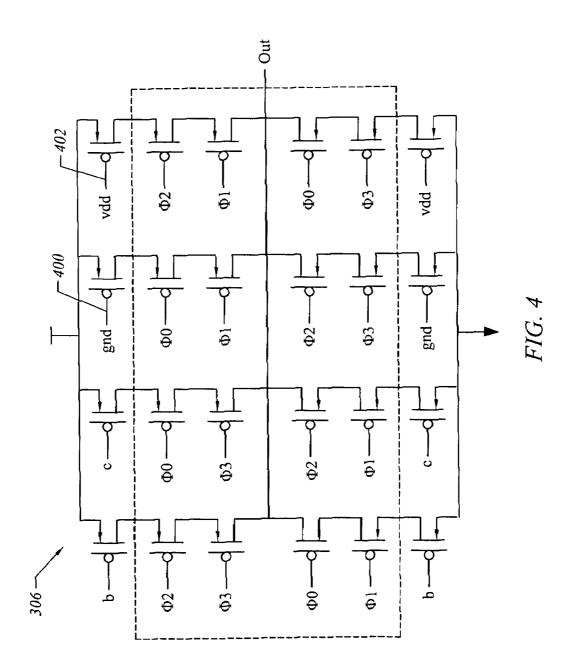

FIG. 4 illustrates a multiplexer that may be used in the clock-edge modulated transmitter of FIG. 3.

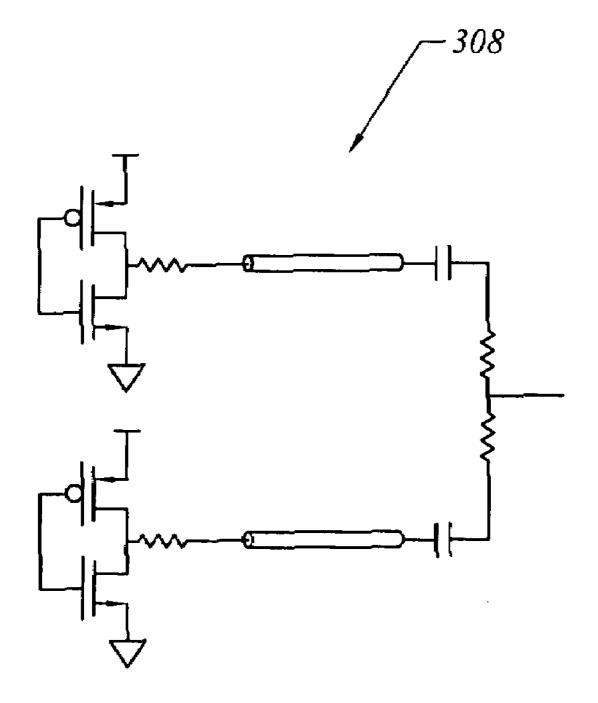

FIG. 5 illustrates a voltage mode driver utilized in accordance with an embodiment of the invention.

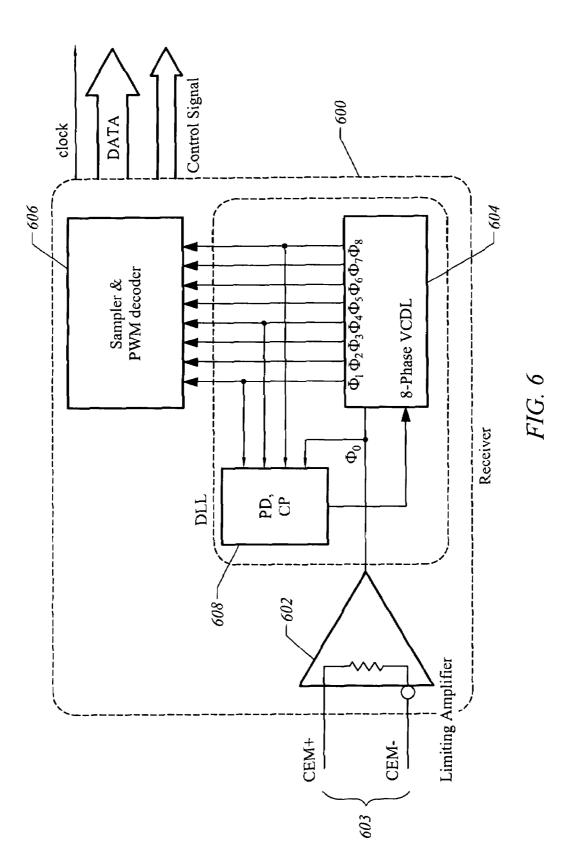

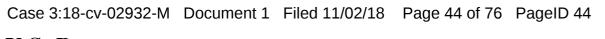

FIG. 6 illustrates a clock-edge modulated receiver configured in accordance with an embodiment of the invention.

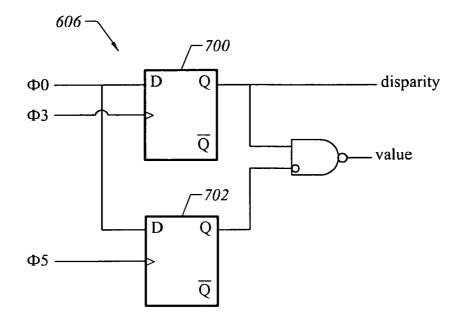

FIG. 7 illustrates clock-edge modulated decoder that may be used in accordance with an embodiment of the invention.

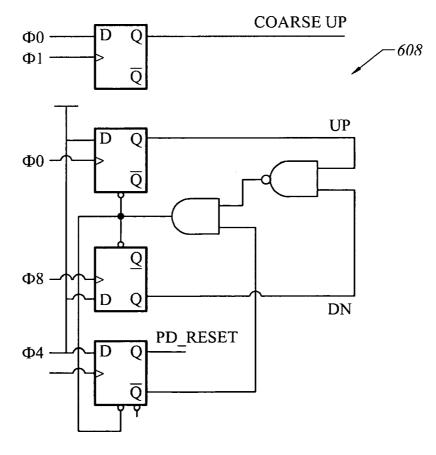

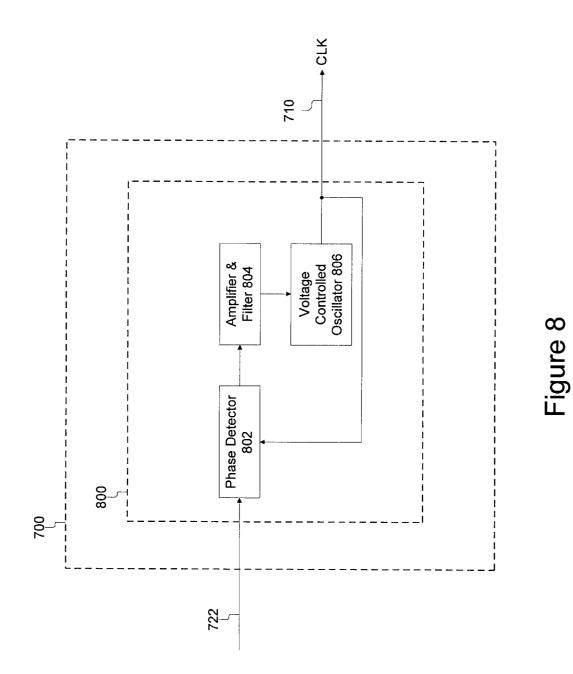

FIG. 8A illustrates a phase detector circuit configured in accordance with an embodiment of the invention.

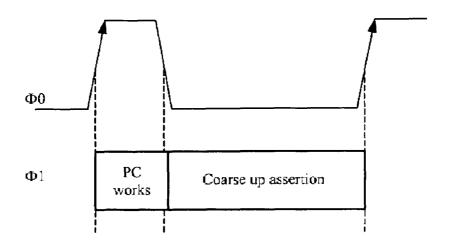

FIG. 8B illustrates the use of a coarse-up signal in accor-55 dance with an embodiment of the invention.

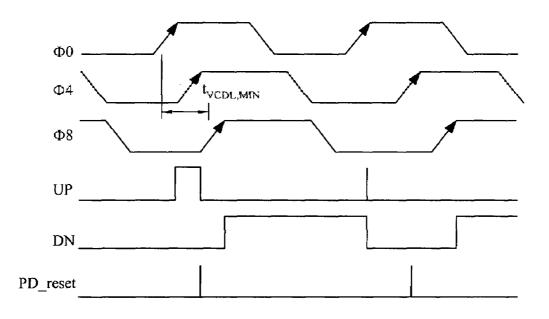

FIG. 8C illustrates various signals processed in accordance with an embodiment of the invention.

Like reference numerals refer to corresponding parts throughout the several views of the drawings.

### DETAILED DESCRIPTION OF THE INVENTION

The invention includes a single-channel serial link using clock edge modulation (CEM). This scheme, also known as pulse-width modulation (PWM), encodes data information onto a periodic clock by varying the position of a selected edge (i.e., the rising edge or falling edge); thus, the pulse-

10

15

45

width of the clock is altered or modulated. The invention provides techniques to transfer a clock signal, data and control signals over a single channel.

By way of example, the invention may be implemented by varying the falling edge of the clock signal. As shown in FIG. 5 2A, data are encoded as a variation of the clock falling edge position, while the position of the rising edge is fixed. The periodic occurrence of the rising edges enables easy extraction of the clock signal, from which the receiver can generate the "dot-clock" simply by dividing down the incoming signal (e.g., by 18) with no further clock recovery mechanism. The modulation of the falling edge position or the clock pulse width allows one to embed data and control signals in the clock, therefore reducing the pin count.

U.S. Pat. No. 6,463,092 (the '092 patent) utilizes a pulse width modulation technique of this type. The '092 patent, which is assigned to the assignee of the current invention, is hereby incorporated by reference. The current invention builds upon the disclosed scheme of the '092 patent to achieve DC-balancing. In one embodiment, DC-balancing is 20 achieved by inserting DC-balancing control signals into the serial link. The DC-balancing control signals may include signals to maintain DC-balance, increase DC-balance, and decrease DC-balance. Standard techniques are used to generate and process the DC-balance control signals. An aspect  $^{25}$ of the invention is directed toward incorporating the DCbalance control signals into a single serial link along with clock and data signals.

In one embodiment of the invention, the bit "0" is coded as a 50% duty cycle clock, indicating that no changes are necessary to keep balance. On the other hand, the bit "1" is coded as either a 25% or a 75% duty cycle clock, denoted as "1-" and "1+", respectively, in FIG. 2(a). Whether to use a 25% or a 75% duty cycle is determined by the DC value of the bits transmitted so far. If the DC value is lower than nominal, the bit "1" is coded as 75%, and vice versa. With this encoding, the maximum disparity counted in unit pulse length (i.e., 25% pulse width) is only 2 and good DC-balance is achieved.

The serial link may also be used to transmit control signals, 40 such as HSYNC and VSYNC. In one embodiment, these control signals are transmitted when DE is unasserted. Leveraging this fact, the state of DE being 0 is coded as two consecutive "1+"'s or "1-"'s, as shown in FIG. 2(b), which is an impossible sequence while the normal pixel data are being sent (i.e., DE is 1). This special sequence indicates that the following 16 pulse-width modulated symbols represent control characters. In this way, the control signals can be transmitted without requiring any additional channels. That is, the invention leverages the DE 0 state (when data is not being sent) to send DC-balance and other control information on a single channel.

FIG. 3 illustrates a transmitter 300 configured in accordance with an embodiment of the invention. The transmitter 300 includes an encoder 302 that receives data and control 55 signals. For example, the data may be 6 bits of red pixel data, 6 bits of green pixel data, and 6 bits of blue pixel data. The control signals may include HSYNC, VSYNC, and DE signals. The output of the encoder 302 is applied to a serializer circuit 304, which serializes the data and control information  $_{60}$ for the serial link. The encoder 302 or the serializer circuit 304 may be used to generate a DC-balance control signal.

The serialized data is then applied to a multiplexer, which receives control inputs form a phase-locked loop 310. The output of the multiplexer 306 is applied to a channel driver 65 308, in this case a voltage mode driver, which produces differential clock-edge modulated signals. In particular, the

channel driver 308 applies a positive CEM signal (CEM+) and a negative CEM signal (CEM-) to a channel node 309.

In one embodiment, the phase detector 312 of the phaselocked loop **310** multiplies the reference clock by 18 and operates with a voltage controlled oscillator 313 to generate 4 clock phases: 0(\u00f60), 90(\u00f61), 180(\u00662), and 270(\u00663). A divider 314 divides the multiplied clock signal and provides a feedback input to the phase detector 312. The transmitter operates as if it is sending 4 Non-Return to Zero (NRZ) bits per symbol using these clock phases. The phase signals are processed by the multiplexer 306.

FIG. 4 illustrates a pulse width modulated 4-to-1 multiplexer configured in accordance with an embodiment of the invention. Note that the first bit 400 and the last bit 402 are fixed at 1 and 0, respectively. Only the middle two bits (b and c in FIG. 4) need to vary to express the three different falling edge positions. The encoder 302 and serializer 304 may be used to generate these two bits from the parallel pixel data and control signals.

Since power consumption is a significant concern in a mobile device, an embodiment of the invention uses a voltage mode driver 308 for off-chip signaling in the CEM transmitter. FIG. 5 illustrates a known voltage mode driver that may be used in accordance with an embodiment of the invention. Unlike other prior art drivers, the voltage mode driver does not have a current source stack, hence it is capable of low voltage operation. To reduce the power consumption, the voltage mode driver is designed to operate at 1.2V supply and the voltage swing is also reduced to 80 mV. Since the link span of the mobile display is short (less than several inches) and the CEM signal is relatively immune to inter-symbol interference, an 80 mV swing is enough to guarantee proper operation of the receiver. Using the voltage mode driver with reduced swing, the CEM transmitter has been implemented to consume less than 1 mW when operating at 270 Mbps.

For the proposed CEM link, the data is delivered on the clock signal, making the receiver architecture much simpler. That is, the receiver does not require an NRZ phase detector nor a local frequency reference, as is the case in many serial link receivers. In one embodiment, the invention uses a delay locked loop (DLL) for data recovery, as shown in FIG. 6.

The receiver 600 has a front-end limiting amplifier 602 which receives differential input signals CEM+ and CEM- at channel node 603. The amplifier 602 facilitates an adequate signal level for the DLL input. A voltage-controlled delay line (VCDL) 604 generates 8-phase delayed clocks to sample and decode the CEM data. FIG. 2(a) shows a timing relationship between sampling clocks and input CEM data. In one embodiment, the sampler 606 examines the CEM data at two different phases ( $\phi$ 3 and  $\phi$ 5, as shown in FIG. 2A) to identify the location of the clock falling edge.

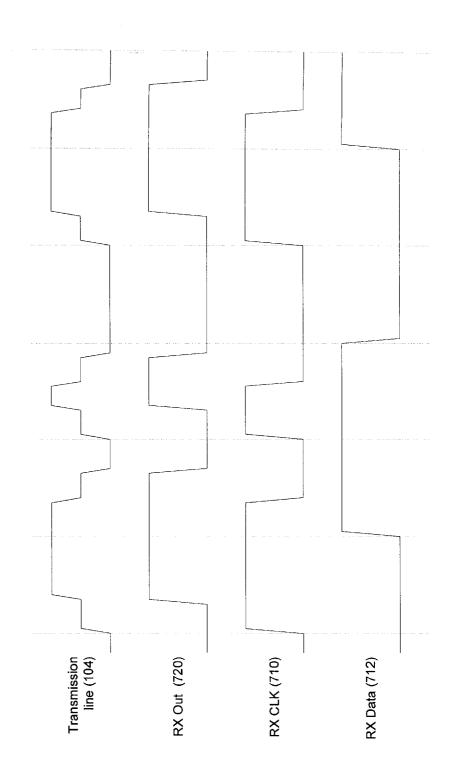

FIG. 7 illustrates a sampler and pulse-width modulated decoder 606 implemented with two flip-flops 700 and 702. Each flip-flop receives the  $\phi 0$  signal, while flip flop 700 receives the  $\phi$ 3 signal and flip flop 702 receives the  $\phi$ 5 signal. Using the sampled results, the CEM decoder extracts the data and disparity information. From the disparity information, the receiver can detect the pixel boundary and special sequences indicating DE, HSYNC, and VSYNC.

As shown in FIG. 6, the input CEM data is sampled by its own delayed version. So, the DLL can recover data even if the input clock has a large amount of jitter. To ensure enough lock range of the DLL, a phase detector 608 with false-lock detection may be used. FIG. 8A illustrates a phase detector 608 configured in accordance with an embodiment of the invention. If the initial delay of VCDL is larger than  $2 \times T_{CLK}$ , i.e., the rising edge of the  $\phi 1$  clock is located in the shaded area of US 7,627,044 B2

5

45

50

FIG. **8**(*b*), the coarse\_up signal is asserted to prevent harmonic lock. On the other hand, when the initial delay is so small that the VCDL delay would be stuck to its minimum value, the PD\_reset signal is asserted to deactivate the false up signal. This is accomplished by comparing rising edges of  $\phi 0$ and  $\phi 4$ , as shown in FIG. **8**(*c*). If the rising edge of  $\phi 4$  is found between  $\phi 0$  and  $\phi 8$ , the phase detector no longer generates an up signal, but makes the VCDL slow down.

The clock-edge modulated serial link of the invention has been fabricated in a standard  $0.18 \,\mu\text{m}$  CMOS technology. The 10 fabricated chip consumes  $3.12 \,\text{mW}$  at  $1.2 \,\text{V}$  supply voltage when operating at 270 Mb/s.

Those skilled in the art will appreciate that the invention may be implemented with various modifications. For example, the serial link may be augmented with multiple 15 links to increase throughput. In addition, the invention can be utilized in a bidirectional (full-duplex) mode. Also, since differential mode signals are used, there is a common mode signal that may be used for other purposes. For example, the common mode signal may be used to exchange configuration 20 data. The configuration data may specify such parameters as data format, data destination (when multiple transmitters/ receivers are connected on the bus), data directionality, and the like.

The foregoing description, for purposes of explanation, 25 used specific nomenclature to provide a thorough understanding of the invention. However, it will be apparent to one skilled in the art that specific details are not required in order to practice the invention. Thus, the foregoing descriptions of specific embodiments of the invention are presented for pur- 30 poses of illustration and description. They are not intended to be exhaustive or to limit the invention to the precise forms disclosed; obviously, many modifications and variations are possible in view of the above teachings. The embodiments were chosen and described in order to best explain the prin- 35 ciples of the invention and its practical applications, they thereby enable others skilled in the art to best utilize the invention and various embodiments with various modifications as are suited to the particular use contemplated. It is intended that the following claims and their equivalents 40 define the scope of the invention.

The invention claimed is:

- 1. A signal transmitter, comprising:

- a channel node to interface with a single direct current balanced differential channel; and

- circuitry connected to the channel node, the circuitry being configured to multiplex clock, data and control signals and apply them to the channel node, wherein the clock signal is pulse width modulated to incorporate direct current balancing control signals.

2. The signal transmitter of claim 1 wherein the circuitry is configured to specify a low direct current value at a first duty cycle position.

**3**. The signal transmitter of claim **2** wherein the circuitry is configured to specify a high direct current value at a second 55 duty cycle position.

**4**. The signal transmitter of claim **3** wherein the circuitry is configured to specify a no change direct current value at a third duty cycle position.

**5**. The signal transmitter of claim **1** wherein the circuitry 60 generates multiple phase signals.

6

6. The signal transmitter of claim 5 wherein the circuitry includes a multiplexer to process the multiple phase signals and serialized data.

7. The signal transmitter of claim 6 wherein the circuitry includes a voltage mode driver to process the output of the multiplexer.

**8**. A signal receiver, comprising:

- a channel node to interface with a channel configured as a single direct current balanced differential channel; and

- circuitry connected to the channel node, the circuitry configured to de-multiplex clock, data and control signals from the channel node, wherein the circuitry identifies direct current balancing control signals within a pulse width modulated clock signal.

**9**. The signal receiver of claim **8** wherein the circuitry includes an amplifier to process signals from the channel.

**10**. The signal receiver of claim **9** wherein the circuitry includes a delay-locked loop to process output from the amplifier.

**11**. The signal receiver of claim **10** wherein the delay-locked loop generates multiple phase signals for application to a pulse width modulated decoder.

**12**. The signal receiver of claim **11** wherein the delay-locked loop generates multiple phase signals for application to a phase detector.

- 13. A battery powered computing device, comprising:

- a channel configured as a single direct current balanced differential channel;

- a signal transmitter connected to the channel, the signal transmitter being configured to multiplex clock, data, and control signals, wherein the clock signal is pulse width modulated to incorporate direct current balancing control signals, the signal transmitter configured to apply the multiplexed signals to the channel; and

- a signal receiver connected to the channel, the signal receiver configured to de-multiplex the clock, data and control signals from the channel node, the signal receiver configured to identify and recover the direct current balancing control signals from the pulse width modulated clock signal.

14. The battery powered computing device of claim 13 wherein the signal transmitter includes a voltage-mode driver.

**15**. The battery powered computing device of claim **13** wherein the channel is terminated only at the signal receiver.

**16**. The battery powered computing device of claim **13** further comprising a graphics controller connected to the signal transmitter.

**17**. The battery powered computing device of claim **13** further comprising a display controller connected to the signal receiver.

18. The battery powered computing device of claim 13 wherein the signal transmitter and the signal receiver are configured to exchange configuration information using a common mode signal on the channel.

**19**. The battery powered computing device of claim **13** wherein the signal transmitter and the signal receiver are configured for bidirectional data transfers over the channel.

\* \* \* \* \*

## Case 3:18-cv-02932-M Document 1 Filed 11/02/18 Page 31 of 76 PageID 31 UNITED STATES PATENT AND TRADEMARK OFFICE CERTIFICATE OF CORRECTION

PATENT NO.

: 7,627,044 B2

APPLICATION NO.

: 11/264303

DATED

: December 1, 2009

INVENTOR(S)

: Kim et al.

Page 1 of 1

It is certified that error appears in the above-identified patent and that said Letters Patent is hereby corrected as shown below:

On the Title Page:

The first or sole Notice should read --

Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 1001 days.

Signed and Sealed this

Second Day of November, 2010

Jand J. 1pos 9

David J. Kappos Director of the United States Patent and Trademark Office

## **EXHIBIT B**

US006463092B1

## (12) United States Patent

### Kim et al.

### (54) SYSTEM AND METHOD FOR SENDING AND RECEIVING DATA SIGNALS OVER A CLOCK SIGNAL LINE

- (75) Inventors: Gyudong Kim, Sunnyvale, CA (US); Min-Kyu Kim, Cupertino, CA (US); Seung Ho Hwang, Palo Alto, CA (US)

- (73) Assignee: Silicon Image, Inc., Sunnyvale, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 09/393,235

- (22) Filed: Sep. 9, 1999

### **Related U.S. Application Data**

- (60) Provisional application No. 60/099,770, filed on Sep. 10, 1998.

- (51) Int. Cl.<sup>7</sup> ..... H04B 1/38

- 370/284; 370/301

### (56) References Cited

#### **U.S. PATENT DOCUMENTS**

4,459,591 A 7/1984 Haubner et al. ...... 340/825.57 5,577,071 A 11/1996 Gehrke et al. ...... 375/259

### FOREIGN PATENT DOCUMENTS

### EP 0 798 901 A1 10/1997

FR

(10) Patent No.:

(45) Date of Patent:

2 251 139

6/1975 ..... H04L/5/14

US 6,463,092 B1

Oct. 8, 2002

#### OTHER PUBLICATIONS

"Phase Modulation I/O Interface Circuit"; Kazutaka Nogami et al.; IEEE International Solid–State Circuit Conference; vol. 37 Feb. 1994 (New York, US); 3 pages.

Loinaz, Marc J., Wooley, Bruce A., "A BiCMOS Time Interval Digitizer for High–Energy Physics Instrumentation", Center for Integrated Systems, Stanford University, IEEE 1993 Custom Integrated Circuits Conference, pp. 28.6.1–28.6.4.

Primary Examiner—Chi Pham

Assistant Examiner—Khanh Cong Tran (74) Attorney, Agent, or Firm—Perkins Coie LLP; Paul Hickman; Steve S. Kelley

### (57) ABSTRACT

The system preferably includes a unique transmitter that sends both clock and data signals over the same transmission line. The receiver uses the same transmission line to send data signals back to the transmitter. The transmitter comprises a clock generator, a decoder and a line interface. The clock generator produces a clock signal that includes a variable position falling edge. The falling edge position is decoded by the receiver to extract data from the clock signal. The receiver comprises a clock re-generator, a data decoder and a return channel encoder. The clock re-generator monitors the transmission line, receives signals, filters them and generates a clock signal at the receiver from the signal on the transmission line. The return channel encoder generates signals and asserts them on the transmission line. The signal is asserted or superimposed over the clock & data signal provided by the transmitter.

### 26 Claims, 17 Drawing Sheets

..... H04L/25/49

| U.S. Patent | Oct. 8, 2002 | Sheet 1 of 17 | US 6,463,092 B1 |

|-------------|--------------|---------------|-----------------|

|             | ·····        |               |                 |

Figure 1

U.S. Patent Oct. 8, 2002 Sheet 2 of 17 US 6,463,092 B1

Figure 2

U.S. Patent

Oct. 8, 2002

Sheet 3 of 17

US 6,463,092 B1

U.S. Patent

Oct. 8, 2002

Sheet 4 of 17

US 6,463,092 B1

| Case 3:18-cv-02932-M | Document 1 | Filed 11/02/18 | Page 38 of 76 | PageID 38 |

|----------------------|------------|----------------|---------------|-----------|

|                      |            |                |               |           |

| U.S. Patent Oct. 8, 2002 Sheet 5 of 17 US 6,463,09 |

|----------------------------------------------------|

|----------------------------------------------------|

Figure 5A

U.S. Patent Oct. 8, 2002 Sheet 6 of 17 US 6,463,092 B1

Oct. 8, 2002

Sheet 7 of 17

US 6,463,092 B1

| U.S. Patent | Oct. 8, 2002 | Sheet 8 of 17 | US 6,463,092 B1 |

|-------------|--------------|---------------|-----------------|

|             | Oct. 0, 2002 | Sheet o UI 17 | US 0,403,092 D. |

Figure 6B

**U.S.** Patent

Oct. 8, 2002

Sheet 9 of 17

Figure 7

| U.S. | Patent | Oct. 8, 2002 |

|------|--------|--------------|

|------|--------|--------------|

Sheet 10 of 17

| U.S. Patent | Oct. 8, 2002 | Sheet 11 of 17 | US 6,463,092 B1 |

|-------------|--------------|----------------|-----------------|

|-------------|--------------|----------------|-----------------|

| U.S. Patent | Oct. 8, 2002 | Sheet 12 of 17 | US 6,463,092 B1 |

|-------------|--------------|----------------|-----------------|

|             |              |                |                 |

Figure 10A

| U.S. Patent | Oct. 8, 2002 | Sheet 13 of 17 | US 6,463,092 B1 |

|-------------|--------------|----------------|-----------------|

|-------------|--------------|----------------|-----------------|

U.S. Patent Oct. 8, 2002 Sheet 14 of 17

US 6,463,092 B1

**U.S. Patent** Oct. 8, 2002 Sheet 15 of 17

US 6,463,092 B1

Figure 11B

U.S. Patent Oct. 8, 2002 Sheet 16 of 17 US 6,463,092 B1

Figure 12A

U.S. Patent Oct. 8, 2002 Sheet 17 of 17 US 6,463,092 B1

Figure 12B

#### SYSTEM AND METHOD FOR SENDING AND **RECEIVING DATA SIGNALS OVER A** CLOCK SIGNAL LINE

This application claims benefit of provisional No. 5 60/099,770 filed Sep. 10, 1998.

#### CROSS-REFERENCES TO RELATED APPLICATIONS

This application is a utility conversion of U.S. Pat. No. 60/099,770, entitled "Embedded Back Channel For TMDS" by Gyudong Kim, filed Sep. 10, 1998.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates generally to the field of data communications, and more particularly, to the transmission of clock and data signals. Still more particularly, the present invention relates to the transmission of clock signals and data signals on the same transmission line in transition minimized differential signaling (TMDS) system.

2. Description of the Background Art

There are a variety of prior art systems and method for 25 transmitting data between a transmitter and a receiver. Various serial links and other methods for transmitting data and clock signals are well known. However, most such schemes provide a single line or channel dedicated for the transmission of the clock signals and other signal lines or 30 channels dedicated for the transmission of data. Once such system is described by Kyeongho Lee, Sungjoon Kim, Gijung Ahn, and Deog-kyoon Jeong in "A CMOS Serial Link For Fully Duplexed Data Communication," IEEE April 1995.

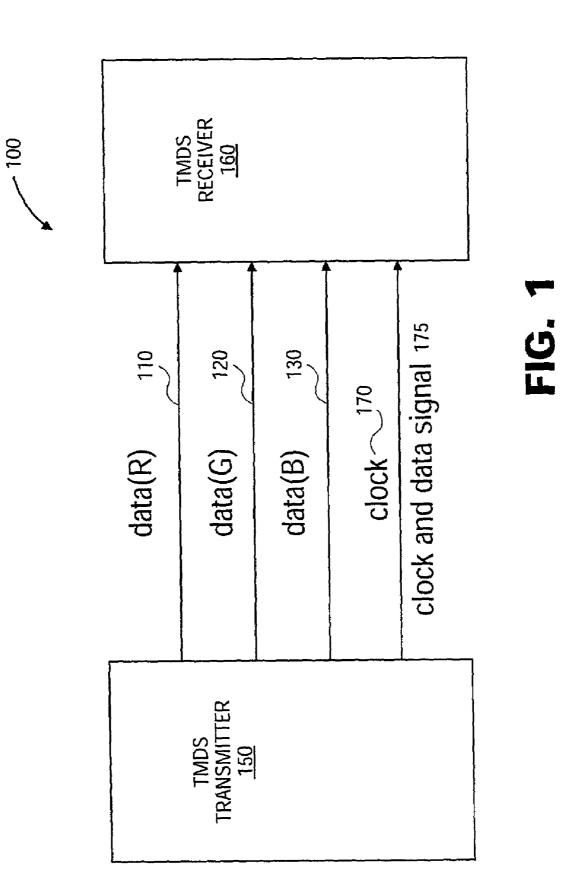

The present invention will be discussed in the context of transition minimized differential signaling (TMDS), however, those skilled in the art will recognize that the present invention is applicable in various other data com- 40 munication contexts. In TMDS, four signal lines are provided, and each signal line is preferably a differential pair. One signal line is a for a low speed clock signal and the three other signal lines are for high-speed data transmission.

One important aspect of all data communication systems 45 is to maximize the bandwidth provided by the data. channels. However, most systems include a variety of control signals that must be sent between the transmitter and the receiver to ensure proper operation, and maintain synchronization between the transmitter and the receiver. For 50 example, it is not uncommon for as much as 20% of the bandwidth to be used for framing and synchronization in serial communication. One problem is that the bandwidth available for data is typically reduced because the data signal lines must be used to transmit these control signals 55 signals on the transmission line, and filters and decodes the between the transmitter and receiver. Yet another problem is latency in transmitting the control signals to the recipient. Especially in video data communication, much of the data must be transmitted in blocks during which control signals cannot be sent. For example, when transmitting data from a 60 controller to a flat panel, the data is transmitted, and then there is a data enable period corresponding to the blanking period in CRT display that is used to send control and synchronization signal. Only during that data enable period can the control signals be sent under most protocols. Therefore, there is latency imposed on transmitting control signals to the receiver. Thus, there is need for a system that

2

can provide for control signaling between the transmitter and the receiver without decreasing the available bandwidth for data transfer, and while reducing the latency in sending control signals.

Yet another problem in the prior art is that most systems do not provide a mechanism to get signals from the receiver back to the transmitter. In other words, there is not a return channel for communication. Some systems have provided additional signal lines, however, their addition and interface 10 add significant complication, require re-wiring and create other problems that make the addition of a physical line unworkable. Another approach is to add a second transmitter, second receiver and signal lines. However, this essentially doubles the hardware requirements making such <sup>15</sup> a solution too expensive. Furthermore, such duplication is overkill for the amount of data that needs to be sent between the transmitter and the receiver, especially when the application is one of sending video data from a transmitter to a receiver such as communication between a graphic control-20 ler and a video display device.

Therefore, there is a need for a system and method for that uses the clock signal line also for transmitting data signals between the transmitter and the receiver and vice-versa.

#### SUMMARY OF THE INVENTION

The present invention overcomes the deficiencies and limitations of the prior art with a unique data communication system. The system preferably includes a unique transmitter and receiver coupled by a transmission line. The transmitter sends both a clock signal and data signals over the transmission line to the receiver. The receiver uses the same transmission line to send data signals back to the transmitter.

The transmitter preferably comprises a clock generator, a Journal of Solid State Circuits, Vol. 30, No. pp. 353-364, 35 decoder and a line interface. The clock generator produces a clock signal that includes a variable position falling edge. The falling edge position is decoded by the receiver to extract data in addition to the clock signal. The line interface couples the output of the clock generator to the transmission line. The line interface also couples the transmission line to the decoder and in doing so removes the signals from the clock generator. The decoder receives the signals from the line interface and decodes the signal to determine the data being sent from the receiver to the transmitter on the same line used to send the clock and data from the transmitter to the receiver.

> The receiver preferably comprises a line interface, a clock re-generator, a data decoder and a return channel encoder. The clock re-generator, the data decoder and the return channel encoder are coupled to the transmission line by the line interface. The clock re-generator monitors the transmission line, receives signals, filters them and generates a clock signal at the receiver from the signal on the transmission line. The data decoder similarly is coupled to receive the signals to produce data signals. This is preferably done by determining the position of the falling edge of the clock signal and translating the falling edge position into bit values. In contrast, the return channel encoder generates signals and asserts them on the transmission line. These signals are asserted or superimposed over the clock & data signals provided by the transmitter.

These and other features and advantages of the present invention may be better understood by considering the 65 following detailed description of a preferred embodiment of the invention. In the course of this description, reference will frequently be made to the attached drawings.

15

25

30

40

#### BRIEF DESCRIPTION OF THE DRAWINGS

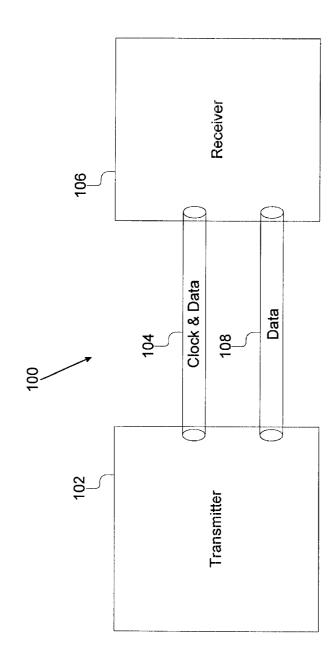

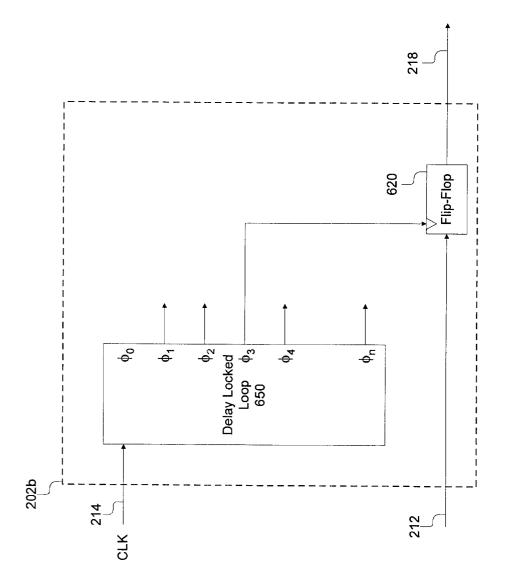

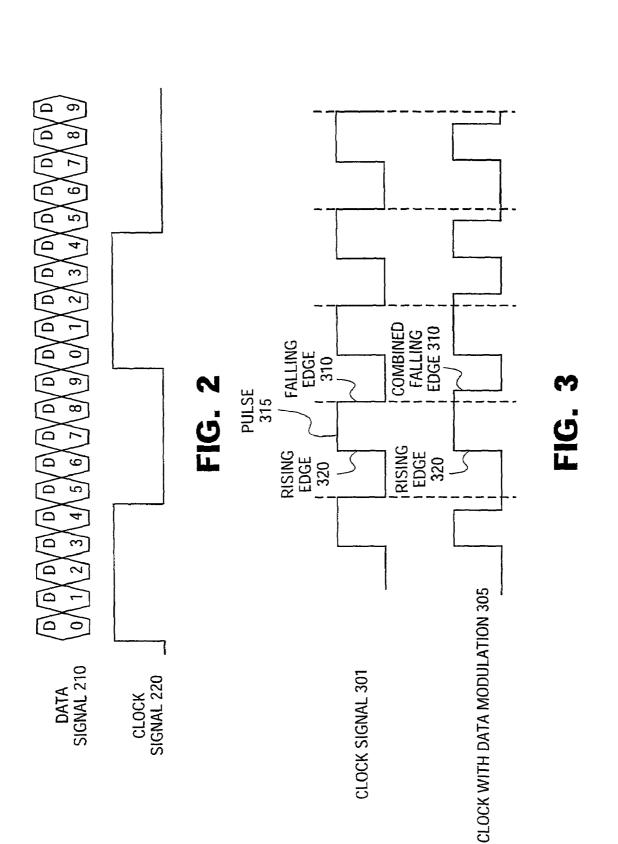

FIG. 1 is a block diagram of system including the combined clock and data signal line of the present invention.

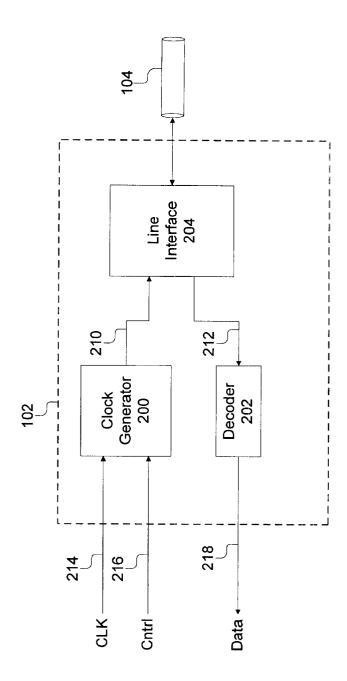

FIG. 2 is a block diagram of a portion of the transmitter showing a clock generator, decoder and a line interface.

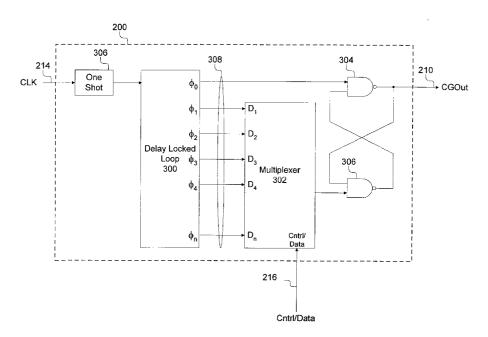

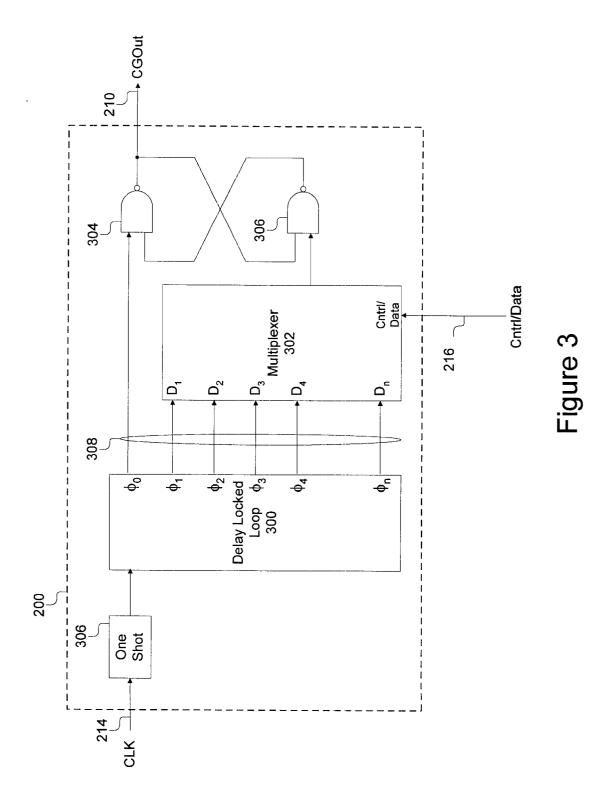

FIG. 3 is a block diagram of a preferred embodiment of the clock generator constructed in accordance with the present invention.

signals that the clock generator of the present invention produces

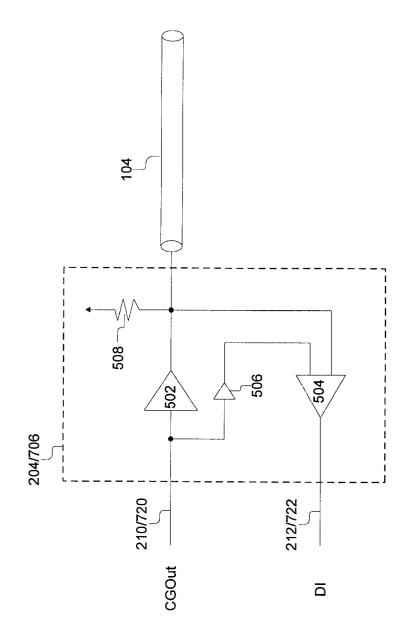

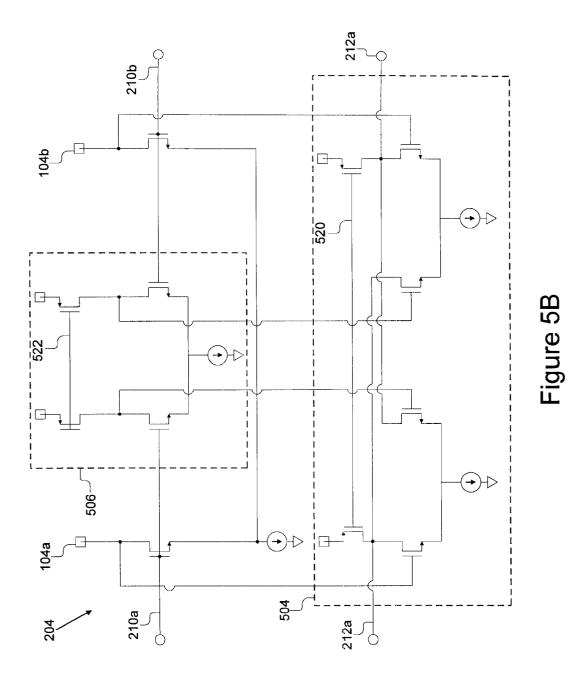

FIG. 5A is a block diagram of a preferred embodiment of the line interface constructed in accordance with the present invention.

FIG. 5B is a circuit diagram of the preferred embodiment of the line interface constructed in accordance with the present invention.

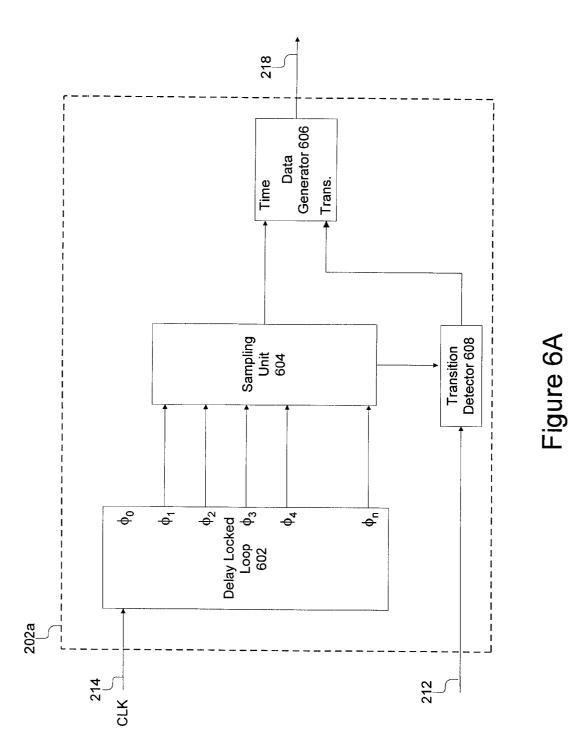

FIG. 6A is a block diagram of a first embodiment of the 20 decoder at the transmitter constructed in accordance with the present invention.

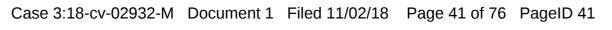

FIG. 6B is a block diagram of a second embodiment of the decoder at the transmitter constructed in accordance with the present invention.

FIG. 7 is a block diagram of a first embodiment of portions of the receiver relating to the present invention.

FIG. 8 is a block diagram of a first embodiment of a clock re-generator of the receiver.

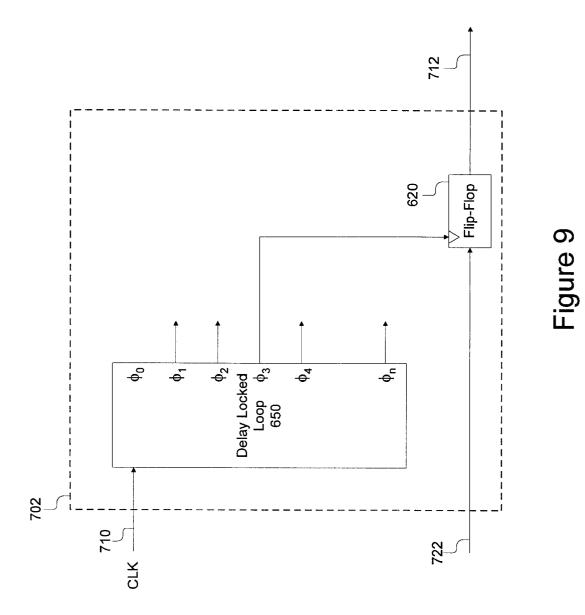

FIG. 9 is a block diagram of a preferred embodiment of a data decoder of the receiver.

FIG. 10A is a block diagram of a first embodiment of a return channel encoder of. the receiver.

embodiment of a return channel encoder of the receiver.

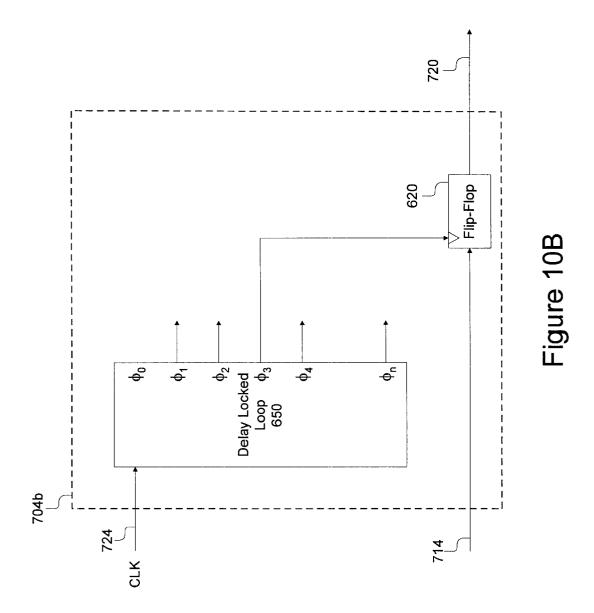

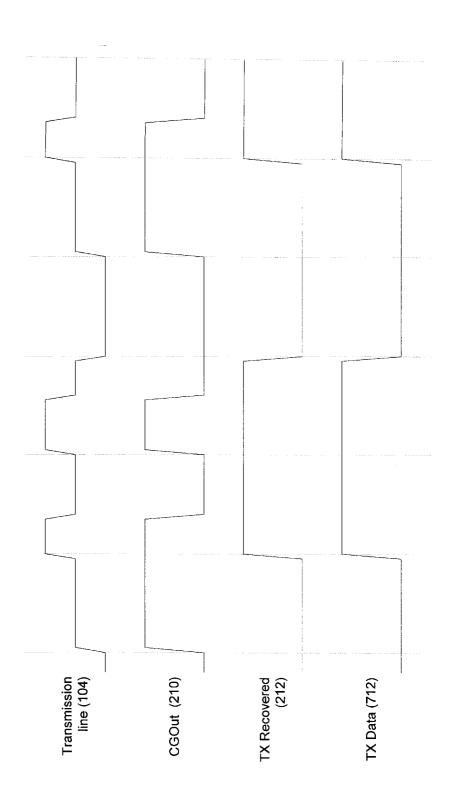

FIG. 11A is a timing diagram illustrating signals on the transmission line, and the clock and data signals generated by the transmitter for return to zero signaling.

FIG. 11B is a timing diagram illustrating signals on the transmission line, the data signal sent by the receiver, and the clock and data signals recovered by the receiver for return to zero signaling.

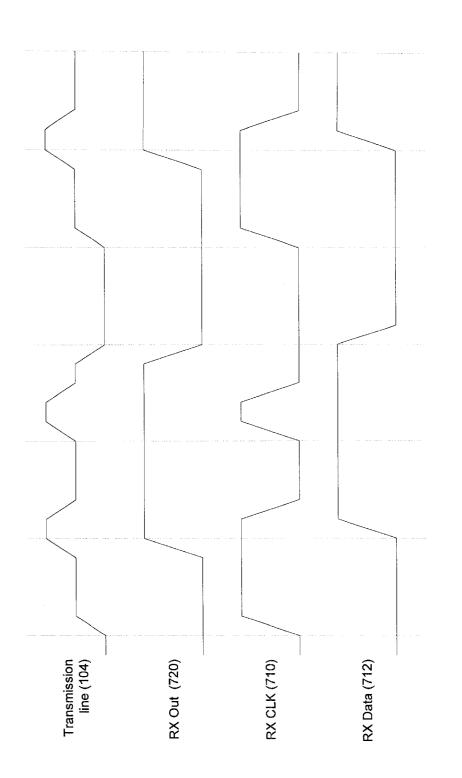

FIG. 12A is a timing diagram illustrating signals on the transmission line, and the clock and data signals generated by the transmitter for non-return to zero signaling.

FIG. 12B is a timing diagram illustrating signals on the transmission line, the data signal sent by the receiver, and the clock and data signals recovered by the receiver for non- 50 return to zero signaling.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Referring now to FIG. 1, a block diagram of system 100 55 including the combined clock and data signal line of the present invention is shown. The system 100 preferably includes a transmitter 102, a clock transmission line 104, a receiver 106 and one or more data transmission lines 108. The transmitter 102 preferably provides a clock signal as 60 well as data signals to the receiver 106 via the clock transmission line 104. These data signals are in addition to those provided to the receiver 106 via the high speed data transmission lines 108. The receiver 106 receives the signals on the transmission line 104 and from them, generates the 65 clock and data signals at the receiver 106. These data signals on the clock line 104 are again in addition to the data signals

1

that the receiver 106 recovers from the data transmission line 108. The transmitter 102 and the receiver 106 include logic for sending and receiving the data from data transmission line 108. This logic preferably includes transition control, DC balancing, and encoding/decoding in a conventional manner. For example, in addition to the components of the present invention for receiving and sending data and clock signals on the clock transmission line 104 that will be described below, the transmitter 102 and the receiver 106 FIG. 4 is a timing diagram illustrating various clock 10 respectively include conventional data transmission logic for TMDS such as that provided in PanelLink by Silicon Image of Cupertino, Calif. For ease of understanding that logic and the data transmission line 108 are omitted from the discussion below and the remaining figures. Those skilled in the art will also realize that while shown as a single line, the clock transmission line 104 and the data transmission line 108 are preferably each a differential pair of signal lines, and the signal is carried on the differential pair of lines. Furthermore, those skilled in the art will understand the preferred embodiment for the data transmission line 108 is three pairs of data lines.

Transmitter

Referring now to FIG. 2, a preferred embodiment of the transmitter 102 is shown in more detail. The transmitter 102 preferably comprises a clock generator 200, a line interface 204, and a decoder 202.

The clock generator 200 has a first input, a second input and an output. The clock generator 200 produces a clock signal that is encoded with data. The data is encoded into the clock signal by varying the modulation of the falling edge of the clock signal. In other words, the position of the falling edge of the clock relative to the rising edge indicates different data values. This is particularly advantageous because it preserves the rising edge of the clock for clock FIG. 10B is a block diagram of a second and alternate 35 recovery. All the activity for a bi-directional data link on the clock transmission line 104 is centered around the falling edge of the clock from the transmitter 102. While most of the present invention will be described in the context of the falling edge of the clock having two different positions, FIG. 3 and will also be described in the context of the falling edge of the clock having five different positions. Each of the four positions representing two bit values and one position representing no data. The first input of the clock generator 200 is coupled to line 214 to receive a clock signal either from 45 another portion of the transmitter **102** or from a oscillator or other conventional clock source. The second input of the clock generator 200 is coupled to line 216 to receive control/data signals. These control/data signals dictate the data or no data that is transmitted as part of the clock signal. These control/data signals may be from another portion of the transmitter 102 or from off chip control logic. The output of the clock generator 200 is provided on line 210 that is coupled to an input of the line interface **204**. The output of the clock generator 200 provides a CGOut signal.

> While the present invention is described throughout this application as preserving the rising edge for the clock signal and centering all the bi-directional data transmission about the falling edge, those skilled in the art will realize that an inverse scheme where the falling edge is preserved for recovering the clock and changes in position of the rising edge is used for encoding data is within the spirit and scope of the present invention.

> The line interface 204 has an input, an output and a bi-directional port. The line interface 204 couples the clock generator 200 and the decoder 202 to the clock transmission line 104. The input of the line interface 204 preferably couples line 210 to the clock transmission line 104 so that

the CGOut signal may be asserted over the clock transmission line 104. The output of the line interface 204 is coupled to the input of the decoder 202 by line 212. The line interface 204 advantageously receives the signal on the clock transmission line 104, removes the CGOut signal as will be described below with reference to FIGS. 5A and 5B, and sends the filtered signal as the input to the decoder 202. The bi-directional port of the line interface 204 is coupled to the clock transmission line 104..

The decoder 202 receives the filtered signals from the 10 transmission line 104 and decodes the signals to generate the data sent by the receiver 106. The decoder 202 preferably performs an inverse function to the encoder 704 (See FIG. 7) of the receiver 106 as will be described below.

Referring now to FIGS. 3 and 4, the preferred embodi- 15 ment for the clock generator 200 will be described. While the clock generator 200 will now be described as providing a clock signal having a falling edge in five possible locations to send two bits of data or no data in addition to the clock signal, those skilled in the art will recognize that this is only 20 by way of example. The clock generator 200 could be configured to send from 1 to n bits of data per clock cycle depending on the clock frequency and the number of possible locations for the falling edge of the clock signal. In general, n locations of the falling edge will allow up to log<sub>2</sub>n 25 bits of data to be transferred per clock cycle. The number of locations for the falling edge is limited only in that the first location must be such that the pulse width is greater than the logic-threshold crossing time of the rising edge, which may be viewed to be jitter by the phase-locked loop at the 30 receiver 106. In other words, the thresholds for set up and hold time in the logic must be sufficient to recognize a rising edge as the beginning of the clock cycle.

The clock generator 200 preferably generates a clock signal at the dot clock frequency, or the frequency used by 35 device (not shown) connected to the receiver 106 for the display of the data. The maximum symbol rate provided by data transfer as part of the clock signal matches the dot clock frequency. For example, if the dot clock is 100 MHz, the symbol rate is 100 Msymbols/s. The actual data rate will 40 depend on the modulation methods and the number of bits per clock or symbol that can be sent. If simple binary modulation is used, then the bit rate is the same and the clock rate with would provide an additional 100 Mb/s for control signals.

The clock generator 200 preferably comprises a monostable multivibrator 306, a delay-locked loop 300, a multiplexer 302, a first NAND gate 304 and a second NAND gate 306. The clock generator 200 preferably uses only return to zero signaling for sending the clock and data 50 signals. Non-return to zero signaling cannot be used for sending from the transmitter 102. The clock signal is received on line 214 and provided as input to the input of the one shot or monostable multivibrator 306. The monostable multivibrator 306 is provided to generate a signal with a 55 narrower pulse width than the clock signal. This is advantageous for use in other portions of the clock generator 200. In an alternative embodiment, the one shot 306, may be replaced by a plurality of monostable multivibrators each respectively coupled in series with an output signal line **308** 60 of the delay locked loop 300. Such an alternate embodiment provides more flexibility in the design of the delay locked loop 300 at the cost of additional monostable multivibrators will be understood by those skilled in the art. The output of the monostable multivibrator **306** is coupled to the input of 65 eliminates signal latency present in the prior art. With the the delay-locked loop 300. The delay-locked loop 300 is of a conventional type and in response to a signal at its input,

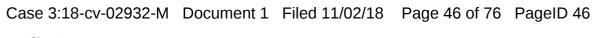

6

provides a plurality of outputs, each output being the same as the input only shifted in phase. The falling edge is modulated using a delay-locked loop 300. The falling edge is chosen from one of the phases provided by the delaylocked loop 300. It is preferable that the selected phases from the delay-locked loop 300 be the ones close to a 50%duty cycle. The delay-locked loop 300 preferably provides five output signals:  $\phi 0$ ,  $\phi 1$ ,  $\phi 2$ ,  $\phi 3$ ,  $\phi 4$ , and  $\phi n$ . The  $\phi 0$  signal is the clock signal unchanged. The  $\phi 1$ ,  $\phi 2$ ,  $\phi 3$ ,  $\phi 4$ , and  $\phi n$  are each phase shifted more with respect to the previous  $\phi$ signal. The  $\phi 0$  is coupled to a first input of the first NAND gate 304. The output of the first NAND gate 304 is provided on line 210 and provides the CGOut signal. The first NAND gate 304 is cross coupled with the second NAND gate 306 to form a set-reset latch. A rising edge on the  $\phi 0$  causes the output of first NAND gate 304 to be set high or asserted until reset to low by the second NAND gate 306. The remaining signals from the delay-locked loop 300,  $\phi$ 1,  $\phi$ 2,  $\phi$ 3,  $\phi$ 4, and φn are coupled to respective data inputs of the multiplexer **302**. The control input of the multiplexer **302** is coupled to line 216 to receive control/data signals. In response to the control/data signals on line 216, the multiplexer 302 will couple one of the signals from the delay-locked loop 300,  $\phi$ 1,  $\phi$ 2,  $\phi$ 3,  $\phi$ 4, and  $\phi$ n, to the input of the second NAND gate 306. Thus, the rising edge on the selected signal from the delay-locked loop 300,  $\phi$ 1,  $\phi$ 2,  $\phi$ 3,  $\phi$ 4, and  $\phi$ n, will cause the latch to be reset and create a falling edge on the output of the first NAND gate 304, and thus, line 210. Thus, it is apparent that using the control/data signals to select one of the signals, the position of the falling edge can be selected. For example control signals such as shown in Table I may be used to control the position of the falling edge.

TABLE I

| 5 | Control/data<br>Signal (216) | NAND-gate<br>306 input | Falling edge<br>Position | Data Sent |

|---|------------------------------|------------------------|--------------------------|-----------|

|   | 000                          | φ1                     | <b>T</b> 0               | 00        |

|   | 001                          | ф2                     | T1                       | 01        |

|   | 100                          | ф3                     | T2                       | 00        |

| ) | 010                          | φ4                     | T3                       | 10        |

|   | 011                          | φn                     | T4                       | 11        |

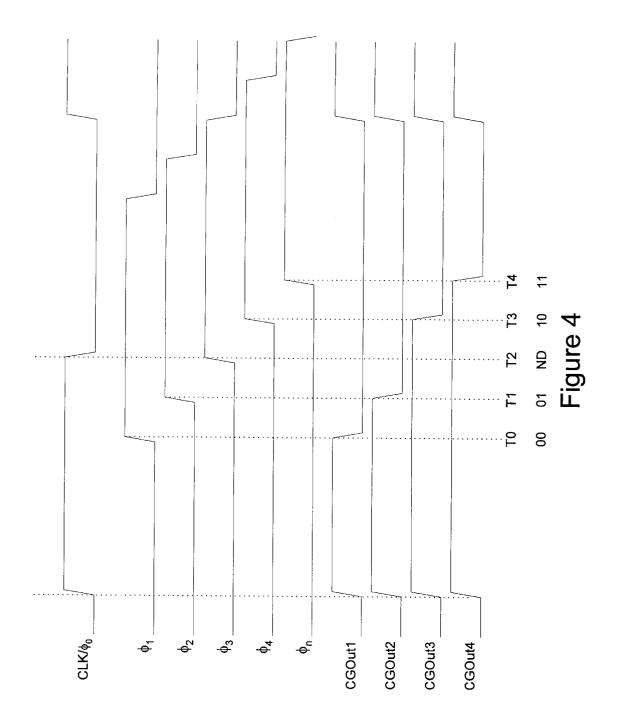

Those skilled in the art will recognize how the clock generator 200 could be modified to create any number of 45 different falling edge positions for the CGOut signal. Referring also to FIG. 4, a timing diagram of the clock/ $\phi$ 0,  $\phi$ 1,  $\phi$ 2,  $\phi$ **3**,  $\phi$ **4**, and  $\phi$ n and the possible CGOut signals are shown. There are five possible CGOut signals. First, the clock/\u00f40 signal is unchanged which is just the input signal with falling edge at time T2 and sending no data. The remaining CGOut1-CGOut4 signals are have a falling edge with an adjusted position to times T0, T1, T3, T4 respectively each representing a different two bit value. Thus, the preferred embodiment is able to transfer two bits per clock from the transmitter 102 to the receiver 106 in addition to the clock signal. Since the receiver 106 uses only the rising edge to detect and define clock cycles, the present invention uses this to achieve the data transfer without any performance disadvantages. For the receiver 106 embodiments described below where only one bit of data per clock is sent, the clock generator 200 would output falling edges at times T1 and T3.

The ability of the present invention to use the clock transmission line 104 to send data from the transmitter 102 to the receiver 104 is particularly advantageous because it present invention as applied to TMDS, the transmitter 102 does not need to wait for the next available data enable (DE)