# IN THE UNITED STATES DISTRICT COURT FOR THE DISTRICT OF DELAWARE

DYNAMIC DATA TECHNOLOGIES, LLC,

Plaintiff,

v.

NVIDIA CORPORATION,

Defendant.

Civil Action No. 18-cv-01726-CFC

JURY TRIAL DEMANDED

# FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT

Dynamic Data Technologies, LLC ("Dynamic Data") bring this action and make the following allegations of patent infringement relating to U.S. Patent Nos.: 8,189,105 (the "'105 patent"); 8,135,073 (the "'073 patent"); 8,073,054 (the "'054A patent"); 6,774,918 (the "'918 patent"); 8,184,689 (the "'689 patent"); 6,996,177 (the "'177 patent"); 7,010,039 (the "'039 patent"); 8,311,112 (the "'112 patent"); 7,894,529 (the "'529 patent"); 7,542,041 (the "'041 patent"); 7,571,450 (the "'450 patent"); 7,750,979 (the "'979 patent"); 6,421,090 (the ""090 patent"); and 6,782,054 (the "'054B patent") (collectively, the "patents-in-suit"). Defendant NVIDIA Corporation ("NVIDIA" or "Defendant") infringes each of the patents-in-suit in violation of the patent laws of the United States of America, 35 U.S.C. § 1 *et seq*.

#### Introduction

- 1. Dynamic Data's portfolio of over 1,200 patent assets encompasses core technologies in the field of image and video processing. The patent portfolio held by Dynamic Data is international in scope and includes several hundred European and Chinese patent grants.

- 2. In addition to ensuring that its intellectual property is appropriately licensed, Dynamic Data has expanded its portfolio of motion estimation and motion compensation patents.

On November 19, 2018, Dynamic Data acquired a further set of 85 patent assets from NXP B.V. relating to motion estimation and motion compensation. Dynamic Data is asserting one of these recently-acquired patents in this First Amended Complaint.<sup>1</sup>

## **DYNAMIC DATA'S LANDMARK INVENTIONS**

3. The groundbreaking inventions in image and video processing taught in the patents-in-suit were pioneered by Philips. Video and image processing were at the heart of Philips' business for over fifty years. In 1891, Philips, then known as Philips & Company, was founded in Eindhoven, Netherlands to manufacture carbon-filament lamps.<sup>2</sup> In the 1920s, Philips began to produce vacuum tubes and small radios, which would augur Philips' later entry into video and audio processing.

N.A. Halbertsma, *The Birth of a Lamp Factory In 1891*, PHILIPS TECHNICAL REVIEW, Vol. 23 at 230, 234 (1961).

4. In 1962, Philips introduced the first audio cassette tape.<sup>3</sup> A year later, Philips launched a small battery-powered audio tape recorder that used a cassette instead of a loose spool.<sup>4</sup>

<sup>&</sup>lt;sup>1</sup> See infra Count XIV (Asserting U.S. Patent No. 6,782,054).

<sup>&</sup>lt;sup>2</sup> Gerard O'Regan, A BRIEF HISTORY OF COMPUTING at 99 (2012).

<sup>&</sup>lt;sup>3</sup> Gerard O'Regan, PILLARS OF COMPUTING: A COMPENDIUM OF SELECT, PIVOTAL TECHNOLOGY FIRMS at 172 (2015) ("Philips invented the compact cassette for audio storage in 1962.")

<sup>&</sup>lt;sup>4</sup> Anthony Pollard, Gramophone: The First 75 Years at 231 (1998).

Philips C-cassette was later used as the first mass storage device for early personal computers in the 1970s and 1980s.

THE ROTARIAN MAGAZINE, Vol. 101 No. 6 at 70 (December 1962) (advertisement showing Philips Norelco device which used cassettes for recording audio for transcription); Fred Chandler, *European Mfrs. Bid For Market Share*, BILLBOARD MAGAZINE AT P-6 (April 8, 1967) (image of the Philips EL 3300 battery-operated tape recorder which was released in 1963); Jan Syrjala, *Car Stereo: How Does The Music Sound?*, N.Y. TIMES at 2-M (September 25, 1966) (showing Philips's Norelco Cassette "the Philips device has two tiny reels inside it, with the tape traveling from one to the other").

5. In 1971, Philips demonstrated the world's first videocassette records (VCR). A year later, Philips launched the world's first home video cassette recorder, the N1500. In 1982, Philips teamed with Sony to launch the Compact Disc; this format evolved into the DVD and later Blu-ray, which Philips launched with Sony in 1997 and 2006 respectively.

Hans Peek, Jan Bergmans, Jos Van Haaren, Frank Toolenaar, and Sorin Stan, ORIGINS AND SUCCESSORS OF THE COMPACT DISC: CONTRIBUTIONS OF PHILIPS TO OPTICAL STORAGE at 15 (2009) (showing image of Joop Sinjou of Philips introducing the compact disc in March 1979); Advertisements for Philip's Compact Disc Products (1982).

- 6. In the late 1990s and early 2000s, Philips pioneered the development of technologies for encoding and decoding of video and audio content. At the time most of the technologies claimed by the patents in Dynamic Data's portfolio were invented, Philips' subsidiary primarily responsible for Philips' work in this field, Philips Semiconductor was the world's sixth largest semiconductor company.<sup>5</sup> The video encoding technologies developed by Philips Semiconductor enable video streaming on set-top boxes, smartphones, popular gaming consoles, Internet-connected computers, and numerous other types of media streaming devices.

- 7. Philips Semiconductor dedicated significant research and development resources to advancing the technology of video compression and transmission by reducing file sizes and

4

<sup>&</sup>lt;sup>5</sup> Company News; Philips in \$1 Billion Deal for VLSI Technology, THE NEW YORK TIMES (May 4, 1999), available at: https://www.nytimes.com/1999/05/04/business/company-news-philips-in-1-billion-deal-for-vlsi-technology.html.

decreasing the processing resources required to transmit the data.<sup>6</sup> Philips Semiconductor was among the first companies aggressively driving innovation in the field of video processing:

The late 1980s and early 1990s saw the announcement of several complex, programmable VSPs. Important examples include chips from Matsushita, NTT, Philips [Semiconductors], and NEC. All of these processors were high-performance parallel processors architected from the ground up for real-time video signal processing. . . . The Philips VSP-1 and NEC processor were probably the most heavily used of these chips. <sup>7</sup>

8. Starting in the 1960s Philips pioneered the development of audio and video technologies that would establish itself as a leader in the field that would later develop into the audio and video encoding fields. Continuing Philips' pioneering history in these fields, the patents-in-suit disclose cutting-edge video compression and transmission technologies.

## **DYNAMIC DATA'S PATENT PORTFOLIO**

9. Dynamic Data's patent portfolio includes over 1,200 patent assets, with over 470 issued patents granted by patent offices around the world. Dynamic Data owns numerous patents issued by the United States Patent and Trademark Office, including each of the patents-in-suit, The State Intellectual Property Office of the People's Republic of China,<sup>8</sup> the European Patent Office,<sup>9</sup> the German Patent and Trademark Office,<sup>10</sup> the Japan Patent Office,<sup>11</sup> and many other national patent offices.

<sup>&</sup>lt;sup>6</sup> Hu, Yu Hen, Programmable Digital Signal Processors: Architecture, Programming, AND APPLICATIONS, at 190 (Dec. 6, 2001) ("Philips Semiconductors developed early dedicated video chips for specialized video processors.").

<sup>&</sup>lt;sup>7</sup> *Id.* at 191.

<sup>&</sup>lt;sup>8</sup> See, e.g., CN100504925C; CN100438609C; CN1679052B; CN1333373C; CN1329870C; CN1303818C.

<sup>&</sup>lt;sup>9</sup> See, e.g., European Patent Nos. EP1032921B1; EP1650978B1; EP1213700B1; EP1520409B1.

<sup>&</sup>lt;sup>10</sup> See, e.g., German Patent Nos. DE60120762; DE50110537; DE60126151; DE60348978; DE602004049357.

<sup>&</sup>lt;sup>11</sup> See, e.g., Japanese Patent Nos. JP4583924B2; JP5059855B2; JP5153336B2; JP4637585B2.

- 10. Philips Semiconductor's pioneering work in the area of video processing and encoding has resulted in various inventions that are fundamental to today's video processing technologies. Dynamic Data is the owner by assignment of over 1,200 of these patent assets, which include over 470 patents issued by patent offices around the world.

- 11. Highlighting the importance of the patents-in-suit is the fact that the patents-in-suit have been cited by over 470 U.S. and international patents and patent applications by a wide variety of the largest companies operating in the field. For example, the patents-in-suit have been cited by companies such as:

- Samsung Electronics Co., Ltd. 12

- Oualcomm Inc. 13

- Google LLC<sup>14</sup>

- Intel Corporation<sup>15</sup>

- Broadcom Corporation<sup>16</sup>

- Microsoft Corporation<sup>17</sup>

- Sony Corporation<sup>18</sup>

- Fujitsu Ltd. 19

- Panasonic Corporation<sup>20</sup>

- Matsushita Electric Industrial Company Limited<sup>21</sup>

<sup>&</sup>lt;sup>12</sup> See, e.g., U.S. Patent Nos. 6,930,729; 7,911,537; 7,532,764; 8,605,790; and 8,095,887.

<sup>&</sup>lt;sup>13</sup> See, e.g., U.S. Patent Nos. 7,840,085; 8,649,437; 8,750,387; 8,918,533; 9,185,439; 9,209,934; 9,281,847; 9,319,448; 9,419,749; 9,843,844; 9,917,874; and 9,877,033.

<sup>&</sup>lt;sup>14</sup> See, e.g., U.S. Patent No. 8,787,454 and U.S. Patent Appl. No. 10/003,793.

<sup>&</sup>lt;sup>15</sup> See, e.g., U.S. Patent Nos. 7,554,559; 7,362,377; and 8,462,164.

<sup>&</sup>lt;sup>16</sup> See, e.g., U.S. Patent Nos. 8,325,273 and 9,377,987.

<sup>&</sup>lt;sup>17</sup> See, e.g., U.S. Patent Nos. 7,453,939; 7,670,227; 7,408,986; 7,421,129; 7,558,320; and 7,929,599.

<sup>&</sup>lt;sup>18</sup> See, e.g., U.S. Patent Nos. 7,218,354 and 8,174,615.

<sup>&</sup>lt;sup>19</sup> See, e.g., U.S. Patent Nos. 7,092,032 and 8,290,308.

<sup>&</sup>lt;sup>20</sup> See, e.g., U.S. Patent Nos. 8,164,687 and 8,432,495.

<sup>&</sup>lt;sup>21</sup> See, e.g., U.S. Patent Nos. 7,362,378 and 7,423,961.

# **THE PARTIES**

## **DYNAMIC DATA TECHNOLOGIES, LLC**

- 12. Dynamic Data Technologies, LLC ("Dynamic Data" or "Plaintiff") is a limited liability company organized under the laws of Delaware.

- 13. In an effort to obtain compensation for Philips' pioneering work in the fields of video data encoding, decoding, and transmission, Dynamic Data acquired the patents-in-suit along with the several hundred additional issued United States and international Patents.

- 14. Dynamic Data pursues the reasonable royalties owed for NVIDIA's use of the inventions claimed in Dynamic Data's patent portfolio, which primarily arise from Philips' groundbreaking technology, both here in the United States and throughout the world.

#### **NVIDIA CORPORATION**

15. On information and belief, NVIDIA Corporation ("NVIDIA"), is a Delaware corporation with its principal place of business at 2701 San Tomas Expressway, Santa Clara, CA 95050. NVIDIA may be served through its registered agent – Corporation Service Company, 251 Little Falls Drive, Wilmington, DE 19808.

#### **JURISDICTION AND VENUE**

- 16. This action arises under the patent laws of the United States, Title 35 of the United States Code. Accordingly, this Court has exclusive subject matter jurisdiction over this action under 28 U.S.C. §§ 1331 and 1338(a).

- 17. Upon information and belief, this Court has personal jurisdiction over NVIDIA in this action because NVIDIA has committed acts within the State of Delaware giving rise to this action and has established minimum contacts with this forum such that the exercise of jurisdiction over NVIDIA would not offend traditional notions of fair play and substantial justice. Defendant

NVIDIA, directly and/or through subsidiaries or intermediaries (including distributors, retailers, and others), has committed and continues to commit acts of infringement in this District by, among other things, offering to sell and selling products and/or services that infringe the patents-in-suit. Moreover, NVIDIA actively directs its activities to customers located in the State of Delaware.

18. Venue is proper in this district under 28 U.S.C. §§ 1391(b)-(d) and 1400(b). Defendant NVIDIA resides in the State of Delaware, upon information and belief, has transacted business in the State of Delaware, and has committed acts of direct and indirect infringement in the State of Delaware.

#### THE ASSERTED PATENTS

## **U.S. PATENT No. 8,189,105**

- 19. U.S. Patent No. 8,189,105 entitled, *Systems and Methods of Motion and Edge Adaptive Processing Including Motion Compensation Features*, was filed on October 17, 2007. The '105 Patent is subject to a 35 U.S.C. § 154(b) term extension of 1258 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '105 Patent. A true and correct copy of the '105 Patent is attached hereto as Exhibit 1.

- 20. The '105 patent discloses novel systems and methods for processing pixel information based on received motion and edge data.

- 21. The '105 patent further discloses the use of a blending component (implemented by hardware, software, firmware, combinations thereof, etc.) that implements interpolating intensity of the pixel to equal to the first intensity estimate if motion reliability data is below a threshold.

- 22. The '105 patent in one embodiment teaches using segmentation to average four contiguous pixels into one averaged pixel segment during motion detection.

- 23. The '105 Patent and its underlying patent applications and foreign counterparts have been cited by 46 patents and patent applications as relevant prior art. Specifically, patents issued to the following companies have cited the '105 Patent and its underlying patent application as relevant prior art:

- Flextronics Ap, LLC

- Qingdao Hisense Electronics Co., Ltd.

- Hon Hai Precision Industry Co., Ltd.

- Intel Corporation

- Sony Corporation

- Fujitsu Corporation

- Himax Media Solutions, Inc.

- Ati Technologies Ulc

- Sharp Kabushiki Kaisha

- Xerox Corporation

#### U.S. PATENT No. 8,135,073

- 24. U.S. Patent No. 8,135,073 (the "'073 patent") entitled, *Enhancing Video Images Depending On Prior Image Enhancements*, was filed on December 12, 2003, and claims priority to December 19, 2002. The '073 patent is subject to a 35 U.S.C. § 154(b) term extension of 1,799 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '073 patent. A true and correct copy of the '073 patent is attached hereto as Exhibit 2.

- 25. The '073 patent discloses novel methods and systems for enhancing subsequent images of a video stream in which frames are encoded based on previous frames using prediction and motion estimation.

- 26. The inventions disclosed in the '073 patent reduce the processing capacity required for providing video enhancements to video processing through re-mapping of previous frames for subsequent frames.

- 27. Accordingly, the technologies disclosed in the '073 patent enable the provision of enhanced video pictures with minimal additional hardware costs for the components required to successfully process the video data.

- 28. The '073 patent discloses a video decoder comprising an input for receiving a video stream containing encoded frame-based video information including an encoded first frame and an encoded second frame.

- 29. The '073 patent discloses a video decoder comprising an input for receiving video information wherein the encoding of the second frame depends on the encoding of the first frame, the encoding of the second frame includes motion vectors indicating differences in positions between regions of the second frame and corresponding regions of the first frame, the motion vectors define correspondence between regions of the second frame and corresponding regions of the first frame.

- 30. The '073 patent discloses a video decoder comprising a decoding unit for decoding the frames, wherein the decoding unit recovers the motion vectors for the second frame.

- 31. The '073 patent discloses a video decoder comprising a processing component configured to determine a re-mapping strategy for video enhancement of the decoded first frame using a region-based analysis, re-map the first frame using the re-mapping strategy, and re-map one or more regions of the second frame depending on the re-mapping strategy for corresponding regions of the first frame.

- 32. The '073 patent and its underlying patent application have been cited by 36 patents and patent applications as relevant prior art. Specifically, patents issued to the following companies have cited the '073 patent and its underlying patent application as relevant prior art:

- Canon Inc.

- Microsoft Corporation

- International Business Machines Corporation

- Qualcomm Inc.

- Digital Fountain Incorporated

- Samsung Electronics Co., Ltd.

- SK Planet Co. Ltd.

## **U.S. PATENT No. 8,073,054**

- 33. U.S. Patent No. 8,073,054 (the "'054A patent") entitled, *Unit For And Method Of Estimating A Current Motion Vector*, was filed on December 12, 2002, and claims priority to January 17, 2002. The '054A patent is subject to a 35 U.S.C. § 154(b) term extension of 1,162 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '054A patent. A true and correct copy of the '054A patent is attached hereto as Exhibit 3.

- 34. The '054A patent discloses novel methods and apparatuses for estimating a current motion vector for a group of pixels of an image.

- 35. The inventions disclosed in the '054A patent enable motion estimation with a relatively fast convergence in finding the appropriate motion vectors of the motion vector fields by adding a further candidate motion vector to the set of candidate motion vectors.

- 36. The '054A patent discloses a motion estimation unit comprising a generating unit for generating a set of candidate motion vectors for the group of pixels, with the candidate motion vectors being extracted from a set of previously estimated motion vectors.

- 37. The '054A patent discloses a motion estimation unit comprising a match error unit for calculating match errors of respective candidate motion vectors.

- 38. The '054A patent discloses a motion estimation unit comprising a selector for selecting the current motion vector from the candidate motion vectors by means of comparing the match errors of the respective candidate motion vectors, characterized in that the motion estimation unit is arranged to add a further candidate motion vector to the set of candidate motion vectors by

calculating the further candidate motion vector on basis of a first motion vector and a second motion vector, both belonging to the set of previously estimated motion vectors.

- 39. The '054A patent discloses a motion estimation unit that calculates the further candidate motion vector on basis of the first motion vector and the second motion vector, with the first motion vector belonging to a first forward motion vector field and the second motion vector belonging to a second forward motion vector field, with the first forward motion vector field and the second forward motion vector field being different.

- 40. The '054A patent discloses a motion estimation unit that arranges to calculate the further candidate motion vector by means of calculating a difference between the second motion vector and the first motion vector.

- 41. The '054A patent and its underlying patent application have been cited by 14 patents and patent applications as relevant prior art. Specifically, patents issued to the following companies have cited the '054A patent and its underlying patent application as relevant prior art:

- Canon Inc.

- Huawei Technologies, Ltd.

- Imagination Technologies Ltd.

- MediaTek Inc.

- Panasonic Corp.

- Samsung Electronics Co., Ltd.

- Siemens Healthcare GmbH

- Tencent Technology (Shenzhen) Co., Ltd.

#### U.S. PATENT No. 6,774,918

42. U.S. Patent No. 6,774,918 ("the '918 patent") entitled, *Video Overlay Processor* with Reduced Memory And Bus Performance Requirements, was filed on June 28, 2000. The '918 patent is subject to a 35 U.S.C. § 154(b) term extension of 591 days. Dynamic Data is the owner

by assignment of all right, title, and interest in the '918 patent. A true and correct copy of the '918 patent is attached hereto as Exhibit 4.

- 43. The '918 patent claims specific methods and systems for providing an overlay such as a cursor in an on-screen display in a consumer electronic device. On-screen display (OSD) data for generating an image on a display device are downloaded to an OSD unit on an integrated circuit.

- 44. The '918 patent discloses downloading on-screen display (OSD) data for generating an image on a display device.

- 45. The '918 patent further discloses downloading the on-screen display (OSD) data in segments separated by gaps.

- 46. The '918 patent further discloses, during a gap in downloading the on-screen display data, downloading an amount of overlay data for generating an overlay on the image generated on a display device.

- 47. Further, the '918 patent discloses that the overlay data downloaded during a gap comprises a portion of the overlay data.

- 48. The inventions disclosed in the '918 patent improve the operation and efficiency of computer components because only a portion of the overlay data is downloaded during each burst gap, thus reducing the amount of memory needed to store the overlay data. The inventions disclosed in the '918 patent further eliminate the requirement that on-chip memory be large enough to hold the data needed for an entire overlay. Instead, only one line or a part of one line of the overlay needs to be stored on-chip.

- 49. The '918 patent claims a technical solution to a problem unique to video processing.

50. The '918 patent has been cited by several United States patents and patent applications as relevant prior art. Specifically, patents issued to Realtek Semiconductor Corp., Samsung Electronics Co., Ltd., and Thomson Licensing SA have all cited the '918 patent as relevant prior art.

#### **U.S. PATENT No. 8,184,689**

- 51. U.S. Patent No. 8,184,689 (the "'689 patent") entitled, *Method Video Encoding And Decoding Preserving Cache Localities*, was filed on August 7, 2006, and claims priority to August 17, 2005. The '689 patent is subject to a 35 U.S.C. § 154(b) term extension of 948 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '689 patent. A true and correct copy of the '689 patent is attached hereto as Exhibit 5.

- 52. The '689 patent discloses novel methods and apparatuses for encoding and decoding video data.

- 53. The inventions disclosed in the '689 patent processing time and power consumption associated with encoding and decoding video stream data is reduced by reducing off-chip memory accesses through using simultaneous encoded/decoded images as a reference image for encoding/decoding at least one of the other simultaneously encoded/decoded images.

- 54. The '689 patent discloses a method for encoding and decoding a video stream, including a plurality of images in a video processing apparatus having a processing unit coupled to a first memory, further comprising a second memory.

- 55. The '689 patent discloses a method for encoding and decoding a video stream comprising providing a subset of image data stored in the second memory in the first memory.

- 56. The '689 patent discloses a method for encoding and decoding a video stream comprising simultaneous encoding/decoding of more than one image of the video stream, by

accessing said subset, wherein the simultaneously encoding/decoding is performed by access sharing to at least one image.

57. The '689 patent and its underlying patent application have been cited by several patents and patent applications as relevant prior art. Specifically, patents issued to Fujitsu Ltd., Qualcomm Inc., Sony Corporation, Sun Patent Trust, and VIXS Systems Incorporated have all cited the '689 patent and its underlying patent application as relevant prior art.

#### U.S. PATENT No. 6,996,177

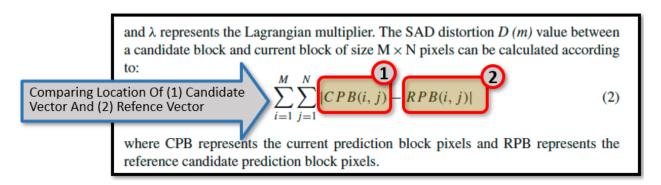

- 1. U.S. Patent No. 6,996,177 (the "177 patent") entitled, *Motion Estimation*, was filed on July 24, 2000, and claims priority to August 22, 1999. The '177 patent is subject to a 35 U.S.C. § 154(b) term extension of 1,103 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '177 patent. A true and correct copy of the '177 patent is attached hereto as Exhibit 6.

- 2. The '177 patent claims specific methods and devices for motion estimation and motion-compensated picture signal processing.

- 3. The '177 patent discloses a motion vector estimation method and device that carries out a block-based motion vector estimation process that involves comparing a plurality of candidate vectors to determine block-based motion vectors.

- 4. The '177 patent discloses a motion vector estimation method and device that determines at least a most frequently occurring block-based motion vector.

- 5. The '177 patent discloses a motion vector estimation method and device that carries out a global motion vector estimation process using at least the most frequently occurring block-based motion vector to obtain a global motion vector.

- 6. The '177 patent discloses a motion vector estimation method and device that applies the global motion vector as a candidate vector to the block-based motion vector estimation process.

- 7. The inventions disclosed in the '177 patent improve the operation of the computer components necessary to the performance of picture signal processing by reducing the load on the central processing unit.

- 8. The '177 patent has been cited by 16 United States and International patents and patent applications as relevant prior art. Specifically, patents issued to the following companies have cited the '177 patent as relevant prior art:

- Qualcomm Incorporated

- LG Electronics

- Microsoft Corporation

- Samsung Electronics Co., Ltd.

- VIXS Systems Incorporated

- General Instrument Corporation

### **U.S. PATENT No. 7,010,039**

- 9. U.S. Patent No. 7,010,039 (the "039 patent") entitled, *Motion Estimator for Reduced Halos in MC Up-Conversion*, was filed on May 15, 2001, and claims priority to May 18, 2000. The '039 patent is subject to a 35 U.S.C. § 154(b) term extension of 768 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '039 patent. A true and correct copy of the '039 patent is attached hereto as Exhibit 7.

- 10. The '039 patent claims specific methods and apparatuses detecting motion at a temporal intermediate position between previous and next images. The inventions disclosed in the '039 patent solve a problem wherein an estimator estimating motion between two successive pictures from a video sequence cannot perform well in areas where covering or uncovering occurs.

- 11. The '039 patent solves this problem by carrying out the optimization at the temporal position of the next image in covering areas and at the temporal position of the previous image in uncovering areas.

- 12. The '039 patent discloses a method and apparatus for detecting motion at a temporal intermediate position between previous and next images.

- 13. The '039 patent discloses the use of a criterion function for selecting and optimizing candidate vectors.

- 14. The '039 patent further discloses a criterion function that depends on data from both previous and next images and in which the optimizing is carried out at the temporal intermediate position in non-covering and non-uncovering areas, characterized in that the optimizing is carried out at the temporal position of the next image in covering areas and at the temporal position of the previous image in uncovering areas.

- 15. The '039 patent and its related patents have been cited by 30 United States and International patents and patent applications as relevant prior art. Specifically, patents issued to the following companies have cited the '039 patent family as relevant prior art:

- Qualcomm Incorporated

- Panasonic Corporation

- Samsung Electronics Co., Ltd.

- Matsushita Electric Industrial Co., Ltd.

- Sharp Kabushiki Kaisha

- Integrated Device Technology, Inc.

- Zoran Corporation

## **U.S. PATENT No. 8,311,112**

58. U.S. Patent No. 8,311,112 (the "'112 patent") entitled, *System And Method For Video Compression Using Predictive Coding*, was filed on December 31, 2008. The '112 patent is subject to a 35 U.S.C. § 154(b) term extension of 847 days. Dynamic Data is the owner by

assignment of all right, title, and interest in the '112 patent. A true and correct copy of the '112 patent is attached hereto as Exhibit 8.

- 59. The '112 patent discloses novel methods and systems for video compression.

- 60. The '112 patent discloses novel technologies for video compression that perform predictive coding on a macroblock of a video frame such that a set of pixels of the macroblock is coded using some of the pixels from the same video frame as reference pixels and the rest of the macroblock is coded using reference pixels from at least one other video frame.

- 61. The '112 patent discloses a system for video compression comprising an intraframe coding unit configured to perform predictive coding on a set of pixels of a macroblock of pixels using a first group of reference pixels, the macroblock of pixels and the first group of reference pixels being from a video frame.

- 62. The '112 patent discloses a system for video compression comprising an interframe coding unit configured to perform predictive coding on the rest of the macroblock of pixels using a second group of reference pixels, the second group of reference pixels being from at least one other video frame.

- 63. The '112 patent and its underlying patent application have been cited by 10 patents and patent applications as relevant prior art. Specifically, patents issued to the following companies have cited the '112 patent and its underlying patent application as relevant prior art:

- British Broadcasting Corporation

- Google LLC

- Megachips Corp.

- Olympus Corp.

- Samsung Electronics Co., Ltd.

- Sony Corporation

- Toshiba Corporation

#### **U.S. PATENT No. 7,894,529**

- 64. U.S. Patent No. 7,894,529 (the "'529 patent") entitled, *Method And Device For Determining Motion Vectors*, was filed on June 1, 2006, and claims priority to June 3, 2005. The '529 patent is subject to a 35 U.S.C. § 154(b) term extension of 1,301 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '529 patent. A true and correct copy of the '529 patent is attached hereto as Exhibit 9.

- 65. The '529 patent discloses novel methods and apparatuses for determining motion vectors that are each assigned to individual image regions.

- 66. The inventions disclosed in the '529 patent enable an increase in the resolution of video and image signals during the motion estimation process.

- 67. The '529 patent discloses a method for determining motion vectors which are assigned to individual image regions of an image.

- 68. The '529 patent discloses a method wherein an image is subdivided into a number of image blocks, and a motion estimation technique is implemented to assign at least one motion vector to each of the image blocks where a modified motion vector is generated for at least a first image block.

- 69. The '529 patent discloses a method that determines at least a second image block through which the motion vector assigned to the first image block at least partially passes.

- 70. The '529 patent discloses a method that generates the modified motion vector as a function of a motion vector assigned to at least the second image block.

- 71. The '529 patent discloses a method that assigns the modified motion vector as the motion vector to the first image block.

- 72. The '529 patent and its underlying patent application have been cited by multiple patents and patent applications as relevant prior art. Specifically, patents issued to Fujifilm Corp.,

and Samsung Electronics Co., Ltd. have cited the '529 patent and its underlying patent application as relevant prior art.

## **U.S. PATENT NO. 7,542,041**

- 73. U.S. Patent No. 7,542,041 (the "041 patent") entitled, *Runtime Configurable Virtual Video Pipeline*, was filed on April 2, 2004, and claims priority to April 3, 2003. The '041 patent is subject to a 35 U.S.C. § 154(b) term extension of 288 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '041 patent. A true and correct copy of the '041 patent is attached hereto as Exhibit 10.

- 74. The '041 patent discloses novel systems for dynamically configuring a multi-pipe pipeline system.

- 75. The inventions disclosed in the '041 patent enable a multiple-pipeline system that is dynamically configurable to effect various combinations of functions for each pipeline.

- 76. The inventions disclosed in the '041 patent teach a multiple pipeline system that includes a pool of auxiliary function blocks that are provided as required to select pipelines.

- 77. In one embodiment of the '041 patent, each pipeline of the multiple-pipeline system is configured to include a homogenous set of core functions. A pool of auxiliary functions is provided for selective insertion of auxiliary functions between core functions of select pipelines.

- 78. In one embodiment of the '041 patent, each auxiliary function includes a multiplexer that allows it to be selectively coupled within each pipeline.

- 79. The '041 patent discloses, in one embodiment, a processing system that includes a plurality of pipelines, with each pipeline of the plurality including a plurality of core pipeline elements that are configured to sequentially process data as it traverses the pipeline.

- 80. The '041 patent discloses, in one embodiment, a processing system that includes a plurality of auxiliary elements, each auxiliary element of the plurality of auxiliary elements being configured to be selectively coupled to multiple pipelines of the plurality of pipelines.

- 81. The '041 patent discloses, in one embodiment, a processing system wherein the auxiliary elements are responsive to external coupling-select signals.

- 82. The '041 patent discloses, in one embodiment, a processing system wherein a plurality of auxiliary elements are within a selected pipeline of the multiple pipelines, between a pair of core pipeline elements of the plurality of core pipeline elements to process the data as it traverses between the pair of core elements.

- 83. The '041 patent has been cited by several United States patents and patent applications as relevant prior art. Specifically, patents and patent applications issued to Microsoft Corporation, Xilinx Inc., Canon Inc., Intel Corporation, and Nokia Oyj have cited the '041 patent and its underlying patent application as relevant prior art.

# **U.S. PATENT NO. 7,571,450**

- 84. U.S. Patent No. 7,571,450 (the "'450 patent") entitled, *System For And Method Of Displaying Information*, was filed on February 12, 2003, and claims priority to March 11, 2002. The '450 patent is subject to a 35 U.S.C. § 154(b) term extension of 846 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '450 patent. A true and correct copy of the '450 patent is attached hereto as Exhibit 11.

- 85. The '450 patent discloses novel methods and systems for displaying information. The inventions disclosed in the '450 patent enable methods and systems wherein a user does not need to make a new selection after being switched from one service to a second service.

- 86. The inventions disclosed in the '450 patent permit a user of an information display system to have selections made on a first service also presented when the user switches to a second service without requiring the user to browse through the menus to define the type of information to be displayed a second time.

- 87. In one embodiment of the '450 patent, the user selection being made on the basis of the provided options while the first service was selected is used to select the appropriate data elements of the stream of the second service.

- 88. The inventions disclosed in the '450 patent enable various content sources to share similar information models.

- 89. The '450 patent, in one embodiment, discloses a method of displaying information on a display device wherein receiving a transport stream comprises services, with the services having elementary streams of video and of data elements.

- 90. The '450 patent, in one embodiment, discloses a method of displaying information on a display device wherein user actions of making a user selection of a type of information to be displayed on the device are received.

- 91. The '450 patent, in one embodiment, discloses a method of displaying information on a display device wherein filtering to select a data element of a first one of the services on the basis of the user selection is performed.

- 92. The '450 patent, in one embodiment, discloses a method of displaying information on a display device wherein rendering to calculate an output image to be displayed on the display device, on the basis of the first data element selected by the filer is performed.

- 93. The '450 patent, in one embodiment, discloses a method of displaying information on a display device wherein switching from the first one of the services to a second one of the

services, characterized in comprising a second step of filtering to select a second data-element of the second one of the services, on basis of the user selection is performed.

- 94. The '450 patent, in one embodiment, discloses a method of displaying information on a display device wherein being switched from the first one of the services to the second one of the services, with the data-element and the second data-element being mutually semantically related and a second step of rendering to calculate the output image to be displayed on the display device, on basis of the second data-element selected by the filter is performed.

- 95. The '450 patent and its underlying patent application have been cited by several patents and patent applications as relevant prior art. Specifically, patents issued to AT&T Intellectual Property I LP, Nokia Oyj, Samsung Electronics Co., Ltd., and ZTE Corporation have all cited the '450 patent and its underlying patent application as relevant prior art.

#### U.S. PATENT No. 7,750,979

- 96. U.S. Patent No. 7,750,979 (the "'979 patent") entitled, *Pixel-Data Line Buffer Approach Having Variable Sampling Patterns*, was filed on October 26, 2001. The '979 patent is subject to a 35 U.S.C. § 154(b) term extension of 2,749 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '979 patent. A true and correct copy of the '979 patent is attached hereto as Exhibit 12.

- 97. The '979 patent discloses novel methods and systems for motion compensation in video signal processing.

- 98. The '979 patent discloses methods and systems that use line buffers that are decoupled and that can deliver a fixed number of pixels, as may be required by a video processing stage, using a sampling pattern that is defined as one among several selectable sampling windows.

- 99. The '979 patent discloses a video processing circuit having an input stream of pixels corresponding to an array of video pixels.

- 100. The '979 patent further discloses having a variable window size for sampling subsets of the array as a two-dimensional window that spans the pixels in the array.

- 101. The '979 patent further discloses having a video processing stage that inputs pixels using a fixed number of pixels.

- 102. The '979 patent further discloses a method for delivering the input stream of pixels to the video processing stage.

- 103. The '979 patent further discloses a method comprising establishing a window size and a sampling-window size, such that the window size is a multiple of the sampling-window size and the sampling-window size defines the fixed number of pixels.

- 104. The '979 patent further discloses a method comprising storing pixels from the input stream into a first set of line butters, the pixels stored in the first set of line butters including pixels for the established window size.

- 105. The '979 patent further discloses a method comprising prefetching the stored pixels from the first set of line butters into a second set of line buffers, the second set of line buffers being sufficiently long to store at least the pixels corresponding to the established sampling-window size.

- 106. The '979 patent further discloses a method comprising fetching the fixed number of pixels from the second set of line buffers for the video processing stage.

#### **U.S. PATENT No. 6,421,090**

107. U.S. Patent No. 6,421,090 (the "'090 patent") entitled, *Motion And Edge Adaptive Deinterlacing*, was filed on August 27, 1999. Dynamic Data is the owner by assignment of all

right, title, and interest in the '090 patent. A true and correct copy of the '090 patent is attached hereto as Exhibit 13.

- 108. The '090 patent discloses novel methods and apparatuses for interpolating a pixel during the deinterlacing of video signals. The various embodiments of the '090 patent utilize multiple, interlaced scan lines of video signal, with each scan line including a series of pixels with intensity values.

- 109. The '090 patent discloses generating a motion value representative of the motion between successive frames about the pixel by segmenting an image into multi-pixel segments and comparing the differences with respect to each segment in successive frames.

- 110. The '090 patent discloses detecting an edge direction about the pixel and performing an edge adaptive interpolation at the pixel using a generated motion value.

- 111. The '090 patent further discloses generating a motion value by comparing segments of pixels about the pixel from at least three successive frames.

- 112. The '090 patent and its underlying patent application have been cited by 86 patents and patent applications as relevant prior art. Specifically, patents issued to the following companies have cited the '090 patent and its underlying patent application as relevant prior art:

- Samsung Electronics Co., Ltd.

- LG Electronics Inc.

- Qualcomm Inc.

- Microsoft Corporation

- Panasonic Corporation

- STMicroelectronics SRL

- Matsushita Electric Industrial Company Ltd.

- Sanyo Electric Company Ltd.

- Fujitsu Limited

- AVerMedia Technologies Inc.

- Sony Corporation

- Himax Technologies Inc.

- Mitsubishi Electric Corporation

- Hewlett-Packard Development Company L.P.

- MediaTek Inc.

- Realtek Semiconductor Corp.

- Imagination Technologies Limited

- Integrated Device Technology Incorporated

- Intel Corporation

- MStar Semiconductor Incorporated

## **U.S. PATENT No. 6,782,054**

- 113. U.S. Patent No. 6,782,054 entitled, *Method And Apparatus For Motion Vector Estimation*, was filed on April 20, 2001. The '054B Patent is subject to a 35 U.S.C. § 154(b) term extension of 485 days. Dynamic Data is the owner by assignment of all right, title, and interest in the '054B Patent. A true and correct copy of the '054B Patent is attached hereto as Exhibit 14.

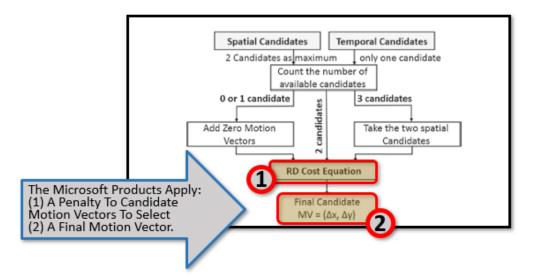

- 114. The '054B Patent discloses novel methods and systems for motion estimation in a sequence of moving video pictures.

- 115. The inventions disclosed in the '054B Patent increase the speed of convergence of motion vectors to improve the convergence process.

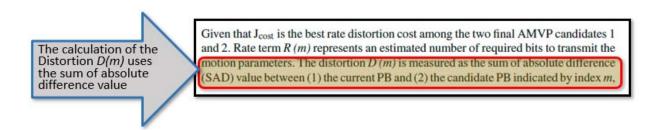

- 116. The '054B Patent discloses a method to enhance motion estimation that includes selecting a displacement vector as a best motion vector for a region in a field from a plurality of at least two candidate motion vectors by applying an error function to each of said plural candidate motion vectors, wherein the candidate motion vector with the least error is selected as the displacement vector for the region in the field.

- 117. The '054B Patent discloses a method to enhance motion estimation that includes an error function comprising a first penalty term that depends on a type of the candidate motion vector and a second penalty term that depends on the position and size of the candidate motion vector.

- 118. The '054B Patent and its underlying patent application have been cited by 54 patents and patent applications as relevant prior art. Specifically, patents issued to the following companies have cited the '054B Patent and its underlying patent application as relevant prior art:

- Samsung Electronics Co., Ltd.

- Sony Corporation

- MediaTek Inc.

- Qualcomm Incorporated

- Micronas GmbH

- Google Inc.

- Thomson Licensing

- Brightscale, Inc.

- Genesis Microchip Inc.

- STMicroelectronics SA

- Toshiba Corp.

## COUNT I INFRINGEMENT OF U.S. PATENT NO. 8,189,105

- 119. Dynamic Data references and incorporates by reference the preceding paragraphs of this Complaint as if fully set forth herein.

- 120. NVIDIA designs, makes, uses, sells, and/or offers for sale in the United States products and/or services for motion compensation in video signal processing.

- 121. NVIDIA designs, makes, uses, sells, and/or offers for sale in the United States products and/or services for processing pixel information based on received motion and edge data.

- 122. NVIDIA designs, makes, sells, offers to sell, imports, and/or uses NVIDIA products, including the following: GeForce GT 1030, GeForce GTX 1050 / 1050 Ti, GeForce GTX 1060, GeForce GTX 1070 1080, GeForce GTX 1080 Ti, GeForce GTX Titan X Titan Xp, Titan V, Quadro P400 P1000, Quadro P2000, Quadro P4000 / P5000, Quadro P6000, Quadro GP100, Quadro GV100, Tesla M4, Tesla P4 / P6, Tesla P40, Tesla P100, Tesla V100, GeForce GTX 750 GeForce GTX 950 960, GeForce GT 1030, Quadro M2000, Quadro P400, Quadro P600, Quadro P620, and Quadro P1000 (collectively, the "NVIDIA '105 Product(s)").

- 123. On information and belief, one or more NVIDIA subsidiaries and/or affiliates use the NVIDIA '105 Products in regular business operations.

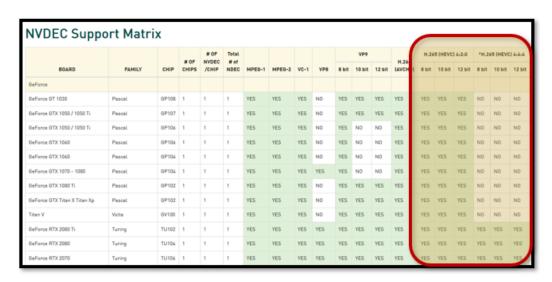

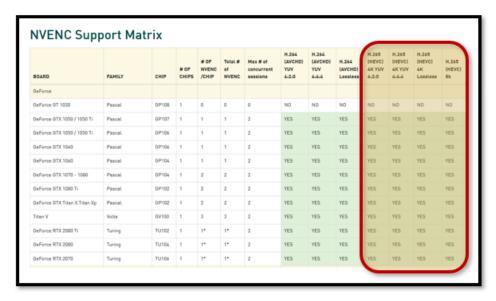

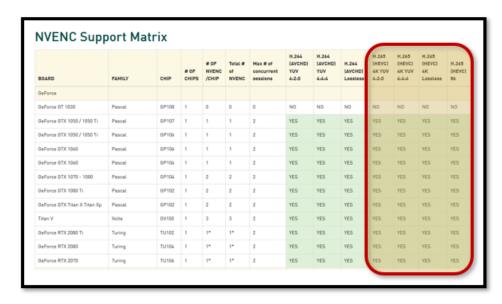

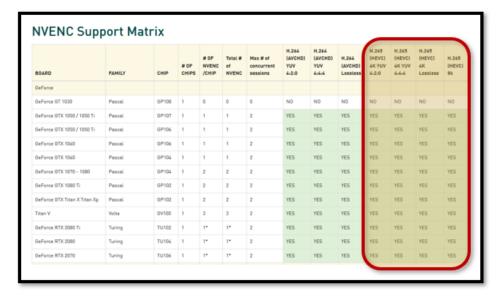

- 124. On information and belief, the NVIDIA '105 Products perform video processing complaint with the HEVC standard. The following excerpt from the NVIDIA Video Encode and Decode GPU Support Matrix identifies that the NVIDIA '105 Products comply with the HEVC standard for decoding data.

*NVIDIA Video Encode and Decode GPU Support Matrix*, NVIDIA DEVELOPER WEBSITE, available at: https://developer.nvidia.com/video-encode-decode-gpu-support-matrix (annotation showing products that enable HEVC decoding in compliance with the HEVC standard).

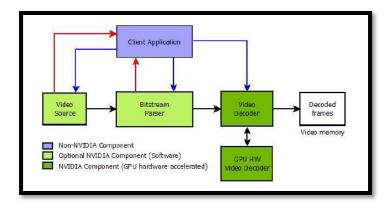

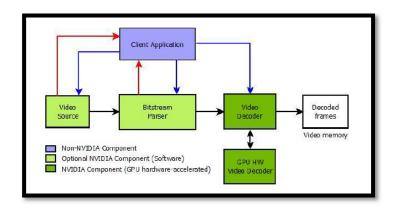

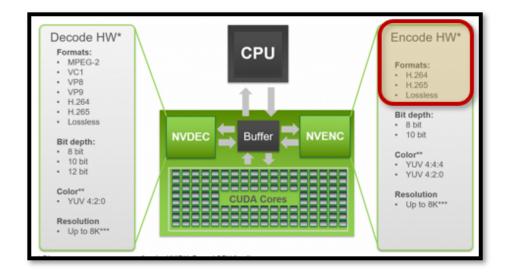

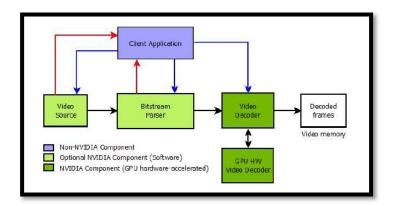

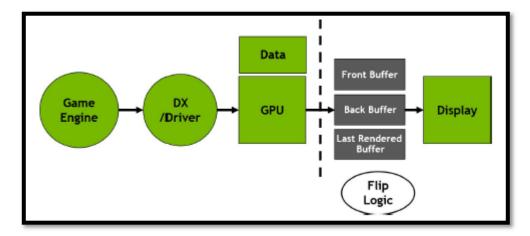

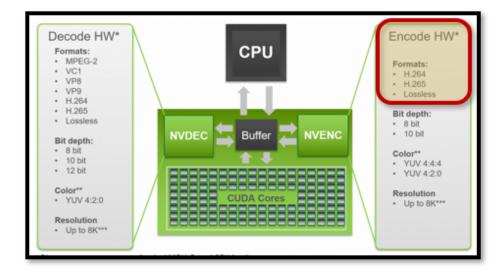

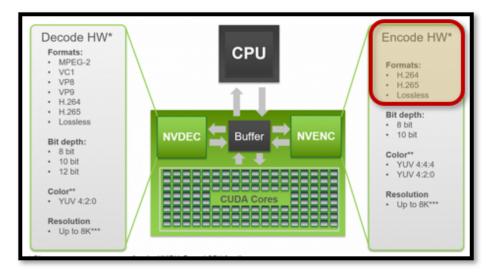

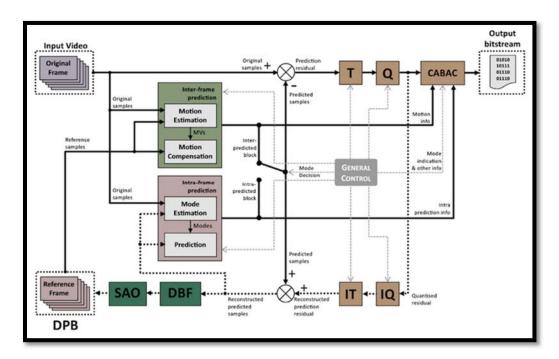

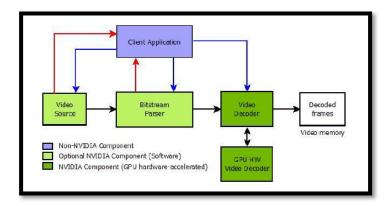

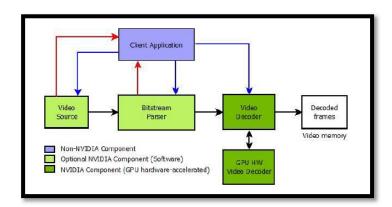

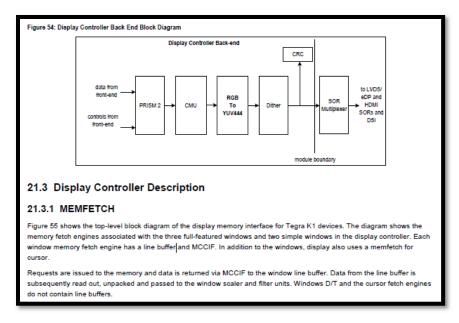

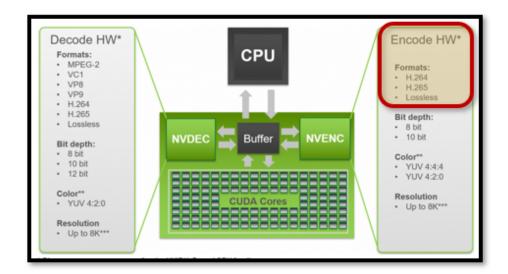

125. The NVIDIA '105 Products comply with the HEVC standard in decoding video data. The NVIDIA document shows the NVDEC interface for decoding video data.

NVIDIA Video Decoder (NVDEC) Interface, NVIDIA PROGRAMMING GUIDE at 4 (June 2016) (annotations added) (showing the functionality for decoding video data for on-screen display).

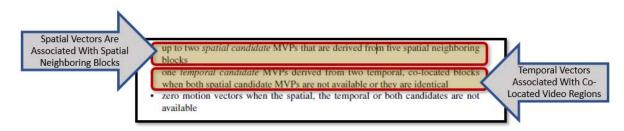

- 126. On information and belief, by complying with the HEVC standard, the NVIDIA devices such as the NVIDIA '105 Products necessarily infringe the '105 patent. The mandatory sections of the HEVC standard require the elements required by certain claims of the '105 patent, including but not limited to claim 1 of the '105 patent. *High Efficiency Video Coding*, SERIES H: AUDIOVISUAL AND Multimedia SYSTEMS: INFRASTRUCTURE OF AUDIOVISUAL SERVICES CODING OF MOVING VIDEO REC. ITU-T H.265 (February 2018) (The following sections of the HEVC Standard are relevant to NVIDIA's infringement of the '105 patent: "8.3.2 Decoding process for reference picture set;" "8.5.4 Decoding process for the residual signal of coding units coded in inter prediction mode;" "8.6 Scaling, transformation and array construction process prior to deblocking filter process;" "8.5.2 Inter prediction process;" "8.5.3 Decoding process for prediction units in inter prediction mode;" and "8.7.2 Deblocking filter process;" "8.7.3 Sample adaptive offset process.").

- 127. On information and belief, the NVIDIA '105 Products comply with the HEVC standard, which requires processing edge data from edge-adaptive interpolation processing.

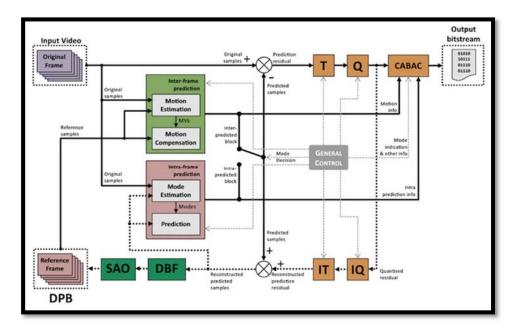

- 128. The NVIDIA '105 Products use two types of prediction methods for processing pixel information when encoding and decoding video data in HEVC format: inter prediction and intra prediction. Inter prediction utilizes motion vectors for block-based inter prediction to exploit

temporal statistical dependencies between different pictures. Intra prediction uses various spatial prediction modes to exploit spatial statistical dependencies in the source signal for a single picture. The HEVC Specification (e.g., High Efficiency Video Coding, SERIES H: AUDIOVISUAL AND MULTIMEDIA SYSTEMS: INFRASTRUCTURE OF AUDIOVISUAL SERVICES – CODING OF MOVING VIDEO REC. ITU-T H.265 (February 2018) sets forth the standard that is followed by HEVC compliant devices such as the NVIDIA '105 Products, and is relevant to both decoding and encoding that are performed pursuant to the HEVC standard. For instance, the NVIDIA '105 Products perform a method for encoding a video signal comprised of pixels using motion vectors when performing encoding of H.265/HEVC video data.

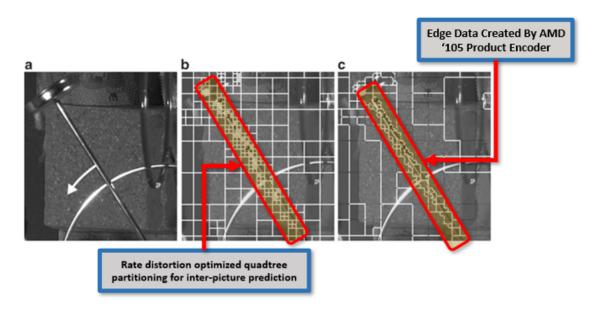

based on edge data. The edge data is generated by the NVIDIA '105 products using merge mode estimation. Specifically, the NVIDIA '105 Products generate merge estimation regions which identify edge information within a video frame. The merge estimation regions are comprised of prediction units ("PU") that contain luma values. For example, in the below diagram PUs are shown. The encoding process then identifies along the edges of each prediction unit a merge estimation region ("MER"). The MER regions thus identify the edges and the PU contains the intensity estimate for the pixels.

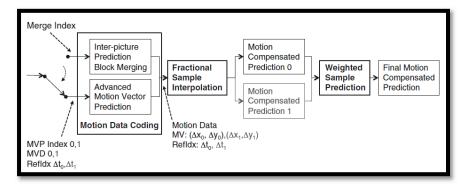

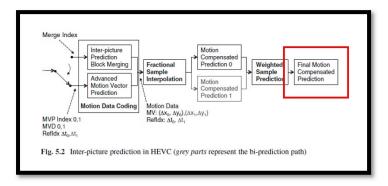

Benjamin Bross et al, *Inter-Picture Prediction in HEVC*, HIGH EFFICIENCY VIDEO CODING (HEVC) at 114 (September 2014) (annotations added).

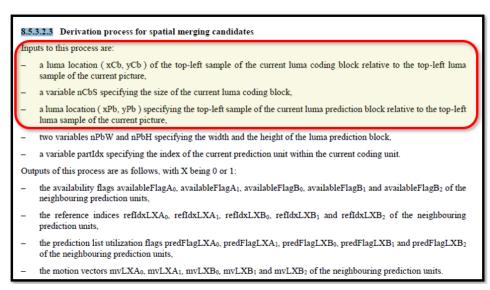

130. The NVIDIA '105 Products in the process of encoding video content in HEVC format generate merge estimation regions generate edge data that include luma location and luma values which include a first intensity estimate. The HEVC standards describes this process as leading to the generation of luma motion vector mvL0 and mvL1.

[T]he derivation process for luma motion vectors for merge mode as specified in clause I.8.5.3.2.7 is invoked with the luma location (xCb, yCb), the luma location (xPb, yPb), the variables nCbS, nPbW, nPbH, and the partition index partIdx as inputs, and the output being the luma motion vectors mvL0, mvL1, the reference indices refIdxL0, refIdxL1, the prediction list utilization flags predFlagL0 and predFlagL1, the flag ivMcFlag, the flag vspMcFlag, and the flag subPbMotionFlag.

High Efficiency Video Coding, SERIES H: AUDIOVISUAL AND MULTIMEDIA SYSTEMS: INFRASTRUCTURE OF AUDIOVISUAL SERVICES – CODING OF MOVING VIDEO REC. ITU-T H.265 at § I.8.5.3.2.1 (February 2018) (emphasis added).

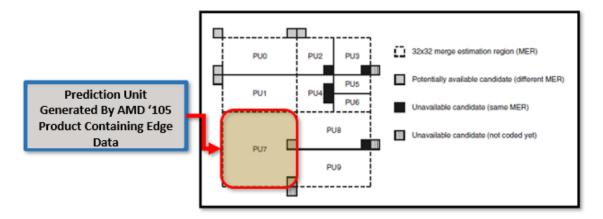

131. The NVIDIA '105 Products perform the step of processing edge data from an edge adaptive interpolation process wherein the edge data includes a first intensity estimate of the pixel. Specifically, the NVIDIA '105 Products implement HEVC encoding which utilizes Parallel Merge Mode and Merge Estimation Regions (MER's) within the interpolation process to determine pixel edges. Parallel Merge Mode Estimation identifies the edge data within a prediction unit. The

below diagram shows how video data is portioned into 10 prediction units and edge data is calculated and passed to the encoder.

Benjamin Bross et al, *Inter-Picture Prediction in HEVC*, HIGH EFFICIENCY VIDEO CODING (HEVC) at 127 (September 2014) (annotations added).

132. The merge estimation processes implemented by the NVIDIA '105 Products is "adaptive." The below excerpt from documentation regarding the HEVC encoding process describes that the "merge estimation level is adaptive."

In order to enable an encoder to trade-off parallelism and coding efficiency, the parallel merge estimation level is adaptive and signaled as log2\_parallel\_merge\_level\_minus2 in the picture parameter set. The following MER sizes are allowed: 4×4 (no parallel merge estimation possible), 8×8, 16×16, 32×32 and 64×64. A higher degree of parallelization, enabled by a larger MER, excludes more potential candidates from the merge candidate list.

Benjamin Bross et al, *Inter-Picture Prediction in HEVC*, HIGH EFFICIENCY VIDEO CODING (HEVC) at 128 (September 2014) (emphasis added).

133. The edge data that is processed from the edge adaptive interpolation process includes intensity estimates for pixels such as pixels in the merge estimation region. The intensity estimate or brightness estimate is referred to as "luma" in the encoding functionality implemented by the NVIDIA '105 Products.

For representing color video signals, HEVC typically uses a tristimulus YCbCr color space with 4:2:0 sampling (although extension to other sampling formats is straightforward, and is planned to be defined in a subsequent version). This separates a color representation into three components called Y, Cb, and Cr. The Y component is also called luma, and represents brightness. The two chroma components Cb and Cr represent the extent to which the color deviates from gray toward blue and red, respectively. Because the human visual system is more

Gary J. Sullivan, Jens-Rainer Ohm, Woo-Jin Han, and Thomas Wiegand, Fellow, IEEE, *Overview of the High Efficiency Video Coding (HEVC) Standard*, published in IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY, Vol. 22, No. 12 at 1654 (December 2012) (emphasis added).

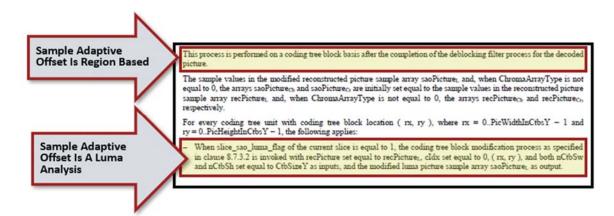

134. The motion estimation region ("MER") is an adaptive interpolation process in which the edges of images are calculated and include the intensity estimates of pixels by way of a luma value. The below excerpt from the HEVC specification describes how during the generation of merge estimation regions edge data includes luminosity values (intensity estimates) for pixels within a region.

High Efficiency Video Coding, Series H: Audiovisual And Multimedia Systems: Infrastructure Of Audiovisual Services – Coding Of Moving Video Rec. ITU-T H.265 at § I.8.5.2.3 (February 2018) (emphasis added).

135. The NVIDIA '105 Products process motion data associated with motion compensation. The motion data processed by the NVIDIA '105 Products include a first estimated

motion vector of pixels within a reference frame prior to the current frame and a second estimated motion vector within the reference field after the current field. Specifically, the NVIDIA '105 products generate motion data in the form of a bi-directional prediction unit (PU) which has two motion vectors (referencing a prior frame and a subsequent frame in the sequence). The two motion vectors are combined to make a "bi-predictive merge candidate." One of the motion vectors is obtained from "reference picture list0" and the other motion vector is obtained from "reference picture list1."

#### 8.5.3.3.2 Reference picture selection process

Input to this process is a reference index refIdxLX.

Output of this process is a reference picture consisting of a two-dimensional array of luma samples refPicL $X_L$  and, when ChromaArrayType is not equal to 0, two two-dimensional arrays of chroma samples refPicL $X_C$ , and refPicL $X_C$ .

The output reference picture RefPicListX[refIdxLX] consists of a pic\_width\_in\_luma\_samples by pic\_height\_in\_luma\_samples array of luma samples refPicLXL and, when ChromaArrayType is not equal to 0, two PicWidthInSamplesC by PicHeightInSamplesC arrays of chroma samples refPicLXCb and refPicLXCb.

The reference picture sample arrays refPicLX<sub>L</sub>, refPicLX<sub>Cb</sub> and refPicLX<sub>Cr</sub> correspond to decoded sample arrays  $S_L$ ,  $S_{Cb}$  and  $S_{Cr}$  derived in clause 8.7 for a previously-decoded picture.

High Efficiency Video Coding, SERIES H: AUDIOVISUAL AND MULTIMEDIA SYSTEMS: INFRASTRUCTURE OF AUDIOVISUAL SERVICES — CODING OF MOVING VIDEO REC. ITU-T H.265 at § I.8.5.3.3 (February 2018).

136. The reference pictures that are used to generate a motion vector comprise both the forward and prior reference pictures which are referred to in the HEVC encoding process implemented by the NVIDIA '105 Products as "refPicLXcb" and "refPicLXcr." The following excerpt describing the implementation of the encoding process in the NVIDIA '105 Products which use bi-predictive slices.

Since a merge candidate comprises all motion data and the TMVP is only one motion vector, the derivation of the whole motion data only depends on the slice type. For bi-predictive slices, a TMVP is derived for each reference picture list. Depending on the availability of the TMVP for each list, the prediction type is set to bi-prediction or to the list for which the TMVP is available. All associated reference picture indices are set equal to zero. Consequently for uni-predictive slices, only the TMVP for list 0 is derived together with the reference picture index equal to zero.

Benjamin Bross et al, *Inter-Picture Prediction in HEVC*, HIGH EFFICIENCY VIDEO CODING (HEVC) at 123 (September 2014) (emphasis added) (describing the use of bi-prediction in which

motion data is derived from the forward and prior reference pictures in generating temporal arrays/vectors).

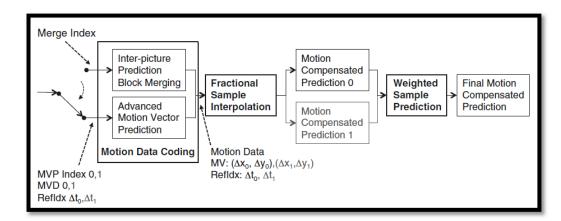

137. The NVIDIA '105 Products interpolation process contains bi-prediction functionality that computes a first estimated motion prediction and a second estimated motion prediction. The below excerpt from documentation of the encoding method used by the NVIDIA '105 products describes that the encoding process includes functionality for generating a second intensity estimate for the pixel data and the edge data determined according to motion. In bi-prediction, the second estimate is defined as  $\Delta x_1$ ,  $\Delta y_1$ ,  $\Delta t_1$ .

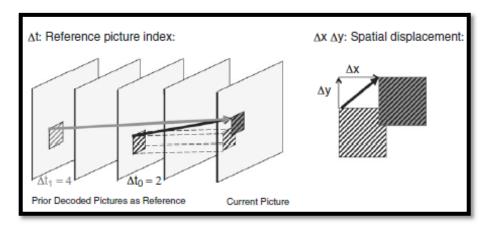

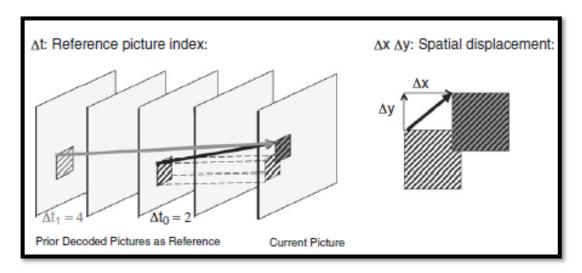

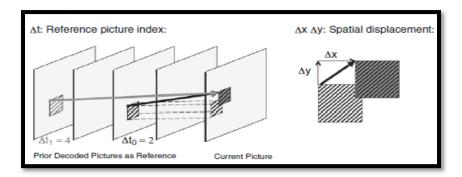

In case of bi-prediction, two sets of motion data  $(\Delta x_0, \Delta y_0, \Delta t_0)$  and  $\Delta x_1, \Delta y_1, \Delta t_1)$  are used to generate two MCPs (possibly from different pictures), which are then combined to get the final MCP. Per default, this is done by averaging but in case of weighted prediction, different weights can be applied to each MCP, e.g. to compensate for scene fade outs. The reference pictures that can be used in bi-prediction are stored in two separate lists, namely list 0 and list 1. In order to limit the memory bandwidth in slices allowing bi-prediction, the HEVC standard restricts PUs with  $4 \times 8$  and  $8 \times 4$  luma prediction blocks to use uni-prediction only. Motion data is derived at the encoder using a motion estimation process. Motion

Benjamin Bross et al, *Inter-Picture Prediction in HEVC*, HIGH EFFICIENCY VIDEO CODING (HEVC) at 114 (September 2014) (emphasis added).

138. In AMVP the system generates a temporal intermediate candidate based on bidirectional motion data. The "inter\_pred\_idc [x0] [y0] specifies whether list0, list1, or biprediction is used for the current prediction unit" according to the below referenced table. "The array indices x0, y0 specify the location (x0, y0) of the top-left luma sample of the considered prediction block relative to the top-left luma sample of the picture."

| Table 7-11 – Name association to inter prediction mode |                        |                      |

|--------------------------------------------------------|------------------------|----------------------|

| inter_pred_idc                                         | Name of inter_pred_idc |                      |

|                                                        | ( nPbW + nPbH ) != 12  | (nPbW + nPbH) = = 12 |

| 0                                                      | PRED_L0                | PRED_L0              |

| 1                                                      | PRED_L1                | PRED_L1              |

| 2                                                      | PRED_BI                | na                   |

High Efficiency Video Coding, Series H: Audiovisual And Multimedia Systems: Infrastructure Of Audiovisual Services – Coding Of Moving Video Rec. ITU-T H.265 at § 7.4.9.6 (February 2018).

data and the motion data. The edge data is combined with the temporal intermediate candidate to generate the temporal candidate. The prediction unit based on the first and second motion vector (motion data) is then combined with the edge data to generate a second intensity estimate. Once the reference picture for obtaining the co-located PU is selected then the position of the co-located Pu will be selected among two candidate positions. A second intensity estimate is generated by using the bi-directional motion vectors and the edge data. The below excerpt from the HEVC specification describes that for a luma motion vector prediction the generation of a second intensity estimate is based on the motion data and the edge data. The edge data here is comprised by the luma location and luma prediction block information. Further, the luma motion vectors mvLO and mvL1 are combined with the edge data including luma location xCB yCB xBL and yBl to generate a second intensity estimate.

#### 8.5.3.2.6 Derivation process for luma motion vector prediction

Inputs to this process are:

- a luma location (xCb, yCb) of the top-left sample of the current luma coding block relative to the top-left luma sample of the current picture,

- a variable nCbS specifying the size of the current luma coding block,

- a luma location (xPb, yPb) specifying the top-left sample of the current luma prediction block relative to the top-left luma sample of the current picture.

- two variables nPbW and nPbH specifying the width and the height of the luma prediction block,

- the reference index of the current prediction unit partition refIdxLX, with X being 0 or 1,

- a variable partIdx specifying the index of the current prediction unit within the current coding unit.

Output of this process is the prediction mvpLX of the motion vector mvLX, with X being 0 or 1.

High Efficiency Video Coding, SERIES H: AUDIOVISUAL AND MULTIMEDIA SYSTEMS: INFRASTRUCTURE OF AUDIOVISUAL SERVICES — CODING OF MOVING VIDEO REC. ITU-T H.265 at § 8.5.3.2.6 (February 2018) (emphasis added).

### 8.5.3.3.1 General

Inputs to this process are:

- a luma location (xCb, yCb) specifying the top-left sample of the current luma coding block relative to the top-left luma sample of the current picture,

- a luma location (xBl, yBl) specifying the top-left sample of the current luma prediction block relative to the top-left sample of the current luma coding block,

- a variable nCbS specifying the size of the current luma coding block,

- two variables nPbW and nPbH specifying the width and the height of the luma prediction block,

- the luma motion vectors mvL0 and mvL1,

- when ChromaArrayType is not equal to 0, the chroma motion vectors mvCL0 and mvCL1,

- the reference indices refIdxL0 and refIdxL1,

- the prediction list utilization flags, predFlagL0, and predFlagL1.

Outputs of this process are:

- an (nCbS<sub>L</sub>)x(nCbS<sub>L</sub>) array predSamples<sub>L</sub> of luma prediction samples, where nCbS<sub>L</sub> is derived as specified below,

- when ChromaArrayType is not equal to 0, an (nCbSw<sub>C</sub>)x(nCbSh<sub>C</sub>) array predSamples<sub>Cb</sub> of chroma prediction samples for the component Cb, where nCbSw<sub>C</sub> and nCbSh<sub>C</sub> are derived as specified below,

High Efficiency Video Coding, SERIES H: AUDIOVISUAL AND MULTIMEDIA SYSTEMS: INFRASTRUCTURE OF AUDIOVISUAL SERVICES – CODING OF MOVING VIDEO REC. ITU-T H.265 at § 8.5.3.3.1 (February 2018) (emphasis added).

140. The NVIDIA '215 Products perform a mixing process in which the final edge/motion data of a pixel is calculated based on a first intensity estimate, second intensity estimate, and motion reliability data. Specifically, the NVIDIA '215 Products encode pixel data using bi-prediction wherein use two types of mixing functions: average mixing and weighted mixing.

In case of bi-prediction, two sets of motion data  $(\Delta x_0, \Delta y_0, \Delta t_0)$  and  $\Delta x_1, \Delta y_1, \Delta t_1)$  are used to generate two MCPs (possibly from different pictures), which are then combined to get the final MCP. Per default, this is done by averaging but in case of weighted prediction, different weights can be applied to each MCP, e.g. to compensate for scene fade outs. The reference pictures that can be used in bi-prediction are stored in two separate lists, namely list 0 and list 1. In order to limit the memory bandwidth in slices allowing bi-prediction, the HEVC standard restricts PUs with  $4 \times 8$  and  $8 \times 4$  luma prediction blocks to use uni-prediction only. Motion data is derived at the encoder using a motion estimation process. Motion

Benjamin Bross et al, *Inter-Picture Prediction in HEVC*, HIGH EFFICIENCY VIDEO CODING (HEVC) at 123 (September 2014) (emphasis added).

141. The HEVC standard includes functionality to perform a mixing process. In MERGE mode, an up-to five-entry MERGE candidate list is first constructed with four (MV, Refldx) pairs from spatial neighbor blocks and one (MV, Refldx) pair from temporal bottom-right or collocated neighbor block, where Refldx is the index of the reference picture that the MV pointed to. After that, the encoder decides to use which candidate (MV, Refldx) pair to encode current block and then encode the candidate index into bitstream. In MERGE mode, the selected (MV, Refldx) pair is directly used to encode current block, and no MVD information needs to be coded. The number of merge candidates could be configured at encoder, with up to five merge candidates."

8.5.3.3.4 Weighted sample prediction process

8.5.3.3.4.1 General

Inputs to this process are:

- two variables nPbW and nPbH specifying the width and the height of the current prediction block,

- two (nPbW)x(nPbH) arrays predSamplesL0 and predSamplesL1,

- the prediction list utilization flags, predFlagL0 and predFlagL1,

- the reference indices refIdxL0 and refIdxL1,

- a variable cIdx specifying colour component index.

Output of this process is the (nPbW)x(nPbH) array pbSamples of prediction sample values.

HIGH EFFICIENCY VIDEO CODING, SERIES H: AUDIOVISUAL AND MULTIMEDIA SYSTEMS: INFRASTRUCTURE OF AUDIOVISUAL SERVICES — CODING OF MOVING VIDEO REC. ITU-T H.265 at § 8.5.3.3.4.1 (February 2018) (emphasis added).

142. The variables predFlagL0 and predFlagL1 are reliability values that are generated by the decoding process. The predFlagL0 and L1 values are prediction utilization values that are used to generate prediction utilization and reliability of the vectors.

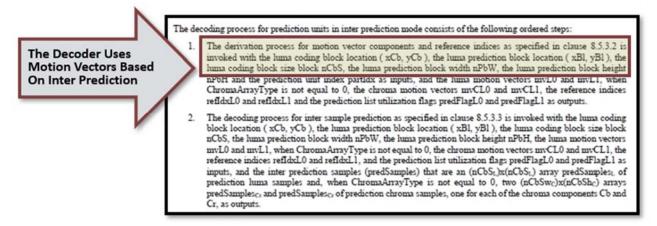

The decoding process for prediction units in inter prediction mode consists of the following ordered steps:

1. The derivation process for motion vector components and reference indices as specified in clause 8.5.3.2 is invoked with the luma coding block location (xCb, yCb), the luma prediction block location (xBl, yBl), the luma coding block size block nCbS, the luma prediction block width nPbW, the luma prediction block height nPbH and the prediction unit index partIdx as inputs, and the luma motion vectors mvL0 and mvL1, when ChromaArrayType is not equal to 0, the chroma motion vectors mvCL0 and mvCL1, the reference indices refIdxL0 and refIdxL1 and the prediction list utilization flags predFlagL0 and predFlagL1 as outputs.

High Efficiency Video Coding, SERIES H: AUDIOVISUAL AND MULTIMEDIA SYSTEMS: INFRASTRUCTURE OF AUDIOVISUAL SERVICES – CODING OF MOVING VIDEO REC. ITU-T H.265 at § 8.5.3.1 (February 2018).

- 143. On information and belief, any implementation of the HEVC standard would infringe the '105 patent as every possible implementation of the standard requires: processing edge data from edge-adaptive interpolation processing, including a first intensity estimate for the pixel as well as data pertaining to one or more pixels that neighbor the pixel; processing motion data associated with motion compensation processing, wherein the motion data includes a first estimated motion vector for a pixel in a reference field prior to the present field and a second estimated motion vector for a pixel in a reference field subsequent to the present field; determining a second intensity estimate for the pixel as a function of the edge data and the motion data; and performing a blending process wherein final edge/motion data of the pixel is calculated as a function of the first intensity estimate, the second intensity estimate, and motion reliability data characterizing reliability of the motion data.

- 144. On information and belief, the NVIDIA '105 Products are available to businesses and individuals throughout the United States.

- 145. On information and belief, the NVIDIA '105 Products are provided to businesses and individuals located in the State of Delaware.

- 146. By making, using, testing, offering for sale, and/or selling products and services for enhancing subsequent images of a video stream in which frames are encoded based on previous frames using prediction and motion estimation, including but not limited to the NVIDIA '037 Products, NVIDIA has injured Dynamic Data and is liable to the Plaintiff for directly infringing one or more claims of the '105 patent, including at least claim 1 pursuant to 35 U.S.C. § 271(a).

- 147. On information and belief, NVIDIA also indirectly infringes the '105 patent by actively inducing infringement under 35 USC § 271(b).

- 148. NVIDIA has had knowledge of the '105 patent since at least service of this First Amended Complaint or shortly thereafter, and on information and belief, NVIDIA knew of the '105 patent and knew of its infringement, including by way of this lawsuit.

- 149. On information and belief, NVIDIA intended to induce patent infringement by third-party customers and users of the NVIDIA '105 Products and had knowledge that the inducing acts would cause infringement or was willfully blind to the possibility that its inducing acts would cause infringement. NVIDIA specifically intended and was aware that the normal and customary use of the accused products would infringe the '105 patent. NVIDIA performed the acts that constitute induced infringement, and would induce actual infringement, with knowledge of the '105 patent and with the knowledge that the induced acts would constitute infringement. For example, NVIDIA provides the NVIDIA '105 Products that have the capability of operating in a manner that infringe one or more of the claims of the '105 patent, including at least claim 1, and NVIDIA further provides documentation and training materials that cause customers and end users of the NVIDIA '105 Products to utilize the products in a manner that directly infringe one or more claims of the '105 patent. <sup>22</sup> By providing instruction and training to customers and end-users on

<sup>&</sup>lt;sup>22</sup> See, e.g., NVIDIA Quadro P4000, NVIDIA DATASHEET (2017); The Right Tools for Professionals: NVIDIA Workstation GPUs, NVIDIA PROFESSIONAL SOLUTION GUIDE (2017);

how to use the NVIDIA '105 Products in a manner that directly infringes one or more claims of the '105 patent, including at least claim 1, NVIDIA specifically intended to induce infringement of the '105 patent. On information and belief, NVIDIA engaged in such inducement to promote the sales of the NVIDIA '105 Products, e.g., through NVIDIA user manuals, product support, marketing materials, and training materials to actively induce the users of the accused products to infringe the '105 patent. Accordingly, NVIDIA has induced and continues to induce users of the accused products to use the accused products in their ordinary and customary way to infringe the '105 patent, knowing that such use constitutes infringement of the '105 patent.

- 150. The '105 patent is well-known within the industry as demonstrated by multiple citations to the '105 patent in published patents and patent applications assigned to technology companies and academic institutions. NVIDIA is utilizing the technology claimed in the '105 patent without paying a reasonable royalty. NVIDIA is infringing the '105 patent in a manner best described as willful, wanton, malicious, in bad faith, deliberate, consciously wrongful, flagrant, or characteristic of a pirate.

- 151. To the extent applicable, the requirements of 35 U.S.C. § 287(a) have been met with respect to the '105 patent.

- 152. As a result of NVIDIA's infringement of the '105 patent, Dynamic Data has suffered monetary damages, and seeks recovery in an amount adequate to compensate for

NVIDIA GeForce GTX 1080, NVIDIA WHITEPAPER (2016); GeForce GTX 1060, NVIDIA USER GUIDE (2016); GeForce GTX 1070, NVIDIA USER GUIDE (2016); Titan Xp, NVIDIA USER GUIDE (2017); NVIDIA Tesla P40 GPU Accelerator, NVIDIA DATASHEET (2017); GRID Virtual GPU, NVIDIA USER GUIDE (Nov. 2016); Virtual GPU Software, NVIDIA USER GUIDE (Oct. 2018); NVIDIA Tesla M60 GPU Accelerator, NVIDIA DATASHEET (2016); Real Interactive Expression: NVIDIA Quadro M6000, NVIDIA DATASHEET (2015); NVIDIA Tesla V100 GPU Architecture, NVIDIA WHITEPAPER (2015).

NVIDIA's infringement, but in no event less than a reasonable royalty for the use made of the invention by NVIDIA together with interest and costs as fixed by the Court.

# COUNT II INFRINGEMENT OF U.S. PATENT No. 8,135,073

- 153. Dynamic Data references and incorporates by reference the preceding paragraphs of this Complaint as if fully set forth herein.

- 154. NVIDIA designs, makes, uses, sells, and/or offers for sale in the United States products and/or services for enhancing subsequent images of a video stream in which frames are encoded based on previous frames using prediction and motion estimation.

- 155. NVIDIA designs, makes, sells, offers to sell, imports, and/or uses NVIDIA products, including the following: GeForce GT 1030, GeForce GTX 1050 / 1050 Ti, GeForce GTX 1060, GeForce GTX 1070 1080, GeForce GTX 1080 Ti, GeForce GTX Titan X Titan Xp, Titan V, Quadro P400 P1000, Quadro P2000, Quadro P4000 / P5000, Quadro P6000, Quadro GP100, Quadro GV100, Tesla M4, Tesla P4 / P6, Tesla P40, Tesla P100, Tesla V100, GeForce GTX 750 GeForce GTX 950 960, GeForce GT 1030, Quadro M2000, Quadro P400, Quadro P600, Quadro P620, and Quadro P1000 (collectively, the "NVIDIA '073 Product(s)").

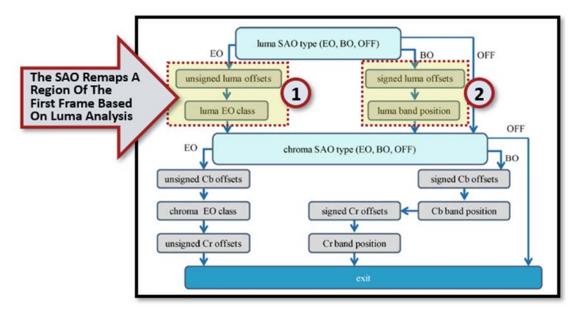

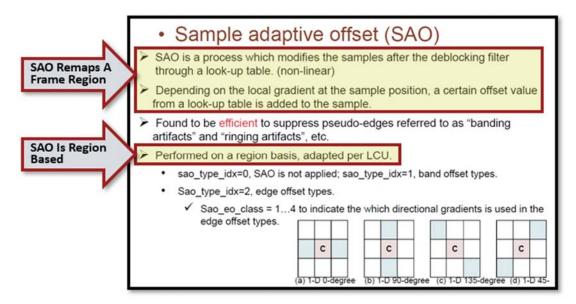

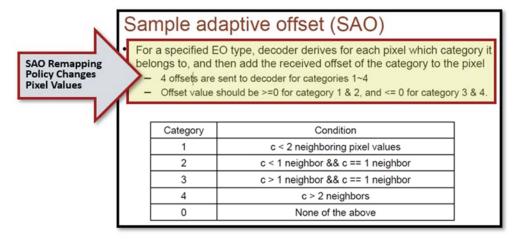

- 156. On information and belief, the NVIDIA '073 Products contain a processor for decoding the received encoded frame-based encoded video data. Further, the NVIDIA '073 Products apply a remapping policy to the first frame of decoded video data using a region-based luma analysis. As part of the decoding process performed by NVIDIA '073 Products, a reference picture (first frame) is decoded and two in-loop filters (deblocking and a sample adaptive offset) are applied to the reference picture.

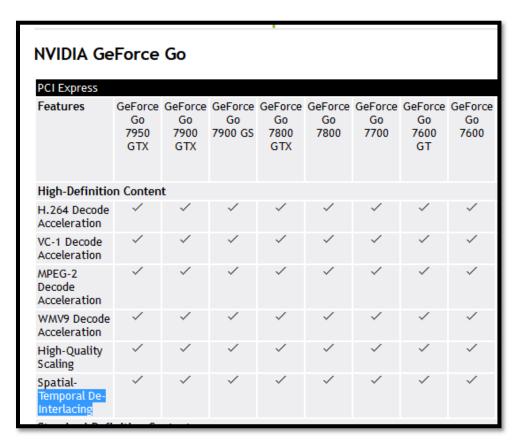

157. The NVIDIA '073 Products enable HEVC video decoding. The following excerpt from the NVIDIA Video Encode and Decode GPU Support Matrix identifies that the NVIDIA '073 Products comply with the HEVC standard for decoding data.

| BOARD                        | FAMILY |       | # OF  | # OF<br>NVDEC<br>/CHIP | Total<br># of<br>NDEC | MPEG-1 | MPEG-2 | VC-1 | VP8 |       | VP9    |        | H.26  | H.265 (HEVC) 4: |        | 14:2:0 | 4:2:0 *H.265 (HEV |        | (C) 4:4:4 |  |

|------------------------------|--------|-------|-------|------------------------|-----------------------|--------|--------|------|-----|-------|--------|--------|-------|-----------------|--------|--------|-------------------|--------|-----------|--|

|                              |        | CHIP  | CHIPS |                        |                       |        |        |      |     | 8 bit | 10 bit | 12 bit | (AVCH | 8 bit           | 10 bit | 12 bit | 8 bit             | 10 bit | 12 bit    |  |

| GeForce                      |        |       |       |                        |                       |        |        |      |     |       |        |        |       |                 |        |        |                   |        |           |  |

| GeForce GT 1030              | Pascal | GP108 | 1     | 1                      | 1                     | YES    | YES    | YES  | NO  | YES   | YES    | YES    | YES   | YES             | YES    | YES    | NO                | NO     | NO        |  |

| GeForce GTX 1050 / 1050 Ti   | Pascal | GP107 | 1     | 1                      | 1                     | YES    | YES    | YES  | NO  | YES   | YES    | YES    | YES   | YES             | YES    | YES    | NO                | NO     | NO        |  |

| GeForce GTX 1050 / 1050 Ti   | Pascal | GP106 | 1     | 1                      | 1                     | YES    | YES    | YES  | NO  | YES   | NO     | NO     | YES   | YES             | YES    | YES    | NO                | NO     | NO        |  |

| GeForce GTX 1060             | Pascal | GP106 | 1     | 1                      | 1                     | YES    | YES    | YES  | NO  | YES   | NO     | NO     | YES   | YES             | YES    | YES    | NO                | NO     | NO        |  |

| GeForce GTX 1060             | Pascal | GP104 | 1     | 1                      | 1                     | YES    | YES    | YES  | NO  | YES   | NO     | NO     | YES   | YES             | YES    | YES    | NO                | NO     | NO        |  |

| GeForce GTX 1070 - 1080      | Pescel | GP104 | 1     | 1                      | 1                     | YES    | YES    | YES  | YES | YES   | NO     | NO     | YES   | YES             | YES    | YES    | NO                | NO     | NO        |  |

| GeForce GTX 1080 Ti          | Pescel | GP102 | 1     | 1                      | 1                     | YES    | YES    | YES  | NO  | YES   | YES    | YES    | YES   | YES             | YES    | YES    | NO                | NO.    | NO        |  |