| 1  | Jon A. Birmingham (CA SBN 271034)                                                    |                              |  |  |  |  |

|----|--------------------------------------------------------------------------------------|------------------------------|--|--|--|--|

| 2  | FITCH, EVEN, TABIN & FLANNERY LLP                                                    |                              |  |  |  |  |

|    | 21700 Oxnard Street, Suite 1740                                                      |                              |  |  |  |  |

| 3  | Woodland Hills, California 91367                                                     |                              |  |  |  |  |

| 4  | Telephone: (818) 715-7025                                                            |                              |  |  |  |  |

| 5  | Facsimile: (818) 715-7033<br>Email: jbirmi@fitcheven.com                             |                              |  |  |  |  |

| 6  |                                                                                      |                              |  |  |  |  |

| 7  | Timothy P. Maloney ( <i>admitted pro hac vice</i> )<br>tpmalo@fitcheven.com          |                              |  |  |  |  |

| 8  | Joseph F. Marinelli ( <i>admitted pro hac vice</i> )<br>jmarinelli@fitcheven.com     |                              |  |  |  |  |

| 9  | David A. Gosse ( <i>admitted pro hac vice</i> )<br>dgosse@fitcheven.com              |                              |  |  |  |  |

| 10 | <b>FITCH, EVEN, TABIN &amp; FLANNERY LLP</b><br>120 South LaSalle Street, Suite 2100 |                              |  |  |  |  |

| 11 | Chicago, Illinois 60603                                                              |                              |  |  |  |  |

| 12 | Telephone: (312) 577-7000<br>Facsimile: (312) 577-7007                               |                              |  |  |  |  |

| 13 | Attorneys for Plaintiff,                                                             |                              |  |  |  |  |

| 14 | LONE STAR SILICON INNOVATIONS LLC                                                    |                              |  |  |  |  |

| 15 | UNITED STATES                                                                        | DISTRICT COURT               |  |  |  |  |

| 16 | UNITED STATES DISTRICT COURT<br>NORTHERN DISTRICT OF CALIFORNIA                      |                              |  |  |  |  |

| 17 | SAN FRANCISCO DIVISION                                                               |                              |  |  |  |  |

| 18 | LONE STAR SILICON INNOVATIONS LLC,                                                   | Case No.: 3:17-cv-04032-WHA  |  |  |  |  |

| 19 |                                                                                      | Case No.: 5.17-CV-04052-WIIA |  |  |  |  |

| 20 | Plaintiff,                                                                           |                              |  |  |  |  |

| 21 | v.                                                                                   | FIRST AMENDED COMPLAINT FOR  |  |  |  |  |

| 22 | NANYA TECHNOLOGY CORPORATION,<br>NANYA TECHNOLOGY CORPORATION                        | PATENT INFRINGEMENT          |  |  |  |  |

| 23 | U.S.A.,<br>NANYA TECHNOLOGY CORPORATION                                              | DEMAND FOR JURY TRIAL        |  |  |  |  |

| 24 | DELAWARE, and                                                                        |                              |  |  |  |  |

| 25 | ADVANCED MICRO DEVICES, INC.,                                                        |                              |  |  |  |  |

| 26 | Defendants.                                                                          |                              |  |  |  |  |

| 27 |                                                                                      | _                            |  |  |  |  |

| 28 |                                                                                      |                              |  |  |  |  |

|    | FIRST AMENDED COMPLAINT FOR PATENT INFRINGE<br>CASE NO. 3:17-cv-04032-WHA            | MENT                         |  |  |  |  |

|    |                                                                                      |                              |  |  |  |  |

l

Plaintiff, Lone Star Silicon Innovations LLC ("Lone Star"), complains against Defendants Nanya

Technology Corporation, Nanya Technology Corporation, U.S.A., and Nanya Technology Corporation

Delaware (individually or collectively, "the Nanya Defendants"), and Advanced Micro Devices, Inc.

(together, "Defendants") as follows:

### **NATURE OF ACTION**

6 1. This is an action for patent infringement of United States Patent Nos. 6,097,061, and

7 6,388,330 (collectively, the "Patents in Suit") under the Patent Laws of the United States, 35 U.S.C. § 1,

8 *et seq.*

9

5

### THE PARTIES

Plaintiff Lone Star is a corporation organized and existing under the laws of the State of

Texas with its principle place of business at 8105 Rasor Blvd., Suite 210, Plano, TX 75024. Lone Star is

in the business of licensing patented technology.

3. Defendant Nanya Technology Corporation ("Nanya") is a corporation incorporated under

the laws of Taiwan with its principal place of business at Hwa Ya Technology Park, 669 Fu Hsing 3rd

Road, KueiShan, TaoYuan 333, Taiwan. Defendant Nanya conducts business in and is doing business in

California and in this District and elsewhere in the United States, including, without limitation, using,

promoting, offering to sell, importing and/or selling memory devices and/or devices that incorporate

memory devices that embody the patented technology, and enabling end-user purchasers to use such

devices in this District.

20 4. Defendant Nanya Technology Corporation, U.S.A. ("Nanya USA") is a corporation 21 organized under the laws of the state of California with its principal place of business at 1735 Technology 22 Dr., Suite 400, San Jose, California 95110. Nanya USA's registered agent for service of process in the 23 State of California is Business Filings Incorporated, located at 818 West Seventh Street, Suite 930, Los Angeles, California 90017. Upon information and belief, Nanya USA is a wholly-owned subsidiary of 24 25 Nanya. Nanya USA supports Nanya's original equipment manufacturers ("OEM") business in the United 26 States with local sales and technical support offices in San Jose, California. These local sales and technical 27 support offices support the sales, product marketing, quality assurance, and logistics operations of Nanya 28 in the United States. Nanya USA also has a network of manufacturer representatives and distributors

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 3 of 85

across the United States to support customers. Nanya USA has also established warehouse locations in

the United States. Defendant Nanya USA conducts business in and is doing business in California, and in

the District, and elsewhere in the United States, including, without limitation, using, promoting, offering

to sell, importing and/or selling memory devices and/or devices that incorporate memory devices that

embody patented technology, and enabling end-user purchasers to use such devices in this District.

6 5. Defendant Nanya Technology Corporation Delaware ("Nanya Delaware") is a corporation organized under the laws of the state of Delaware with principal places of business at 5104 Old Ironside 7 8 Drive, Suite 113, Santa Clara, California 95054, and 108 West 13th Street, Wilmington, Delaware 19801. 9 Nanya Delaware's registered agent for service of process in the State of California is C T Corporation 10 System, 818 West Seventh Street, Suite 930, Los Angeles CA 90017. Upon information and belief, Nanya 11 Delaware is a wholly-owned subsidiary of Nanya. Defendant Nanya Delaware conducts business in and 12 is doing business in California and in the District and elsewhere in the United States, including, without 13 limitation, using, promoting, offering to sell, importing and/or selling memory devices and/or devices that 14 incorporate memory devices that embody patented technology, and enabling end-user purchasers to use 15 such devices in this District.

16 6. Upon information and belief, Nanya controls and is the majority owner of the other Nanya

17 Defendants, and the Nanya Defendants are joint tortfeasors with one another with respect to the matters

18 alleged herein.

Advanced Micro Devices, Inc. ("AMD") is a corporation organized and existing under the

law of the State of Delaware, and maintains its principal place of business at One AMD Place, Sunnyvale,

California 94085.

8. As alleged in more detail below, AMD previously transferred rights in the Patents in Suit to Lone Star pursuant to a Patent Transfer Agreement effective August 4, 2016, which was amended on or about November 23, 2016, a copy of which is attached as Exhibit 1 (collectively "the Patent Transfer Agreement"). The rights transferred to Lone Star included "all rights to pursue damages, injunctive relief and other remedies for past, current and future infringement of" the Patents in Suit. The Court previously held that Lone Star lacked sufficient rights to bring suit against the Nanya Defendants without AMD, and dismissed the action without prejudice. (Dkt. No. 93, January 20, 2018 Order). Limestone appealed the

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 4 of 85

1 decision of the Court to Federal Circuit, arguing that it had all substantial rights to the Patent in Suit, and, 2 alternatively, that if it did not that it did not have all substantial rights to the Patents in Suit then it should 3 be allowed join AMD. The Federal Circuit held that Lone Star did not have all substantial rights under the 4 Patents in Suit and that some of the substantial rights were held by AMD. Lone Star Silicon Innovations 5 LLC v. Nanya Tech. Corp et al., 925 F.3d 1225, 1229-34 (Fed. Cir. 2019). The Federal Circuit vacated 6 the decision of the Court to dismiss this action, and remanded the case with instructions that Lone Star be 7 permitted an opportunity to join AMD under Fed. R. Civ. P. 19(a). Id. at 1236–1239. The Federal Circuit 8 instructed the Court to consider whether AMD's joinder is feasible and, "[i]f so, then AMD must be 9 joined—involuntarily if need be." Id. at 1236.

10 9. In view of the rulings of this Court and of the Federal Circuit that AMD holds some 11 substantial rights in the Patents in Suit, AMD should be joined as a required party to this action. AMD has 12 an implied legal obligation to Lone Star to allow its name to be used as joined co-plaintiff in order to 13 assure that Lone Star can enforce the rights granted to Lone Star under the Patent Transfer Agreement. 14 Lone Star requested that AMD join this action as a plaintiff, but AMD declined that request and has 15 refused to voluntarily join as a plaintiff. Joining AMD is feasible because AMD is subject to service of 16 process and to personal jurisdiction in this Court, and such joinder would not divest the Court of subject 17 matter jurisdiction and would not make venue improper.

18 10. Rule 19(a)(2) permits joining AMD as a defendant or as an involuntary plaintiff. Under the 19 "primary purpose" test applied in the Ninth Circuit, a district court should align those parties whose 20 interests coincide respecting the primary matter in dispute. Realignment of AMD as a plaintiff is 21 appropriate because the primary matter in dispute is infringement and validity of the Patents in Suit and 22 Lone Star's request for infringement damages. The interests of AMD and Lone Star coincide with respect 23 to the primary matter in dispute because AMD is the original owner of the Patents in Suit, is a party to the 24 Patent Transfer Agreement, and has a contingent financial interest in any recovery.

25

### JURISDICTION AND VENUE

26 11. On October 7, 2016, Lone Star initiated this action against the Nanya Defendants under the 27 Patent Laws of the United States, Title 35 of the United States Code in the District Court for the Eastern 28 District of Texas. On February 28, 2017, the Nanya Defendants moved to transfer venue to this District. FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT 3

CASE NO. 3:17-cv-04032-WHA

Case 2:16-cv-01117-JRG-RSP, Docket No. 17. On May 22, 2017, the Supreme Court decided *TC Heartland LLC v. Kraft Foods Group Brands LLC*, 137 S.Ct. 1514 (2017). On June 19, 2017, in light of

the *TC Heartland* decision, Lone Star conceded to transfer the action to this District. On July 14, 2017,

the District Court for the Eastern District of Texas transferred the action to this District. This Court has

subject matter jurisdiction over this action pursuant to 28 U.S.C. §§ 1331 and 1338(a).

6 12. Nanya USA is subject to personal jurisdiction in this Court because it has an established 7 place of business in this District and is incorporated under the laws of the State of California. Nanya 8 Delaware consented to jurisdiction and venue in this District for purposes of this case. Case No. 2:16-cv-9 01117-JRG-RSP, Docket No. 17 ("NTC Delaware consents to jurisdiction in the Northern District of 10 California for purposes of this lawsuit only.") On information and belief, the Nanya Defendants are also 11 subject to this Court's specific and general personal jurisdiction pursuant to due process and/or the 12 California Long Arm Statute, due at least to their substantial business conducted in this forum, directly 13 and/or through intermediaries, including (i) having solicited business in the State of California, having 14 transacted business within the State of California, and having attempted to derive financial benefit from 15 residents of the State of California, including benefits directly related to the instant patent infringement 16 causes of action set forth herein; (ii) having placed their products and services into the stream of commerce 17 throughout the United States and having been actively engaged in transacting business in California and 18 in this District; and (iii) either alone or in conjunction with others, having committed acts of infringement 19 within California and in this District. On information and belief, within this district the Nanya Defendants, 20 directly and/or through intermediaries, have advertised (including through websites), offered to sell, sold 21 and/or distributed infringing products, and/or have induced the sale and use of infringing products in the 22 United States and in California. The Nanya Defendants have, directly or through their distribution 23 network, purposefully and voluntarily placed such products in the stream of commerce knowing and 24 expecting them to be purchased and used by consumers in California. The Nanya Defendants have either 25 committed direct infringement in California or committed indirect infringement based on acts of direct 26 infringement in California and from Nanya USA's location in San Jose, California. Further, on 27 information and belief, the Nanya Defendants are subject to the Court's general jurisdiction, including 28 from regularly doing or soliciting business, engaging in other persistent courses of conduct, and/or

deriving substantial revenue from goods and services provided to individuals in California and in this

District.

3 13. On information and belief, the Nanya Defendants do one or more of the following with 4 memory devices and/or devices that incorporate memory devices that embody the patented technology 5 that they or their foundries manufacture: (a) make these devices in the United States for sale to customers, 6 including customers in California; (b) import these devices into the United States for sale to consumers, 7 including consumers in California; (c) sell them or offer them for sale in the United States, including to 8 customers in California; and/or (d) sell them to customers who incorporate them into products that such 9 customers import, sell, or offer for sale in the United States, including in California.

10 14. AMD is subject to personal jurisdiction in this Court because it has an established place of 11 business in this District. On information and belief, AMD is also subject to this Court's specific and 12 general personal jurisdiction pursuant to due process and/or the California Long Arm Statute, due at least 13 to its substantial business conducted in this forum, directly and/or through intermediaries, including (a) 14 having solicited business in the State of California, having transacted business within the State of 15 California, and having attempted to derive financial benefit from residents of the State of California; (b) 16 having placed its products and services into the stream of commerce throughout the United States and 17 having been actively engaged in transacting business in California and in this District; and (c) having 18 consented to jurisdiction and venue in the United States District Court for the Northern District of 19 California with respect to all civil actions or other legal proceedings directly arising between the Lone 20 Star and AMD under the Patent Transfer Agreement.

21 15. Venue lies in this District pursuant to 28 U.S.C. §§ 1391 and 1400. Defendant Nanya USA 22 is subject to personal jurisdiction in this District, has a regular and established place of business within 23 this District, resides in this District, and has committed acts of infringement within this District. Defendant 24 Nanya Delaware consented to venue in this District. In addition, venue is proper in this District for 25 Defendant Nanya pursuant to 28 U.S.C. § 1391(c)(3) because it is not resident in the United States, and 26 therefore may be sued in any federal judicial district. Venue is proper in this District as to AMD under 28 27 U.S.C. §§ 1391 and 1400 because it is subject to personal jurisdiction in this District and resides in this 28 District.

1 2

### THE PATENTS IN SUIT

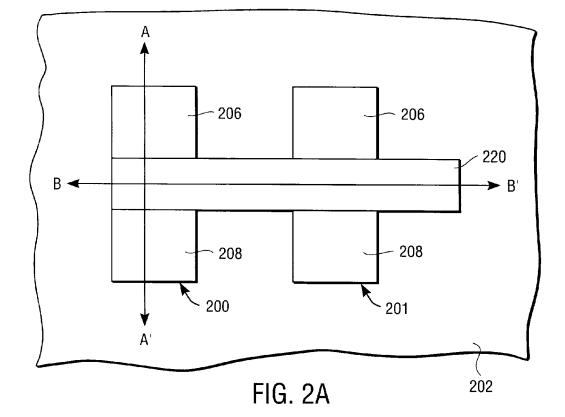

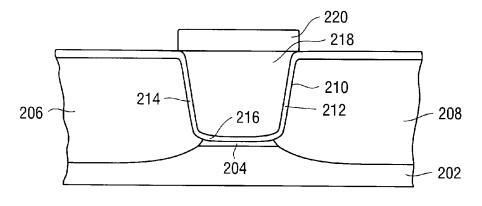

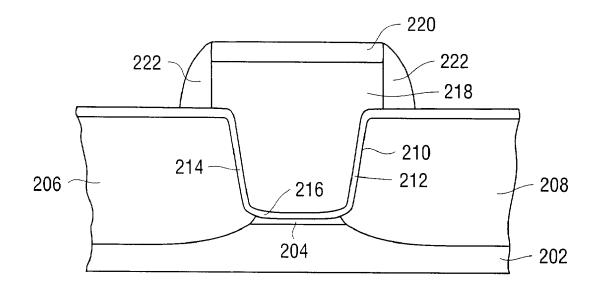

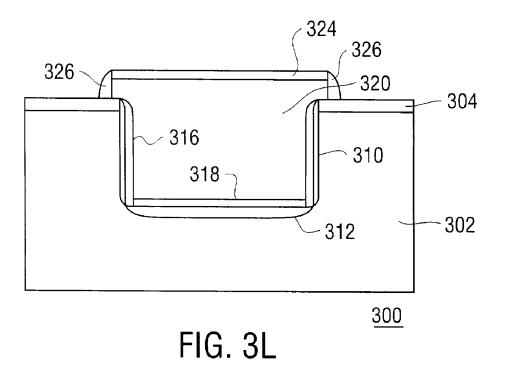

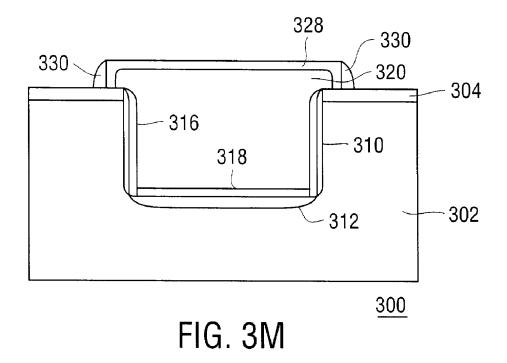

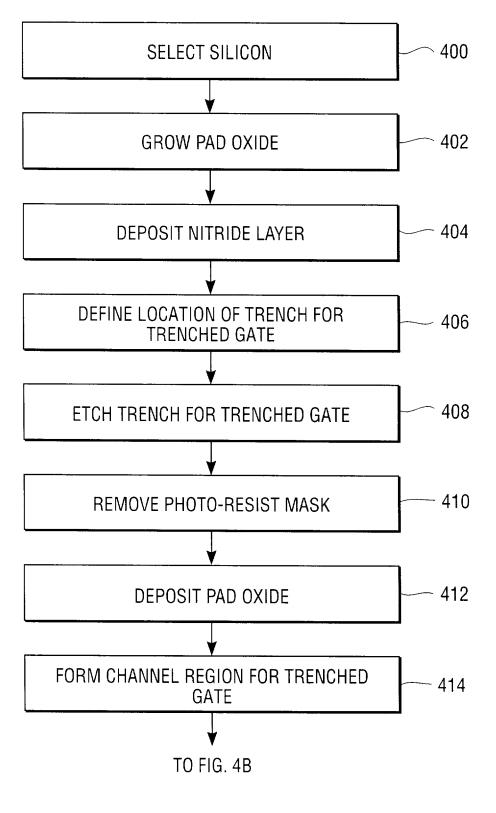

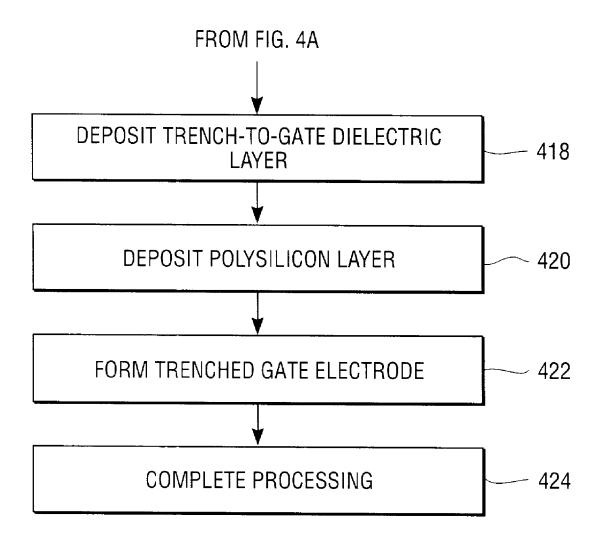

16. On August 1, 2000, U.S. Patent No. 6,097,061 ("the '061 patent"), entitled "Trenched Gate

Metal Oxide Semiconductor Device And Method," a copy of which is attached hereto as Exhibit 2, was

duly and legally issued. The '061 patent issued from U.S. patent application Serial Number 09/052,051

filed December March 30, 1998 and discloses and relates to the design of and processes for fabricating

semiconductor transistor devices.

7 17. In an assignment recorded in the United States Patent Office Reel/Frame 009083/0052 on 8 March 30, 1998, the inventors of the inventions contained in the '061 patent assigned all right, title, and 9 interest in the '061 patent and all inventions contained therein to AMD. An assignment recorded in the 10 United States Patent Office on August 5, 2016, Reel/Frame 039597/0957, indicates that AMD assigned 11 "all of [its] entire right, title and interest in and to" the '061 patent to Lone Star, including all rights "in 12 and to causes of actions and enforcement rights" and "all rights to pursue damages, injunctive relief and 13 other remedies for past, present and future infringement of' the '061 patent. The assignment of the '061 14 patent from AMD to Lone Star was made subject to the terms and conditions of the Patent Transfer 15 Agreement (which was inadvertently referenced as a Confidential Purchase and Sale Agreement in the 16 recorded assignment document). Lone Star has the right to sue the Nanya Defendants for infringement 17 and collect past, present, and future damages and to seek and obtain injunctive or any other relief for 18 infringement of the '061 patent.

19 18. The validity of the '061 patent was challenged before the United States Patents and

20 Trademark Office in *inter partes* review proceedings numbered: IPR2017-01562 and IPR2018-00063. In

21 IPR2017-01562, claims 1, 3–6, 11, and 13–16 of the '061 patent were found to be invalid. In IPR201822 00063, claims 1, 3, 4, 11, 13, and 14 of the '061 patent were found to be invalid. Lone Star has appealed

23 each of these decisions to the Federal Circuit in Appeal Nos. 19-1556 and 19-2152.

24 19. On May 14, 2002, U.S. Patent No. 6,388,330 ("the '330 patent"), entitled "Low Dielectric

25 Constant Etch Stop Layers In Integrated Circuit Interconnects," a copy of which is attached hereto as

26 Exhibit 3, was duly and legally issued. The '330 patent issued from U.S. patent application Serial Number

27 09/776,012 filed February 1, 2001 and discloses and relates to the design of and processes for fabricating

28 semiconductor devices.

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 8 of 85

1 20. In an assignment recorded in the United States Patent Office on February 2, 2001, 2 Reel/Frame 011530/0755, the inventors of the inventions contained in the '330 patent assigned all right, 3 title, and interest in the '330 patent and all inventions contained therein to AMD. An assignment recorded 4 in the United States Patent Office on August 5, 2016, Reel/Frame 039597/0957, indicates that AMD 5 assigned "all of [its] entire right, title and interest in and to" the '330 patent to Lone Star, including all 6 rights "in and to causes of actions and enforcement rights" and "all rights to pursue damages, injunctive 7 relief and other remedies for past, present and future infringement of" the '330 patent. The assignment of 8 the '330 patent from AMD to Lone Star was made subject to the terms and conditions of the Patent 9 Transfer Agreement (which was inadvertently referenced as a Confidential Purchase and Sale Agreement 10 in the recorded assignment document). Lone Star has the right to sue the Nanya Defendants for 11 infringement and collect past, present, and future damages and to seek and obtain injunctive or any other 12 relief for infringement of the '330 patent.

13 21. The validity of the '330 patent was challenged before the United States Patents and 14 Trademark Office in *inter partes* review proceedings numbered: IPR2017-01566, IPR2017-01869, 15 IPR2018-00062, and IPR2018-00087. Each of those inter partes review proceedings were instituted and 16 each proceeded to a final written decision except IPR2018-00087 which was terminated prior to entry of 17 a final written decision. In IPR2017-01566, claims 1, 2, 5–7, and 10 were found to be invalid. Lone Star 18 has appealed that decision to the Federal Circuit (Appeal No. 19-1669) with respect to claim 2. In 19 IPR2017-01869 claims 1, 4-6, 9, and 10 were found to be invalid. In IPR2018-00062 claims 1, 5, 6, and 20 10 were found to be invalid. In both IPR2017-01869 and IPR2018-00062, claim 2 was not shown to be 21 invalid. Nanya has appealed the Board's final written decision in IPR2018-00062, with respect to claim 22 2, to the Federal Circuit (Appeal No. 19-2030). The Board's final written decision in IPR2017-01869, 23 with respect to claim 2, was not appealed.

24

### LONE STAR'S STANDING TO BRING THIS LAWSUIT

25 22. Lone Star and AMD have standing to bring this action because together they possess all

26 substantial rights to the Patents in Suit.

27 23. The Patent Transfer Agreement refers interchangeably to "Listed Patents" (see Exhibit A

28 thereof) and "Assigned Patents" (see Exhibit B thereof). The Patents in Suit are included among the Listed

FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT 7

CASE NO. 3:17-cv-04032-WHA

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 9 of 85

Patents and the Assigned Patents. The Patent Transfer Agreement includes a representation that AMD, or 1 2 one of its Affiliates, has good and marketable title to each Listed Patent, "including all rights, title, and 3 interest in each such Listed Patent and the right to sue for past, present and future infringement thereof," 4 and is the original assignee of the Listed Patents. (Ex. 1, §§ 6.1(b)(i) and (ii).) The Patent Transfer 5 Agreement purports to assign to Lone Star "all right, title and interest in, to and under the Assigned 6 Patents" including "any and all legal rights entitled by [AMD] and all rights of AMD to sue for past, 7 present and future infringement of any and all of the Assigned Patents." (Ex. 1, § 2.1.) The Patent Transfer 8 Agreement also states that AMD assigned to Lone Star "all right, title and interest in, to and under all 9 causes of action and enforcement rights, whether known, unknown, currently pending, filed, or otherwise, 10 for the Assigned Patents, including all rights to pursue damages, injunctive relief and other remedies for 11 past, current and future infringement of the Assigned Patents." (Ex. 1, § 2.2.) Lone Star also received all 12 rights "to collect royalties under such Assigned Patents, to prosecute all existing Assigned Patents worldwide, to apply for additional Assigned Patents worldwide and to have Assigned Patents issue in the 13 name of Lone Star." (Ex. 1, § 2.1.) 14

15 24. As consideration for assigning the Assigned Patents to Lone Star, AMD is entitled to

16 deferred compensation in the form of "Contingent Payments" based on any proceeds generated by Lone

17 Star's patent enforcement and licensing efforts. (Ex. 1 at § 5.1.)

Pursuant to the Patent Transfer Agreement and as part of the consideration provided to

AMD, Lone Star contractually granted a non-exclusive license back to AMD, effective as of the Effective

Date. The rights granted to AMD include, inter alia, the right to make, offer for sale and sell AMD products

covered by the Assigned Patents. (Ex. 1, § 4.1.)

22 26. The Patent Transfer Agreement acknowledges that the Assigned Patents are subject to 23 certain pre-existing rights previously extended directly or indirectly by AMD to certain third parties, and 24 reflects the parties' commitment to respect those rights. These are defined as "Existing Encumbrances," 25 which may include, for example, pre-existing patent licenses, covenants not to sue, releases for past 26 infringement granted by AMD, and pre-existing commitments relating to AMD's activities in 27 standardization activities or patent pool activities. (Ex. 1, § 1.) Lone Star acknowledged that the Assigned

28

Patents are subject to these Existing Encumbrances, and "commit[ted] to comply with such Existing

Encumbrances...." (Ex. 1, § 2.3.)

3 27. The Patent Transfer Agreement includes a list of "Unlicensed Third Party Entities" that are 4 "not authorized or otherwise granted any rights (other than potentially by an implied license running with 5 [AMD's] Licensed Products) by AMD to the Assigned Patents to use, develop, copy, modify, import, 6 make and have made, offer for sale, sell, lease, import, export, distribute, demonstrate, display, transfer 7 and/or otherwise exploit or dispose of a product or service by the Unlicensed Third Party Entity." (Ex. 1, 8 § 1 and Exhibit E.) AMD further represented and warranted that to its knowledge, none of the Unlicensed 9 Third Party Entities have been granted any rights under the Assigned Patents by AMD or its Affiliates. 10 (Ex. 1, § 6.1(b)(vii).) The Nanya Defendants each qualify as an Unlicensed Third Party Entity.

28. As additional consideration, Lone Star further contractually agreed to provide notice to

AMD in the event that Lone Star decided not to pay a renewal, annuity, or maintenance fee on any

Assigned Patent, and to assign such patent back to AMD or AMD's chosen designee upon AMD's request.

(Ex. 1, § 3.4.) This clause of the Patent Transfer Agreement is of no legal or practical effect on the

Assigned Patents because, as of the Effective Date, all maintenance fees had already been paid for the full

remaining life of the patents.

17 29. For the purpose of protecting AMD's interest in Contingent Payments, Lone Star also

18 agreed that it would not transfer its ownership of any Assigned Patents unless all such patents are

19 transferred collectively, the proposed assignee agrees in writing (with copy to AMD) to be bound by the

20 Patent Transfer Agreement as Lone Star's successor-in-interest, and AMD provides its written consent to

21 the transfer, "which shall not be unreasonably withheld." (Ex. 1, § 2.6.)

30. The Federal Circuit confirmed that the Patent Transfer Agreement gave Lone Star constitutional standing to bring this suit. *Lone Star Silicon Innovations LLC*, 925 F.3d 1225 at 1235. As such, Lone Star holds the status of an exclusive licensee of the Patents in Suit for the purpose of standing and has standing to bring this action against the Nanya Defendants with AMD joined as a co-plaintiff. As the transferor of substantial exclusionary rights in the Patents in Suit to Lone Star and the holder of a contractual financial interest in the damages relief sought herein and of other contractual warranties and covenants extended by Lone Star, AMD has been joined to assure that principles of prudential standing are satisfied to enable Lone Star to secure the relief sought herein. As alleged above, AMD must be joined

as a co-party because such joinder is feasible.

3

### THE NANYA DEFENDANTS' INFRINGING PRODUCTS AND METHODS

4 31. The Nanya Defendants make, use, sell, offer for sale and/or import into the United States 5 DRAM memory semiconductor devices and products incorporating these devices. These products are 6 high-density, random access memory devices that provide high-speed data storage and retrieval. The 7 Nanya Defendants' DRAM memory devices include computing DRAM products, consumer DRAM 8 products, mobile RAM products, and Elixir Notebook or Desktop memory cards. The devices are provided 9 as wafers and chips, and are integrated as components of personal computer memories, mobile device 10 memories, networking devices, servers, digital home appliances, consumer electronics, communications 11 equipment, computer peripherals, automotive systems and other applications. The Nanya Defendants' LPDDR products offer lower power consumption relative to other DRAM products and are used in mobile 12 13 phones, tablets, embedded applications, ultra-thin laptop computers and other mobile consumer devices 14 that require low power consumption. Despite not having a license to the '330 or '061 patents, the Nanya 15 Defendants DRAM memory products adopt the designs claimed in these patents.

16

### FIRST CAUSE OF ACTION – INFRINGEMENT OF THE '061 PATENT

17 32. Plaintiff hereby repeats and re-alleges the allegations contained in paragraphs 1 to 31, as if

18 fully set forth herein.

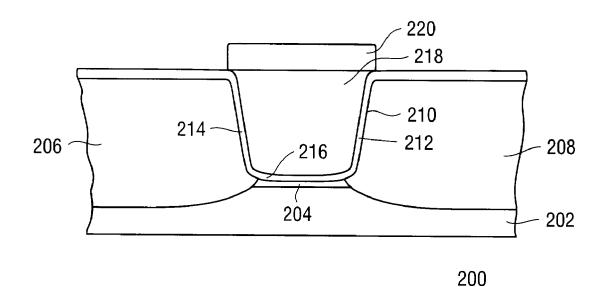

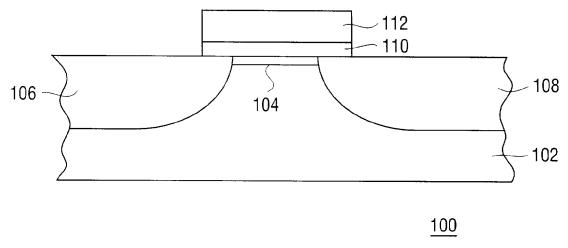

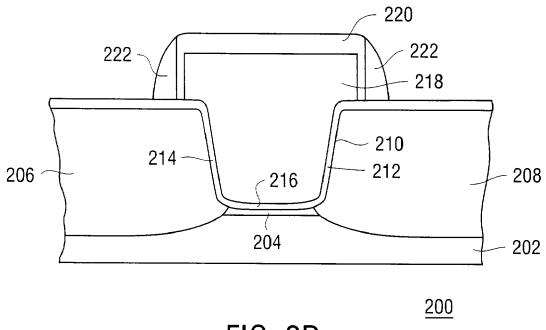

19 33. The Nanya Defendants, directly and/or through their subsidiaries, affiliates, agents, and/or 20 business partners, have in the past and continue to directly infringe the '061 patent pursuant to 35 U.S.C. 21 § 271(a) by making, using, selling, offering to sell and/or importing DRAM memory semiconductor 22 devices that embody the inventions claimed in the '061 patent, within the United States and within this 23 District, including at least claims 1, 3, 4, 11, 13 and 14. In violation of the '061 patent, Nanya Defendants' 24 accused DRAM memory devices include: (a) a semiconductor substrate of a first conductivity type; (b) a 25 source region of a second conductivity type in the semiconductor substrate; (c) a drain region of the second 26 conductivity type spaced from the source region in the semiconductor substrate; (d) a trench having 27 substantially upright vertical surfaces and a bottom surface formed in the semiconductor substrate 28 intermediate the source and drain regions; (e) a channel region formed in the semiconductor substrate and

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 12 of 85

forming a contiguous region beneath the bottom surface of the trench and immediately contiguous to the

source and drain regions; (f) a trench-to-gate insulating layer formed on the substantially upright vertical

surfaces and the bottom surface inside the trench and forming a contiguous layer inside the trench; and

(g) a trenched gate electrode having a top surface and formed on the trench-to-gate insulating layer inside

the trench.

6 34. The Nanya Defendants have been and are engaged in one or more of these direct infringing activities related to their DRAM memory semiconductor devices, including at least their computing 7 8 DRAM products (e.g., part numbers beginning in "NT256," "NT512," "NT1G," "NT2G," "NT4G," 9 "NT8G," "NT16T," "NT32T"), including DDR2 SDRAM and DDR3 SDRAM; consumer DRAM 10 products (e.g., part numbers beginning in "NT5"), including any of the DDR, DDR2, DDR3, DDR4 chips 11 configured in Commercial Grade, Industrial Grade, or Automotive Grade; mobile RAM products (e.g., 12 part numbers beginning in "NT6"), including any of the Mobile LPSDR, Mobile LPDDR, Mobile 13 LPDDR2, Mobile LPDDR3 chips; and Elixir Notebook or Desktop memory cards, including DDR3 14 SDRAM SODIMM (e.g., products with part numbers beginning with M2S4G64C or M2S8G64C), DDR3 15 SDRAM Unbuffered DIMM (e.g., products with part numbers beginning with M2F4G64C, M2X4G64C, 16 M2F8G64C, M2X8G64C); and any other DRAM memory devices of substantially similar design ("the 17 '061 Accused DRAM Products").

18 35. The Nanya Defendants, directly and/or through their subsidiaries, affiliates, agents, and/or 19 business partners, have been and are now indirectly infringing the '061 patent under 35 U.S.C. § 271(b) 20 by actively inducing acts of direct infringement performed by others, including at least claims 1, 3, 4, 11, 21 13 and 14. The Nanya Defendants have actual notice of the '061 patent and the infringement alleged herein 22 at least upon the service of the original Complaint in this action. Upon information and belief, the Nanya 23 Defendants have numerous lawyers and other active agents of the Nanya Defendants and of their owned and controlled subsidiaries who regularly review patents and published patent applications relevant to 24 25 technology in the fields of the Patents in Suit, specifically including patents directed to semiconductor 26 memory devices issued to competitors such as AMD, the original assignee of the '061 patent. Upon 27 information and belief, Nanya itself has been issued over 500 patents, including dozens of patents 28 prosecuted in the USPTO in the same classifications as the '061 patent, giving the Nanya Defendants

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 13 of 85

intimate knowledge of the art in fields relevant to this civil action. The timing, circumstances and extent

of the Nanya Defendants' obtaining actual knowledge of the '061 patent prior to the commencement of

this lawsuit will be confirmed during discovery.

36. Upon gaining knowledge of the '061 patent, it was, or became, apparent to the Nanya

Defendants that the manufacture, sale, importing, offer for sale, and use of their '061 Accused DRAM

Products result in infringement of the '061 patent. Upon information and belief, the Nanya Defendants

have continued and will continue to engage in activities constituting inducement of infringement,

notwithstanding their knowledge, or willful blindness thereto, that the activities they induce result in

infringement of the '061 patent.

10 37. The '061 Accused DRAM Products are intended for integration into products known to be 11 sold widely in the United States. The Nanya Defendants make DRAM semiconductor devices that embody 12 the inventions claimed in the '061 patent, and those devices infringe when they are imported into, or sold, 13 used, or offered for sale in, the United States. The Nanya Defendants indirectly infringe by inducing 14 customers (such as makers of mobile devices, desktop computers and other devices that use DRAM 15 memory) to import products that integrate DRAM semiconductor devices embodying inventions claimed 16 in the '061 patent, or to sell or use such products, or offer them for sale, in the United States. For example, 17 the Nanya Defendants induce third-party manufacturers, OEMs, importers, resellers, and other customers 18 who purchase devices manufactured at the Nanya Defendants' overseas facilities, or supplied under 19 agreements with partner foundries, to import devices embodying inventions claimed in the '061 patent, or 20 to sell or use such devices, or offer them for sale in the United States without authority.

21 38. The Nanya Defendants encourage customers, resellers, OEMs, or others to import into the 22 United States and sell and use in the United States the '061 Accused DRAM Products embodying 23 inventions claimed in the '061 patent with knowledge and the specific intent to cause the acts of direct 24 infringement performed by these third parties. On information and belief, after the Nanya Defendants 25 obtained knowledge of the '061 patent, the '061 Accused DRAM Products have been and will continue 26 to be imported into the United States and sold in large volumes by them and by others, such as customers, 27 distributors and resellers. The Nanya Defendants are aware that the '061 Accused DRAM Products are 28 integral components of the computer and mobile products incorporating them, that the infringing DRAM

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 14 of 85

Products are built into the computer and other products, and cannot be removed or disabled by a purchaser of the consumer products containing the infringing DRAM memory devices, such that the Nanya Defendants' customers will infringe one or more claims of the '061 patent by incorporating such DRAM semiconductor devices in other products, and that subsequent importation, sale, and use of such products in the United States would be a direct infringement of the '061 patent. Therefore, the Nanya Defendants are aware that their customers will infringe one or more claims of the '061 patent by selling, offering for sale, importing, and/or using the products as-sold and as-marketed by the Nanya Defendants.

8 39. The Nanya Defendants directly benefit from and actively and knowingly encourage 9 customers, resellers, and users' importation of these products into the United States and sale and use within 10 the United States. The Nanya Defendants actively encourage customers and downstream users, OEMs, 11 and resellers to import, use, and sell in the United States the '061 Accused DRAM Products that they 12 manufacture and supply, including through advertising, marketing, and sales activities directed at United 13 States sales. On information and belief, the Nanya Defendants are aware of the size and importance of the 14 United States market for customers of the Nanya Defendants' products, and also distribute or supply these 15 products intended for importation, use, and sale in the United States. The Nanya Defendants routinely 16 market their infringing DRAM memory products to third parties for inclusion in products that are sold to 17 customers in the United States, as well as directly to end user customers. Nanya has publicly stated that 18 its DRAM products are primarily targeted for desktop computers, tablet computers, mobile phones, 19 networking devices, servers, and other products, all of which are widely sold and used in the United States. 20 The Nanya Defendants have numerous direct sales, distributors, and reseller outlets for these products in 21 the United States. The Nanya Defendants' marketing efforts show that they have specifically intended to 22 and have induced direct infringement in the United States.

40. The Nanya Defendants also provide OEMs, manufacturers, importers, resellers, customers,

and end users with instructions, user guides, and technical specifications on how to incorporate the '061

Accused DRAM Products into electronics products that are made, used, sold, offered for sale in, and/or

imported into the United States. When OEMs, manufacturers, importers, resellers, customers, and end

users follow such instructions, user guides, and technical specifications and embed the Nanya Defendants'

products in end products and make, use, offer to sell, sell, or import into the United States, they directly

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 15 of 85

infringe one or more claims of the '061 patent. The Nanya Defendants know that by providing such 1 2 instructions, user guides, and technical specifications, OEMs, manufacturers, importers, resellers, 3 customers, and end users follow them, and therefore directly infringe one or more claims of the '061 4 patent. The Nanya Defendants thus know that their actions actively induce infringement.

5 41. The Nanya Defendants have engaged and will continue to engage in additional activities 6 to specifically target the United States market for the '061 Accused DRAM Products and actively induce 7 OEMs, manufacturers, importers, resellers, customers, and end users to directly infringe one or more 8 claims of the '061 patent in the United States. For example, the Nanya Defendants have set up a global 9 sales network that includes the United States to encourage various OEMs, manufacturers, importers, 10 resellers, customers, and end users to include their infringing technology in their computers, mobile 11 devices, removable storage devices and other products. Defendant Nanya USA is responsible for the 12 Nanya Defendants' sales and marketing activities in the United States.

13 42. The Nanya Defendants derive significant revenue by selling the '061 Accused DRAM 14 Products to third parties who directly infringe the '061 patent in the United States. The Nanya Defendants' 15 extensive sales and marketing efforts, sales volume, and partnerships all evidence their intent to induce 16 companies to infringe one or more claims of the'061 patent by using, offering to sell, selling, or importing 17 products that incorporate the '061 Accused DRAM Products, in the United States. The Nanya Defendants 18 have had specific intent to induce infringement or have been willfully blind to the direct infringement they 19 are inducing.

20 43. Upon information and belief, the Nanya Defendants have continued and will continue to 21 engage in activities constituting contributory infringement of the '061 patent under 35 U.S.C. § 271(c), 22 including at least claims 1, 3, 4, 11, 13 and 14. The Nanya Defendants contributorily infringe with 23 knowledge that the '061 Accused DRAM Products, or the use thereof, infringe the '061 patent. The Nanya 24 Defendants knowingly and intentionally contributed to the direct infringement of the '061 patent by others, 25 by supplying these DRAM memory chipset products that embody a material part of the claimed invention 26 of the '061 patent, and that are known by the Nanya Defendants to be specially made or adapted for use 27 in an infringing manner. For example, and without limitation, the '061 Accused DRAM Products are used 28 in end products, including computers, laptops, tablets, and mobile telephones. The '061 Accused DRAM FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 16 of 85

1 Products are not staple articles or commodities of commerce suitable for non-infringing use and are 2 especially made for or adapted for use in infringing the '061 patent. There are no substantial uses of the 3 '061 Accused DRAM Products that do not infringe the '061 patent. By contributing a material part of the 4 infringing computing products sold, offered for sale, imported and used by their customers, resellers and 5 users, the Nanya Defendants have been and are now indirectly infringing the '061 patent under 35 U.S.C. 6 § 271(c).

7 44. The Nanya Defendants' direct and indirect infringement of the '061 patent has injured Lone 8 Star, and Lone Star is entitled to recover damages adequate to compensate for such infringement pursuant 9 to 35 U.S.C. § 284. Unless they cease their infringing activities, the Nanya Defendants will continue to 10 injure Lone Star by infringing the '061 patent.

11 45. On information and belief, The Nanya Defendants acted egregiously and with willful 12 misconduct in that their actions constituted direct or indirect infringement of a valid patent, and this was 13 either known or so obvious that the Nanya Defendants should have known about it. The Nanya Defendants 14 continue to infringe the '061 patent by making, using, selling, offering for sale and importing in the United 15 States the '061 Accused DRAM Products and to induce the direct infringement of others performing these 16 acts, or they have acted at least in reckless disregard of Lone Star's patent rights. On information and 17 belief, the Nanya Defendants will continue their infringement notwithstanding actual knowledge of the 18 '061 patent and without a good faith basis to believe that their activities do not infringe any valid claim of 19 the '061 patent. All infringement of the '061 patent following the Nanya Defendants' knowledge of the 20 '061 patent is willful and Lone Star is entitled to treble damages and attorneys' fees and costs incurred in 21 this action under 35 U.S.C. §§ 284 and 285.

- 22

### SECOND CAUSE OF ACTION – INFRINGEMENT OF THE '330 PATENT

23 46. Plaintiff hereby repeats and re-alleges the allegations contained in paragraphs 1 to 31, as if 24 fully set forth herein.

25 47. The Nanya Defendants, directly and/or through their subsidiaries, affiliates, agents, and/or 26 business partners, have in the past and continue to directly infringe the '330 patent pursuant to 35 U.S.C. 27 § 271(a) by making, using, selling, offering to sell and/or importing DRAM memory semiconductor 28 devices that embody the inventions claimed in the '330 patent, within the United States and within this FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT

CASE NO. 3:17-cv-04032-WHA

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 17 of 85

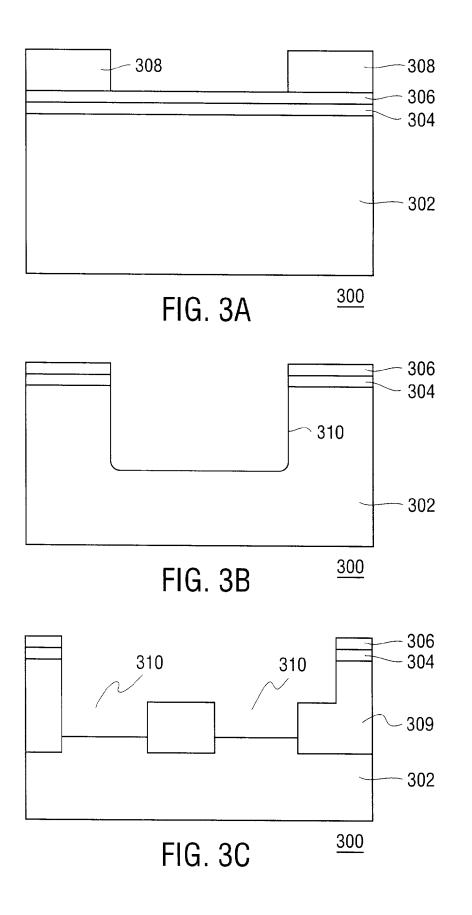

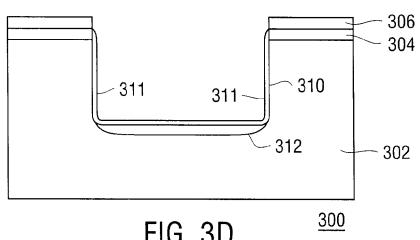

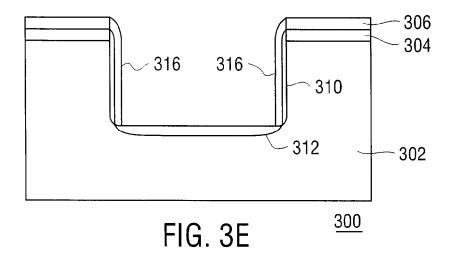

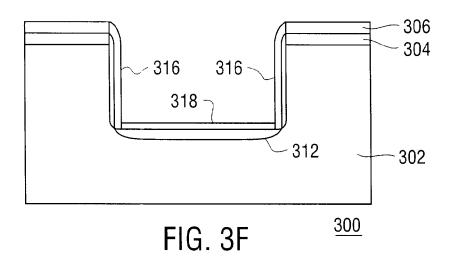

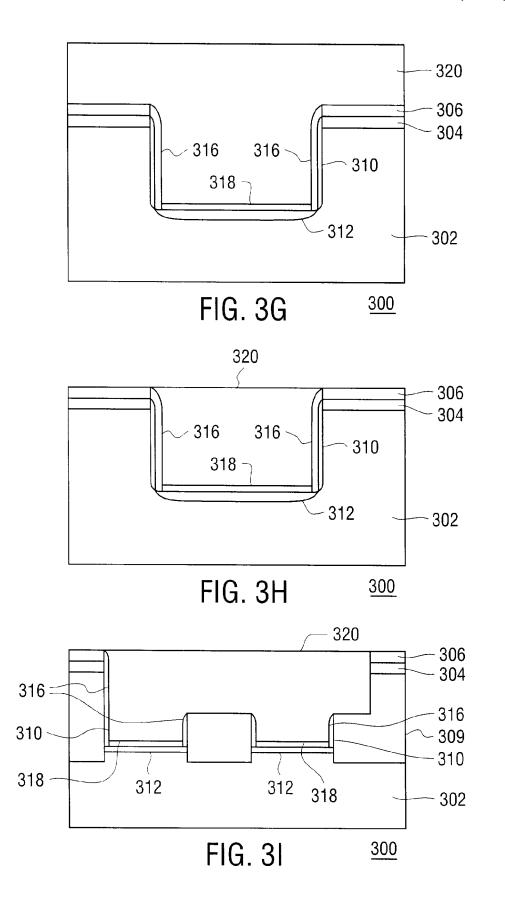

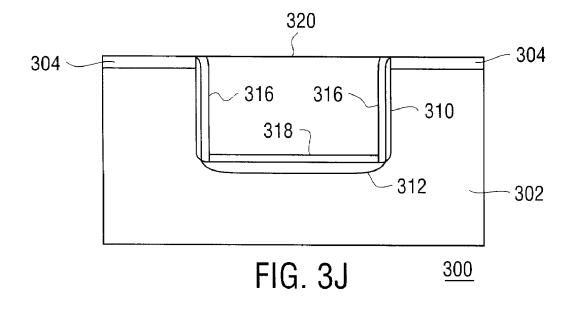

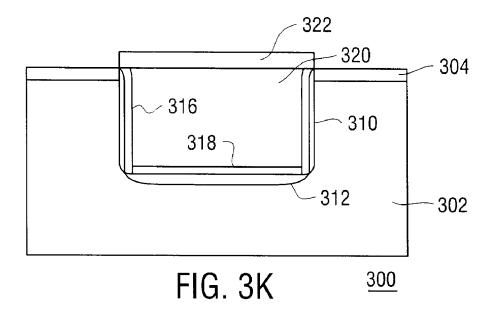

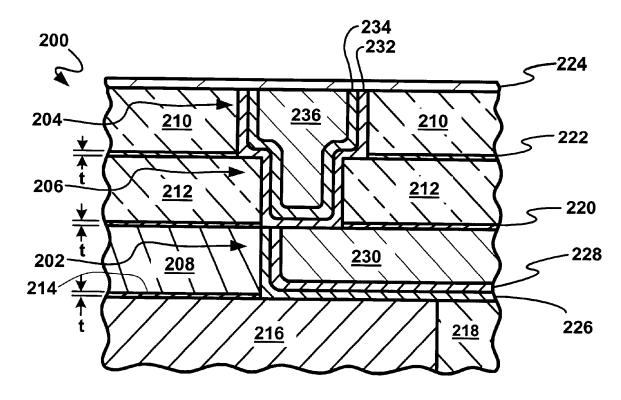

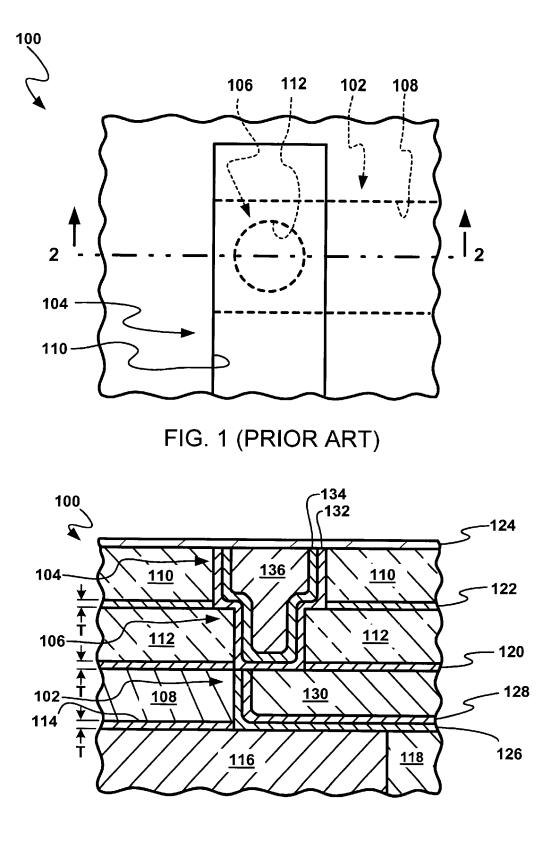

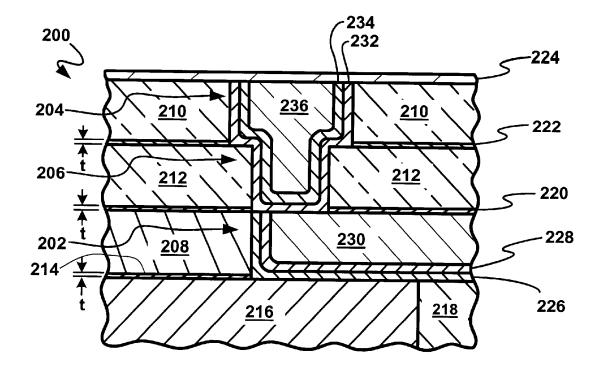

1 District, including at least claim 2. In violation of the '330 patent, the Nanya Defendants' accused DRAM 2 memory devices include: (a) a semiconductor substrate having a semiconductor device provided thereon; 3 (b) a first dielectric layer formed over the semiconductor substrate having a first opening; (c) a first 4 conductor core filling the first opening and connected to the semiconductor device; (d) an etch stop layer 5 of silicon nitride formed over the first dielectric layer and the first conductor core, the etch stop layer 6 having a dielectric constant below 5.5; (e) a second dielectric layer formed over the etch stop layer and 7 having a second opening open to the first conductor core; and (f) a second conductor core filling the second 8 opening and connected to the first conductor core. The Nanya Defendants further directly infringe the 9 '330 patent because, for example, their DRAM memory devices include: (g) an etch stop layer that is a 10 multilayer structure.

11 48. The Nanya Defendants have been and are engaged in one or more of these direct infringing 12 activities related to their DRAM memory semiconductor devices, including at least their computing 13 DRAM products (e.g., part numbers beginning in "NT256," "NT512," "NT1G," "NT2G," "NT4G," 14 "NT8G," "NT16T," "NT32T"), including DDR2 SDRAM and DDR3 SDRAM; consumer DRAM 15 products (e.g., part numbers beginning in "NT5"), including any of the DDR, DDR2, DDR3, DDR4 chips 16 configured in Commercial Grade, Industrial Grade, or Automotive Grade; mobile RAM products (e.g., 17 part numbers beginning in "NT6"), including any of the Mobile LPSDR, Mobile LPDDR, Mobile 18 LPDDR2, Mobile LPDDR3 chips; and Elixir Notebook or Desktop memory cards, including DDR3 19 SDRAM SODIMM (e.g., products with part numbers beginning with M2S4G64C or M2S8G64C), DDR3 20 SDRAM Unbuffered DIMM (e.g., products with part numbers beginning with M2F4G64C, M2X4G64C, 21 M2F8G64C, M2X8G64C); and any other DRAM memory devices of substantially similar design ("the 22 '330 Accused DRAM Products").

49. The Nanya Defendants, directly and/or through their subsidiaries, affiliates, agents, and/or

business partners, have been and are now indirectly infringing the '330 patent under 35 U.S.C. § 271(b)

by actively inducing acts of direct infringement performed by others. The Nanya Defendants have actual

notice of the '330 patent and the infringement alleged herein at least upon the service of the original

Complaint in this action, including at least claim 2. Upon information and belief, the Nanya Defendants

have numerous lawyers and other active agents of the Nanya Defendants and of their owned and controlled

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 18 of 85

subsidiaries who regularly review patents and published patent applications relevant to technology in the 1 2 fields of the Patents in Suit, specifically including patents directed to semiconductor memory devices 3 issued to competitors such as AMD, the original assignee of the '330 patent. Upon information and belief, 4 Nanya itself has been issued over 500 patents, including over a dozen patents prosecuted in the USPTO 5 in the same classifications as the '330 patent, giving the Nanya Defendants intimate knowledge of the art 6 in fields relevant to this civil action. The timing, circumstances and extent of the Nanya Defendants' 7 obtaining actual knowledge of the '330 patent prior to the commencement of this lawsuit will be confirmed 8 during discovery.

9 50. Upon gaining knowledge of the '330 patent, it was, or became, apparent to the Nanya

10 Defendants that the manufacture, sale, importing, offer for sale, and use of their '330 Accused DRAM

11 Products result in infringement of the '330 patent. Upon information and belief, the Nanya Defendants

12 have continued and will continue to engage in activities constituting inducement of infringement,

13 notwithstanding their knowledge, or willful blindness thereto, that the activities they induce result in

14 infringement of the '330 patent under 35 U.S.C. § 271(b).

15 51. The '330 Accused DRAM Products are intended for integration into products known to be 16 sold widely in the United States. The Nanya Defendants and their subsidiaries make DRAM 17 semiconductor devices that embody the inventions claimed in the '330 patent, and those devices infringe when they are imported into, or sold, used, or offered for sale in, the United States. The Nanya Defendants 18 19 indirectly infringe by inducing customers (such as makers of mobile devices, desktop computers and other 20 devices that use DRAM memory) to import products that integrate DRAM semiconductor devices 21 embodying inventions claimed in the '330 patent, or to sell or use such products, or offer them for sale, in 22 the United States. For example, the Nanya Defendants induce third-party manufacturers, original 23 equipment manufacturers (OEMs), importers, resellers, and other customers who purchase devices manufactured at Nanya's overseas facilities, or supplied under agreements with partner foundries, to 24 25 import devices embodying inventions claimed in the '330 patent, or to sell or use such devices, or offer 26 them for sale in the United States without authority.

52. The Nanya Defendants encourage customers, resellers, OEMs, or others to import into the

United States and sell and use in the United States the '330 Accused DRAM Products embodying

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 19 of 85

1 inventions claimed in the '330 patent with knowledge and the specific intent to cause the acts of direct 2 infringement performed by these third parties. On information and belief, after the Nanya Defendants 3 obtained knowledge of the '330 patent, the '330 Accused DRAM Products have been and will continue to be imported into the United States and sold in large volumes by them and by others, such as customers, 4 5 distributors and resellers. The Nanya Defendants are aware that the '330 Accused DRAM Products are 6 integral components of the computer and mobile products incorporating them, that the infringing DRAM 7 Products are built into the computer and other products, and cannot be removed or disabled by a purchaser 8 of the consumer products containing the infringing DRAM memory devices, such that the Nanya 9 Defendants' customers will infringe the asserted claim of the '330 patent by incorporating such DRAM 10 semiconductor devices in other products, and that subsequent importation, sale and use of such products 11 in the United States would be a direct infringement of the '330 patent. Therefore, the Nanya Defendants are aware that their customers will infringe the asserted claim of the '330 patent by selling, offering for 12 13 sale, importing and/or using the products as-sold and as-marketed by the Nanya Defendants.

14 53. The Nanya Defendants directly benefit from and actively and knowingly encourage 15 customers, resellers, and users' importation of these products into the United States and sale and use within 16 the United States. The Nanya Defendants actively encourage customers and downstream users, OEMs, 17 and resellers to import, use, and sell in the United States the '330 Accused DRAM Products that they 18 manufacture and supply, including through advertising, marketing, and sales activities directed at United 19 States sales. On information and belief, the Nanya Defendants are aware of the size and importance of the 20 United States market for customers of the Nanya Defendants' products, and also distribute or supply these 21 products intended for importation, use, and sale in the United States. Defendants routinely market their 22 infringing DRAM memory products to third parties for inclusion in products that are sold to customers in 23 the United States, as well as directly to end-user customers. The Nanya Defendants have publicly stated 24 that its DRAM products are primarily targeted for desktop computers, tablet computers, mobile phones, 25 networking devices, servers, and other products, all of which are widely sold and used in the United States. 26 The Nanya Defendants have numerous direct sales, distributors, and reseller outlets for these products in 27 the United States. The Nanya Defendants' marketing efforts show that they have specifically intended to 28 and have induced direct infringement in the United States.

1 54. The Nanya Defendants also provide OEMs, manufacturers, importers, resellers, customers, 2 and end users with instructions, user guides, and technical specifications on how to incorporate the '330 3 Accused DRAM Products into electronics products that are made, used, sold, offered for sale in, and/or 4 imported into the United States. When OEMs, manufacturers, importers, resellers, customers, and end 5 users follow such instructions, user guides, and technical specifications and embed the Nanya Defendants' 6 products in end products and make, use, offer to sell, sell, or import into the United States, they directly 7 infringe the asserted claim of the '330 patent. The Nanya Defendants know that by providing such 8 instructions, user guides, and technical specifications, OEMs, manufacturers, importers, resellers, 9 customers, and end users will follow them, and therefore directly infringe the asserted claim of the '330 10 patent. The Nanya Defendants thus know that their actions actively induce infringement.

11 55. The Nanya Defendants have engaged and will continue to engage in additional activities to specifically target the United States market for the '330 Accused DRAM Products and actively induce 12 13 OEMs, manufacturers, importers, resellers, customers, and end users to directly infringe the asserted claim 14 of the'330 patent in the United States. For example, the Nanya Defendants have set up a global sales 15 network that includes the United States to encourage various OEMs, manufacturers, importers, resellers, 16 customers, and end users to include their infringing technology in their computers, mobile devices, 17 removable storage devices, and other products. Defendant Nanya USA is responsible for the Nanya 18 Defendants' sales and marketing activities in the United States.

19 56. The Nanya Defendants derive significant revenue by selling the '330 Accused DRAM 20 Products to third parties who directly infringe the '330 patent in the United States. The Nanya Defendants' 21 extensive sales and marketing efforts, sales volume, and partnerships all evidence their intent to induce 22 companies to infringe the asserted claim of the '330 patent by, using, offering to sell, selling, or importing 23 products that incorporate the '330 Accused DRAM Products, in the United States. The Nanya Defendants have had specific intent to induce infringement or have been willfully blind to the direct infringement they 24 25 are inducing.

26 57. Upon information and belief, the Nanya Defendants have continued and will continue to 27 engage in activities constituting contributory infringement of the '330 patent under 35 U.S.C. § 271(c), 28 including at least claim 2. The Nanya Defendants contributorily infringe with knowledge that the '330 FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT 19 CASE NO. 3:17-cv-04032-WHA

### Case 3:17-cv-04032-WHA Document 117 Filed 09/19/19 Page 21 of 85

1 Accused DRAM Products, or the use thereof, infringe the '330 patent. The Nanya Defendants knowingly 2 and intentionally contributed to the direct infringement of the '330 patent by others, by supplying these 3 DRAM memory chipset products, that embody a material part of the claimed invention of the '330 patent, 4 that are known by the Nanya Defendants to be specially made or adapted for use in an infringing manner. 5 For example, and without limitation, the '330 Accused DRAM Products are used in end products, 6 including computers, laptops, tablets and mobile telephones. The '330 Accused DRAM Products are not 7 staple articles or commodities of commerce suitable for non-infringing use and are especially made for or 8 adapted for use in infringing the '330 patent. There are no substantial uses of the '330 Accused DRAM 9 Products that do not infringe the '330 patent. By contributing a material part of the infringing computing 10 products sold, offered for sale, imported and used by their customers, resellers and users, the Nanya 11 Defendants have been and are now indirectly infringing the '330 patent under 35 U.S.C. § 271(c).

12 58. The Nanya Defendants' direct and indirect infringement of the '330 patent has injured Lone

13 Star, and Lone Star is entitled to recover damages adequate to compensate for such infringement pursuant

14 to 35 U.S.C. § 284. Unless they cease their infringing activities, The Nanya Defendants will continue to

15 injure Lone Star by infringing the '330 patent.

16 59. On information and belief, the Nanya Defendants acted egregiously and with willful 17 misconduct in that their actions constituted direct or indirect infringement of a valid patent, and this was 18 either known or so obvious that the Nanya Defendants should have known about it. The Nanya Defendants 19 continue to infringe the '330 patent by making, using, selling, offering for sale and importing in the United 20 States the '330 Accused DRAM Products and to induce the direct infringement of others performing these 21 acts, or they have acted at least in reckless disregard of Lone Star's patent rights. On information and 22 belief, the Nanya Defendants will continue their infringement notwithstanding actual knowledge of the 23 '330 patent and without a good faith basis to believe that its activities do not infringe any valid claim of 24 the '330 patent. All infringement of the '330 patent following the Nanya Defendants' knowledge of the 25 '330 patent is willful and Lone Star is entitled to treble damages and attorneys' fees and costs incurred in 26 this action under 35 U.S.C. §§ 284 and 285.

- 27

- 28

|    | Case 3:17-cv-04032-WHA Document 117                                                                    | Filed 09/19/19 Page 22 of 85                                                                               |  |  |  |  |  |

|----|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1  | PRAYER FOR RELIEF                                                                                      |                                                                                                            |  |  |  |  |  |

| 2  |                                                                                                        |                                                                                                            |  |  |  |  |  |

| 3  | 1. Judgment that the '061, and '330 patents are each valid and enforceable;                            |                                                                                                            |  |  |  |  |  |

| 4  | 2. Judgment that the '061, and '330 patents are infringed by the Nanya Defendants;                     |                                                                                                            |  |  |  |  |  |

| 5  | 3. Judgment that the Nanya Defendants' acts of patent infringement relating to the patents are         |                                                                                                            |  |  |  |  |  |

| 6  | willful;                                                                                               |                                                                                                            |  |  |  |  |  |

| 7  | 4. An award of damages arising out of the Nanya Defendants' acts of patent infringement,               |                                                                                                            |  |  |  |  |  |

| 8  | together with pre-judgment and post-judgment interest;                                                 |                                                                                                            |  |  |  |  |  |

| 9  | 5. Judgment that the damages so adjudged be trebled in accordance with 35 U.S.C. § 284;                |                                                                                                            |  |  |  |  |  |

| 10 | 6. An award of Plaintiff's attorneys' fees, costs and expenses incurred in this action in              |                                                                                                            |  |  |  |  |  |

| 11 | accordance with 35 U.S.C. § 285; and                                                                   |                                                                                                            |  |  |  |  |  |

| 12 | 7. Such other and further relief as the Court may deem just and proper.                                |                                                                                                            |  |  |  |  |  |

| 13 | RESERVATION OF RIGHTS                                                                                  |                                                                                                            |  |  |  |  |  |

| 14 | Plaintiff's investigation is ongoing, and certain material information remains in the sole possession  |                                                                                                            |  |  |  |  |  |

| 15 | of Nanya Defendants or third parties, which will be obtained via discovery herein. Plaintiff expressly |                                                                                                            |  |  |  |  |  |

| 16 | 6 reserves the right to amend or supplement the causes of a                                            | reserves the right to amend or supplement the causes of action set forth herein in accordance with Rule 15 |  |  |  |  |  |

| 17 | 7 of the Federal Rules of Civil Procedure.                                                             | of the Federal Rules of Civil Procedure.                                                                   |  |  |  |  |  |

| 18 | 8                                                                                                      |                                                                                                            |  |  |  |  |  |

| 19 | 9                                                                                                      | Respectfully,                                                                                              |  |  |  |  |  |

| 20 | Dated: September 19, 2019                                                                              | FITCH, EVEN, TABIN & FLANNERY LLP                                                                          |  |  |  |  |  |

| 21 | 21                                                                                                     | /s/ Joseph F. Marinelli                                                                                    |  |  |  |  |  |

| 22 | 22                                                                                                     | Joseph F. Marinelli (admitted pro hac vice)                                                                |  |  |  |  |  |

| 23 | 23                                                                                                     | <i>Attorney for Plaintiff</i><br>LONE STAR SILICON INNOVATIONS LLC                                         |  |  |  |  |  |

| 24 | 24                                                                                                     | LONE STAR SILICON INNO VATIONS LLC                                                                         |  |  |  |  |  |

| 25 | JURY DEMAND                                                                                            |                                                                                                            |  |  |  |  |  |

| 26 | Plaintiff demands trial by jury of all issues triable of right by a jury.                              |                                                                                                            |  |  |  |  |  |

| 27 |                                                                                                        |                                                                                                            |  |  |  |  |  |

| 28 |                                                                                                        |                                                                                                            |  |  |  |  |  |

|    | FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT                                                        | г 21                                                                                                       |  |  |  |  |  |

CASE NO. 3:17-cv-04032-WHA

l

|          | Case 3:17-cv-04032-WHA D                                        | Oocument 117   | Filed 09/19/19                             | Page 23 of 85                                          |     |

|----------|-----------------------------------------------------------------|----------------|--------------------------------------------|--------------------------------------------------------|-----|

| 1        | Detech Sentember 10, 2010                                       |                | Respectfully su                            |                                                        | τD  |

| 2<br>3   | Dated: September 19, 2019                                       |                |                                            | TABIN & FLANNERY L                                     |     |

| 3<br>4   |                                                                 |                | <u>/s/ Joseph F. Ma</u><br>Joseph F. Marir | <i>arinelli</i><br>nelli (admitted <i>pro hac vice</i> | )   |

| 5        |                                                                 |                | Attorney for Pla                           | uintiff                                                |     |

| 6        |                                                                 |                | LONE STAR S                                | ILICON INNOVATIONS I                                   | LLC |

| 7        |                                                                 |                |                                            |                                                        |     |

| 8        |                                                                 |                |                                            |                                                        |     |

| 9        |                                                                 |                |                                            |                                                        |     |

| 10       |                                                                 |                |                                            |                                                        |     |

| 11       |                                                                 |                |                                            |                                                        |     |

| 12       |                                                                 |                |                                            |                                                        |     |

| 13       |                                                                 |                |                                            |                                                        |     |

| 14       |                                                                 |                |                                            |                                                        |     |

| 15       |                                                                 |                |                                            |                                                        |     |

| 16<br>17 |                                                                 |                |                                            |                                                        |     |

| 17       |                                                                 |                |                                            |                                                        |     |

| 10       |                                                                 |                |                                            |                                                        |     |

| 20       |                                                                 |                |                                            |                                                        |     |

| 21       |                                                                 |                |                                            |                                                        |     |

| 22       |                                                                 |                |                                            |                                                        |     |

| 23       |                                                                 |                |                                            |                                                        |     |

| 24       |                                                                 |                |                                            |                                                        |     |

| 25       |                                                                 |                |                                            |                                                        |     |

| 26       |                                                                 |                |                                            |                                                        |     |

| 27       |                                                                 |                |                                            |                                                        |     |

| 28       |                                                                 |                |                                            |                                                        |     |

|          | FIRST AMENDED COMPLAINT FOR PATEN<br>CASE NO. 3:17-cv-04032-WHA | NT INFRINGEMEN | Т                                          |                                                        | 22  |

# Exhibit 1

## AMD bank account information redacted pursuant to April 5, 2018 Order (Case No. 18-01680-WHA, D.I. 40)

### Confidential

### PATENT TRANSFER AGREEMENT

This PATENT TRANSFER AGREEMENT (this "Agreement") is entered into on August 4<sup>th</sup>, 2016 (the "Effective Date"), by and between Lone Star Silicon Innovations LLC, an entity organized under the laws of State of Texas having its primary place of business at 5204 Bluewater Drive, Frisco, TX 75034 . ("Lone Star") and Advanced Micro Devices, Inc., a Delaware corporation ("AMD"). Lone Star and AMD are herein referred to separately as "a party" or collectively as "the parties."

### RECITALS

Whereas Lone Star wishes to acquire certain patents and patent applications owned by AMD; and

Whereas AMD is interested in selling such certain patents and patent applications to Lone Star while retaining a license and certain sub-license rights to such patents and patent applications;

Now therefore, in consideration of the mutual covenants and conditions stated herein, and for other good and valuable consideration, the receipt and sufficiency of which is hereby acknowledged, the parties hereby agree as set forth herein.

### AGREEMENT

### 1. DEFINITIONS

"Affiliate" means, with respect to a Person, any Person Controlling, Controlled by, or under common Control with such Person. A Person shall be deemed an Affiliate only so long as such Control exists.

"Agreement" shall have the meaning set forth in the introduction.

"Alternate Forum" shall have the meaning set forth in Section 7.1.

"AMD" shall have the meaning set forth in the introduction.

"Assigned Patents" means and includes all patents listed in Exhibit A hereto. In addition, "Assigned Patents" also includes the following to the extent owned and assignable by AMD: (i) all patents and patent applications listed in Exhibit B hereto, (ii) applications for the foregoing in all countries of the world, and (iii) any other procedure or formality with respect to the aforesaid that can result in an enforceable patent right anywhere in the world.

"Assignment" shall have the meaning set forth in Section 2.1.

"Confidentiality and Common Interest Agreement" means an agreement, in the form set forth on Exhibit D, setting forth the terms under which Lone Star and AMD will seek to protect certain information relating to the Assigned Patents as confidential and/or under the common interest privilege.

"Control" means, with respect to a Person, (a) direct or indirect ownership of more than fifty percent (50%) of the outstanding shares representing the right to vote for members of the board of directors or other managing officers of such Person, or (b) for a Person that does not have outstanding shares, more

than fifty percent (50%) of the direct or indirect ownership interest representing the right to make decisions for such Person.

"Lone Star" shall have the meaning set forth in the introduction.

"Disclosure Schedule" shall refer to the schedule of Exhibit F hereto.

"Effective Date" shall have the meaning set forth in the introduction.

"Existing Encumbrances" means, in relation to the Assigned Patents, (a) pre-existing patent licenses, covenants not to assert, promises or agreements to license, and/or similar patent immunities; (b) rights to renew or extend pre-existing patent licenses exercised unilaterally by third parties (such as legally binding options); (c) releases for past infringement; and/or (d) pre-existing commitments related to AMD's or its Affiliates' standardization activities or patent pool activities, and other pre-existing specification-related or standards-related licenses, covenants and promises of AMD or any of its Affiliates, which, in each of (a), (b), (c) and (d), shall transfer in connection with the transfer of the Assigned Patent(s) and/or which AMD or any of its Affiliates has committed to maintain in connection with the transfer of such Assigned Patent(s).

"Former Affiliate" shall have the meaning set forth in Section 4.1(b)(i)

"Former Asset" shall have the meaning set forth in Section 4.1(b)(ii).

"Forum" shall have the meaning set forth in Section 7.1.

"Governmental Authority" means any governmental agency or authority of the United States, any domestic state or any foreign country, and any political subdivision or agency thereof, and includes any authority having governmental or quasi-governmental powers, including any administrative agency or commission.

"Grantee" shall have the meaning set forth in Section 4.1(a).

"Grantor" shall have the meaning set forth in Section 4.1(a).

"Knowledge" shall have the meaning set forth in Section 6.1.

"Law" or "law" means all laws, statutes, ordinances, regulations and similar mandates of any Governmental Authority having the effect of law in any jurisdiction, including any judgment, order, decision, writ, injunction, ruling or decree of, or any settlement under the jurisdiction of, any court or Governmental Authority having the effect of law in each such jurisdiction.