# IN THE UNITED STATES DISTRICT COURT FOR THE WESTERN DISTRICT OF TEXAS AUSTIN DIVISION

BELL SEMICONDUCTOR, LLC,

Plaintiff,

v.

NXP SEMICONDUCTORS, N.V.; NXP, B.V.; and NXP USA, INC.,

Civil Action No. 1:20-cv-00611-ADA

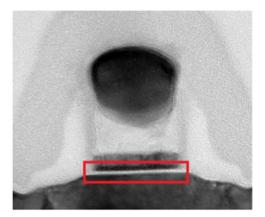

JURY TRIAL DEMANDED

Defendants.

# BELL SEMICONDUCTOR, LLC'S FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT

Plaintiff Bell Semiconductor, LLC ("Bell Semic") as and for its complaint against NXP Semiconductors, N.V.; NXP, B.V.; and NXP USA, Inc., alleges as follows:

# **INTRODUCTION**

1. Bell Semic is a technology and intellectual property licensing company. Bell Semic's patent portfolio comprises over 1,900 worldwide patents and applications, approximately 1,500 of which are active United States patents. This patent portfolio of semiconductor-related inventions was developed over many years by some of the world's leading semiconductor technology innovators, including AT&T Bell Laboratories, Lucent Technologies (Lucent), Agere Systems (Agere), LSI Logic and LSI Corporation (LSI). The portfolio reflects expertise developed at the various R&D laboratories and manufacturing locations of these companies around the world. The technology created, developed, and patented at those companies underlies many important innovations in the development of semiconductors and integrated circuits for high-tech products, including smartphones, computers, wearables,

### Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 2 of 133

digital signal processors, IoT devices, automobiles, broadband carrier access, switches, network processors and wireless connectors.

2. Bell Semic was formed in 2017 to manage this portfolio of semiconductor-related intellectual property acquired from Broadcom and assigned to Bell Semic. Several Bell Semic executives previously served as engineers and in leadership roles within the intellectual property departments of Lucent, Agere, LSI, Avago Technologies (Avago), and Broadcom. As a result, Bell Semic executives were personally involved in creating, patenting, and licensing various aspects of the portfolio even before Broadcom assigned it to Bell Semic, including:

- Bell Semic's Chief Executive Officer and Board Member, Mr. John Veschi, served as General Manager of the Intellectual Property business at LSI, had similar responsibilities at Agere, and began his in-house intellectual property experience with the formation of Lucent.

- Bell Semic's President and General Counsel, Mr. Chad Hilyard, served as Managing IP Counsel and in other roles at LSI and Agere, where he was involved in licensing many of the patents in the portfolio now assigned to Bell Semic;

- Bell Semic's Chief Technology Officer, Dr. Sailesh Merchant was a Fellow at Broadcom, Avago, and LSI Corporation; a Distinguished Engineer at LSI Corporation; and a Distinguished Member of the Technical Staff of Agere and Lucent. Dr. Merchant is also a Senior Member of the IEEE and an inventor on more than 250 worldwide patents including many of the patents in Bell Semic's portfolio—and three of the patents asserted in this Complaint;

- Bell Semic's Senior Director for IP, Mr. Kouros Azimi, served as Director of Intellectual Property at Avago/Broadcom; a Patent Engineer and Director of Patent Development at

### Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 3 of 133

LSI/Avago Technologies; and a Member of the Technical Staff at Agere, Lucent, and AT&T Bell Labs. Mr. Azimi is also a Senior Member of the IEEE.

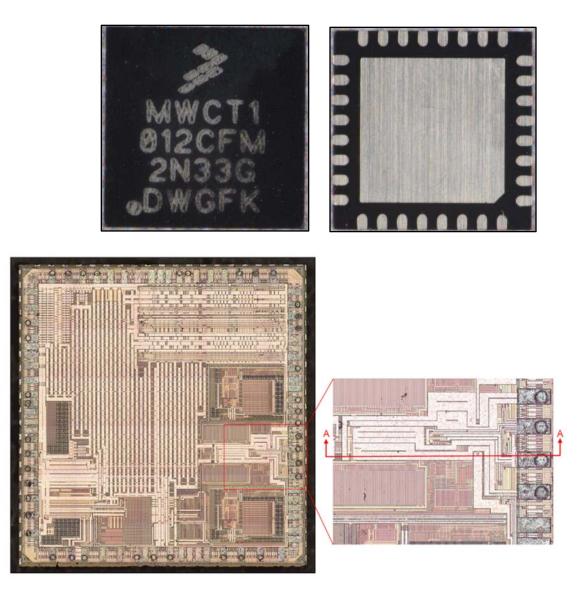

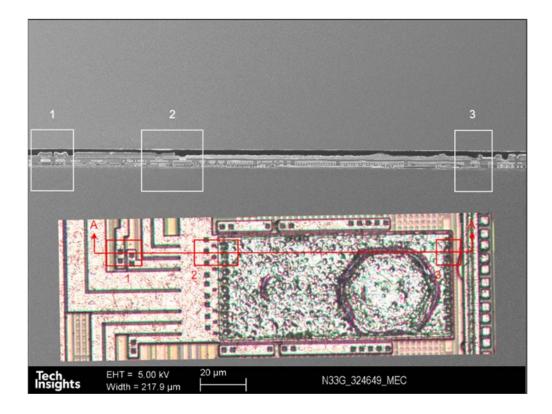

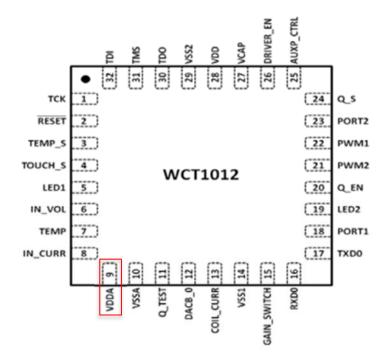

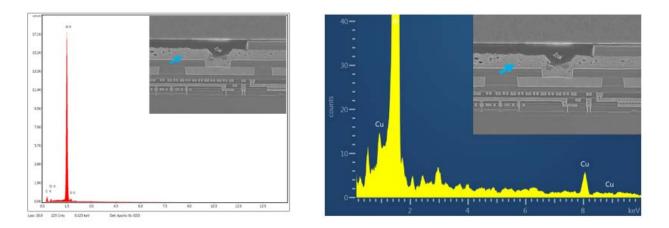

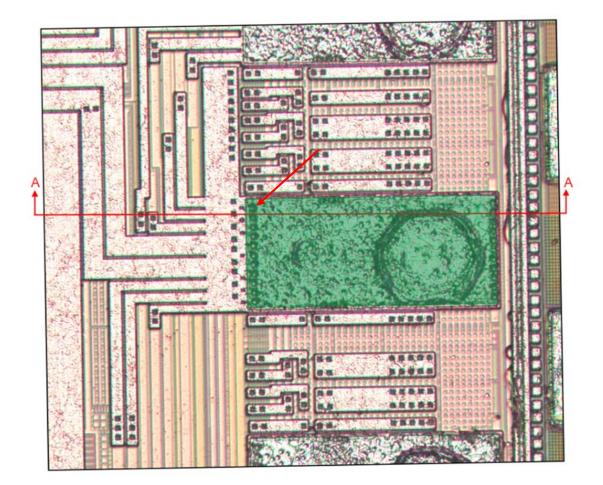

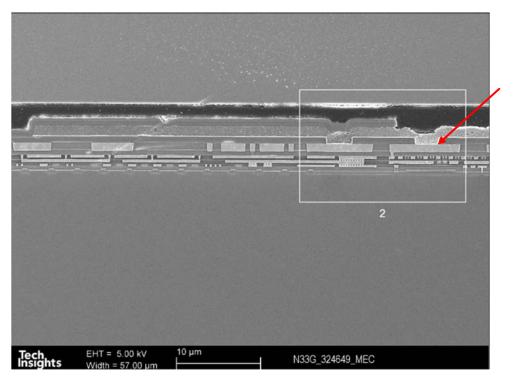

3. Defendants NXP Semiconductors, N.V. ("NXP NV"); NXP, B.V. ("NXP BV"); and NXP USA, Inc. ("NXP USA") (collectively, "NXP" or "Defendants") have infringed and continue to infringe Bell Semic's patents by making, using, selling, offering for sale, and/or importing products (including importing products made by a patented process) throughout the United States, including within this District. NXP's customers incorporate those products into downstream products that are made, used, sold, offered for sale, and/or imported throughout the United States and within this District. Such downstream products include, but are not limited to, the NXP 80V18 PN80V near field communications (NFC) controller used in the iPhone X; the NXP LS1088AXN7Q1A QorIQ Layerscape communications processor used in highperformance open virtual edge appliance platforms; and the NXP MWCT1012CFM wireless charging transmitter used in handheld consumer applications.

4. Bell Semic has notified NXP of its infringement in writing multiple times since January 2019 and provided detailed claim charts showing NXP's infringement of numerous Bell Semic patents by numerous different NXP semiconductor devices, but NXP has failed to provide a substantive response and has otherwise refused to have a meeting with Bell Semic to discuss licensing of the Bell Semic portfolio, including the infringed Bell Semic patents. Instead, NXP has continued to infringe, and thus its infringement is and has been willful under the Patent Act.

## NATURE OF THE CASE

5. This action arises under 35 U.S.C. § 271 for NXP's infringement of Bell Semic's United States Patent Nos. 8,049,340 ("the Hall 340 Patent"); 8,288,269 ("the Hall 269 Patent"); 7,566,964 ("the Kang Patent"); 6,281,129 ("the Merchant Patent"); 6,153,543 ("the Chesire Patent"); 6,743,669 ("the Lin Patent"); 6,544,907 ("the Ma Patent"); 6,342,734 ("the Allman

### Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 4 of 133

Patent"); 6,960,836 ("the Bachman Patent"); and 6,624,007 ("the Kobayakawa Patent") (collectively, Bell Semic's "Asserted Patents").

# **PARTIES**

6. Bell Semiconductor, LLC is a Delaware limited liability company with a place of business at One West Broad Street, Suite 901, Bethlehem, PA 18018.

7. On information and belief, NXP Semiconductors, N.V. ("NXP NV") is a Dutch public company with limited liability (nammloze vennootschap) organized under the laws of the Netherlands with a global headquarters at 60 High Tech Campus, Eindhoven, Netherlands, 5656 AG. NXP Semiconductors, N.V.'s only material assets are the direct ownership of 100% of the shares of NXP, B.V.

8. On information and belief, NXP, B.V. ("NXP BV") is a Dutch private company with limited liability (besloten vennootschap met beperkte aansprakelijkheid) organized under the laws of the Netherlands with a place of business at 60 High Tech Campus, Eindhoven, Netherlands, 5656 AG.

9. On information and belief, NXP USA, Inc. ("NXP USA") is a corporation organized under the laws of Delaware, with a principal place of business at 6501 William Cannon Drive West, Austin, TX 78735. NXP USA may be served with process through its registered agent Corporation Service Company d/b/a CSC - Lawyers Incorporating Service Company, 211 E. 7th Street, Suite 620, Austin, TX 78701-3218.

10. On information and belief, NXP USA was formerly known as Freescale Semiconductor, Inc. Upon NXP's merger with Freescale in 2016, Freescale Semiconductor, Inc. changed its name to NXP USA and became NXP NV's registered agent in the United States.

11. NXP is a global semiconductor company that designs, manufactures, and provides to the United States and other markets a wide variety of semiconductors that are used in a wide-

### Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 5 of 133

range of end-market applications, such as automotive, industrial and Internet of Things (IOT), mobile, and communication infrastructure.

#### JURISDICTION AND VENUE

12. This action arises under the patent laws of the United States, Title 35 of the United States Code. Accordingly, this Court has subject matter jurisdiction under 28 U.S.C. §§ 1331 and 1338(a).

13. This Court has personal jurisdiction over NXP NV and NXP BV. NXP NV and NXP BV have purposefully and voluntarily availed themselves of the privileges of conducting business in the United States, in the State of Texas, and in the Western District of Texas by continuously and systematically placing goods into the stream of commerce through an established distribution channel with the expectation that they, or third party products incorporating them, will be purchased by consumers in the Western District of Texas. NXP NV has also established NXP USA, headquartered within the Western District of Texas, as its "registered agent in the United States." NXP NV and NXP BV through intermediaries (including customers, distributors, sales agents, and others), ship, distribute, offer for sale, sell, advertise, and/or use its products (including, but not limited to, the products that are accused of patent infringement in this lawsuit), and/or products incorporating these products, in the United States, the State of Texas, and the Western District of Texas.

14. This Court has personal jurisdiction over NXP USA at least because NXP USA is a resident of Texas as defined by Texas law. NXP USA is also subject to this Court's specific and general personal jurisdiction because NXP USA has sufficient minimum contacts within the State of Texas and this District, pursuant to due process and/or the Texas Long Arm Statute. NXP USA is headquartered in the State of Texas and in this District, and NXP USA has conducted and continues to regularly conduct business within the State of Texas. NXP USA is

# Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 6 of 133

registered to do business within the State of Texas and maintains an agent for service of process in Texas. NXP USA has purposefully and voluntarily availed itself of the privileges of conducting business in the United States, in the State of Texas, and in the Western District of Texas by continuously and systematically placing goods into the stream of commerce through an established distribution channel with the expectation that they will be purchased by consumers in the United States and in the Western District of Texas. NXP USA directly and/or through intermediaries (including distributors, sales agents, and others), ships, distributes, offers for sale, sells, advertises, and/or uses its products (including, but not limited to, the products that are accused of patent infringement in this lawsuit) in the United States, the State of Texas, and the Western District of Texas.

15. NXP USA has derived substantial revenues from its infringing acts occurring within the United States, the State of Texas and within this District.

16. Venue is proper as to NXP NV and NXP BV under 28 U.S.C. § 1391(c)(3) in that they are not residents of the United States and may, therefore, be sued in any judicial district. *Brunette Mach. Works, Ltd. v. Kockum Indus., Inc.,* 406 U.S. 706, 714 (1972).

17. Venue is proper as to NXP USA under 28 U.S.C. § 1400(b) because it has committed acts of infringement in this District and has regular and established places of business within this District. *TC Heartland LLC v. Kraft Foods Grp. Brands LLC*, 137 S. Ct. 1514, 1521 (2017). Specifically, NXP maintains its "Oak Hill" facility at 6501 William Cannon Drive West, Austin, TX 78735, and its 960,000 square foot "Ed Bluestein" facility at 3501 Ed Bluestein Blvd., Austin, TX 78721.

18. NXP USA has not disputed this District's personal jurisdiction over it in other recent patent infringement actions, nor has NXP USA disputed that venue is proper as to it in the

# Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 7 of 133

Western District of Texas. See, e.g., Bicameral LLC v. NXP USA, Inc., et al., Case No. 6:18-cv-00294 (W.D. Tex.), Dkt. 25 at ¶¶ 10-11.

19. Joinder of NXP NV, NXP BV, and NXP USA is proper because they are related parties who are either jointly and severally liable for infringement, or who make, use, sell, offer for sale, or import the same or similar accused products that practice the same Asserted Patents. On information and belief, NXP BV and NXP USA are wholly owned subsidiaries of NXP NV. Further, on information and belief, NXP NV, NXP BV, and NXP USA use the same underlying hardware and/or software in their infringing products and therefore the factual question of infringement will substantially overlap between NXP NV, NXP BV, and NXP USA. Further, Plaintiff anticipates that there will be substantial overlap during the discovery process.

20. NXP has committed acts of infringement in this District giving rise to this action and does business in this District, including making sales and/or providing service and support for its respective customers in this District. NXP purposefully and voluntarily sold one or more of the infringing products with the expectation that they would be purchased by consumers in this District and/or incorporated into products that would be purchased by consumers in this District. These infringing products have been and continue to be purchased by consumers in this District. NXP has committed acts of patent infringement within the United States, the State of Texas, and the Western District of Texas.

#### **BELL SEMIC'S ASSERTED PATENTS**

### A. U.S. Patent No. 8,049,340 (Hall 340 Patent)

21. Bell Semic is the owner by assignment of U.S. Patent No. 8,049,340 ("the Hall 340 Patent"), owns all right, title, and interest in the Hall 340 Patent; and holds the right to sue and recover damages for infringement thereof, including past infringement. The Hall 340 Patent

### Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 8 of 133

is entitled "Device for Avoiding Parasitic Capacitance in an Integrated Circuit Package." A true and correct copy of the Hall 340 Patent is attached as **Exhibit A**.

22. The inventors of the Hall 340 Patent are Jeffrey Hall, Shawn Nikoukary, Amar Amin, and Michael Jenkins.

23. The application for the Hall 340 Patent was filed on March 22, 2006, and it duly and properly issued as a patent on November 1, 2011.

24. As of September 2020, the disclosure of the Hall 340 Patent has been cited as pertinent prior art by a patent examiner or an applicant during the prosecution of at least 2 patents and published applications filed by leading technology companies Alcatel Lucent and Intel.

## B. U.S. Patent No. 8,288,269 (Hall 269 Patent)

25. Bell Semic is the owner by assignment of U.S. Patent No. 8,288,269 ("the Hall 269 Patent"), owns all right, title, and interest in the Hall 269 Patent; and holds the right to sue and recover damages for infringement thereof, including past infringement. The Hall 269 Patent is entitled "Methods for Avoiding Parasitic Capacitance in an Integrated Circuit Package." The Hall 269 Patent issued on October 16, 2012. A true and correct copy of the Hall 269 Patent is attached as **Exhibit B**.

26. The inventors of the Hall 269 Patent are Jeffrey Hall, Shawn Nikoukary, Amar Amin, and Michael Jenkins.

27. The application for the Hall 269 Patent was filed on October 4, 2011, and claims priority to the application leading to the Hall 340 Patent, which was filed on March 22, 2006. The Hall 269 Patent issued as a patent on October 16, 2012.

## C. U.S. Patent No. 7,566,964 (Kang Patent)

28. Bell Semic is the owner by assignment of U.S. Patent No. 7,566,964 ("the Kang Patent"), owns all right, title, and interest in the Kang Patent; and holds the right to sue and recover damages for infringement thereof, including past infringement. The Kang Patent is entitled "Aluminum Pad Power Bus and Signal Routing for Integrated Circuit Devices Utilizing Copper Technology Interconnect Structures." A true and correct copy of the Kang Patent is attached as **Exhibit C**.

29. The inventors of the Kang Patent are Seung H. Kang, Roland P. Krebs, Kurt George Steiner, Michael C. Ayukawa, and Dr. Sailesh M. Merchant.

30. The application for the Kang Patent was filed on September 30, 2003, and it claims priority to Provisional Application No. 60/462,504, filed on April 10, 2003. The Kang Patent issued as a patent on July 28, 2009.

31. As of September 2020, the disclosure of the Kang Patent has been cited as pertinent prior art by a patent examiner or an applicant during the prosecution of at least 13 patents and published applications filed by leading technology companies such as IBM, Texas Instruments, Renesas, and Advanced Semiconductor Engineering.

# D. U.S. Patent No. 6,281,129 (Merchant Patent)

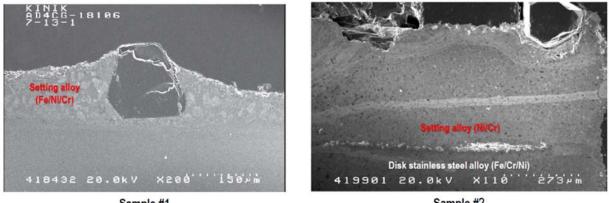

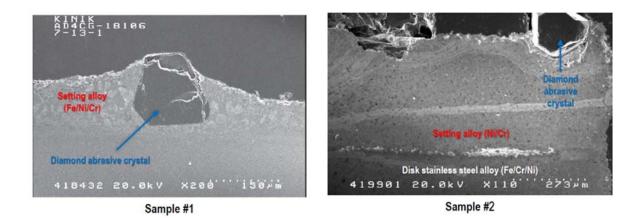

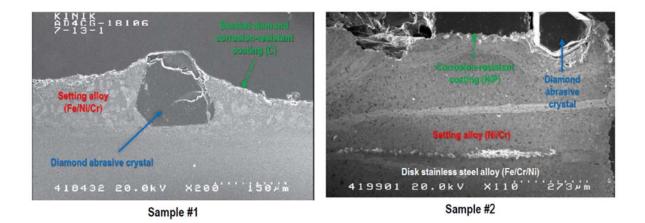

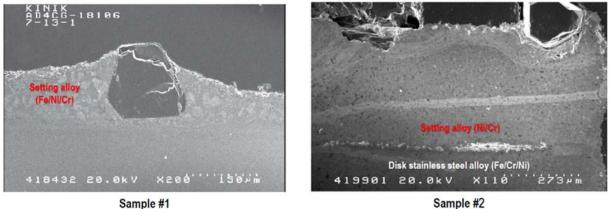

32. Bell Semic is the owner by assignment of U.S. Patent No. 6,281,129 (the "Merchant Patent"), owns all right, title, and interest in the Merchant Patent; and holds the right to sue and recover damages for infringement thereof, including past infringement. The Merchant Patent is entitled "Corrosion-Resistant Polishing Pad Conditioner." A true and correct copy of the Merchant Patent is attached as **Exhibit D**.

The inventors of the Merchant Patent are Dr. Sailesh M. Merchant, William G.

Easter, and John A. Maze.

# Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 10 of 133

34. The application for the Merchant Patent was filed on September 20, 1999, and it issued as a patent on August 28, 2001.

35. As of September 2020, the disclosure of the Merchant Patent has been cited as pertinent prior art by a patent examiner or an applicant during the prosecution of at least 22 patents and published applications.

# E. U.S. Patent No. 6,153,543 (Chesire Patent)

36. BSL is the owner by assignment of U.S. Patent No. 6,153,543 (the "Chesire Patent"). The Chesire Patent is entitled "High Density Plasma Passivation Layer and Method of Application." A true and correct copy of the Chesire Patent is attached as **Exhibit E.**

37. The inventors of the Chesire Patent are Daniel P. Chesire, Edward P. Martin, Jr., Leonard J. Olmer, Barbara D. Kotzias, and Rafael N. Barba.

38. The application for the Chesire Patent was filed on August 9, 1999, and it issued as a patent on November 28, 2000.

39. As of September 2020, the disclosure of the Chesire Patent has been cited as pertinent prior art by a patent examiner or an applicant during the prosecution of at least 27 issued patents and published applications—including during the prosecution of patent applications filed by leading technology companies such as Nanya, Cypress Semiconductor, Hynix Semiconductor, and Sandisk.

# F. U.S. Patent No. 6,743,669 (Lin Patent)

40. Bell Semic is the owner by assignment of U.S. Patent No. 6,743,669 (the "Lin Patent"), owns all right, title, and interest in the Lin Patent; and holds the right to sue and recover damages for infringement thereof, including past infringement. The Lin Patent is entitled "Method of Reducing Leakage Using Si<sub>3</sub>N<sub>4</sub> or SiON Block Dielectric Films." A true and correct copy of the Lin Patent is attached as **Exhibit F**.

# FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT

41. The inventors of the Lin Patent are Hong Lin, Shiqun Gu, and Peter McGrath.

42. The application for the Lin Patent was filed on June 5, 2002, and it issued as a patent on June 1, 2004.

43. As of September 2020, the disclosure of the Lin Patent has been cited as pertinent prior art by a patent examiner or an applicant during the prosecution of at least 14 issued patents and published applications—including during the prosecution of patent applications filed by leading technology companies such as Samsung, IBM, Fujitsu, and United Microelectronics Corp.

# G. U.S. Patent No. 6,544,907 (Ma Patent)

44. Bell Semic is the owner by assignment of U.S. Patent No. 6,544,907 (the "Ma Patent"), owns all right, title, and interest in the Ma Patent; and holds the right to sue and recover damages for infringement thereof, including past infringement. The Ma Patent is entitled "Method of Forming a High Quality Gate Oxide Layer Having a Uniform Thickness." A true and correct copy of the Ma Patent is attached as **Exhibit G**.

45. The inventors of the Ma Patent are Yi Ma and Edith Yang.

46. The application for the Ma Patent was filed on October 12, 2000, and it issued as a patent on April 8, 2003.

47. As of September 2020, the Ma Patent has been cited as pertinent prior art by a patent examiner or an applicant during the prosecution of at least 1 published application filed by leading technology company Hynix Semiconductor.

# H. U.S. Patent No. 6,342,734 (Allman Patent)

48. Bell Semic is the owner by assignment of U.S. Patent No. 6,342,734 (the "Allman Patent"), owns all right, title, and interest in the Allman Patent; and holds the right to sue and recover damages for infringement thereof, including past infringement. The Allman Patent is

## Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 12 of 133

entitled "Interconnect-Integrated Metal-Insulator-Metal Capacitor and Method of Fabricating Same." A true and correct copy of the Allman Patent is attached as **Exhibit H**.

49. The inventors of the Allman Patent are Derryl D. J. Allman, John Q. Walker, Verne C. Hornback, and Todd A. Randazzo.

50. The application for the Allman Patent was filed on April 27, 2000, and it issued as a patent on January 29, 2002.

51. As of September 2020, the disclosure of the Allman Patent has been cited as pertinent prior art by a patent examiner or an applicant during the prosecution of at least 37 issued patents and published applications—including during the prosecution of patent applications filed by leading technology companies such as IBM, Mitsubishi, Samsung, TSMC, Sharp, Philips, Fujitsu, Renesas, and Qualcomm.

# I. U.S. Patent No. 6,960,836 (Bachman Patent)

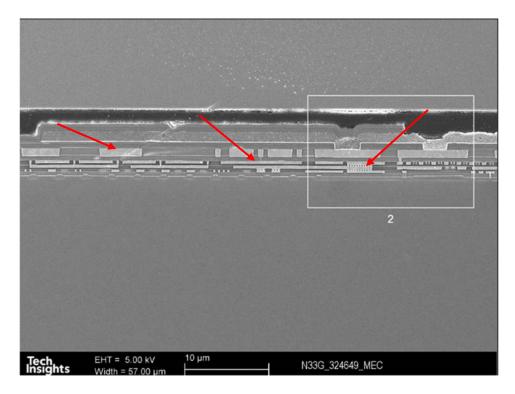

52. Bell Semic is the owner by assignment of U.S. Patent No. 6,960,836 (the "Bachman Patent"), owns all right, title, and interest in the Bachman Patent; and holds the right to sue and recover damages for infringement thereof, including past infringement. The Bachman Patent is entitled "Reinforced Bond Pad." A true and correct copy of the Bachman Patent is attached as **Exhibit I**.

53. The inventors of the Bachman Patent are Mark Adam Bachman, Daniel Patrick Chesire, Dr. Sailesh M. Merchant, John William Osenbach, and Kurt George Steiner.

54. The application for the Bachman Patent was filed on September 30, 2003, and it issued as a patent on November 1, 2005.

55. As of September 2020, the disclosure of the Bachman Patent has been cited as pertinent prior art by a patent examiner or an applicant during the prosecution of at least 17 issued patents and published applications—including during the prosecution of patent

## Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 13 of 133

applications filed by leading technology companies such as Texas Instruments, Infineon, TSMC, Northrup Gruman, Renesas, and Fujitsu.

## J. U.S. Patent No. 6,624,007 (Kobayakawa Patent)

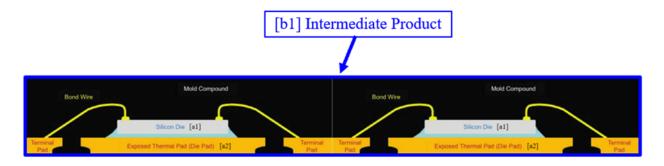

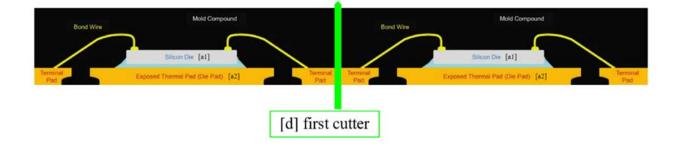

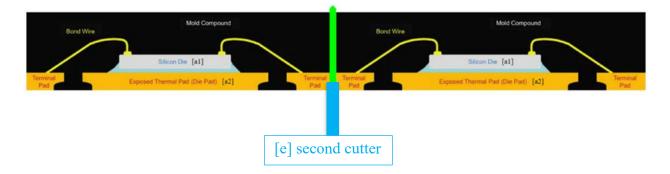

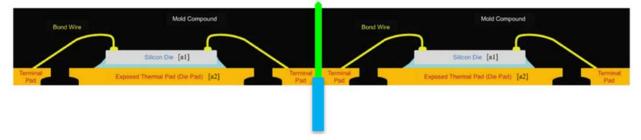

56. Bell Semic is the owner by assignment of U.S. Patent No. 6,624,007 (the "Kobayakawa Patent"), owns all right, title, and interest in the Kobayakawa Patent; and holds the right to sue and recover damages for infringement thereof, including past infringement. The Kobayakawa Patent is entitled "Method of Making Leadframe by Mechanical Processing." A true and correct copy of the Kobayakawa Patent is attached as **Exhibit J**.

57. The inventors of the Kobayakawa patent are Masahiko Kobayakawa and Masahide Maeda.

58. The application for the Kobayakawa Patent was filed on July 25, 2002, and it issued as a patent on September 23, 2003.

59. As of September 2020, the disclosure of the Kobayakawa Patent has been cited as pertinent prior art by a patent examiner or an applicant during the prosecution of at least 8 patents and published applications—including during the prosecution of patent applications filed by leading technology companies such as Rohm, Nichia, Infineon, and Texas Instruments.

# FACTUAL BACKGROUND

60. Bell Semic incorporates the preceding paragraphs as if fully set forth herein.

61. On June 1, 2002, Lucent, having its roots with Bell Laboratories and AT&T Corporation, spun off its microelectronics business as Agere. Agere later merged with LSI Logic forming LSI Corporation in 2007, which was in turn acquired by Avago in 2014. In 2016, Avago purchased Broadcom and assumed its name to become the current Broadcom Inc. In 2017, Broadcom assigned a patent portfolio containing over 1,900 worldwide patents and applications,

### Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 14 of 133

approximately 1,500 of which are active U.S. patents, to Bell Semic that included patents originally assigned or issued to Bell Labs, Lucent, Agere, LSI Logic, and LSI.

62. Portions of the Bell Semic portfolio are presently licensed and/or were previously licensed to leading technology companies by Bell Semic senior executives while they were working at Lucent, Agere, LSI, Avago, and/or Broadcom. (*See supra*  $\P$  2.) Portions of the Bell Semic portfolio were also invented and co-invented by other Bell Semic senior executives while they were working at Lucent, Agere, LSI, Avago, and/or Broadcom. (*Id.*)

63. Bell Semic's Asserted Patents arise out of the research, conception, creation, and design of innovative technology developed by leading high-technology companies, including LSI Logic, Agere, and LSI Corporation. Prior to their ultimate acquisition by Avago (now Broadcom), those companies were pioneers of innovative semiconductor technology—and made substantial investments into researching, inventing, creating, and manufacturing cutting-edge semiconductor technology. Bell Semic's Asserted Patents are directed to this inventive technology relating to semiconductors, integrated circuits and related products.

64. NXP infringes and has infringed by making, selling, offering to sell, using, and/or importing products (including importing products made by a patented process) throughout the United States. Moreover, NXP works closely with its customers, foundry suppliers, distributors, OEMs, or other third parties to make, use, sell, offer to sell, and/or import semiconductor devices, integrated circuits, and related products. NXP tailors its manufacturing process for its customers and designs its products to be integrated into downstream products. In addition to its own manufacturing, NXP's affirmative acts in furtherance of the manufacture, use, sale, offer to sell, and importation of its products in and/or into the United States by itself and others further include, without limitation, any one or a combination of: (i) designing specifications for

# Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 15 of 133

manufacture of NXP's products; (ii) collaborating on, encouraging, and/or funding the development of processes for the manufacture of NXP's products; (iii) soliciting and/or sourcing the manufacture of NXP's products; (iv) licensing, developing, and/or transferring technology and know-how to enable the manufacture of their products; (v) enabling and encouraging the use, sale, or importation of their products in the United States; and (vi) advertising its products and/or downstream products incorporating them in the United States.

65. NXP provides marketing and/or technical support services for its products from its facilities in the United States. For example, NXP maintains a website that advertises its products, including identifying the applications for which they can be used and providing specifications for their products. (*See, e.g.*, <u>https://www.nxp.com/</u>.) NXP's publicly-available website also contains datasheets, application notes, fact sheets, and other materials related to its products. (*See* <u>https://www.nxp.com/design/documentation:DOCUMENTATION#/</u>.) For example, NXP's website contains reference designs

(https://www.nxp.com/design/designs:REFDSGNHOME#/), spanning at least audio, interfaces, peripherals and logic, power management, processors and microcontrollers, RFID, security and authentication, sensors, and wireless connectivity; development support including design toolboxes, evaluation and development boards, and a library of RF designs (https://www.nxp.com/design/development-boards:EVDEBRDSSYS#/); software including

application design software, integrated development environment software, and software development kits (<u>https://www.nxp.com/design/software:SOFTWARE-</u>

<u>CENTER#/home/query/~query~/~filter~/popularity/0</u>); and customer support through NXP's support forums (<u>https://community.nxp.com/welcome</u>).

# Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 16 of 133

66. In addition to these resources, NXP also provides numerous support resources for the customers of its semiconductor devices in addition to datasheets and application notes, including online and in-person training through NXP Connects and NXP Technology Days (https://www.nxp.com/design/training:TRAINING-EVENTS#/). This training includes: NXP Connects, which is "a world-class program combining in-depth technical training, a first-look at cutting-edge live demonstrations, and unique opportunities to hear from an array of industry leaders whose technology is shaping the future" (https://www.nxp.com/design/training/nxpconnects:NXP-CONNECTS); "NXP Technology Days," which provide "a deep-dive, technical training program for engineers designing solutions with embedded technology" (https://www.nxp.com/design/training/nxp-technology-days:NXP-TECH-DAYS); and access to commercial support and engineering services (https://www.nxp.com/design/engineeringservices: SW-SUPPORT). Moreover, NXP supports an "NXP Partner Directory," which is "a global network of independent engineering companies that offer the vital tools, software, technology, engineering services and training to speed [NXP customer's] design" (https://www.nxp.com/support/support/nxp-partner-directory:PARTNER-DIRECTORY#/).

# **NXP'S PRE-SUIT KNOWLEDGE OF ITS INFRINGEMENT FROM BELL SEMIC**

67. Before filing this lawsuit, Bell Semic notified NXP that Broadcom assigned to Bell Semic a large portfolio of semiconductor patents, identified NXP Technology Nodes that infringe Bell Semic's Asserted Patents, further identified exemplary products from those Technology Nodes that infringe the Asserted Patents, and offered to license those patents to NXP. 68. Specifically, on January 9, 2019, Mr. Hilyard, sent a letter to NXP's Austin,

Texas headquarters addressed to Mr. Changhae Park (NXP's Senior Vice President and Chief IP

# Officer):

"I am writing to inform you that Bell Semic acquired the semiconductor-related patent assets previously owned by Agere Systems Inc. and LSI Corporation. We understand that both NXP and Freescale have been licensed to at least a portion of these patents in the past. As you probably know, this portfolio includes patents originally assigned to Bell Labs and Lucent Technologies, as well as those assigned to Agere and LSI.

As you are most likely aware, the portfolio reflects expertise and inventions developed at various R&D labs and manufacturing facilities associated with these companies around the world . . . The patent portfolio comprises over 3,000 worldwide patents and applications – approximately 2,000 of which are active U.S. patents.

Our records indicate that NXP's most recent license to this portfolio expired at the end of 2014 and Freescale's most recent license to this portfolio expired in October 2016. Because NXP and Freescale have previously enjoyed a license to this portfolio, we believe you understand and appreciate the value of the unique and ground-breaking technologies covered by this patent portfolio.

By way of background, I've previously served as part of the Agere/LSI licensing team. At Bell Semiconductor, I am joined by other former members of the Lucent/Agere/LSI licensing teams, including John Veschi and Sailesh Merchant. We are very familiar with this pioneering patent portfolio and have licensed this portfolio to many of the world's leading semiconductor companies. Our goal is to build upon the amicable licensing history between Lucent/Agere/LSI and NXP and Freescale – as well as the similar relationships we previously established throughout the semiconductor industry. Over the last few months, we have been acquiring NXP products and conducting reverse engineering to establish NXP's use of exemplary patents in the portfolio. Our preliminary analysis evidences that NXP is currently making, using, selling, or offering for sale products that infringe one or more of Bell Semic's patents."

69. Bell Semic's January 9, 2019 letter also provided NXP with notice of

infringement by NXP's Technology Nodes and exemplary products from those Nodes, including

the Allman, Chesire, and Merchant Asserted Patents as follows:

| Device             | Product<br>Application           | Device Type                        | Technology<br>Node | Allman<br>6342734 | Ali<br>6591410 | Chesire<br>6153543 | Chittipeddi<br>6207547 | Easter<br>6281129 | Easter<br>6596639 | Esry<br>6406999 |

|--------------------|----------------------------------|------------------------------------|--------------------|-------------------|----------------|--------------------|------------------------|-------------------|-------------------|-----------------|

| PN5180A0HN/C3E     | Identification &<br>Security     | NFC Reader                         | 0.18um             |                   |                |                    |                        |                   | х                 | x               |

| TDA18250AHN/C1,557 | Media & Audio                    | Silicon Tuners                     | 0.30um             | х                 | х              |                    |                        |                   |                   |                 |

| TDF8530TH/N2,118   | Media & Audio                    | Class-D Power<br>Amp (Car radio)   | 0.18um             |                   |                |                    |                        |                   | х                 |                 |

| NXP 80V18: PN80V   | NFC                              | Bluetooth                          | 0.18um             |                   |                |                    |                        | х                 |                   | x               |

| ASL2500SHNY        | Power<br>Management              | Automotive<br>Lighting             | 0.18um             |                   |                | x                  |                        | х                 | x                 | х               |

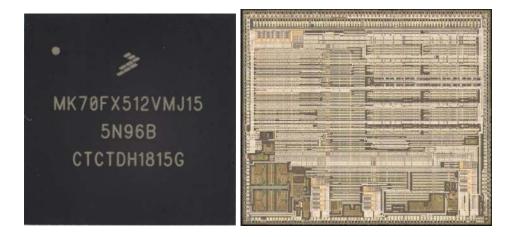

| MK70FX512VMJ15     | Processors &<br>Microcontrollers | ARM Cortex<br>Processor            | 90nm               |                   |                |                    |                        | х                 |                   |                 |

| LPC11U35FET48/501  | Processors &<br>Microcontrollers | ARM Cortex<br>Processor            | 90nm               |                   |                | x                  | x                      | х                 | х                 | х               |

| BGU8009            | RF                               | LNA for GPS                        | 0.35um             |                   |                |                    |                        | х                 |                   |                 |

| FXTH87EH11DT1      | Sensors                          | Tire Pressure<br>Monitoring Sensor | 0.25um             | x                 |                | x                  | x                      | x                 |                   |                 |

| FXAS21002CQR1      | Sensors                          | Gyroscope                          | 0.18um             | x                 |                | x                  |                        | х                 | x                 | x               |

Exemplary List of Bell Semic's Patents Infringed by NPX Products

70. In the January 9, 2019 letter, Bell Semic also proposed having a near-term dialogue with NXP to discuss details about the licensing program and the patent portfolio, as well as providing claim charts.

71. On February 4, 2019, having not received a response, Mr. Hilyard again sent an email to Mr. Park requesting to set up a phone call.

72. On February 8, 2019, Mr. Mark Patrick, Senior Law Director, Intellectual Property at NXP responded, stating "In your letter, Bell Semic claims that Bell Semic's patents are infringed by NXP products. You seek to have a dialogue with NXP about Bell Semic's licensing program and patent portfolio. Prior to any such dialogue, NXP requires that Bell Semic substantiate its accusations by providing claim charts of the Bell Semic patents to NXP for NXP's review and comment."

73. On June 10, 2019, Bell Semic attached a proposed non-disclosure agreement, and stated, "Sorry for the delay in getting back to you. We have been diligently preparing claim

#### Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 19 of 133

charts for your review. We are now in a position to provide them to you, but we would like to have an NDA in place before we do that. Attached is an NDA for your review and consideration. Please let me know if you have any comments on the draft."

74. On June 12, 2019, NXP responded, "NXP does not enter into confidentiality or other like agreements in connection with patent accusations against NXP. To engage in patent licensing discussions with NXP, Bell Semic would need to provide to NXP the claim charts without any confidentiality requirement or use restriction. However, we do recognize and accept that the claim charts would be provided subject to Rule 408 of the Federal Rules of Civil Procedure."

75. On September 12, 2019, Mr. Hilyard provided claim charts for the Asserted Patents – Allman, Chesire, Merchant, Easter, Hall 340, and Kang, among others. Each of these claim charts provided detailed mappings, including reverse engineering, of the products identified in Bell Semic's January 9, 2019 letter for these Asserted Patents.

76. In the September 12, 2019 emails, Bell Semic requested an in-person meeting at the beginning of October: "Also, as I mentioned previously, we believe a face-to-face meeting to discuss the charts in detail is the best way to proceed. Please let me know if you and your team can meet the first or second week of October. If so, please provide dates and times during those weeks that will work. If you would like to discuss, let me know and we can set-up a call."

77. On October 9, 2019, Bell Semic's Mr. Hilyard sent another email to NXP requesting a meeting, "We would like to schedule a meeting to discuss the claim charts I forwarded to you. Are you and your team available for a meeting the week of October 28 or November 4. We can make most of those days work."

78. On October 12, 2019, NXP responded, stating "It wasn't clear from your prior response that you won't be providing more claim charts. Please confirm that there will be no more claim charts to follow."

79. Bell Semic responded the same day, confirming that there were no new claim charts.

80. On October 15, 2019, NXP responded, stating that NXP was "now able to involve our expert in the review of the charts. We will provide an initial written response, including if an in-person meeting is justified. I can't confirm the timeframe for our response at this moment."

81. On October 25, 2019, NXP responded, "I received an initial response back from our expert that most of the claim charts are incomplete. Here are the particulars:

'543 Chesire. Page 2 is blank.

'129 Easter. Pages 2 and 3 are blank. No independent claim is asserted (pages 7, 8, 9, 10 and 11 show photos and arrows only).

'734 Allman. Page 2 is blank.'639 Easter. Page 2 is blank.'964 Kang. Page 2 is blank.'340 Hall. Page 2 is blank."

82. On October 30, 2019, "Sorry for the confusion on these. For some reason, a few pictures were deleted when converting to PDF. All the page 2s are just a snapshot of the front page of each patent. They don't have anything to do with the mappings. We are working on fixing the others. We will send shortly."

83. On December 9, 2019, Mr. Hilyard provided the corrected claim charts in four separate emails, and responded, "As I mentioned in my previous email, for the majority of the CCs, the only pictures missing were the front pages of the patent, so you should have been able to review." These claim charts also mapped additional NXP products to the Asserted Patents.

### Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 21 of 133

84. On January 8, 2020, having not received a response from NXP, Mr. Hilyard sent another email to NXP to follow up and attempt to set up a meeting to discuss the claim charts.

85. On February 21, 2020, still having not received a response from NXP, Mr. Veschi sent an email to Mr. Patrick from NXP, attaching a letter addressed to Ms. Jennifer Wuamett, NXP's Executive Vice President and General Counsel. Mr. Veschi indicated Bell Semic's desire to "meet in the next two weeks to discuss licensing options if at all possible."

86. Mr. Veschi's letter to Ms. Wuamett stated, "We are following up on our previous communications with NXP Semiconductors regarding the above matter. Since our initial communication in January 2019, we have provided NXP with claim charts illustrating products produced and/or sold by NXP Semiconductors that infringe one or more of the patents within the Bell Semiconductor Portfolio. We have continued our reverse engineering efforts of your products and are providing an updated summary of our infringement analysis to date in the table below. Please let me know your availability for a meeting in the next two weeks to discuss licensing options for the patents and products identified below as well as the broader Bell Semiconductor portfolio."

87. The chart referenced by Mr. Veschi included an identification of numerous NXP products and provided exemplary patents that these products infringed, including an identification of the previously claim charted products:

| NXP<br>Device     | Product<br>Application           | Device Type                                     | Tech<br>Node    | Alman 6342734 | Bachman<br>6960836 | Bachman<br>7221173 | Chesire 6153543 | Chittipeddi<br>6207547 | Downey 6194323 | Easter 6281129 | Easter 6596639 | Esry 6406999 | Kang 7566964 | Un 6743669 | Ma 6544907 | Miller 6459049 | Greenberg<br>6140710 | Govind 6531932 | Hall 8288269 | Hall 8049340 |

|-------------------|----------------------------------|-------------------------------------------------|-----------------|---------------|--------------------|--------------------|-----------------|------------------------|----------------|----------------|----------------|--------------|--------------|------------|------------|----------------|----------------------|----------------|--------------|--------------|

| 8GU8009           | RF                               | LNA for GPS                                     | 0.35um          |               |                    |                    |                 |                        |                | x              |                |              |              |            |            |                |                      |                |              |              |

| TDA18250AHN/C     | Media & Audio                    | Silicon Tuners                                  | 0.30um          | x             |                    |                    |                 |                        |                | x              |                |              |              |            | Ĵ,         |                |                      |                |              |              |

| FXTH87EH11DT1     | Sensors                          | Tire Pressure<br>Monitoring Sensor              | 0.25um          | x             |                    |                    | X               | x                      |                | x              |                |              |              |            |            |                |                      |                |              |              |

| FXAS21002CQR1     | Sensors                          | Gyroscope                                       | 0.18um          | x             |                    |                    | x               |                        | x              | x              | x              | x            |              |            |            |                |                      |                |              |              |

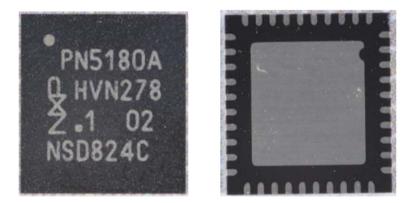

| PN5180A0HN/C3E    | Identification &<br>Security     | NFC Reader                                      | 0.18um          |               | x                  |                    |                 |                        | x              | x              | x              | x            |              |            |            |                |                      |                |              |              |

| TDF8530TH/N2      | Media & Audio                    | Audio Amplifier                                 | 0.18um          |               |                    |                    |                 |                        |                | x              | x              |              |              |            |            |                |                      |                |              |              |

| NXP 80V18: PN80V  | NFC                              | Bluetooth                                       | 0.18um          |               | x                  |                    |                 |                        | x              | x              | x              | x            |              |            |            |                |                      |                |              |              |

| ASL2500SHNY       | Power Management                 | Automotive Lighting                             | 0.18um          |               | x                  |                    | x               | x                      | x              | x              | x              | x            |              |            |            |                |                      |                |              |              |

| MK70FX512VMJ15    | Processors &<br>Microcontrollers | ARM Cortex<br>Processor                         | 90nm            |               |                    |                    |                 |                        |                | x              |                |              | x            | x          |            |                |                      |                |              |              |

| LPC11U35FET48     | Processors &<br>Microcontrollers | ARM Cortex<br>Processor                         | 90nm            |               |                    |                    | x               | x                      | x              | x              | x              | x            |              |            |            |                |                      |                |              |              |

| MWCT1012CFM       | Power Management                 | Wireless Charging IC                            | 90nm            |               |                    |                    |                 |                        |                | x              |                |              | x            | x          |            |                |                      |                |              |              |

| MCIMX281AVM48     | Processors &<br>Microcontrollers | ARM Automotive<br>Processor                     | 90nm            |               |                    |                    |                 |                        |                | x              |                |              | x            |            |            |                |                      |                |              |              |

| MKW41Z512VHT4     | Wireless                         | Zigbee                                          | 90 nm           |               |                    |                    |                 | x                      |                | x              |                |              | x            |            |            |                |                      |                |              |              |

| NxH2280C1         | RF                               | Radio for Wireless<br>Streaming                 | 90nm            |               |                    | x                  |                 |                        |                | x              |                |              |              |            |            |                |                      |                |              |              |

| MCIMX755EVM085C   | Processors &<br>Microcontrollers | Application<br>Processor                        | 28 nm           |               |                    |                    | 1               |                        |                | x              |                |              |              | x          | x          |                |                      |                |              |              |

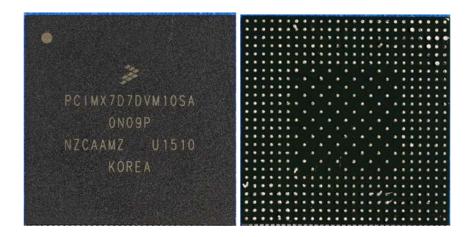

| PCIMX7D7DVM10SA   | Processors & SoC                 | LMX 7 Dual: 2x<br>Cortex-A7, Cortex-<br>M4,     | 28 nm           |               |                    |                    |                 |                        |                | x              |                |              |              | x          | x          |                |                      |                |              |              |

| PCIMX7U5DVP08SC   | Microprocessor                   | I.MX 7ULP                                       | 28 nm           |               |                    |                    |                 |                        |                | x              |                |              | x            |            |            |                |                      |                |              |              |

| F532V234CMN1VUB   | Automotive                       | Vision Processor                                | 28 nm           |               |                    |                    |                 |                        |                |                |                |              |              |            |            | x              |                      |                |              |              |

| MIMXRT1061DVL6A   | Microprocessor                   | ARM Cortex m7 600<br>mhz                        | 28 nm           |               |                    |                    |                 |                        |                | x              |                |              | x            |            |            |                |                      |                |              |              |

| MIMX8MM6DVTLZAA   | Microprocessor                   | I.MX 8M Mini - ARM<br>Cortex-A53, Cortex-<br>M4 | 14 nm<br>Finfet |               |                    |                    |                 |                        |                | x              |                |              |              |            | x          |                |                      |                |              |              |

| NTAG210           | RFID                             | NTAG 21x, NFC<br>Forum Type 2 Tag               |                 |               |                    |                    |                 | x                      |                |                |                |              |              |            |            |                |                      |                |              |              |

| LPC11U37F8D48/401 | Processors &<br>Microcontrollers | LPC Cortex                                      | 48 LQFP         |               |                    |                    |                 |                        |                | x              |                |              |              |            |            |                |                      |                |              |              |

| MIMX8MQ6DVAJZAA   | Processors &<br>Microcontrollers | Quad Applications<br>Processor                  | FC8GA           |               |                    |                    |                 |                        |                |                |                |              |              |            |            | x              |                      |                | x            | x            |

| MCIMX6QP4AVT1AA   | Processors &<br>Microcontrollers | Application<br>Processor                        | 624 FCBGA       |               |                    |                    |                 |                        |                |                |                |              |              |            |            |                |                      |                | x            | x            |

| LS1088AXN7Q1A     | Processors &<br>Microcontrollers | Communications<br>Processor                     | 780 FBGA        |               |                    |                    |                 |                        |                |                |                |              |              |            |            |                |                      |                | x            | x            |

| MPC8543VJANGD     | Processors &<br>Microcontrollers | PowerQUICC III<br>Processor                     | 783 BGA         |               |                    |                    |                 |                        |                |                |                |              |              |            |            |                |                      |                | x            | x            |

| BSC9131NXN1KHKB   | Processors &<br>Microcontrollers | Multicore Baseband<br>Processor                 | FCBGA           |               |                    |                    |                 |                        |                |                |                |              |              |            |            | x              | x                    | x              |              |              |

X January 9, 2019 Notice

X + X Claim charts sent (September 12, 2019 and December 9, 2019)

X February 21, 2020 Notice

88. Despite Bell Semic's continuous and repeated efforts since January 9, 2019, NXP has thus far refused to engage in any meaningful discussions to end their infringement of Bell Semic's Asserted Patents with a license. Thus, NXP continues to knowingly and willfully infringe Bell Semic's Asserted Patents directly, contributorily, and by inducement—to obtain the substantial benefits of those inventions without a license from Bell Semic. Bell Semic is thus left with no other choice but to seek relief from this Court.

# COUNT 1

# Willful Infringement of U.S. Patent No. 8,049,340 (Hall 340 Patent)

89. Plaintiff re-alleges and incorporates by reference the allegations in the foregoing paragraphs as if fully set forth herein.

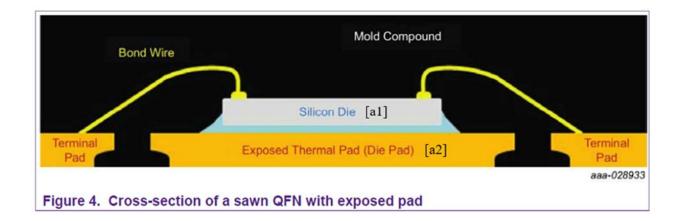

90. The Hall 340 Patent is generally related to an integrated circuit package substrate that has a first and an additional electrically conductive layer separated from each other by an electrically insulating layer, a contact pad formed in the first electrically conductive layer for making a direct connection between the integrated circuit package substrate and a printed circuit board, and a cutout formed in the additional electrically conductive layer that encloses an area that completely surrounds the contact pad for avoiding parasitic capacitance between the additional electrically conductive layer and the printed circuit board. (*See* Hall 340 Patent, Abstract.)

91. Parasitic capacitance results when parts in an electronic circuit are in close proximity to each other, potentially leading to interference with the input or output to a device. Reducing parasitic capacitance has become increasingly necessary as integrated circuit devices, particularly high-speed devices, have included more external connections (for example, the NXP MIMX8MQ6DVA described below includes 621 pins). In order to reduce parasitic capacitance in the multi-layer packages for these integrated circuits, the Hall 340 Patent teaches the use of cutouts over the electrical contacts in electrically conductive layers so that there would be substantially no overlap between the electrical contacts and metal in the electrically conductive layers.

92. The Hall 340 Patent contains 3 independent claims and 19 total claims, covering various integrated circuit package substrates. Claim 12 reads:

An integrated circuit package substrate, comprising:

a first layer comprising a plurality of rows of electrical contacts;

a plurality of electrically conductive layers disposed immediately proximate the first layer;

a plurality of dielectric layers separating, respectively, the electrically conductive layers and the first layer from each other, and

a plurality of rows of cutouts formed in each of the plurality of the electrically conductive layers, each of the cutouts overlapping a corresponding one of the electrical contacts for reducing parasitic capacitance between the electrically conductive layers and the first layer such that there is substantially no overlap of the rows of electrical contacts with metal in the plurality of electrically conductive layers.

93. NXP USA has directly infringed, and continues to directly infringe, one or more

claims of the Hall 340 Patent under 35 U.S.C. § 271(a), either literally or under the doctrine of

equivalents, at least by making, using, selling, offering to sell, and/or importing in or into the

United States without authorization products covered by one or more claims of the Hall 340

Patent (e.g., claims 1, 4, 5, and 12-13),<sup>1</sup> including, but not limited to:

- NXP products with at least one metal layer, proximate to another metal layer having electrical contacts, that has cutouts;

- NXP's MIMX8MQ6DVA, an NXP i.MX 8M Quad processor that includes a quad Arm Cortex-A53 core for use in consumer products;

- NXP's MCIMX6QP4AVT1AA, an NXP i.MX 6 series 32-bit MPU that includes a quad Arm Cortex-A9 core;

- NXP's LS1088AXN7Q1A, an NXP QorIQ Layerscape communications processor;

<sup>&</sup>lt;sup>1</sup> Throughout this Complaint, wherever Bell Semic identifies specific claims of the Asserted Patents that NXP infringes, Bell Semic expressly reserves the right to identify additional asserted claims and products in its infringement contentions in accordance with the local patent rules. Specifically identified claims throughout this Complaint are provided for notice pleading only and are not presented as "exemplary" claims of all other claims for any Asserted Patent.

• NXP's MPC8543VJANGD, an NXP PowerQUICC III processor with high-speed connectivity; and

• NXP's devices that are variants of the above-identified products; (collectively, the "Hall 340 Accused Products").

94. By way of non-limiting example only, NXP's MIMX8MQ6DVA infringes claim 12 of the Hall 340 Patent because it is an integrated circuit that has an integrated circuit package substrate with (1) a first layer that has two or more rows of electrical contacts; (2) two or more electrically conductive layers disposed immediately proximate the first layer; (3) two or more dielectric layers separating, respectively, the electrically conductive layers and the first layer from each other; and (4) two or more rows of cutouts formed in each of the two or more electrically conductive layers, each of the cutouts overlapping a corresponding one of the electrical contacts for reducing parasitic capacitance between the electrically conductive layers and the first layer such that there is substantially no overlap of the rows of electrical contacts with metal in the two or more electrically conductive layers.

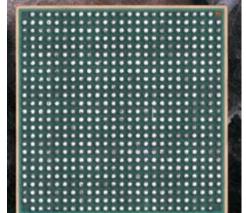

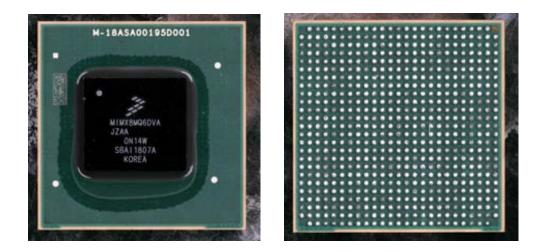

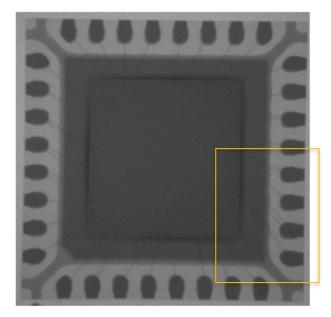

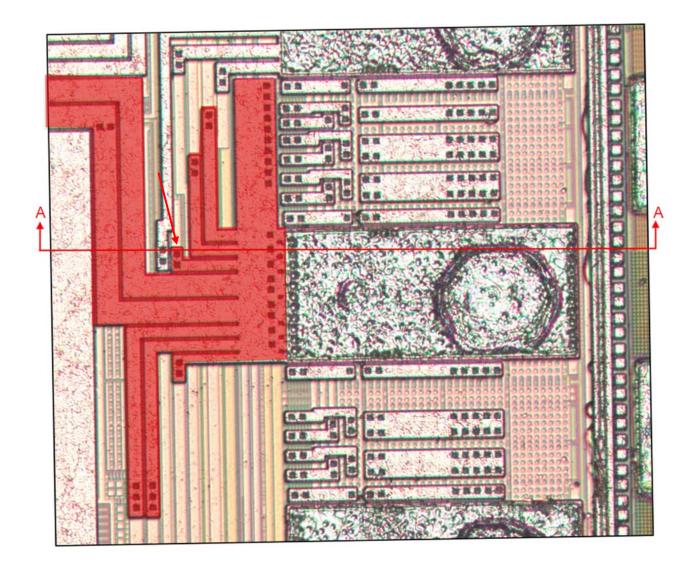

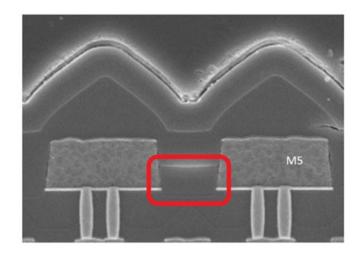

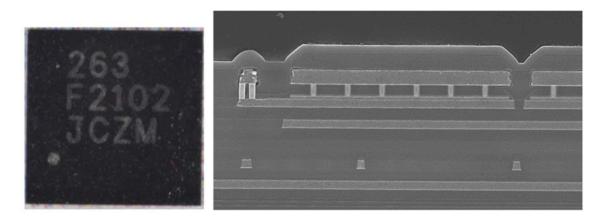

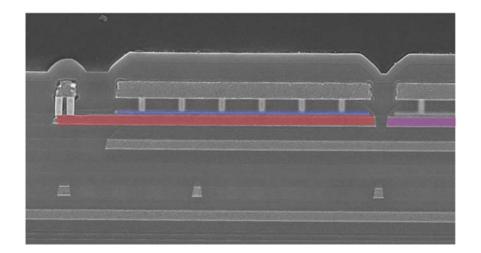

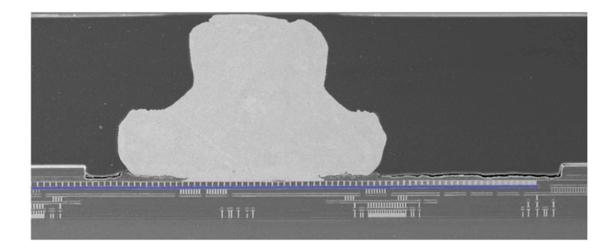

95. As shown below, NXP's MIMX8MQ6DVA is an integrated circuit with an integrated circuit package substrate.

# Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 26 of 133

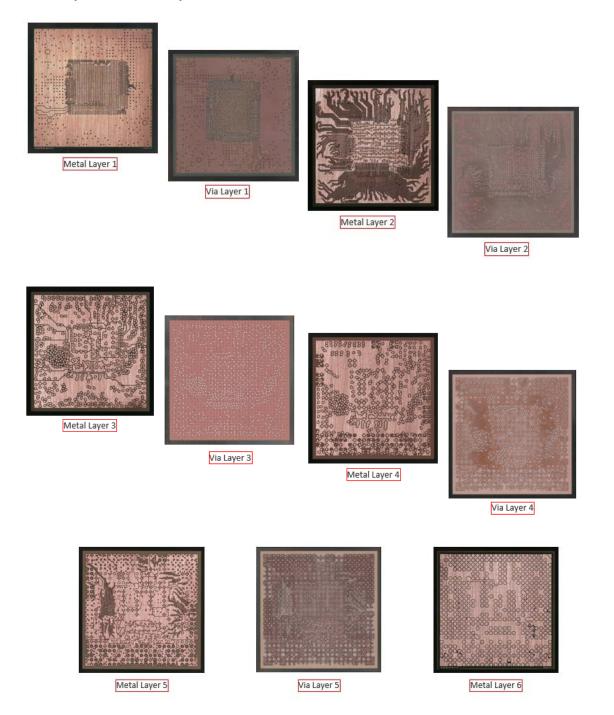

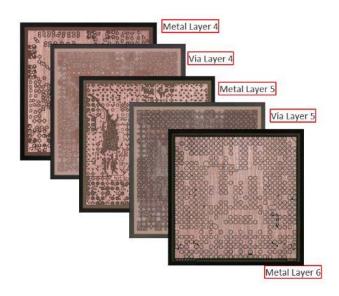

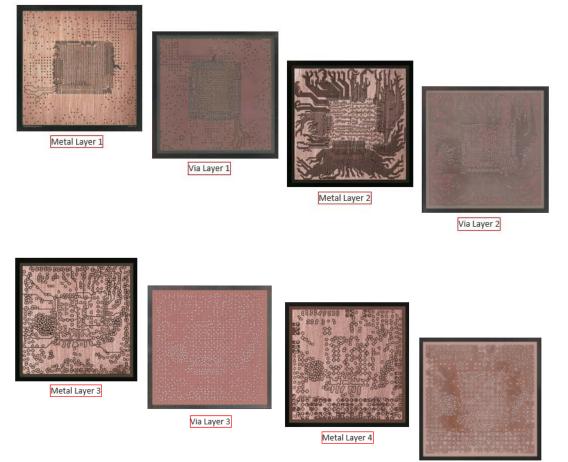

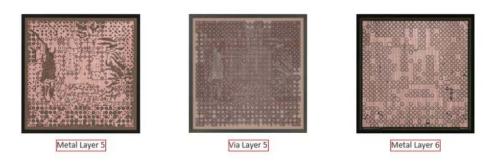

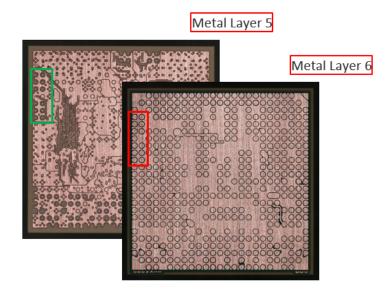

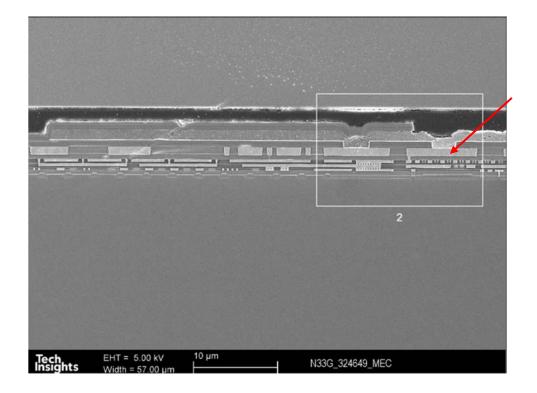

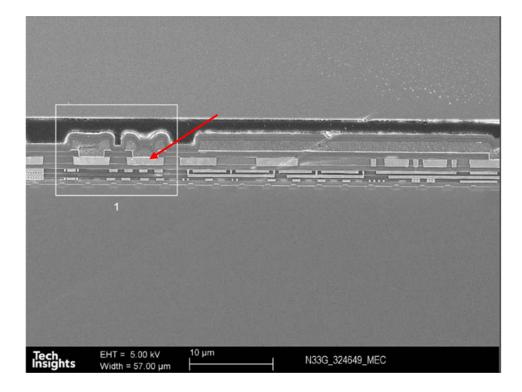

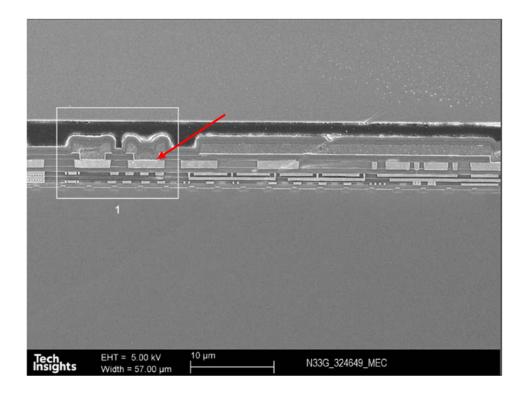

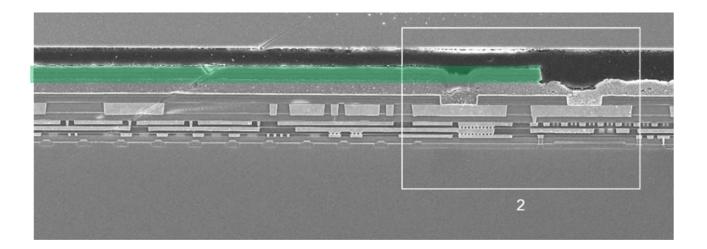

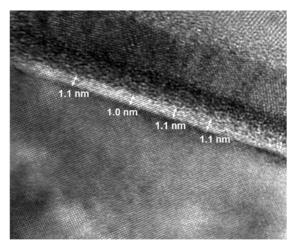

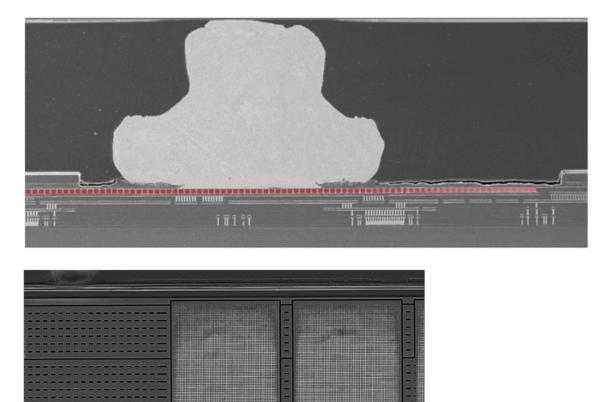

96. The integrated circuit package substrate of the NXP MIMX8MQ6DVA has 6 metal layers and 5 via layers.

# Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 27 of 133

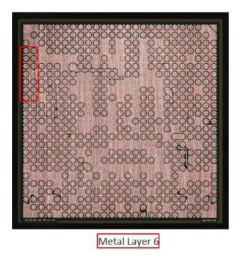

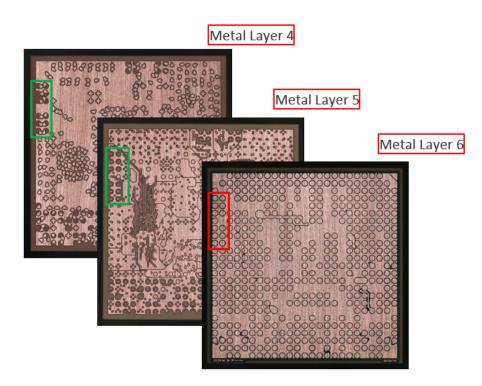

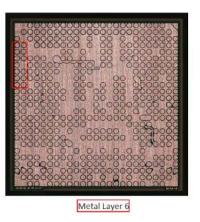

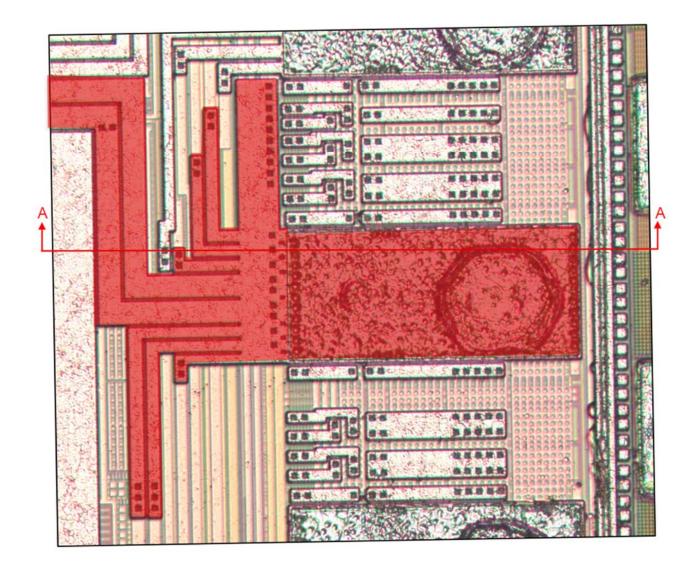

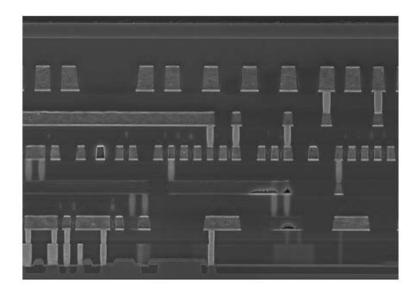

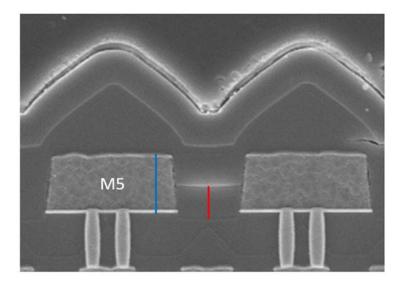

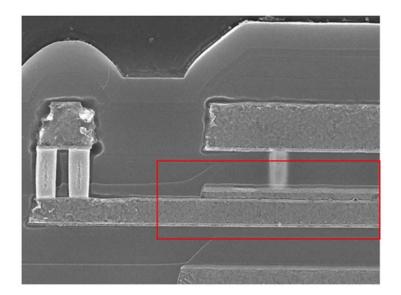

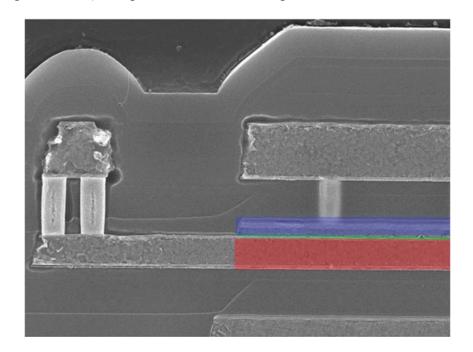

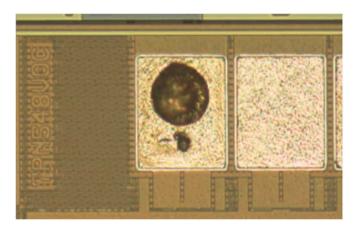

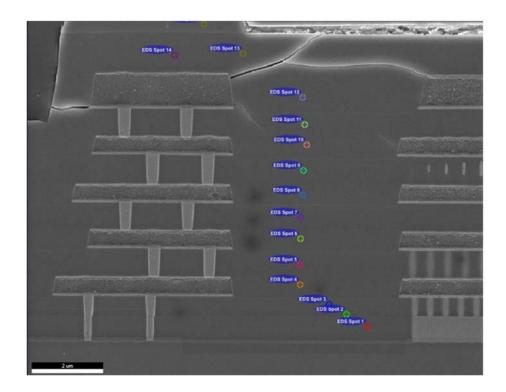

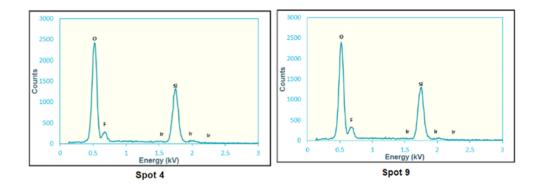

97. The first layer (metal layer 6) of the NXP MIMX8MQ6DVA has a plurality of rows of electrical contacts and forms the ball grid array layer with solder balls, removed for clarity (for example, as indicated in red below).

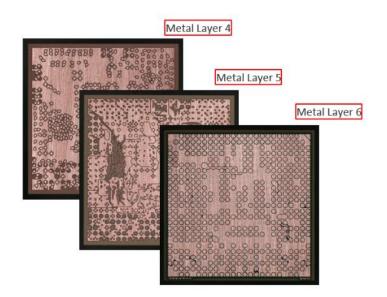

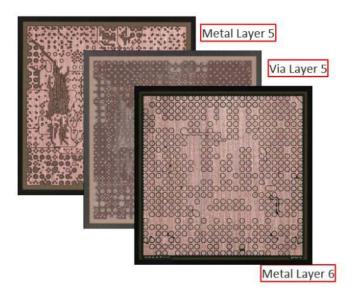

98. The NXP MIMX8MQ6DVA also has a plurality of electrically conductive layers(for example, metal layers 4 and 5) disposed immediately proximate the first layer (metal layer6).

# Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 28 of 133

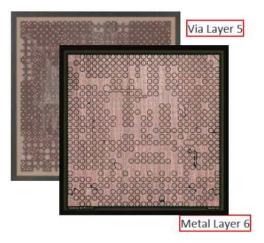

99. The NXP MIMX8MQ6DVA further has a plurality of dielectric layers (for example, via layers 4 and 5) separating, respectively, the electrically conductive layers (metal layers 4 and 5) and the first layer (metal layer 6) from each other.

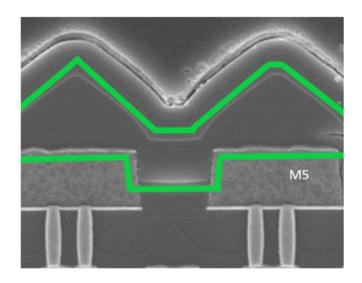

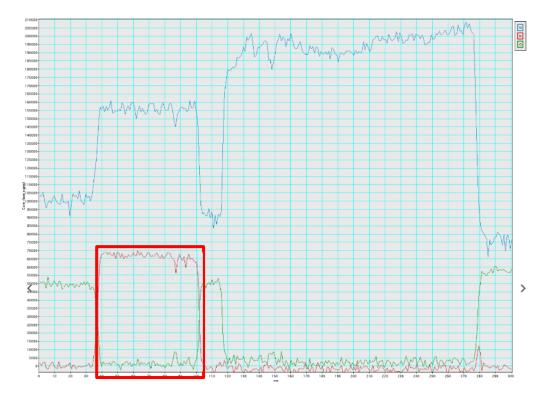

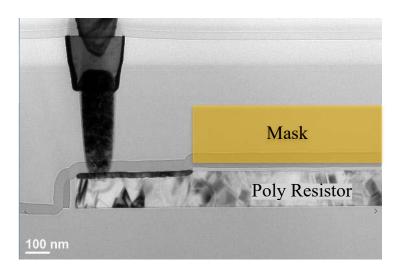

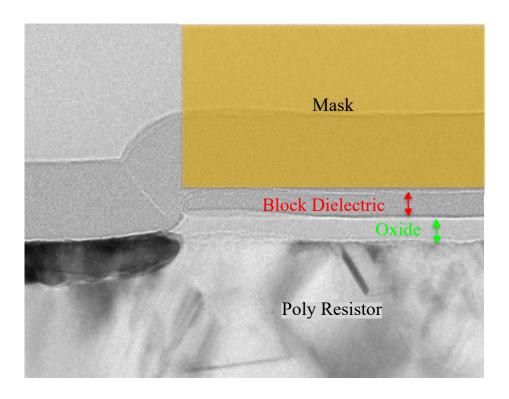

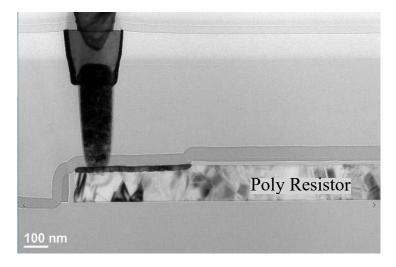

100. The NXP MIMX8MQ6DVA further has a plurality of rows of cutouts (for example, in green below) formed in each of the plurality of the electrically conductive layers, each of the cutouts overlapping a corresponding one of the electrical contacts (for example, in red below) for reducing parasitic capacitance between the electrically conductive layers and the first layer such that there is substantially no overlap of the rows of electrical contacts with metal in the plurality of electrically conductive layers:

101. Claim 12 of the Hall 340 Patent applies to each Hall 340 Accused Product at least because each of those products contain the same or similar at least one metal layer, proximate to another metal layer having electrical contacts, that has cutouts, like the NXP MIMX8MQ6DVA.

102. On information and belief, each of the Hall 340 Accused Products have been available for purchase in the United States, including but not limited to, directly from NXP, through NXP's website, and/or through NXP-authorized Americas distributors.

103. By way of example only, the NXP MIMX8MQ6DVA has been available for purchase in the United States, including but not limited to through NXP's website, either directly from NXP or through at least five NXP-authorized Global or Americas distributors:

# Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 30 of 133

| MIMX8MQ6DVAJZ4                                                                      | AB (Active)     |                           | Package<br>© FBGA621                                                                                     |                      |        |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------|-----------------|---------------------------|----------------------------------------------------------------------------------------------------------|----------------------|--------|--|--|--|--|--|--|

| i.MX 8M: Cortex-A53 up                                                              | to 1.5GHz and   | d Cortex-M4               |                                                                                                          |                      |        |  |  |  |  |  |  |

| Data Sheet Product Summary                                                          |                 |                           | FBGA621, fine-pitch ball grid array<br>package; 621 terminals, 0.65 mm<br>pitch, 17 mm x 17 mm x 2.03 mm |                      |        |  |  |  |  |  |  |

| 🔀 Software & Tools                                                                  | Docume          | ntation                   | body                                                                                                     |                      |        |  |  |  |  |  |  |

| Buy Options Operating                                                               | Characteristics | Environmental Information | Quality Information                                                                                      | Shipping Information |        |  |  |  |  |  |  |

| Buy Options                                                                         |                 |                           |                                                                                                          |                      |        |  |  |  |  |  |  |

| MIMX8MQ6DVAJZAB<br>935377779557<br>ACTIVE                                           |                 |                           |                                                                                                          | Distri               | butors |  |  |  |  |  |  |

| TRAY-Tray, Bakeable, Multiple i<br>Min. Package Quantity: 90<br>Lead Time: 15 weeks | in Drypack      |                           |                                                                                                          |                      |        |  |  |  |  |  |  |

| <ul> <li>Available Distributors: MIN</li> </ul>                                     | AX8MQ6DVAJZAB   |                           |                                                                                                          |                      |        |  |  |  |  |  |  |

|                                                                                     |                 |                           |                                                                                                          |                      |        |  |  |  |  |  |  |

| Shipping Location A                                                                 | LL T            |                           |                                                                                                          |                      |        |  |  |  |  |  |  |

| Distributor Name                                                                    |                 | Region                    | Inventory                                                                                                | Inventory Date       |        |  |  |  |  |  |  |

| Arrow                                                                               | Arrow           |                           | 2                                                                                                        | 2020-03-11           | Order  |  |  |  |  |  |  |

| Avnet                                                                               |                 | AMERICAS                  | 0                                                                                                        | 2020-03-10           | Order  |  |  |  |  |  |  |

| Future                                                                              |                 | AMERICAS                  | 0                                                                                                        | 2020-03-10           | Order  |  |  |  |  |  |  |

| Avnet                                                                               |                 | EMEA                      | 180                                                                                                      | 2020-03-10           | Order  |  |  |  |  |  |  |

| Digikey                                                                             |                 | GLOBAL                    | 30                                                                                                       | 2020-03-11           | Order  |  |  |  |  |  |  |

| Mouser                                                                              |                 | GLOBAL                    | 144                                                                                                      | 2020-03-10           | Order  |  |  |  |  |  |  |

See https://www.nxp.com/part/MIMX8MQ6DVAJZAB#/ (last visited March 11, 2020).

104. NXP has known of the Hall 340 Patent and has been on notice of its infringement of the Hall 340 Patent since at least September 12, 2019, when Bell Semic provided a claim chart showing the NXP MIMX8MQ6DVA as infringing and exemplary of NXP's infringement of the Hall 340 Patent. On February 21, 2020, Bell Semic sent a letter to NXP further identifying the MCIMX6QP4AVT1AA, LS1088AXN7Q1A, and MPC8543VJANGD as exemplary of NXP's infringement of the Hall 340 Patent. NXP has not substantively responded in any way to the infringement allegations in this claim chart or Bell Semic's further identification of infringing products.

# Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 31 of 133

105. To the extent applicable, the requirements of 35 U.S.C. § 287 have been met with respect to the Hall 340 Patent at least because Bell Semic provided NXP with written notice of its infringement as detailed above.

NXP, knowing its products infringe the Hall 340 Patent and with specific intent 106. for others to infringe the Hall 340 Patent, has induced infringement of, and continues to induce infringement of, one or more claims of the Hall 340 Patent under 35 U.S.C. § 271(b), either literally and/or under the doctrine of equivalents, at least by actively inducing others, including its OEMS, foundry suppliers, package assemblers, distributors, customers, end-users, and/or other third parties, to make, use, sell, offer to sell, and/or import in or into the United States without authorization the Hall 340 Accused Products, as well as products containing the same. NXP knowingly and intentionally instructs its customers, OEMs, foundry suppliers, package assemblers, distributors, and/or other third parties to infringe at least through user manuals, product documentation, and other materials, including without limitation those located on NXP's website. NXP actively and knowingly aids and abets infringement through the use, importation, sale, and/or offers for sale by its customers and downstream distributors and through the use by end-users of the products incorporating the Hall 340 Accused Products in the United States. NXP knows, and has known since at least September 12, 2019, that the Hall 340 Accused Products infringe the Hall 340 Patent, and purposefully and knowingly sells and offers to sell the Hall 340 Accused Products to its customers with the knowledge and expectation that the Hall 340 Accused Products and/or products containing the same will enter the United States market, where they will be imported, used, sold, and offered for sale by its customers and downstream distributors.

#### Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 32 of 133

NXP further induced infringement by encouraging its customers, downstream 107. distributors, OEMs, and other end-users of the Hall 340 Accused Products and/or products incorporating the Hall 340 Accused Products in the United States by marketing the Hall 340 Accused Products in the United States; providing information such as detailed datasheets supporting use of the Hall 340 Accused Products that promote their features, specifications, and applications; providing design, layout, and power requirements for the Hall 340 Accused Products; providing technical documentation for the Hall 340 Accused Products including application notes, user guides, and reference manuals describing how to implement, optimize, and test applications; providing design and development tools (such as integrated development environment software); providing support and training through NXP Community; and by promoting the incorporation of the Hall 340 Accused Products into end-user products by providing for its customers reference designs; commercial support and engineering services; hardware, software, and development tools; and robust customer support. In addition to these resources, NXP also provides numerous support resources for the customers of its Hall 340 Accused Products, including live training and video.

108. NXP USA has contributed to the infringement of, and continues to contribute to the infringement of, one or more claims of the Hall 340 Patent under 35 U.S.C. § 271(c), either literally and/or under the doctrine of equivalents, at least by selling, offering to sell, and/or importing in or into the United States the Hall 340 Accused Products, which constitute a material part of the invention of the Hall 340 Patent, knowing the Hall 340 Accused Products to be especially made or especially adapted for use in infringement of the Hall 340 Patent, and not a staple article or commodity of commerce suitable for substantial non-infringing use.

## Case 1:20-cv-00611-ADA Document 30 Filed 09/30/20 Page 33 of 133

109. Bell Semic has sustained and is entitled to recover damages as a result of NXP's past and continuing infringement, in an amount adequate to compensate for NXP's infringement, but in no event less than a reasonable royalty for the use made of the invention, together with interest and costs as fixed by the Court.

NXP's infringement of the Hall 340 Patent is and has been knowing, deliberate, 110. and willful. NXP learned of its infringement of the Hall 340 Patent no later than September 12, 2019. As detailed above, on September 12, 2019, Bell Semic provided a claim chart showing the NXP MIMX8MQ6DVA as infringing and exemplary of NXP's infringement of the Hall 340 Patent. On February 21, 2020, Bell Semic sent a letter to NXP further identifying 3 additional NXP products as exemplary of NXP's infringement of the Hall 340 Patent. NXP has not substantively responded in any way to the infringement allegations in this claim chart or Bell Semic's further identification of infringing products. Despite these efforts, and knowing that it was willfully infringing the Hall 340 Patent, NXP continued and continues to commit acts of direct and indirect infringement despite knowing its actions constitute infringement of the valid and enforceable Hall 340 Patent, despite a risk of infringement that was known or so obvious that it should have been known to NXP, and/or even though NXP otherwise knew or should have known that its actions constituted an unjustifiably high risk of infringement of that valid and enforceable patent. Under these circumstances, NXP's conduct is and has been egregious. NXP's knowing, deliberate, and willful infringement of the Hall 340 Patent entitles Bell Semic to increased damages under 35 U.S.C. § 284, and attorney fees and costs from prosecuting this action under 35 U.S.C. § 285.

# COUNT 2

# Willful Infringement of U.S. Patent No. 8,288,269 (Hall 269 Patent)

111. Plaintiff re-alleges and incorporates by reference the allegations in the foregoing paragraphs as if fully set forth herein.

112. The Hall 269 Patent is generally related to methods for avoiding parasitic capacitance in an integrated circuit package, such as an integrated circuit package substrate that has a first and an additional electrically conductive layer separated from each other by an electrically insulating layer, a contact pad formed in the first electrically conductive layer for making a direct connection between the integrated circuit package substrate and a printed circuit board, and a cutout formed in the additional electrically conductive layer that encloses an area that completely surrounds the contact pad for avoiding parasitic capacitance between the additional electrically conductive layer and the printed circuit board. (*See* Hall 269 Patent, Abstract.)

113. Parasitic capacitance results when parts in an electronic circuit are in close proximity to each other, potentially leading to interference with the input or output to a device. Reducing parasitic capacitance has become increasingly necessary as integrated circuit devices, particularly high-speed devices, have included more external connections (for example, the NXP MIMX8MQ6DVA described below includes 621 pins) while packages decrease in size. In order to reduce parasitic capacitance in the multi-layer packages for these integrated circuits, the Hall 269 Patent teaches the formation of cutouts over the electrical contacts in electrically conductive layers so that there would be substantially no overlap between the electrical contacts and metal in the electrically conductive layers.

114. The Hall 269 Patent contains 2 independent claims and 20 total claims, covering various methods. Claim 1 reads:

A method, comprising steps of:

forming a first electrically conductive layer including a plurality of rows of contact pads;

forming an electrically insulating layer on the first electrically conductive layer; and

forming a second electrically conductive layer over the electrically insulating layer such that there is no intermediate conductive layer between the first and second electrically conductive layers, the second electrically conductive layer comprising metal and a plurality of cutouts wherein each cutout encloses an electrically insulating area within the second electrically conductive layer and wherein each electrically insulating area completely overlaps a corresponding one of the contact pads such that there is substantially no overlap of the rows of contact pads with metal in the second electrically conductive layer.

115. NXP USA has directly infringed, and continues to directly infringe, one or more

claims of the Hall 269 Patent, either literally or under the doctrine of equivalents, under 35

U.S.C. § 271(a) by making products in the United States without authorization using methods

covered by one of more claims of the Hall 269 Patent, and/or NXP USA has directly infringed,

and continues to directly infringe, one or more claims of the Hall 269 Patent, either literally or

under the doctrine of equivalents, under 35 U.S.C. § 271(g) at least by using, selling, offering to

sell, and/or importing in or into the United States products that are made by a process using one

or more claims of the Hall 269 Patent (e.g., claims 1, 4, 7, and 10-13). Such products

manufactured using these infringing methods include, but are not limited to:

- NXP products with at least one metal layer, proximate to another metal layer having electrical contacts, that has cutouts;

- NXP's MIMX8MQ6DVA, an NXP i.MX 8M Quad processor that includes a quad Arm Cortex-A53 core for use in consumer products;

- NXP's MCIMX6QP4AVT1AA, an NXP i.MX 6 series 32-bit MPU that includes a quad Arm Cortex-A9 core;

- NXP's LS1088AXN7Q1A, an NXP QorIQ Layerscape communications processor;

- NXP's MPC8543VJANGD, an NXP PowerQUICC III processor with high-speed connectivity; and

- NXP's devices that are variants of the above-identified products; (collectively "Hall 269 Accused Products").

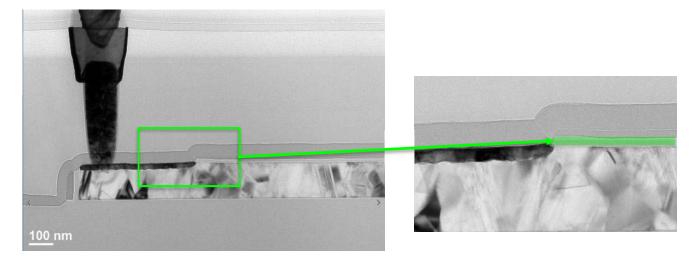

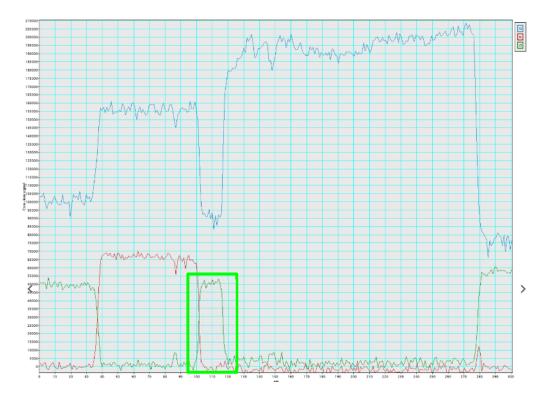

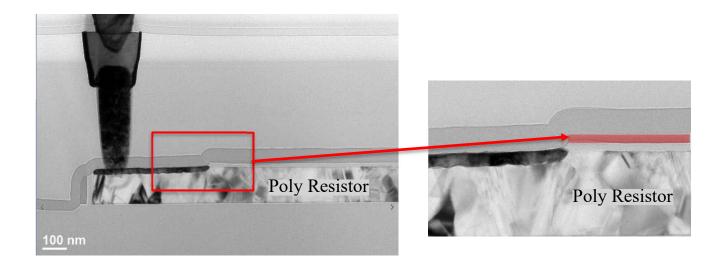

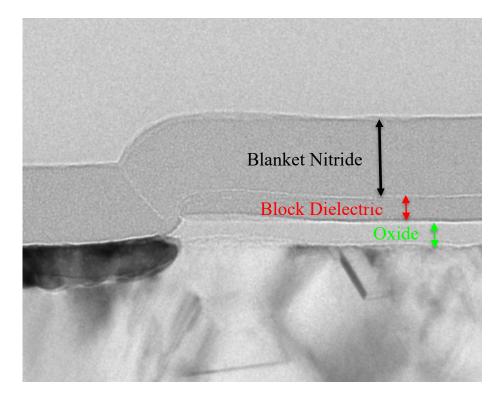

- 116. By way of example only, the process of manufacturing the NXP