## IN THE UNITED STATES DISTRICT COURT FOR THE EASTERN DISTRICT OF TEXAS MARSHALL DIVISION

LIBERTY PATENTS LLC,

Plaintiff,

v.

TEXAS INSTRUMENTS, INC.,

Defendant.

CIVIL ACTION NO. 2:21-cv-50

ORIGINAL COMPLAINT FOR PATENT INFRINGEMENT

JURY TRIAL DEMANDED

## **ORIGINAL COMPLAINT FOR PATENT INFRINGEMENT**

Plaintiff Liberty Patents LLC ("Liberty Patents" or "Plaintiff") files this original complaint against Defendant Texas Instruments, Inc. ("TI" or "Defendant"), alleging, based on its own knowledge as to itself and its own actions and based on information and belief as to all other matters, as follows:

## **PARTIES**

1. Liberty Patents is a limited liability company formed under the laws of the State of Texas, with its principal place of business at 2325 Oak Alley, Tyler, Texas, 75703.

2. Defendant Texas Instruments, Inc. is a company organized and existing under the laws of the state of Delaware. Texas Instruments, Inc. may be served with process through its registered agent, CT Corporation System at 1999 Bryan St., Suite 900, Dallas, Texas, 75201.

3. TI is "a global semiconductor company that designs, manufactures, tests and sells analog and embedded processing chips."<sup>1</sup> It "design[s], manufacture[s], test[s] and sell[s] analog and embedded semiconductors" for "nearly 100,000 customers around the globe."<sup>2</sup> It has a

<sup>&</sup>lt;sup>1</sup> See <u>https://www.ti.com/about-ti/company/overview.html</u>.

<sup>&</sup>lt;sup>2</sup> See <u>https://www.ti.com/about-ti/company/what-we-do.html</u>.

## Case 2:21-cv-00050-JRG Document 1 Filed 02/12/21 Page 2 of 124 PageID #: 2

portfolio of about 80,000 products with 14 manufacturing sites worldwide, operating "10 wafer fabs, seven assembly and test factories, and multiple bump and probe facilities."<sup>3</sup>

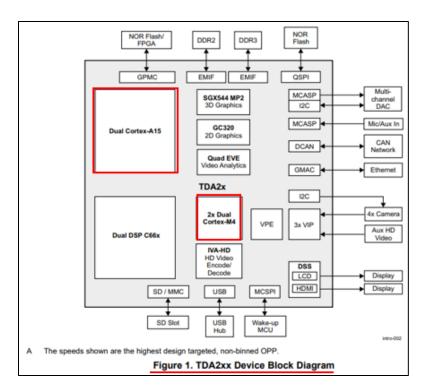

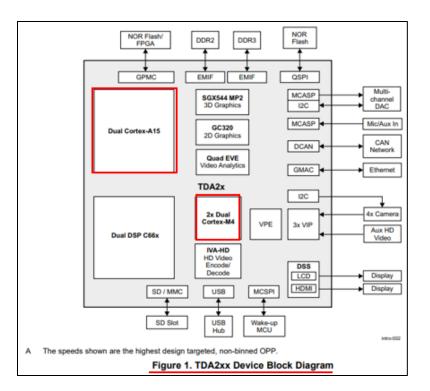

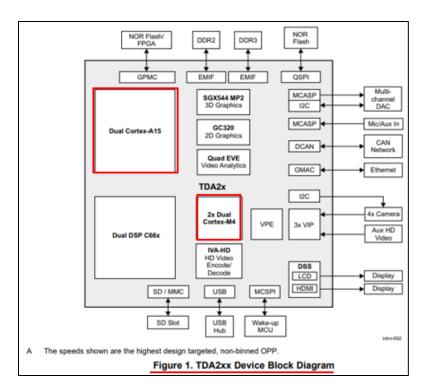

## JURISDICTION AND VENUE

4. This is an action for infringement of a United States patent arising under 35 U.S.C. §§ 271, 281, and 284–85, among others. This Court has subject matter jurisdiction of the action under 28 U.S.C. § 1331 and § 1338(a).

5. This Court has personal jurisdiction over TI pursuant to due process and/or the Texas Long Arm Statute because, *inter alia*, (i) TI has done and continues to do business in Texas; (ii) TI has committed and continues to commit acts of patent infringement in the State of Texas, including making, using, offering to sell, and/or selling accused products in Texas, and/or importing accused products into Texas, including by Internet sales and/or sales via retail and wholesale stores, inducing others to commit acts of patent infringement in Texas, and/or committing at least a portion of any other infringements alleged herein in Texas, and (iii) TI is registered to do business in Texas.

6. Venue is proper in this district under 28 U.S.C. § 1400(b). Venue is further proper because TI has committed and continues to commit acts of patent infringement in this district, including making, using, offering to sell, and/or selling accused products in this district, and/or importing accused products into this district, including by Internet sales and/or sales via retail and wholesale stores, inducing others to commit acts of patent infringement in this district, and/or committing at least a portion of any other infringements alleged herein in this district.

7. TI also has a regular and established place of business in this district, including at least at 6412 US-75, Sherman, Texas, 75090:

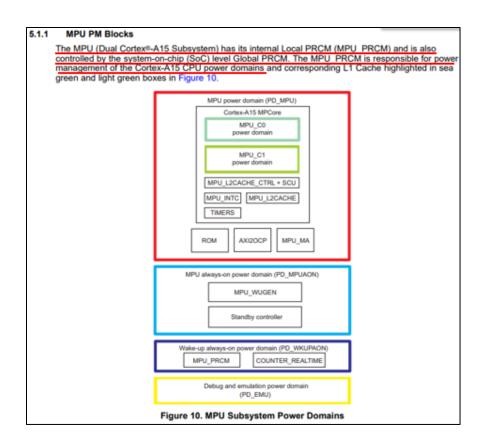

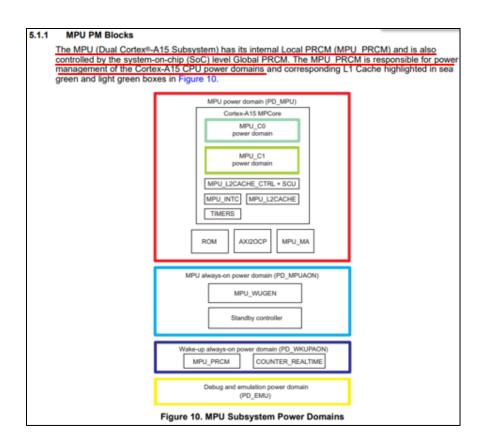

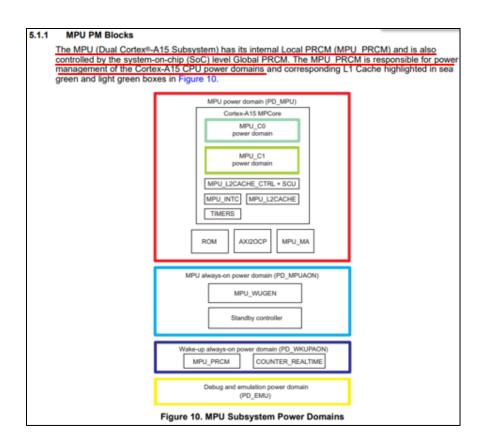

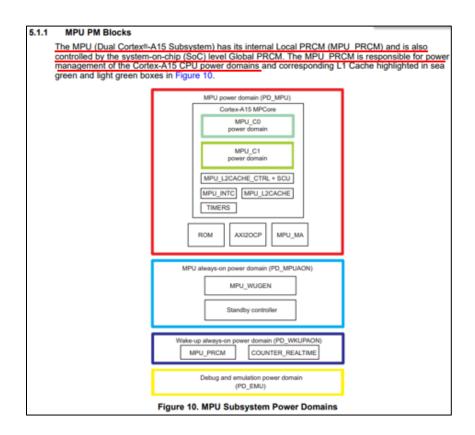

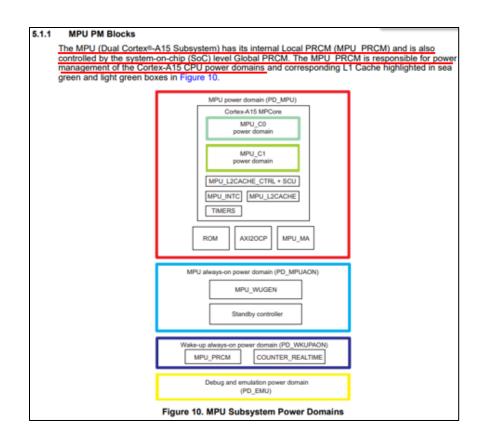

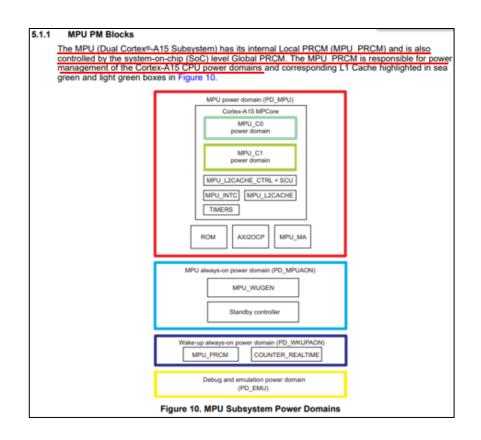

Source: <u>https://goo.gl/maps/QsyZgk86RKkHp7qb8</u>; <u>https://goo.gl/maps/rBda8qr16vW3LPHa8</u>.

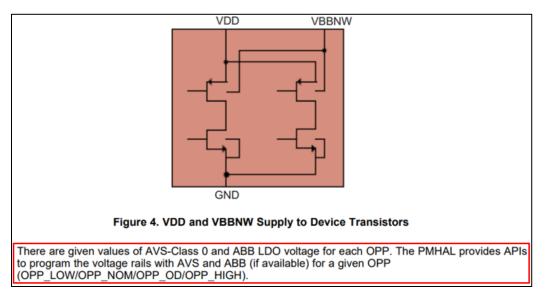

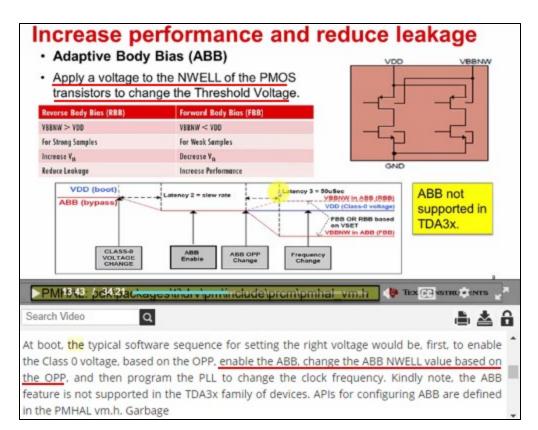

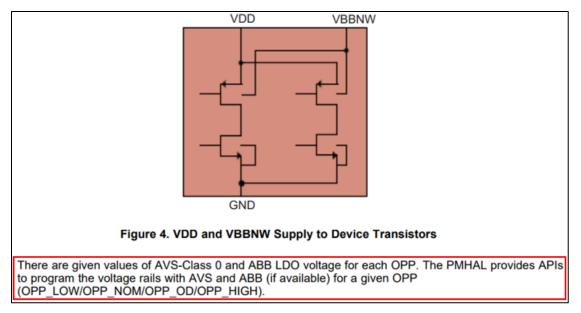

#### **BACKGROUND**

8. The patents-in-suit describe key improvements in electronic circuitry relating to the enhancement of processors through reduced power consumption, increased processing, and greater performance.

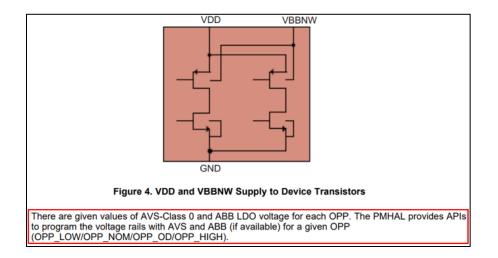

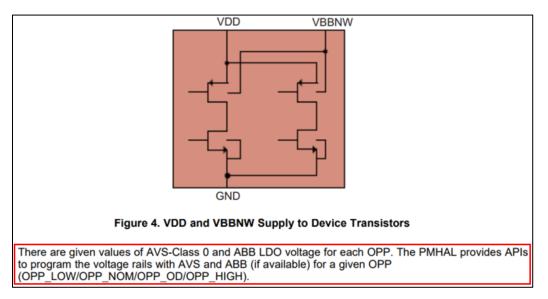

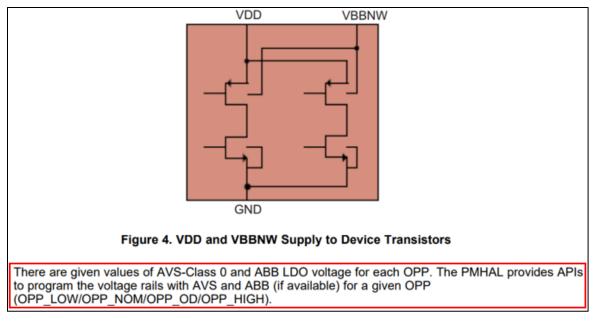

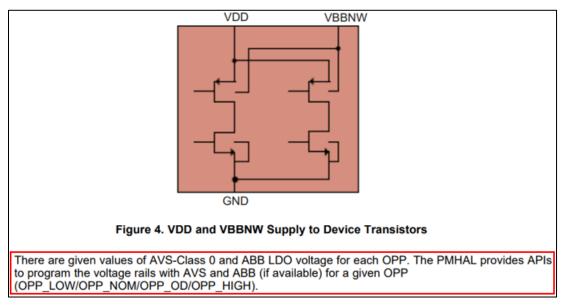

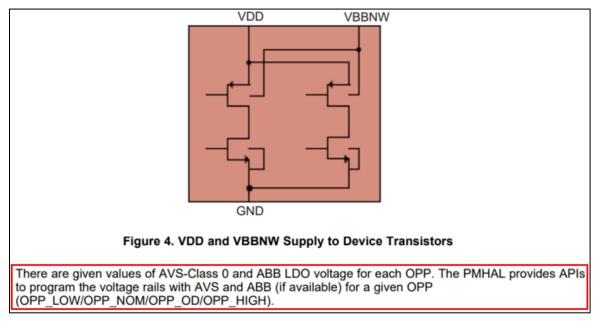

9. U.S. Patent Nos. 7,509,504 ("the '504 Patent"), 8,127,156 ("the '156 Patent"), and 8,458,496 ("the '496 Patent") are part of the same family of patents, which generally relates to body biasing voltages used in integrated circuits (ICs). The patents teach application of body biasing techniques that improve circuit performance and reduce power consumption in one or more power modes. Specifically, they disclose systems and methods for generating body biasing voltages so that a processor can operate with increased power savings. For example, the family of patents describes techniques for using body biasing voltages to decrease power consumption during high performance applications. Other examples disclose use of body biasing voltages during low power modes.

10. The use of body biasing voltages in ICs has become an increasingly necessary design feature in many applications today. Coupled with the explosive demand for ICs over the last few years, the more stringent requirement that ICs consume less and less power has focused the industry towards using body biasing voltages. Body biasing voltage techniques are now being used in applications ranging from automotive technologies to industrial IoT devices. Whether an application requires high performance circuitry or ultra-low power modes (or both), body biasing techniques have become essential.

11. The technology described by the '504 Patent, the '156 Patent, and the '496 Patent was developed by engineers at Transmeta Corp. Transmeta was a technology company formed in 1995 and best known for designing high performance processors, such as the Crusoe and the Efficeon in the early 2000s. In particular, Transmeta's major focus was on developing low

4

#### Case 2:21-cv-00050-JRG Document 1 Filed 02/12/21 Page 5 of 124 PageID #: 5

power, high performance ICs. To achieve such high power savings, one of the major techniques used by Transmeta engineers was to apply body biasing voltages to its ICs.

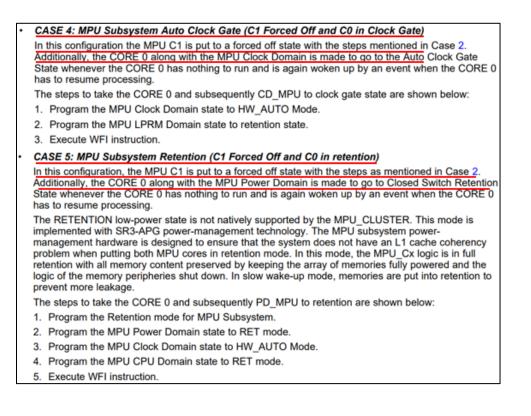

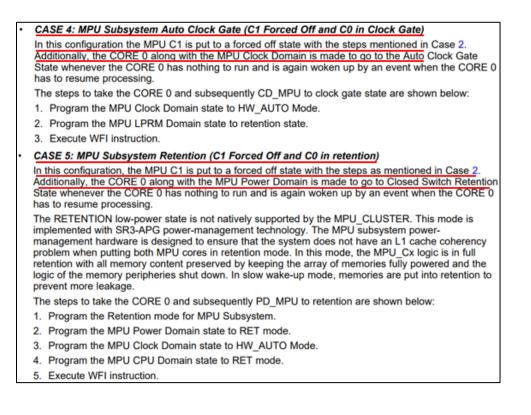

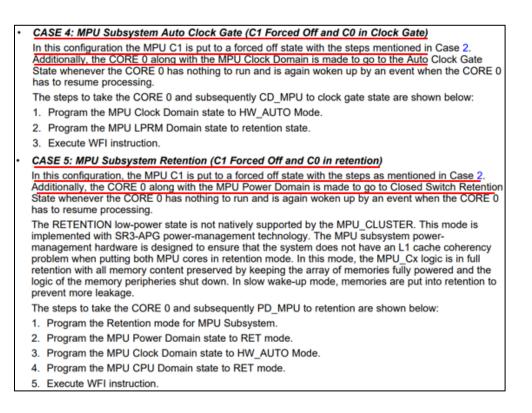

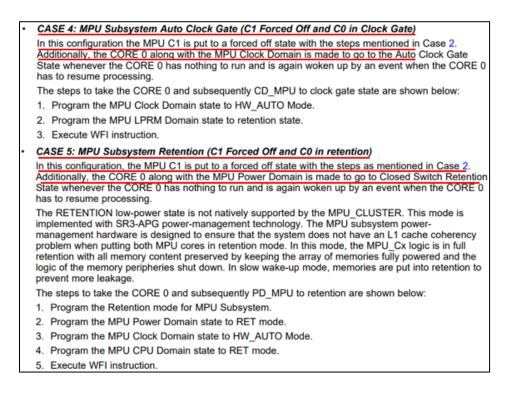

12. Industry experts have recognized the technological innovation of Transmeta's processors, and some have noted that Transmeta's energy-saving processors were ahead of their time.<sup>4</sup> The inventions disclosed in these patents are extremely important to multiple industries, and have been cited by major technology companies and processor developers like Canon, Freescale Semiconductor (now part of NXP), Nvidia, Packet Digital, and Smart Technologies (now part of Foxconn).

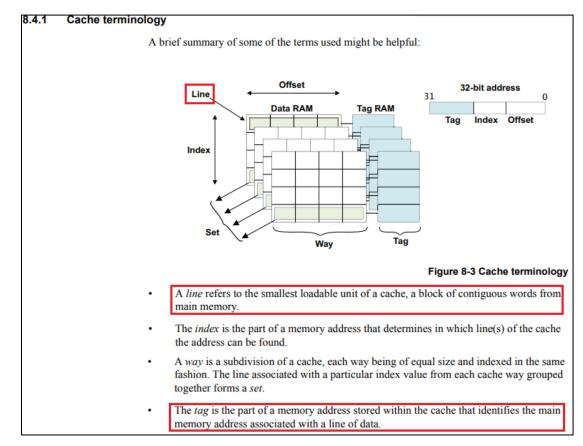

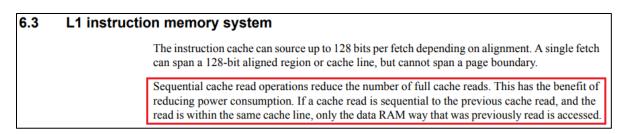

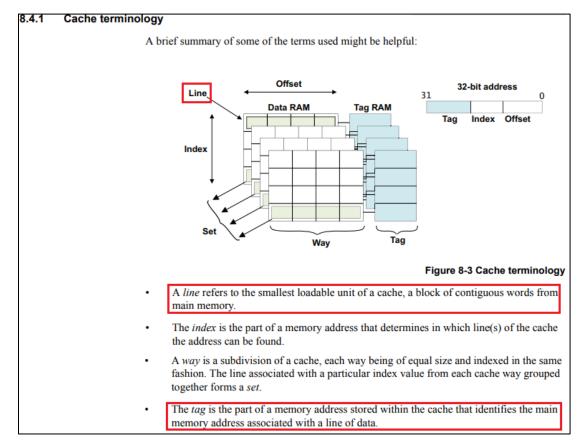

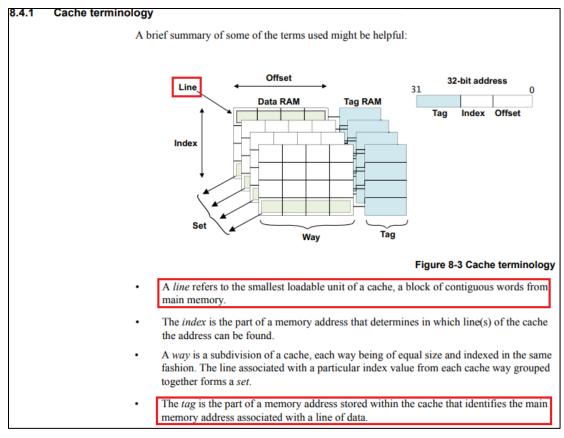

13. U.S. Patent No. 6,535,959 ("the '959 Patent") covers technology used in a wide array of electronic devices and applications, including computer processors for mobile and automotive industries, SoCs, graphics display controllers, LCD systems, etc. More particularly, it describes techniques for more efficient handling of computer instructions in processors for faster processing.

14. In particular, the '959 Patent discloses a processor that includes a set-associative instruction cache comprising multiple blocks. Claim 1 of the '959 patent, as an example, is directed to a processor that generates a power reduction signal, which indicates whether the subsequent instruction to be executed resides in the same block of the instruction cache as the current instruction that is being executed. This advantageously allows, for example, the processor to read consecutive instructions (or instructions that are in the same block) quickly,

<sup>&</sup>lt;sup>4</sup> See, e.g., Chip Hall of Fame: Transmeta Corp. Crusoe Processor, IEEE Spectrum (June 30, 2017) ("Ahead of its time, this chip heralded the mobile era when energy use, not processing power, would become the most important spec."), <u>https://spectrum.ieee.org/tech-history/silicon-revolution/chip-hall-of-fame-transmeta-corp-crusoe-processor</u>.

## Case 2:21-cv-00050-JRG Document 1 Filed 02/12/21 Page 6 of 124 PageID #: 6

without multiple additional steps. The novel system results in a processor with increased operating speed and decreased power consumption.

15. The invention described in the '959 Patent was the result of research conducted by two inventors at Conexant Systems, Inc., which was—at the time—the world's largest, standalone communications-IC company. Conexant, itself, was a spin-off from the semiconductor division of the well-known and well-regarded Rockwell International Corp. Conexant was known as a leading supplier of innovative semiconductor solutions for imaging, audio, embedded modem, and video surveillance applications.<sup>5</sup> Recently, Conexant was acquired by Synaptics, the leading developer of human interface solutions for over \$300 million. Since its formation, Conexant has been an innovator in the semiconductor field (and others) with more than a thousand patents assigned to it.

The '959 Patent has been cited by multiple technology companies—as recently as

2017—including, Apple, ARM, Fujitsu, Hewlett-Packard, Honeywell, IBM, Intel, Panasonic

(Matsushita), Oracle, Samsung, STMicroelectronics, Toshiba, and Transmeta.

## COUNT I

## **DIRECT INFRINGEMENT OF U.S. PATENT NO. 7,509,504**

17. On March 24, 2009, U.S. Patent No. 7,509,504 ("the '504 Patent") was duly and legally issued by the United States Patent and Trademark Office for an invention entitled "Systems and Methods for Control of Integrated Circuits Comprising Body Biasing Systems."

<sup>&</sup>lt;sup>5</sup> See Conexant's Audio Solution Named CES Innovations 2011 Awards Honoree, BUSINESS WIRE (Nov. 9, 2010),

http://finance.sunnyvale.com/camedia.sunnyvale/news/read/15498866/conexant%E2%80%99s\_a udio solution named ces innovations 2011 awards honoree.

18. Liberty Patents is the owner of the '504 Patent, with all substantive rights in and to that patent, including the sole and exclusive right to prosecute this action and enforce the '504 Patent against infringers, and to collect damages for all relevant times.

19. TI made, had made, used, imported, provided, supplied, distributed, sold, and/or offered for sale products and/or systems including, for example, TI's TDA2x System-on-Chip devices and other products<sup>6</sup> that are capable of applying body biasing voltages during a power mode of a processor or other integrated circuit ("accused products"):

# **TDA2x ADAS System-on-Chip**

🔱 TEXAS INSTRUMENTS

<sup>&</sup>lt;sup>6</sup> See, e.g., TI AM5706, AM5708, AM5716, AM5718, AM5718-HIREL, AM5726, AM5728, AM5729, AM5746, AM5748, AM5749, DRA710, DRA712, DRA714, DRA716, DRA718, DRA722, DRA724, DRA725, DRA726, DRA744, DRA745, DRA746, DRA74P, DRA750, DRA756, DRA75P, DRA76P, DRA77P, DRA790, DRA791, DRA793, DRA797, OMAP4430, OMAP4460, OMAP4470, OMAP5430, OMAP5432, TDA2E, TDA2EG-17, TDA2HF, TDA2HG, TDA2HV, TDA2LF, TDA2P-ABZ, TDA2P-ACD, TDA2SA, TDA2SG, TDA2SX, TMDXIDK5718, TMDSEVM572X, TMDSIDK572, TMDSIDK574, D3-3P-ADAS-DK, D3-3P-TDAX-DK, DRA71XEVM, DRA72XEVM, DRA79XEVM, 703664-1001, 705851-1001, 705852-1001, DRA76XP-DRA77XP-TDA2PX-ACD-CPUBOARD, J6EVM5777, OMAP5432-EVM, TDA2EXEVM, TDA2PXEVM, EVM5777BG-03-00-00, EVM5777G-03-40-00, EVM5777VISION-V2-0, etc.

| High-Speed Inte                                                                                                 | erconnect 🛛 🚸 28 nm                                           |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|

|                                                                                                                 | Vision AccelerationPac<br>O Up to quad EVEs                   |  |  |  |

|                                                                                                                 | Video Front End<br>3 Video input ports for up<br>to 6 cameras |  |  |  |

| System Mailbox System ×13                                                                                       | Display Subsystem                                             |  |  |  |

| Up to 2.5MB L3 RAM w/ ECC                                                                                       | Overlay<br>GFX pipeline<br>Video pipeline                     |  |  |  |

| DDR2/3 32b<br>w/ ECC DDR2/3 32b                                                                                 | Video Codec Accelerator<br>IVA HD 1080p video                 |  |  |  |

| System Services<br>EDMA WDT 15 Timers                                                                           | Graphics Engine<br>Up to dual SGX544                          |  |  |  |

| McASP JTAG Connectivity and I/O GPMC QSPI<br>PCIe GMAC UART DCAN SPI I <sup>2</sup> C NAND/<br>x10 x2 x4 x5 NOR |                                                               |  |  |  |

▲ Figure 1. Block diagram for TDA2x SoC

https://www.ti.com/lit/ml/sprt681/sprt681.pdf?ts=1597386693056&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 1)

20. By doing so, TI has directly infringed (literally and/or under the doctrine of equivalents) at least Claims 1 and 9 of the '504 Patent. TI's infringement in this regard is ongoing.

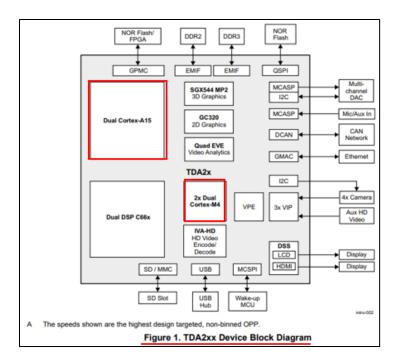

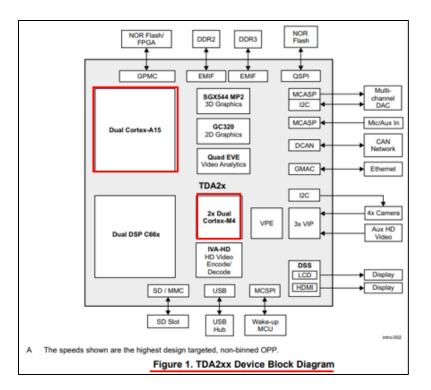

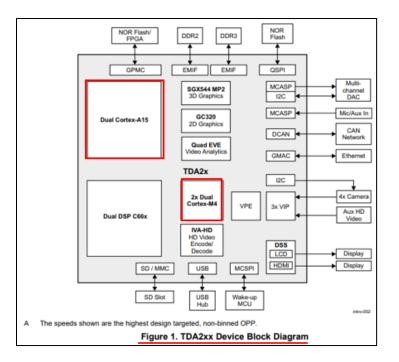

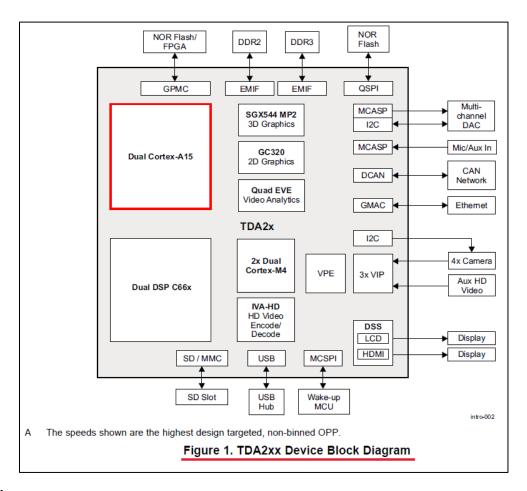

21. TI's TDA2x System-on-Chip devices are exemplary accused products. The devices include a computer system.

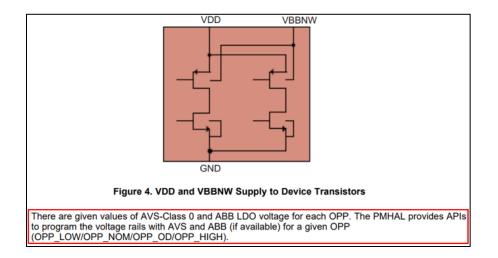

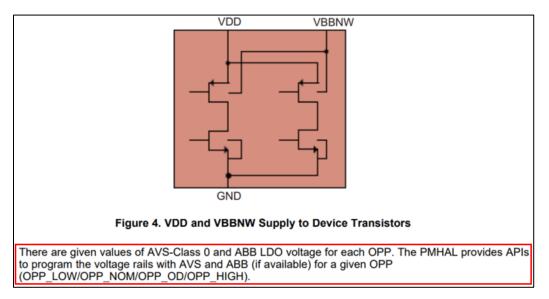

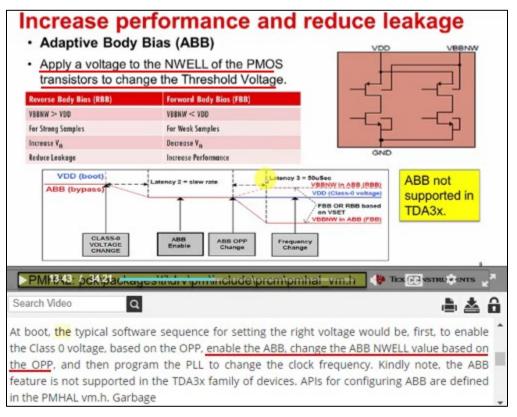

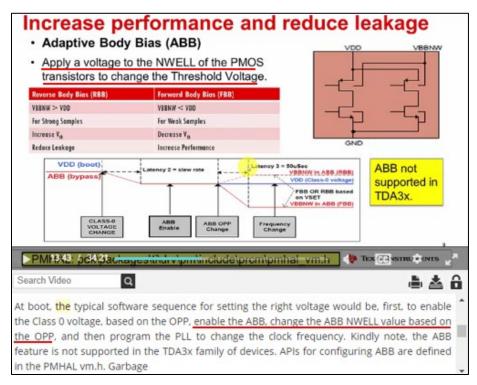

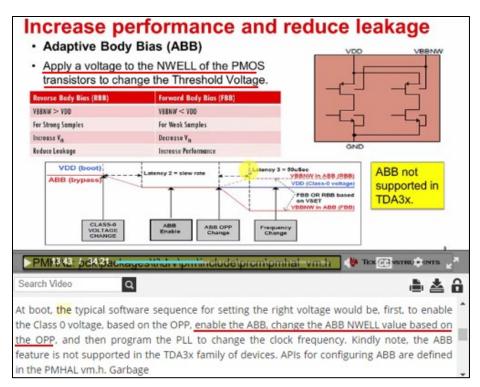

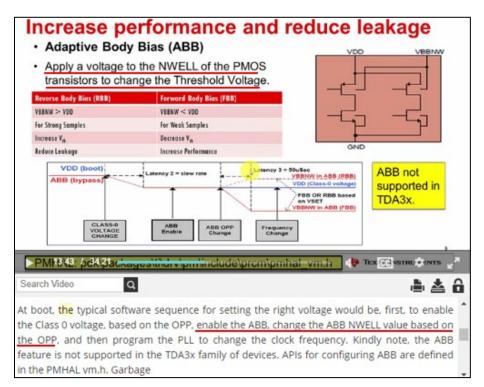

22. For example, TI's TDA2x System-on-Chip devices include a dual core processor module along with different memory elements and peripherals ("computer system"). The devices support Adaptive Body Bias (ABB), which can apply a forward or reverse body bias voltage to the transistors of the device using ABB.

# **TDA2x ADAS System-on-Chip**

## 🚸 Texas Instruments

#### Source:

https://www.ti.com/lit/ml/sprt681/sprt681.pdf?ts=1597386693056&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 1)

#### TDA2x (Vision 28) ADAS Application Processor

#### Overview

TI's new TDA2x Vision 28 system-on-chip (SoC) is a highly optimized and scalable device family designed to meet the requirements of leading advanced driver assistance systems (ADAS). The TDA2x family empowers broad ADAS applications in today's automobiles by integrating an optimal mix of performance, low power and ADAS vision-analytics processing that aims to facilitate a more autonomous and collision-free driving experience.

The TDA2x SoC makes possible sophisticated embedded vision technology, providing the industry's broadest range of ADAS applications such as front camera, park assist, surround view and sensor fusion on a single architecture. Front-camera applications include high-beam assist, lane-keep assist,

#### TDA2x

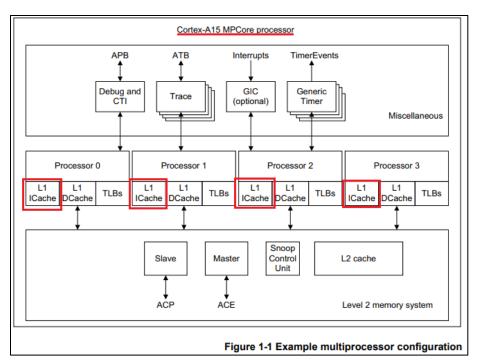

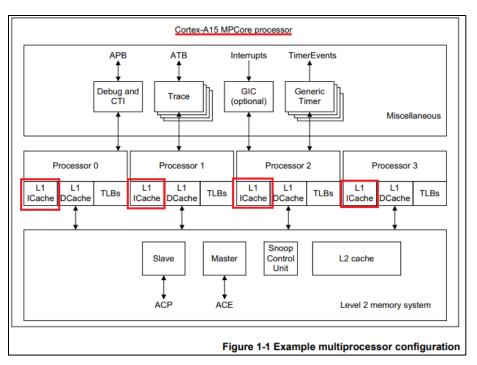

The TDA2x SoC incorporates a heterogeneous, scalable architecture that includes a mix of TI's fixed- and floatingpoint TMS320C66x digital signal processor (DSP) generation cores, Vision AccelerationPac, <u>ARM Cortex-A15 MPCore</u> and dual Cortex-M4 processors. The integration of video for decoding multiple video streams over Ethernet audio-video bridging (AVB) networks, along with graphics accelerators for rendering virtual views, allows for a 3-D viewing experience. And the TDA2x SoC integrates a host of peripherals, including multicamera interfaces (both parallel and serial) for LVDS-based surround-view systems, displays, CAN and Gigabit Ethernet AVB.

Source: <a href="https://m.eet.com/media/1241324/slyy044.pdf">https://m.eet.com/media/1241324/slyy044.pdf</a> (Page 5)

https://www.ti.com/lit/an/sprac21a/sprac21a.pdf?ts=1597386703137&ref\_url=https%253A%252 F%252Fwww.google.com%252F (Page 6)

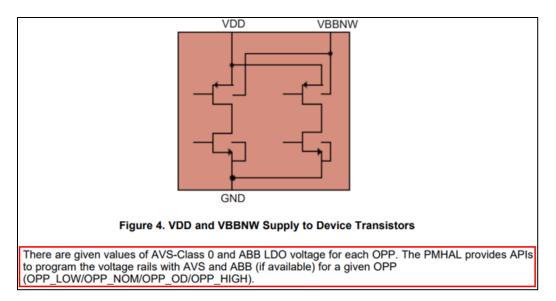

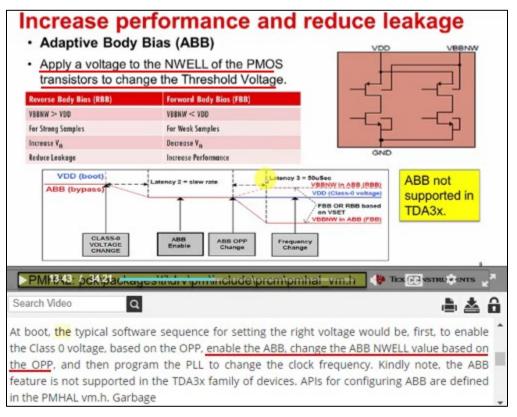

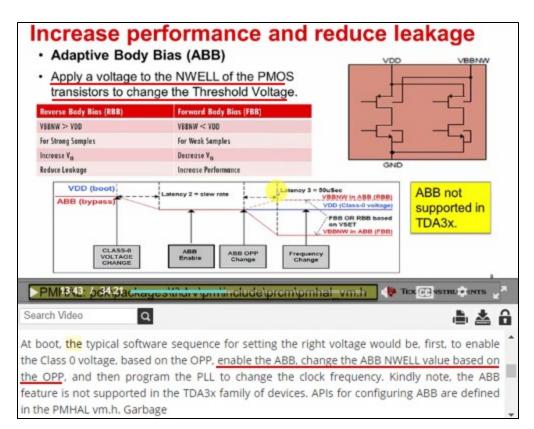

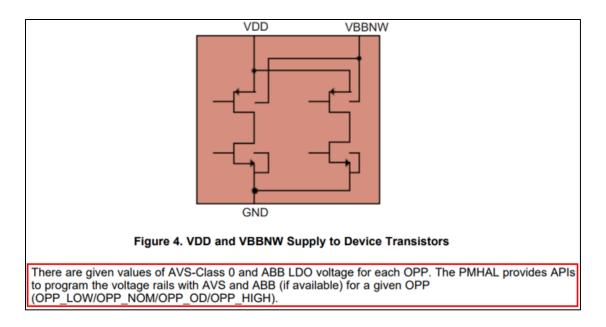

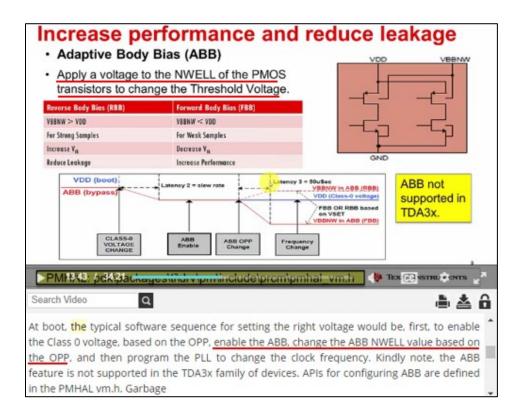

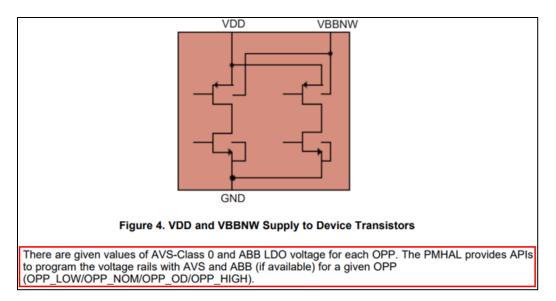

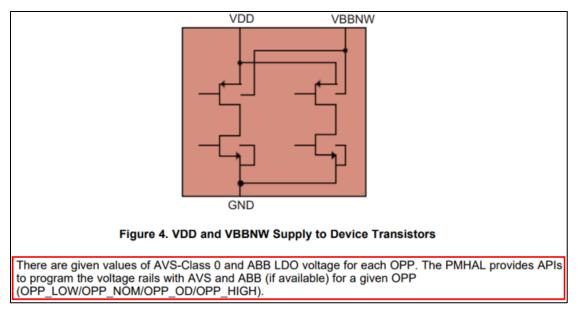

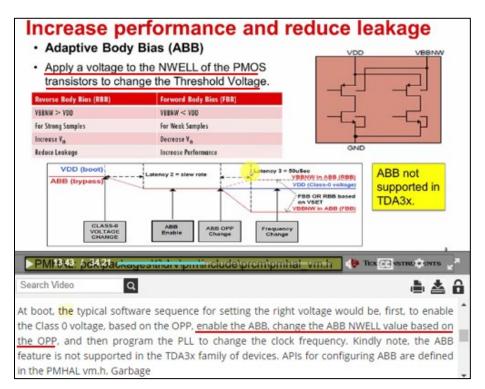

<u>The TDA2xx/TDA2ex family of devices also support Adaptive Body Bias (ABB), which helps control further</u> leakage, improve the performance of the silicon by applying a voltage to the NWELL of the PMOS transistors of the device, and change  $V_{TH}$  of the transistors.

| Table 2. Ada | otive Body | v Bias (AB | B) Impact of | on Strong | and Weak Samples |

|--------------|------------|------------|--------------|-----------|------------------|

|              |            |            |              |           |                  |

| Reverse Body Bias (RBB)  | Forward Body Bias (FBB)  |

|--------------------------|--------------------------|

| VBBNW > VDD              | VBBNW < VDD              |

| For Strong Samples       | For Weak Samples         |

| Increase V <sub>th</sub> | Decrease V <sub>th</sub> |

| Reduce Leakage           | Increase Performance     |

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 5)

23. TI's TDA2x System-on-Chip devices include a plurality of data storage locations

comprising body biasing voltage information corresponding to a plurality of power modes of the

computer system. At least one of the plurality of power modes enables operation of the

computer system at at least two different clock frequencies.

24. For example, TI's TDA2x System-on-Chip devices include a dual core processor module. Further, the System-on-Chip includes an MPU\_PRCM module for power management of the processor. The TDA2x family of devices supports multiple power states (e.g., a power state in which both cores are on, a power state in which one core is forced off, a power state in which one core is forced off and the other core is in retention, etc.).

25. The devices support Adaptive Body Bias (ABB). ABB voltage values are available for each OPP (Operating Performance Point), and therefore, for each power state. The OPP is the operating condition for the device and is defined by the voltage and frequency applied to the processor. The ABB voltage values ("body biasing voltage information") corresponding to the different power states ("plurality of power modes") are stored in Efuse registers ("data storage locations"). A power state changes based on the processor's performance, and each power state is associated with a different clock frequency and/or a different voltage.

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

<u>%252Fwww.google.com%252F</u> (Page 19)

the CPUs for the low-power state. The different power states for the different CPUs in the system, from highest (left most) to lowest (right most), are summarized in Table 10. The following sections dive deep into the power and clock state of the different subsystems and the programming sequence to achieve the desired power state.

| Table 10. Different Power States supported by CPU Subsystems |                        |                   |                                   |                              |                        |

|--------------------------------------------------------------|------------------------|-------------------|-----------------------------------|------------------------------|------------------------|

| CPU Subsystem                                                | Highest Power<br>State |                   |                                   |                              | Lowest Power<br>State  |

| MPU                                                          | On                     | Core 1 Forced Off | Core 1 Forced Off,<br>Core 0 Idle | Subsystem Auto<br>Clock Gate | Subsystem<br>Retention |

| DSP                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

| IPU                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

| EVE                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 18)

| 5.1.2 |                           | MPU PM States                                                                                                                                                                                                                                                                                                                                        |  |

|-------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       | an<br>TD                  | is section discusses the different power states of the MPU subsystem and understands the power down<br>d wake up latencies based on the power savings. Contact your TI representative to get access to the<br>DA2xx/TDA2ex Power Estimation Spread Sheet and analyze the exact power savings for the different<br>pported low power modes.           |  |

|       | •                         | CASE 1: MPU ON (Core 0 (C0) and Core 1 (C1) On)                                                                                                                                                                                                                                                                                                      |  |

|       |                           | In this configuration, the Cortex-A15 CPUs are both alive and running their respective software. This is the highest power consumption configuration and the power consumption is determined by the kind of operations the A15 is performing. The sub-modules in the MPU subsystem are ON and the clocks are enabled for the subsystem and the CPUs. |  |

|       | CASE 2: MPU C1 Forced Off |                                                                                                                                                                                                                                                                                                                                                      |  |

|       |                           | In this configuration, the MPU C1 is forced off and the MPU C0 is alive and running its own software.<br>In this configuration, the MPU C1 logic, L1 Cache is off, the clocks to the MPU C1 are gated and the<br>MPU C1 LPRM shows the CPU to be in power off mode.                                                                                  |  |

|       | •                         | CASE 3: MPU C1 Forced Off and C0 in IDLE                                                                                                                                                                                                                                                                                                             |  |

|       |                           | In this configuration, the MPU C1 is put to a forced off state with the steps as mentioned in Case 2.<br>Additionally the CORE 0 is made to go to IDLE state whenever the CORE 0 has nothing to run and is again woken up by an event when the CORE 0 has to resume processing.                                                                      |  |

|       |                           | The steps to take the CORE 0 to IDLE are shown below:                                                                                                                                                                                                                                                                                                |  |

|       |                           | 1. Program the MPU LPRM Domain state to the desired power state.                                                                                                                                                                                                                                                                                     |  |

|       |                           | 2. Execute WFI instruction.                                                                                                                                                                                                                                                                                                                          |  |

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

## %252Fwww.google.com%252F (Pages 20 and 21)

#### Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

<u>%252Fwww.google.com%252F</u> (Page 23)

<u>The TDA2xx/TDA2ex family of devices also support Adaptive Body Bias (ABB), which helps control further</u> leakage, improve the performance of the silicon by applying a voltage to the NWELL of the PMOS transistors of the device, and change  $V_{TH}$  of the transistors.

#### Table 2. Adaptive Body Bias (ABB) Impact on Strong and Weak Samples

| Reverse Body Bias (RBB) | Forward Body Bias (FBB)  |

|-------------------------|--------------------------|

| VBBNW > VDD             | VBBNW < VDD              |

| For Strong Samples      | For Weak Samples         |

| Increase V <sub>m</sub> | Decrease V <sub>th</sub> |

| Reduce Leakage          | Increase Performance     |

#### Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

## <u>%252Fwww.google.com%252F</u> (Page 5)

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F %252Fwww.google.com%252F

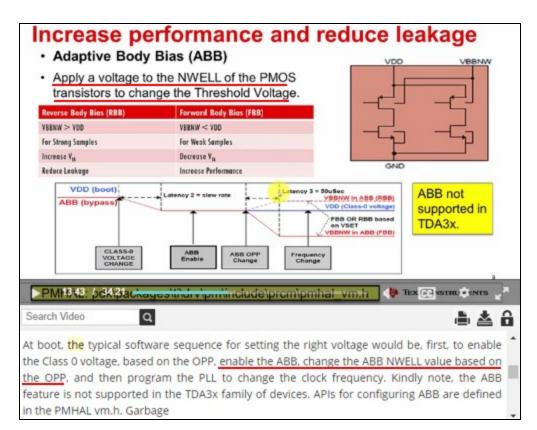

The next step is to register the PMIC operations with PMHAL. In this example, we have registered the Tps65917 with the PMHAL. Once this registration is successful, we set the AVS and the ABB for the corresponding voltage domain and OPP ID using the API PMHALVMSetOpp. This API will reach the AVS EFUSE values and programs the PMIC to set the AVS voltage. Once the AVS has been programmed, it also programs the appropriate NWELL voltage, as read from the ABB EFUSE.

Source: <u>https://training.ti.com/introduction-adas-power-management-software</u> (at 17:07)

| <ul> <li>ti,abb_info: An array of 6-tuples u32 items providing information about ABB<br/>configuration needed per operational voltage of the device.</li> </ul> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| o 1 1 o                                                                                                                                                         |

| Each item consists of the following in the same order:                                                                                                          |

| volt: voltage in uV - Only used to index ABB information.                                                                                                       |

| ABB mode: one of the following:                                                                                                                                 |

| 0-bypass                                                                                                                                                        |

| 1-Forward Body Bias(FBB)                                                                                                                                        |

| 3-Reverse Body Bias(RBR)                                                                                                                                        |

| efuse: (see Optional properties)                                                                                                                                |

| RBB enable efuse Mask: (See Optional properties)                                                                                                                |

| FBB enable efuse Mask: (See Optional properties)                                                                                                                |

| Vset value efuse Mask: (See Optional properties)                                                                                                                |

Source: https://www.kernel.org/doc/Documentation/devicetree/bindings/regulator/ti-abb-

## regulator.txt

ti,abb\_opp\_sel: Addendum to the description in required properties

efuse: Mandatory if 'efuse-address' register is defined. Provides offset

from efuse-address to pick up ABB characteristics. Set to 0 if

'efuse-address' is not defined.

RBB enable efuse Mask: Optional if 'efuse-address' register is defined.

'ABB mode' is force set to RBB mode if value at "efuse-address"

+ efuse maps to RBB mask. Set to 0 to ignore this.

FBB enable efuse Mask: Optional if 'efuse-address' register is defined.

'ABB mode' is force set to FBB mode if value at "efuse-address"

+ efuse maps to FBB mask. Set to 0 to ignore this.

FBB enable efuse Mask: Optional if 'efuse-address' register is defined.

'ABB mode' is force set to FBB mode if value at "efuse-address"

+ efuse maps to FBB mask (valid only if RBB mask does not match)

Set to 0 to ignore this.

Vset value efuse Mask: Mandatory if ldo-address is set. Picks up from

efuse the value to set in 'ti,ldovbb-vset-mask' at ldo-address.

Source: https://www.kernel.org/doc/Documentation/devicetree/bindings/regulator/ti-abb-

## regulator.txt

## 3.3 Setting the Frequency of Modules

Based on the expected CPU operations, the CPUs in the system can be configured to operate at different frequencies as determined by the OPP and speed bin of the device. Setting the OPP of the CPU involves setting the DPLLs to provide the desired clock frequency and setting the PMIC to provide the desired voltage as determined in the AVS EFuse registers. Similarly, different peripherals require different

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

<u>%252Fwww.google.com%252F</u> (Page 9)

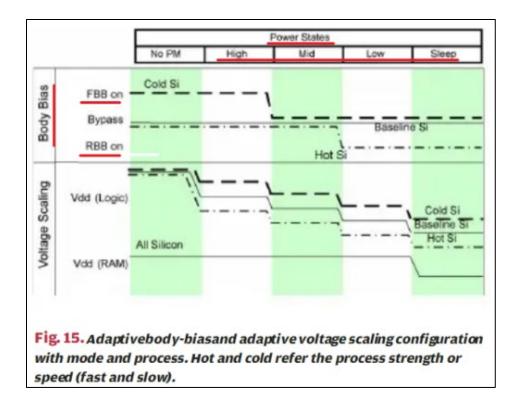

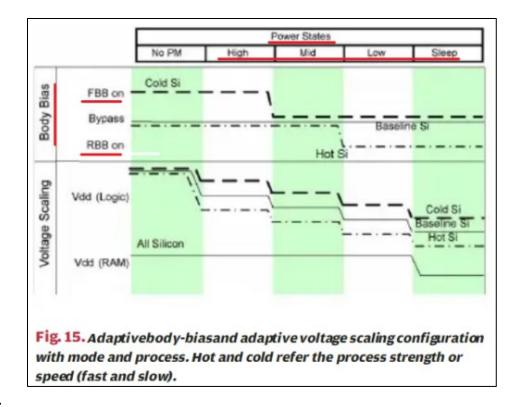

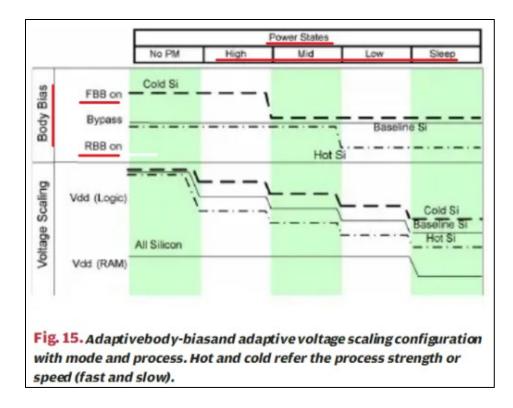

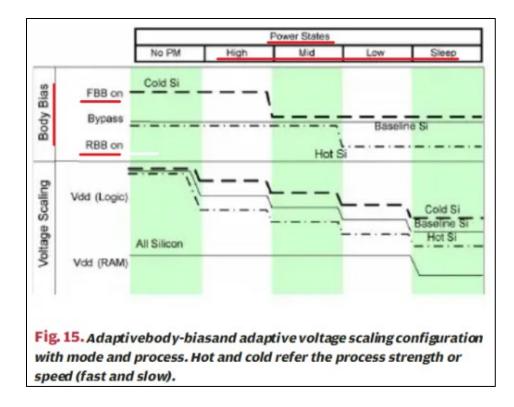

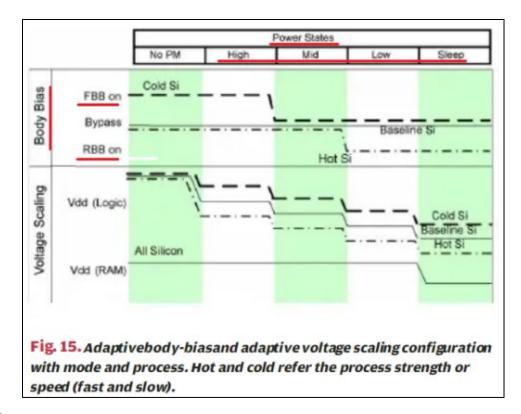

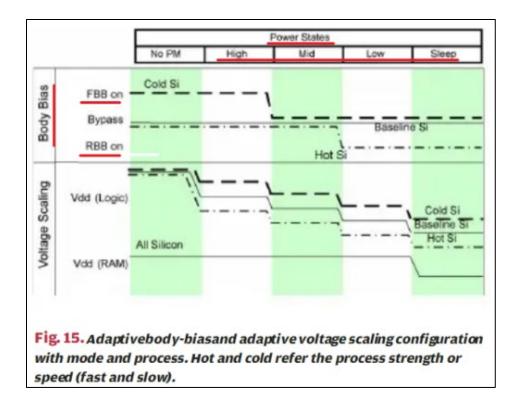

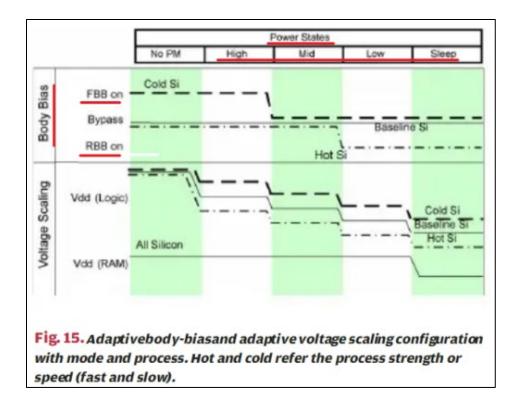

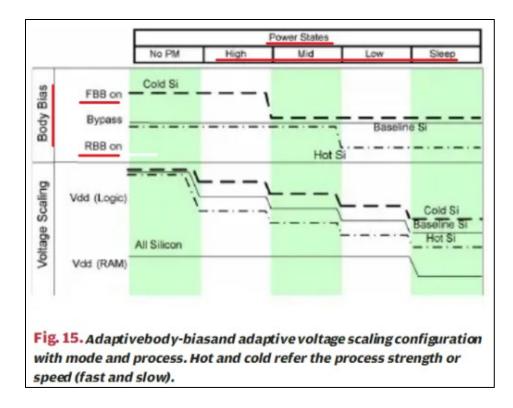

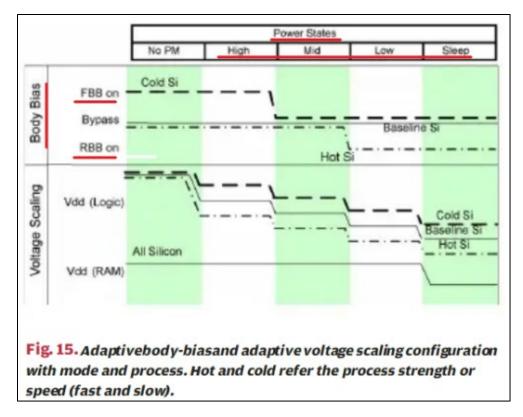

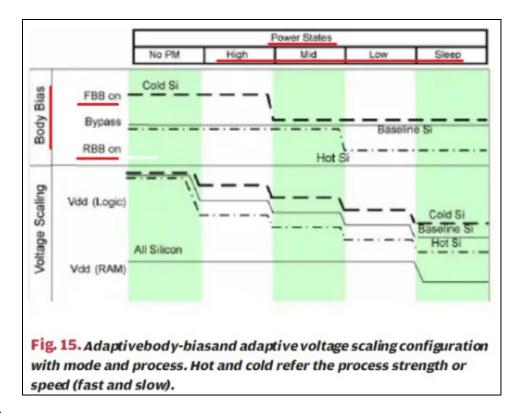

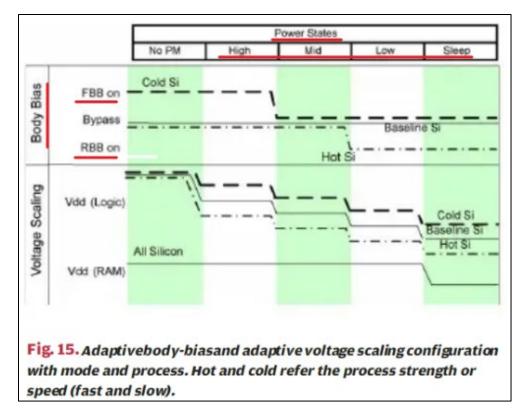

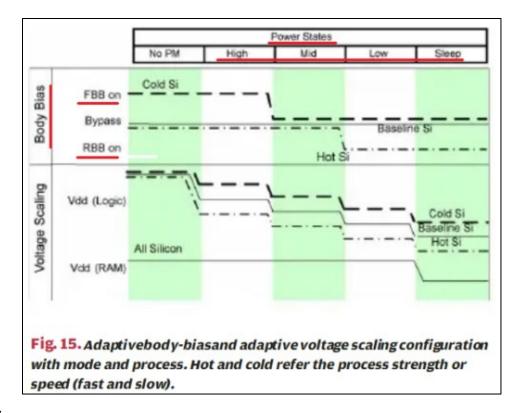

TI's approach to ABB is to apply body-bias when and where it adds value rather than globally or continuously. In application modes when more performance is demanded at the highest operating performance point, FBB is used to boost performance and increase system throughput. Since the performance is limited by the slowest silicon, FBB is only applied to these die. FBB is not applied to all silicon, since this unnecessarily increases leakage power on faster die already capable of providing the required performance. When lower operating performance is acceptable and active leakage becomes a dominant source of power consumption, RBB is applied to increase the effective Vt, hence reducing leakage power. Since the worst case leakage power occurs on fast silicon, RBB is applied only to these die. RBB is not applied to all silicon since this decreases performance on die that already dissipate lower leakage power. Selectively applying ABB based on operating mode and silicon strength (Fig. 15) achieves an optimal balance of performance and power with circuit techniques alone, eliminating the need for additional LVT or HVT logic transistors.

## Source:

https://www.academia.edu/29769936/SmartReflex\_Power\_and\_Performance\_Management\_Tec hnologies for 90 nm 65 nm and 45 nm Mobile Application Processors (Page 152)

https://www.academia.edu/29769936/SmartReflex\_Power\_and\_Performance\_Management\_Tec hnologies for 90 nm 65 nm and 45 nm Mobile Application Processors (Page 152)

26. TI's TDA2x System-on-Chip devices include a voltage supply to generate a body biasing voltage for circuitry of said computer system according to said body biasing voltage information

27. For example, TI's TDA2x System-on-Chip devices include a dual core processor module. The devices support Adaptive Body Bias (ABB). The ABB feature allows application of forward body bias to improve performance and reverse body bias to reduce leakage in the device. A programmed reverse body bias voltage is supplied by the ABB LDO ("voltage supply") to VBBNW pin of the transistors of the device's microprocessor. For example, to reduce leakage in low power states or low operating performance points (OPP Low), the reverse body bias voltage value ("body biasing voltage information") is accessed and applied to the device.

The TDA2xx/TDA2ex family of devices also support Adaptive Body Bias (ABB), which helps control further leakage, improve the performance of the silicon by applying a voltage to the NWELL of the PMOS transistors of the device, and change  $V_{TH}$  of the transistors.

#### Table 2. Adaptive Body Bias (ABB) Impact on Strong and Weak Samples

| Reverse Body Bias (RBB)  | Forward Body Bias (FBB)  |

|--------------------------|--------------------------|

| VBBNW > VDD              | VBBNW < VDD              |

| For Strong Samples       | For Weak Samples         |

| Increase V <sub>th</sub> | Decrease V <sub>th</sub> |

| Reduce Leakage           | Increase Performance     |

#### Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

<u>%252Fwww.google.com%252F</u> (Page 5)

#### 2.5 Adaptive Body Bias

The adaptive body bias (ABB) is a feature that enables the body bias voltage of the transistor (also called NWELL voltage or VBBNW) to be adjusted in order to control transistor performance. The ABB LDO is located on the IC that supplies the body bias voltage. The ABB must be set and enabled while running at certain OPPs based on the characteristics of the device data stored on the device.

#### Source:

https://www.ti.com/lit/an/slva646/slva646.pdf?ts=1597323545336&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 4)

#### Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 6)

Source: https://training.ti.com/introduction-adas-power-management-software?cu=1137175 (at

13:43)

| P | ИΗ                                                                                                                                                               | ardware Abstraction Layer (PMHAL) provides low level APIs that allow:                                |  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| • | Pr                                                                                                                                                               | ogramming PRCM registers                                                                             |  |

|   | -                                                                                                                                                                | Power Domain Manager (PDM)<br><stw dir="" install="">\include\pm\pmhal\pmhal_pdm.h</stw>             |  |

|   | -                                                                                                                                                                | Clock Domain Manager (CM)<br><stw dir="" install="">\include\pm\pmhal\pmhal_cm.h</stw>               |  |

|   | -                                                                                                                                                                | Reset Manager (RM)<br><stw dir="" install="">\include\pm\pmhal\pmhal_rm.h</stw>                      |  |

|   | -                                                                                                                                                                | Module Manager (MM)<br><stw dir="" install="">\include\pm\pmhal\pmhal_mm.h</stw>                     |  |

| • |                                                                                                                                                                  | ogramming Temperature Sensor Registers (Temp)<br>TW Install Dir>\include\pm\pmhal\pmhal_bgap.h       |  |

| • | Programming Voltage Domain Adaptive Voltage Scaling (AVS) and Adaptive Body Bias (ABB) (VM) <pre><stw dir="" install="">\include\pm\pmhal\pmhal_vm.h</stw></pre> |                                                                                                      |  |

| • | Pr<br><s< td=""><td>ogramming board specific Power Management IC (PMIC)<br/>TW Install Dir&gt;\include\pm\pmhal\pmhal_pmic.h</td></s<>                           | ogramming board specific Power Management IC (PMIC)<br>TW Install Dir>\include\pm\pmhal\pmhal_pmic.h |  |

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 4)

TI's approach to ABB is to apply body-bias when and where it adds value rather than globally or continuously. In application modes when more performance is demanded at the highest operating performance point, FBB is used to boost performance and increase system throughput. Since the performance is limited by the slowest silicon, FBB is only applied to these die. FBB is not applied to all silicon, since this unnecessarily increases leakage power on faster die already capable of providing the required performance. When lower operating performance is acceptable and active leakage becomes a dominant source of power consumption, RBB is applied to increase the effective Vt, hence reducing leakage power. Since the worst case leakage power occurs on fast silicon, RBB is applied only to these die. RBB is not applied to all silicon since this decreases performance on die that already dissipate lower leakage power. Selectively applying ABB based on operating mode and silicon strength (Fig. 15) achieves an optimal balance of performance and power with circuit techniques alone, eliminating the need for additional LVT or HVT logic transistors.

## Source:

https://www.academia.edu/29769936/SmartReflex\_Power\_and\_Performance\_Management\_Tec hnologies for 90 nm 65 nm and 45 nm Mobile Application Processors (Page 152)

https://www.academia.edu/29769936/SmartReflex\_Power\_and\_Performance\_Management\_Tec hnologies for 90 nm 65 nm and 45 nm Mobile Application Processors (Page 152)

28. TI's TDA2x System-on-Chip devices include circuitry to selectively couple the body biasing voltage information from one of the plurality of data storage locations corresponding to one of the plurality of power modes to the voltage supply.

29. For example, TI's TDA2x System-on-Chip devices include a dual core processor module. The devices support Adaptive Body Bias (ABB). A body bias voltage is applied to the transistors of the device using ABB. ABB voltage values are available for each OPP (Operating Performance Point), and therefore, for each power state. The ABB voltage values corresponding to the different power states are stored in Efuse registers ("data storage locations"). Further, the body bias voltage value is supplied by the ABB LDO ("voltage supply") to the VBBNW pin of the transistors of the device's microprocessor. For example, to reduce leakage in low power states or low operating performance points (OPP Low), the reverse body bias voltage value

("body biasing voltage information") is accessed and applied to the device. Accordingly, the

devices include circuitry for selectively coupling the body bias voltage information stored in the

registers to the ABB LDO voltage supply.

| The TDA2xx/TDA2ex family of devices also support Adaptive Body Bias (ABB), which helps control further leakage, improve the performance of the silicon by applying a voltage to the NWELL of the PMOS transistors of the device, and change V <sub>TH</sub> of the transistors.<br><b>Table 2. Adaptive Body Bias (ABB) Impact on Strong and Weak Samples</b> |                          |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|

| Reverse Body Bias (RBB)                                                                                                                                                                                                                                                                                                                                       | Forward Body Bias (FBB)  |  |  |

| VBBNW > VDD                                                                                                                                                                                                                                                                                                                                                   | VBBNW < VDD              |  |  |

| For Strong Samples                                                                                                                                                                                                                                                                                                                                            | For Weak Samples         |  |  |

| Increase V <sub>th</sub>                                                                                                                                                                                                                                                                                                                                      | Decrease V <sub>th</sub> |  |  |

| Reduce Leakage                                                                                                                                                                                                                                                                                                                                                | Increase Performance     |  |  |

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 5)

## 2.5 Adaptive Body Bias

The adaptive body bias (ABB) is a feature that enables the body bias voltage of the transistor (also called NWELL voltage or VBBNW) to be adjusted in order to control transistor performance. The ABB LDO is located on the IC that supplies the body bias voltage. The ABB must be set and enabled while running at certain OPPs based on the characteristics of the device data stored on the device.

## Source:

https://www.ti.com/lit/an/slva646/slva646.pdf?ts=1597323545336&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 4)

$\underline{https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341\&ref\_url=https\%253A\%252F$

%252Fwww.google.com%252F (Page 6)

Source: <u>https://training.ti.com/introduction-adas-power-management-software?cu=1137175</u> (at 13:43)

The next step is to register the PMIC operations with PMHAL. In this example, we have registered the Tps65917 with the PMHAL. Once this registration is successful, we set the AVS and the ABB for the corresponding voltage domain and OPP ID using the API PMHALVMSetOpp. This API will reach the AVS EFUSE values and programs the PMIC to set the AVS voltage. Once the AVS has been programmed, it also programs the appropriate NWELL voltage, as read from the ABB EFUSE.

Source: <u>https://training.ti.com/introduction-adas-power-management-software</u> (at 17:07)

| - ti,abb_info: An array of 6-tuples u32 items providing i      | nformation about ABB |

|----------------------------------------------------------------|----------------------|

| configuration needed per operational voltage of t              | he device.           |

| Each item consists of the following in the same o              | rder:                |

| volt: voltage in uV - Only used to index ABB info              | rmation.             |

| ABB mode: one of the following:                                |                      |

| 0-bypass                                                       |                      |

| 1-Forward Body Bias(FBB)                                       |                      |

| 3-Reverse Body Riss(RBR)                                       |                      |

| efuse: (see Optional properties)                               |                      |

| RBB enable efuse Mask: (See Optional properties)               |                      |

| FBB enable efuse Mask: (See Optional properties)               |                      |

| Vset value efuse Mask: (See Optional properties)               |                      |

| ····· ····· ····· (••• ······ ····· ······ ····· ······ ······ |                      |

Source: https://www.kernel.org/doc/Documentation/devicetree/bindings/regulator/ti-abb-

## regulator.txt

ti,abb\_opp\_sel: Addendum to the description in required properties

efuse: Mandatory if 'efuse-address' register is defined. Provides offset

from efuse-address to pick up ABB characteristics. Set to 0 if

'efuse-address' is not defined.

RBB enable efuse Mask: Optional if 'efuse-address' register is defined.

'ABB mode' is force set to RBB mode if value at "efuse-address"

+ efuse maps to RBB mask. Set to 0 to ignore this.

FBB enable efuse Mask: Optional if 'efuse-address' register is defined.

'ABB mode' is force set to FBB mode if value at "efuse-address"

+ efuse maps to FBB mask (valid only if RBB mask does not match)

Set to 0 to ignore this.

Vset value efuse Mask: Mandatory if ldo-address is set. Picks up from

efuse the value to set in 'ti,ldovbb-vset-mask' at ldo-address.

Source: https://www.kernel.org/doc/Documentation/devicetree/bindings/regulator/ti-abb-

regulator.txt

PM Hardware Abstraction Layer (PMHAL) provides low level APIs that allow: Programming PRCM registers Power Domain Manager (PDM) <STW Install Dir>\include\pm\pmhal\pmhal\_pdm.h Clock Domain Manager (CM) <STW Install Dir>\include(pm\pmhal\pmhal\_cm.h Reset Manager (RM) <STW Install Dir>\include\pm\pmhal\pmhal\_rm.h Module Manager (MM) <STW Install Dir>\include\pm\pmhal\pmhal mm.h Programming Temperature Sensor Registers (Temp) <STW Install Dir>\include\pm\pmhal\pmhal\_bgap.h Programming Voltage Domain Adaptive Voltage Scaling (AVS) and Adaptive Body Bias (ABB) (VM) <STW Install Dir>\include\pm\pmhal\pmhal\_vm.h Programming board specific Power Management IC (PMIC) <STW Install Dir>\include\pm\pmhal\pmhal\_pmic.h

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

<u>%252Fwww.google.com%252F</u> (Page 4)

TI's approach to ABB is to apply body-bias when and where it adds value rather than globally or continuously. In application modes when more performance is demanded at the highest operating performance point, FBB is used to boost performance and increase system throughput. Since the performance is limited by the slowest silicon, FBB is only applied to these die. FBB is not applied to all silicon, since this unnecessarily increases leakage power on faster die already capable of providing the required performance. When lower operating performance is acceptable and active leakage becomes a dominant source of power consumption, RBB is applied to increase the effective Vt, hence reducing leakage power. Since the worst case leakage power occurs on fast silicon, RBB is applied only to these die. RBB is not applied to all silicon since this decreases performance on die that already dissipate lower leakage power. Selectively applying ABB based on operating mode and silicon strength (Fig. 15) achieves an optimal balance of performance and power with circuit techniques alone, eliminating the need for additional LVT or HVT logic transistors.

## Source:

https://www.academia.edu/29769936/SmartReflex\_Power\_and\_Performance\_Management\_Tec hnologies for 90 nm 65 nm and 45 nm Mobile Application Processors (Page 152)

https://www.academia.edu/29769936/SmartReflex\_Power\_and\_Performance\_Management\_Tec hnologies for 90 nm 65 nm and 45 nm Mobile Application Processors (Page 152)

30. TI has infringed the '504 Patent by using the accused products and thereby

practicing a method for determining a body biasing voltage applied to a microprocessor.

31. For example, TI's TDA2x System-on-Chip devices include a dual core processor module ("microprocessor"). The devices support Adaptive Body Bias (ABB), which can apply a forward or reverse body bias voltage to the transistors of the device's microprocessor using ABB.

## **TDA2x ADAS System-on-Chip**

## **U** Texas Instruments

#### Source:

https://www.ti.com/lit/ml/sprt681/sprt681.pdf?ts=1597386693056&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 1)

#### TDA2x (Vision 28) ADAS Application Processor

#### Overview

TI's new TDA2x Vision 28 system-on-chip (SoC) is a highly optimized and scalable device family designed to meet the requirements of leading advanced driver assistance systems (ADAS). The TDA2x family empowers broad ADAS applications in today's automobiles by integrating an optimal mix of performance, low power and ADAS vision-analytics processing that aims to facilitate a more autonomous and collision-free driving experience.

The TDA2x SoC makes possible sophisticated embedded vision technology, providing the industry's broadest range of ADAS applications such as front camera, park assist, surround view and sensor fusion on a single architecture. Front-camera applications include high-beam assist, lane-keep assist,

#### TDA2x

The TDA2x SoC incorporates a heterogeneous, scalable architecture that includes a mix of TI's fixed- and floatingpoint TMS320C66x digital signal processor (DSP) generation cores, Vision AccelerationPac, <u>ARM Cortex-A15 MPCore</u> and dual Cortex-M4 processors. The integration of video for decoding multiple video streams over Ethernet audio-video bridging (AVB) networks, along with graphics accelerators for rendering virtual views, allows for a 3-D viewing experience. And the TDA2x SoC integrates a host of peripherals, including multicamera interfaces (both parallel and serial) for LVDS-based surround-view systems, displays, CAN and Gigabit Ethernet AVB.

Source: <a href="https://m.eet.com/media/1241324/slyy044.pdf">https://m.eet.com/media/1241324/slyy044.pdf</a> (Page 5)

https://www.ti.com/lit/an/sprac21a/sprac21a.pdf?ts=1597386703137&ref\_url=https%253A%252 F%252Fwww.google.com%252F (Page 6)

<u>The TDA2xx/TDA2ex family of devices also support Adaptive Body Bias (ABB), which helps control further</u> leakage, improve the performance of the silicon by applying a voltage to the NWELL of the PMOS transistors of the device, and change  $V_{TH}$  of the transistors.

|  | Table 2. Adaptiv | ve Body Bias | (ABB) Imp | act on Strong | and Weak Samples |

|--|------------------|--------------|-----------|---------------|------------------|

|--|------------------|--------------|-----------|---------------|------------------|

| Reverse Body Bias (RBB)  | Forward Body Bias (FBB)  |  |  |

|--------------------------|--------------------------|--|--|

| VBBNW > VDD              | VBBNW < VDD              |  |  |

| For Strong Samples       | For Weak Samples         |  |  |

| Increase V <sub>th</sub> | Decrease V <sub>th</sub> |  |  |

| Reduce Leakage           | Increase Performance     |  |  |

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 5)

32. The method practiced using the accused products comprises receiving a command

to change to a different power condition of a computer system comprising the microprocessor.

The power condition comprises a different microprocessor clock frequency and/or a different

microprocessor operating voltage.

33. For example, TI's TDA2x System-on-Chip devices include a dual core processor module. Further, the System-on-Chip ("computer system") includes an MPU\_PRCM module for power management of the processor ("microprocessor"). The TDA2x family of devices supports multiple power states (e.g., a power state in which both cores are on, a power state in which one core is forced off, a power state in which one core is forced off and the other core is in retention, etc.).

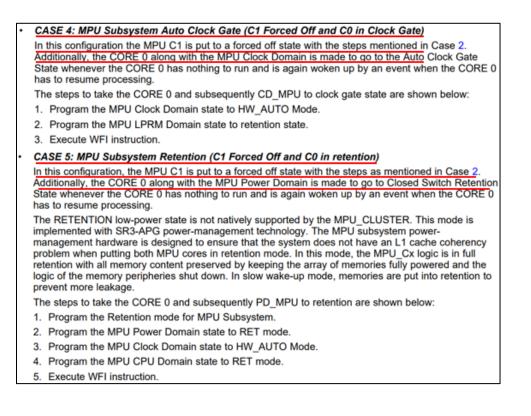

34. The desired power state can be achieved through programming—that is, a command can be received by the device to change from one power state to a different power state. For example, the system can receive a command to change from a power state in which both cores are on to a power state in which one core is forced off and the other core is in retention ("said different power condition"). A power state changes based on the processor's performance, and each power state is associated with a different clock frequency and/or a different voltage.

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 19)

the CPUs for the low-power state. The different power states for the different CPUs in the system, from highest (left most) to lowest (right most), are summarized in Table 10. The following sections dive deep into the power and clock state of the different subsystems and the programming sequence to achieve the desired power state.

| Table 10. Different Power States supported by CPU Subsystems |                        |                   |                                   |                              |                        |

|--------------------------------------------------------------|------------------------|-------------------|-----------------------------------|------------------------------|------------------------|

| CPU Subsystem                                                | Highest Power<br>State |                   |                                   |                              | Lowest Power<br>State  |

| MPU                                                          | On                     | Core 1 Forced Off | Core 1 Forced Off,<br>Core 0 Idle | Subsystem Auto<br>Clock Gate | Subsystem<br>Retention |

| DSP                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

| IPU                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

| EVE                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 18)

| 5.1.2 |                                                                                                                                                                                                                                                                                                                                                 | MPU PM States |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|--|

|       | This section discusses the different power states of the MPU subsystem and understands the power do<br>and wake up latencies based on the power savings. Contact your TI representative to get access to the<br>TDA2xx/TDA2ex Power Estimation Spread Sheet and analyze the exact power savings for the different<br>supported low power modes. |               |  |  |  |  |

|       | CASE 1: MPU ON (Core 0 (C0) and Core 1 (C1) On)                                                                                                                                                                                                                                                                                                 |               |  |  |  |  |

|       | In this configuration, the Cortex-A15 CPUs are both alive and running their respective software.<br>the highest power consumption configuration and the power consumption is determined by the k<br>operations the A15 is performing. The sub-modules in the MPU subsystem are ON and the clock<br>enabled for the subsystem and the CPUs.      |               |  |  |  |  |

|       | CASE 2: MPU C1 Forced Off                                                                                                                                                                                                                                                                                                                       |               |  |  |  |  |

|       | In this configuration, the MPU C1 is forced off and the MPU C0 is alive and running its own softw<br>In this configuration, the MPU C1 logic, L1 Cache is off, the clocks to the MPU C1 are gated and<br>MPU C1 LPRM shows the CPU to be in power off mode.                                                                                     |               |  |  |  |  |

|       | <ul> <li>CASE 3: MPU C1 Forced Off and C0 in IDLE</li> <li>In this configuration, the MPU C1 is put to a forced off state with the steps as mentioned in Cas<br/>Additionally the CORE 0 is made to go to IDLE state whenever the CORE 0 has nothing to run<br/>again woken up by an event when the CORE 0 has to resume processing.</li> </ul> |               |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                                                 |               |  |  |  |  |

|       | The steps to take the CORE 0 to IDLE are shown below:                                                                                                                                                                                                                                                                                           |               |  |  |  |  |

|       | 1. Program the MPU LPRM Domain state to the desired power state.                                                                                                                                                                                                                                                                                |               |  |  |  |  |

|       | 2. Execute WFI instruction.                                                                                                                                                                                                                                                                                                                     |               |  |  |  |  |

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

## %252Fwww.google.com%252F (Pages 20 and 21)

#### Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 23)

#### 3.3 Setting the Frequency of Modules

Based on the expected CPU operations, the CPUs in the system can be configured to operate at different frequencies as determined by the OPP and speed bin of the device. Setting the OPP of the CPU involves setting the DPLLs to provide the desired clock frequency and setting the PMIC to provide the desired voltage as determined in the AVS EFuse registers. Similarly, different peripherals require different

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 9)

35. The method practiced using the accused products further comprises accessing body biasing voltage information corresponding to the power condition.

36. For example, TI's TDA2x System-on-Chip devices support Adaptive Body Bias (ABB). ABB voltage values are given for each OPP (Operating Performance Point), which is the operating condition for the device and is defined by the voltage and frequency applied to the processor. Further, the TDA2x family of devices supports multiple power states (e.g., a power state in which both cores are on, a power state in which one core is forced off, a power state in which one core is forced off and other core is in retention, etc.). An OPP is established based on the power state (i.e., operation) of the CPU.

37. Accordingly, the TDA2x family of devices stores the ABB voltage values associated with each OPP and corresponding power state. The ABB feature allows application of forward body bias to improve performance and reverse body bias to reduce leakage in the device. To reduce leakage in low power states or low operating performance points (OPP Low), the reverse body bias voltage value ("body biasing voltage information") is accessed and applied to the device. This occurs during one of the low power states of the device, such as during the power state in which one core is forced off and the other core is in retention ("said power condition").

32

| The TDA2xx/TDA2ex family of devices also support Adaptive Body Bias (ABB), which helps control further leakage, improve the performance of the silicon by applying a voltage to the NWELL of the PMOS transistors of the device, and change $V_{TH}$ of the transistors. |                          |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|--|

| Table 2. Adaptive Body Bias (ABB) Impact on Strong and Weak Samples                                                                                                                                                                                                      |                          |  |  |  |

| Reverse Body Bias (RBB)                                                                                                                                                                                                                                                  | Forward Body Bias (FBB)  |  |  |  |

| VBBNW > VDD                                                                                                                                                                                                                                                              | VBBNW < VDD              |  |  |  |

| For Strong Samples                                                                                                                                                                                                                                                       | For Weak Samples         |  |  |  |

| Increase V <sub>th</sub>                                                                                                                                                                                                                                                 | Decrease V <sub>th</sub> |  |  |  |

| Reduce Leakage                                                                                                                                                                                                                                                           | Increase Performance     |  |  |  |

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

## <u>%252Fwww.google.com%252F</u> (Page 5)

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

<u>%252Fwww.google.com%252F (Page 6)</u>

Source: https://training.ti.com/introduction-adas-power-management-software?cu=1137175 (at

13:43)

## 3.3 Setting the Frequency of Modules

Based on the expected CPU operations, the CPUs in the system can be configured to operate at different frequencies as determined by the OPP and speed bin of the device. Setting the OPP of the CPU involves setting the DPLLs to provide the desired clock frequency and setting the PMIC to provide the desired voltage as determined in the AVS EFuse registers. Similarly, different peripherals require different

## Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 9)

| Table 10. Different Power States supported by CPU Subsystems |                        |                   |                                   |                              |                        |

|--------------------------------------------------------------|------------------------|-------------------|-----------------------------------|------------------------------|------------------------|

| CPU Subsystem                                                | Highest Power<br>State |                   |                                   |                              | Lowest Power<br>State  |

| MPU                                                          | On                     | Core 1 Forced Off | Core 1 Forced Off,<br>Core 0 Idle | Subsystem Auto<br>Clock Gate | Subsystem<br>Retention |

| DSP                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

| IPU                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

| EVE                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 18)

| Voltage Rail | TDA2xx OPP SUPPORT |           |               |               |  |

|--------------|--------------------|-----------|---------------|---------------|--|

|              | OPP LOW            | OPP NOM   | OPP OD        | OPP HIGH      |  |

| VD_MPU       | Supported          | Supported | Supported     | Supported     |  |

| VD_DSPEVE    | Not Supported      | Supported | Supported     | Supported     |  |

| VD_IVA       | Not Supported      | Supported | Supported     | Supported     |  |

| VD_GPU       | Not Supported      | Supported | Supported     | Supported     |  |

| VD_CORE      | Not Supported      | Supported | Not Supported | Not Supported |  |

Source: <a href="https://processors.wiki.ti.com/images/b/b7/TDA\_SBL\_UserGuide.pdf">https://processors.wiki.ti.com/images/b/b7/TDA\_SBL\_UserGuide.pdf</a> (Page 23)

TI's approach to ABB is to apply body-bias when and where it adds value rather than globally or continuously. In application modes when more performance is demanded at the highest operating performance point, FBB is used to boost performance and increase system throughput. Since the performance is limited by the slowest silicon, FBB is only applied to these die. FBB is not applied to all silicon, since this unnecessarily increases leakage power on faster die already capable of providing the required performance. When lower operating performance is acceptable and active leakage becomes a dominant source of power consumption, RBB is applied to increase the effective Vt, hence reducing leakage power. Since the worst case leakage power occurs on fast silicon, RBB is applied only to these die. RBB is not applied to all silicon since this decreases performance on die that already dissipate lower leakage power. Selectively applying ABB based on operating mode and silicon strength (Fig. 15) achieves an optimal balance of performance and power with circuit techniques alone, eliminating the need for additional LVT or HVT logic transistors.

## Source:

https://www.academia.edu/29769936/SmartReflex\_Power\_and\_Performance\_Management\_Tec hnologies for 90 nm 65 nm and 45 nm Mobile Application Processors (Page 152)

https://www.academia.edu/29769936/SmartReflex\_Power\_and\_Performance\_Management\_Tec hnologies for 90 nm 65 nm and 45 nm Mobile Application Processors (Page 152)

38. The method practiced using the accused products further comprises commanding a voltage supply coupled to a body terminal of the microprocessor to generate a voltage corresponding to the body biasing voltage information corresponding to the power condition.

39. For example, TI's TDA2x System-on-Chip devices include a dual core processor module ("microprocessor"). The devices support Adaptive Body Bias (ABB), which allows application of forward body bias to increase performance and reverse body bias to reduce leakage in the device. The ABB voltage value can be programmed—that is, a command can be generated by the device to apply a body bias voltage value. Further, the programmed reverse body bias voltage value is supplied by the ABB LDO ("voltage supply") to the VBBNW pin ("body terminal") of the transistors of the device's microprocessor.

40. To reduce leakage in low power states or low operating performance points (OPP Low), the reverse body bias voltage value ("body biasing voltage information") is accessed and applied to the device. This occurs during one of the low power states of the device, such as the power state in which one core is forced off and the other core is in retention ("said power condition"). Accordingly, the device can command the ABB LDO, which is coupled to the VBBNW pin, to supply a reverse body bias voltage corresponding to the low power state, i.e., the power state in which one core is forced off and other core is in retention ("said power condition").

The TDA2xx/TDA2ex family of devices also support Adaptive Body Bias (ABB), which helps control further leakage, improve the performance of the silicon by applying a voltage to the NWELL of the PMOS transistors of the device, and change V<sub>TH</sub> of the transistors.

Table 2. Adaptive Body Bias (ABB) Impact on Strong and Weak Samples

|                          | Forward Body Bias (FBB)  |

|--------------------------|--------------------------|

| VBBNW > VDD              | VBBNW < VDD              |

|                          | For Weak Samples         |

| Increase V <sub>th</sub> | Decrease V <sub>th</sub> |

| Reduce Leakage           | Increase Performance     |

#### Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 5)

#### 2.5 Adaptive Body Bias

The adaptive body bias (ABB) is a feature that enables the body bias voltage of the transistor (also called NWELL voltage or VBBNW) to be adjusted in order to control transistor performance. The ABB LDO is located on the IC that supplies the body bias voltage. The ABB must be set and enabled while running at certain OPPs based on the characteristics of the device data stored on the device.

# Source:

https://www.ti.com/lit/an/slva646/slva646.pdf?ts=1597323545336&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 4)

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 6)

Source: <u>https://training.ti.com/introduction-adas-power-management-software?cu=1137175</u> (at 13:43)

PM Hardware Abstraction Layer (PMHAL) provides low level APIs that allow: Programming PRCM registers Power Domain Manager (PDM) <STW Install Dir>\include\pm\pmhal\pmhal pdm.h Clock Domain Manager (CM) <STW Install Dir>\include\pm\pmhal\pmhal\_cm.h Reset Manager (RM) <STW Install Dir>\include\pm\pmhal\pmhal\_rm.h Module Manager (MM) <STW Install Dir>\include\pm\pmhal\pmhal mm.h Programming Temperature Sensor Registers (Temp) <STW Install Dir>\include\pm\pmhal\pmhal bgap.h Programming Voltage Domain Adaptive Voltage Scaling (AVS) and Adaptive Body Bias (ABB) (VM) <STW Install Dir>\include\pm\pmhal\pmhal vm.h Programming board specific Power Management IC (PMIC) <STW Install Dir>\include\pm\pmhal\pmhal\_pmic.h

# Source:

$\underline{https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341\&ref\_url=https\%253A\%252F}$

%252Fwww.google.com%252F (Page 4)

#### 3.3 Setting the Frequency of Modules

Based on the expected CPU operations, the CPUs in the system can be configured to operate at different frequencies as determined by the OPP and speed bin of the device. Setting the OPP of the CPU involves setting the DPLLs to provide the desired clock frequency and setting the PMIC to provide the desired voltage as determined in the AVS EFuse registers. Similarly, different peripherals require different

#### Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F

%252Fwww.google.com%252F (Page 9)

| Table 10. Different Power States supported by CPU Subsystems |                        |                   |                                   |                              |                        |

|--------------------------------------------------------------|------------------------|-------------------|-----------------------------------|------------------------------|------------------------|

| CPU Subsystem                                                | Highest Power<br>State |                   |                                   |                              | Lowest Power<br>State  |

| MPU                                                          | On                     | Core 1 Forced Off | Core 1 Forced Off,<br>Core 0 Idle | Subsystem Auto<br>Clock Gate | Subsystem<br>Retention |

| DSP                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

| IPU                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

| EVE                                                          | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

#### Source:

https://www.ti.com/lit/an/sprac22/sprac22.pdf?ts=1597386914341&ref\_url=https%253A%252F %252Fwww.google.com%252F (Page 18)

| Voltage Rail | TDA2xx OPP SUPPORT |           |               |               |

|--------------|--------------------|-----------|---------------|---------------|

|              | OPP LOW            | OPP NOM   | OPP OD        | OPP HIGH      |

| VD_MPU       | Supported          | Supported | Supported     | Supported     |

| VD_DSPEVE    | Not Supported      | Supported | Supported     | Supported     |

| VD_IVA       | Not Supported      | Supported | Supported     | Supported     |

| VD_GPU       | Not Supported      | Supported | Supported     | Supported     |

| VD_CORE      | Not Supported      | Supported | Not Supported | Not Supported |

Source: <u>https://processors.wiki.ti.com/images/b/b7/TDA\_SBL\_UserGuide.pdf</u> (Page 23)

TI's approach to ABB is to apply body-bias when and where it adds value rather than globally or continuously. In application modes when more performance is demanded at the highest operating performance point, FBB is used to boost performance and increase system throughput. Since the performance is limited by the slowest silicon, FBB is only applied to these die. FBB is not applied to all silicon, since this unnecessarily increases leakage power on faster die already capable of providing the required performance. When lower operating performance is acceptable and active leakage becomes a dominant source of power consumption, RBB is applied to increase the effective Vt, hence reducing leakage power. Since the worst case leakage power occurs on fast silicon, RBB is applied only to these die. RBB is not applied to all silicon since this decreases performance on die that already dissipate lower leakage power. Selectively applying ABB based on operating mode and silicon strength (Fig. 15) achieves an optimal balance of performance and power with circuit techniques alone, eliminating the need for additional LVT or HVT logic transistors.

# Source:

https://www.academia.edu/29769936/SmartReflex\_Power\_and\_Performance\_Management\_Tec hnologies for 90 nm 65 nm and 45 nm Mobile Application Processors (Page 152)

https://www.academia.edu/29769936/SmartReflex\_Power\_and\_Performance\_Management\_Tec hnologies\_for\_90\_nm\_65\_nm\_and\_45\_nm\_Mobile\_Application\_Processors (Page 152)

41. TI has had knowledge of the '504 Patent at least as of the date when it was notified of the filing of this action.