## IN THE UNITED STATES DISTRICT COURT FOR THE DISTRICT OF DELAWARE

FG SRC LLC,

Plaintiff,

v.

XILINX, INC.,

Defendant.

Case No. 1:20-cv-00601-LPS

JURY TRIAL DEMANDED

## PLAINTIFF'SECOND AMENDED COMPLAINT FOR PATENT INFRINGEMENT

Plaintiff FG SRC LLC ("SRC") files this Second Amended Complaint for Patent Infringement ("Second Amended Complaint") against Defendant Xilinx, Inc. ("Defendant" or "Xilinx"). Plaintiff alleges as follows:

## I. NATURE OF THE ACTION

1. This is an action for infringement of U.S. Patent No. 9,153,311 (the "'311 patent").

2. SRC is a limited liability company incorporated in Delaware and is the successor to SRC Computers, LLC ("SRC Computers").

3. Xilinx, Inc. is a Delaware corporation with its principal place of business located at 2100 Logic Drive, San Jose, California 95154.

## **II. JURISDICTION**

4. This action arises under the Patent Laws of the United States, 35 U.S.C. § 1, *et seq.*, including 35 U.S.C. §§ 271, 281, 283, 284, and 285. This is a patent infringement lawsuit, over which this Court has subject matter jurisdiction under 28 U.S.C. §§ 1331 and 1338(a).

5. This Court has general and specific personal jurisdiction over Defendant because it is present in and transacts and conducts business in and with residents of this District and the

State of Delaware. Defendant is incorporated in the State of Delaware and has conducted and does conduct business therein. Defendant has purposefully and voluntarily availed itself of the privileges of conducting business in the United States and the State of Delaware by continuously and systematically placing goods into the stream of commerce through a distribution channel with the expectation that they will be purchased by consumers in Delaware. Plaintiff's causes of action arise directly from Defendant's business contacts and other activities in the State of Delaware.

6. Upon information and belief, Defendant has committed acts of infringement in this District giving rise to this action and does business in this District, including making sales and/or providing services and support for its customers in this District. Defendant purposefully and voluntarily sold one or more of its infringing products with the expectation that they would be purchased by consumers in this District. These infringing products have been and continue to be purchased by consumers in this District.

## III. VENUE

7. Venue is proper as to Defendant under 28 U.S.C. § 1400(b) in that Defendant is incorporated in Delaware and, therefore, resides in this District. *TC Heartland LLC v. Kraft Foods Grp. Brands LLC*, 137 S. Ct. 1514, 1521 (2017).

## IV. FG SRC LLC AND DEFENDANT'S PRODUCTS

## A. FG SRC LLC

8. SRC Computers was co-founded by Seymour R. Cray, Jim Guzy, and Jon Huppenthal in 1996 to produce unique high-performance computer systems using Intel's Merced microprocessor.

9. SRC is the successor to SRC Computers.

10. Jim Guzy is a co-founder of Intel Corporation and served on Intel's board for 38 years.

#### PLAINTIFF'S SECOND AMENDED COMPLAINT FOR PATENT INFRINGEMENT – Page 2

11. Mr. Guzy was named to Forbes Midas List, which surveys the top tech deal makers in the world, in 2006 and 2007.

12. Seymour Cray was an American electrical engineer and supercomputer architect who designed a series of computers that were the fastest in the world for decades.

13. Mr. Cray has been credited with creating the supercomputing industry.

14. Unfortunately, Mr. Cray died shortly after founding SRC Computers.

15. But his legacy was carried on by Jon Huppenthal and a talented team of engineers that worked with Mr. Cray and Mr. Huppenthal for decades.

16. SRC Computers' focus was creating easy-to-program, general-purpose reconfigurable computing systems.

17. In early 1997, Mr. Huppenthal and his team realized that the microprocessors of the day had many shortcomings relative to the custom processing engines that they were used to.

18. As a result, they decided to incorporate dedicated processing elements built from Field Programmable Gate Arrays ("FPGAs") and that idea quickly evolved into a novel system combining reconfigurable processors and Central Processing Units ("CPUs").

19. SRC Computers' heterogenous system had 100x performance, 1/50<sup>th</sup> of the operating expense, 1/100<sup>th</sup> of the power usage, and required 1/500<sup>th</sup> of the space of more traditional computer systems.

20. SRC Computers' proven systems are used for some of the most demanding military and intelligence applications, including the simultaneous real-time processing and analysis of radar, flight and mission data collected from a variety of aerial vehicles in over 1,000 successful counter-terrorism and counter-insurgency missions for the U.S. Department of Defense.

21. SRC Computers offered its first commercial product in 2015 called the Saturn 1 server.

22. The Saturn 1 was 100 times faster than a server with standard Intel microprocessors while using one percent of the power.

23. The Saturn 1 was designed to be used in HP's Moonshot server chassis for data centers.

24. SRC Computers has had over 30 U.S. patents issued for its innovative technology.

25. SRC Computers' patent portfolio covers numerous aspects of reconfigurable computing and has more than 2,090 forward citations.

26. In February 2016, SRC Computers restructured into three new entities: a corporate parent FG SRC LLC, an operating company DirectStream, LLC ("DirectStream"), and a licensing entity SRC Labs, LLC ("SRC Labs").

## **B.** Accused Products

27. In this Second Amended Complaint, Plaintiff accuses the following Xilinx products (collectively "Accused Products") of infringing the '311 patent. For clarity, accused product families are listed, as are exemplary device names and/or part numbers or part number prefixes.

| Product Family                                       | Exemplary Device Names                             | Exemplary Part Numbers<br>and/or Part Number Prefixes |

|------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|

| Alveo accelerator<br>cards                           | U25, U200, U250, U280,<br>SN1022 (aka SN1000)      | and/ of 1 art (valide) 1 fenxes                       |

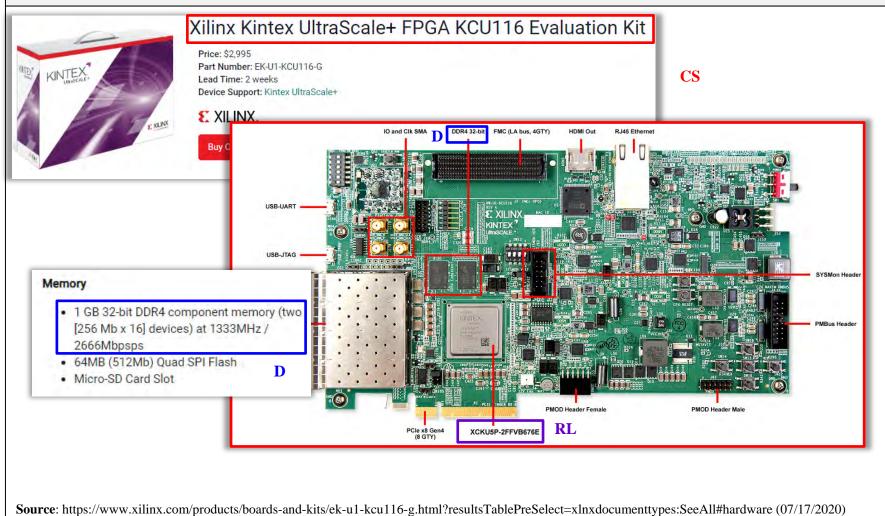

| Kintex UltraScale+<br>Evaluation Kit                 | KCU116                                             |                                                       |

| Virtex UltraScale+<br>Evaluation Kit                 | VCU118                                             |                                                       |

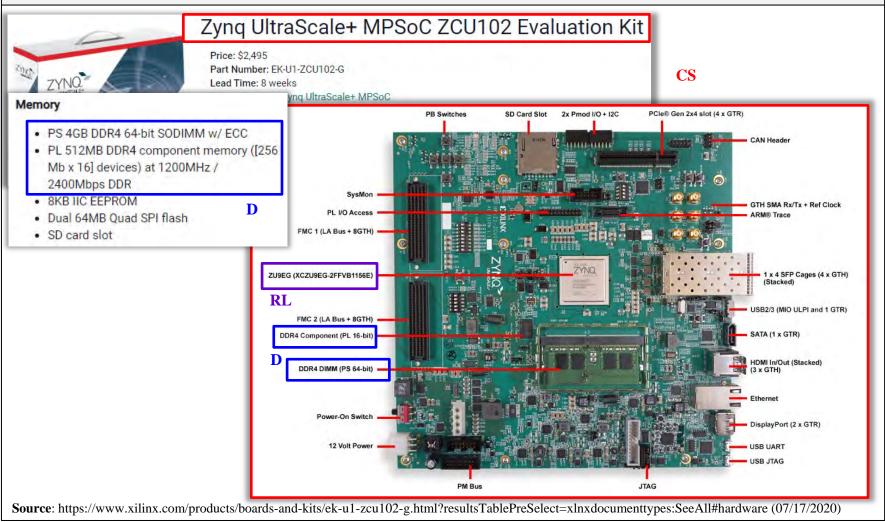

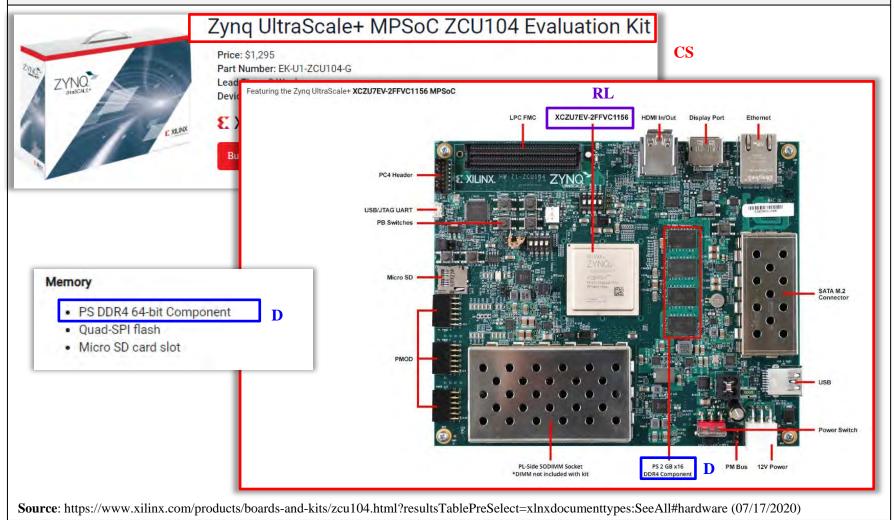

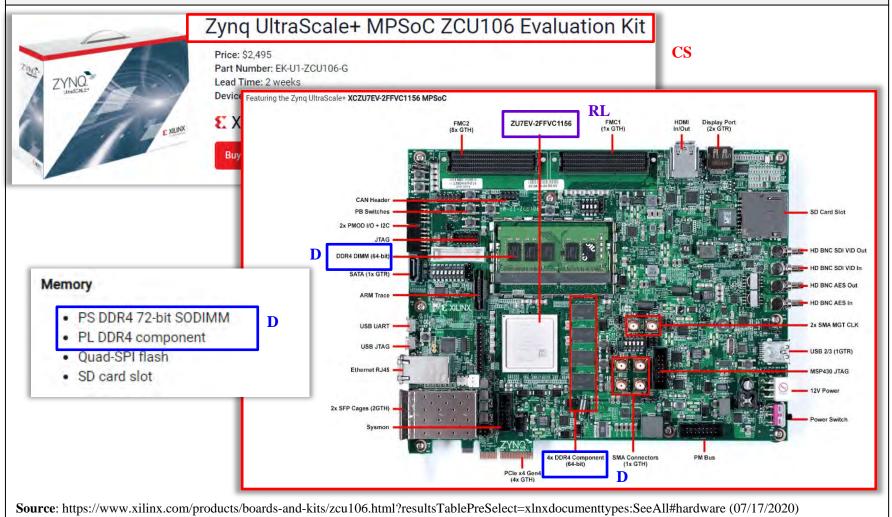

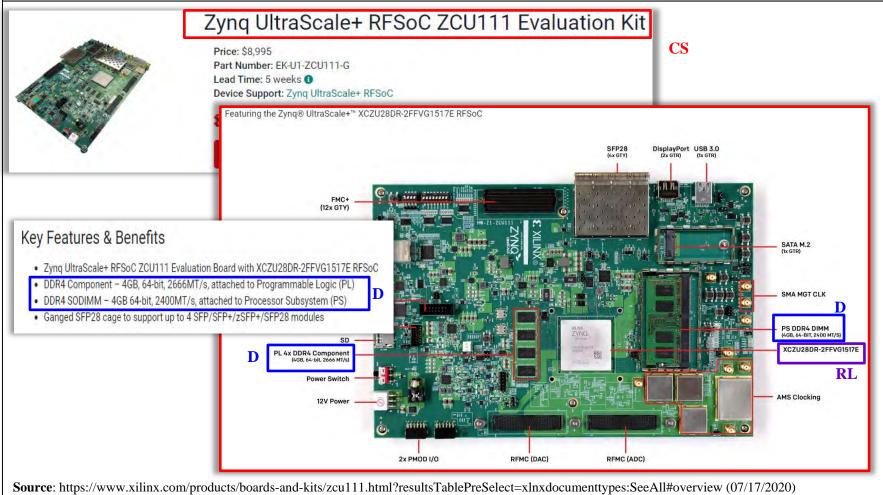

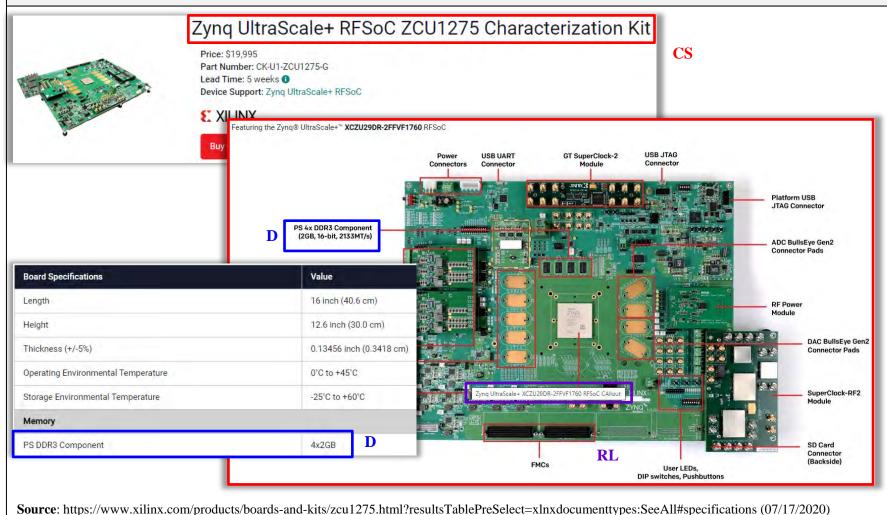

| Zynq UltraScale+<br>Evaluation Kits and              | ZCU102, ZCU104, ZCU106,<br>ZCU111, ZCU208, ZCU216, |                                                       |

| Characterization Kits                                | ZCU1275, ZCU1285                                   |                                                       |

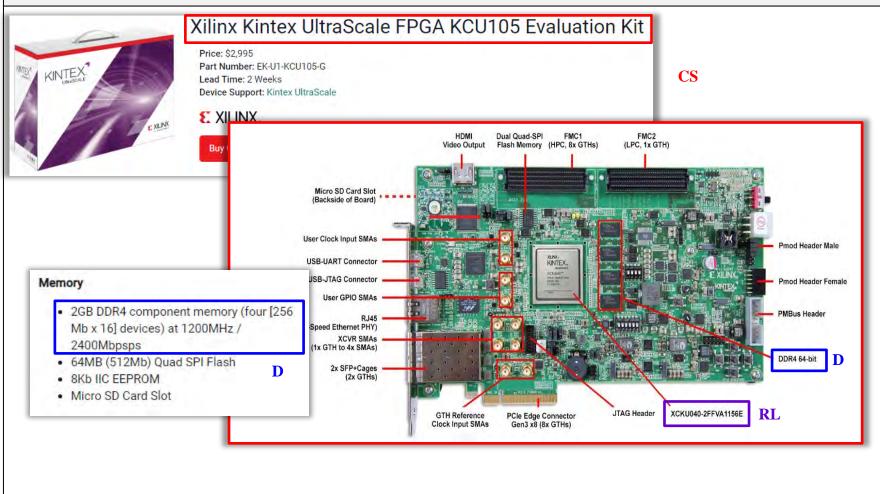

| Kintex UltraScale<br>Evaluation Kit                  | KCU105                                             |                                                       |

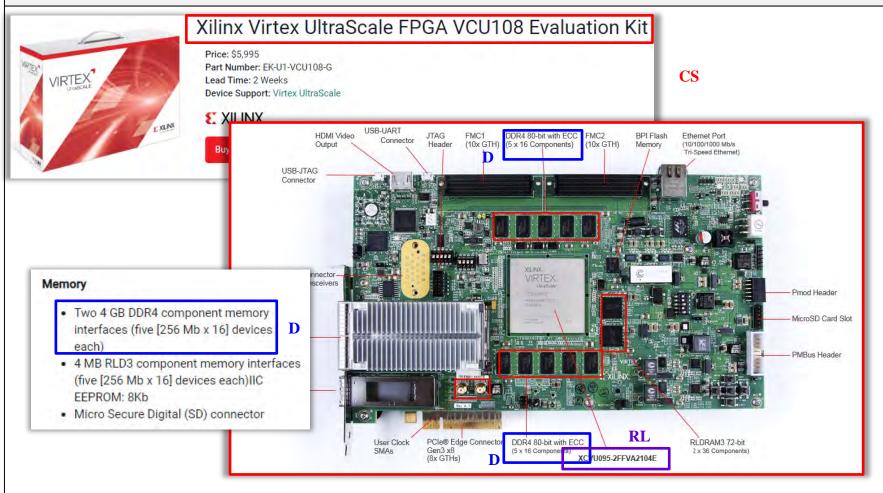

| Virtex UltraScale<br>Evaluation Kit                  | VCU108                                             |                                                       |

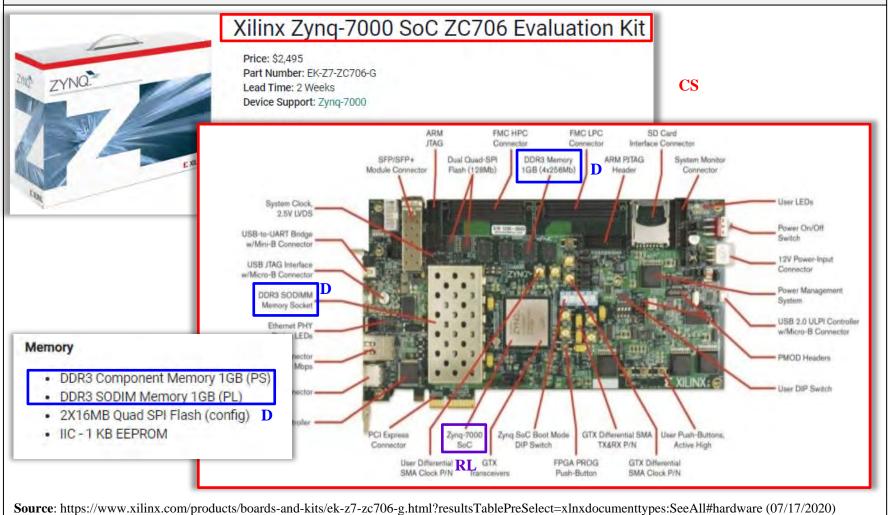

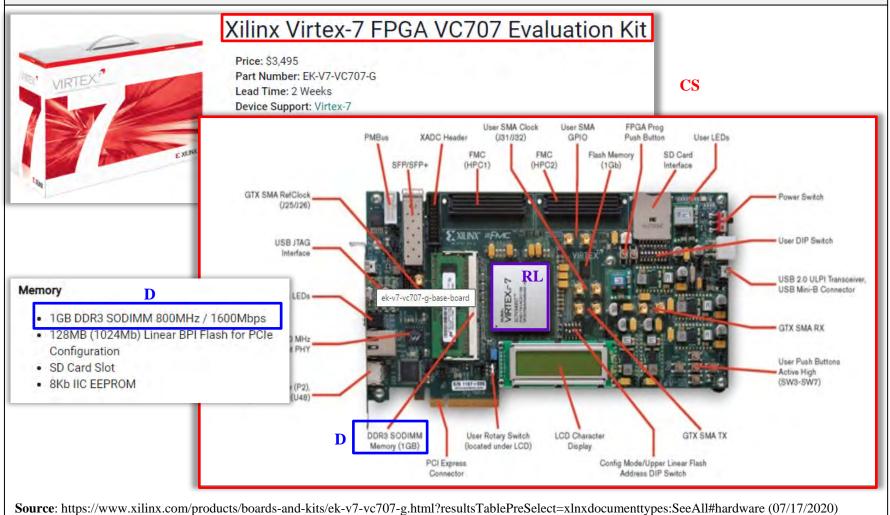

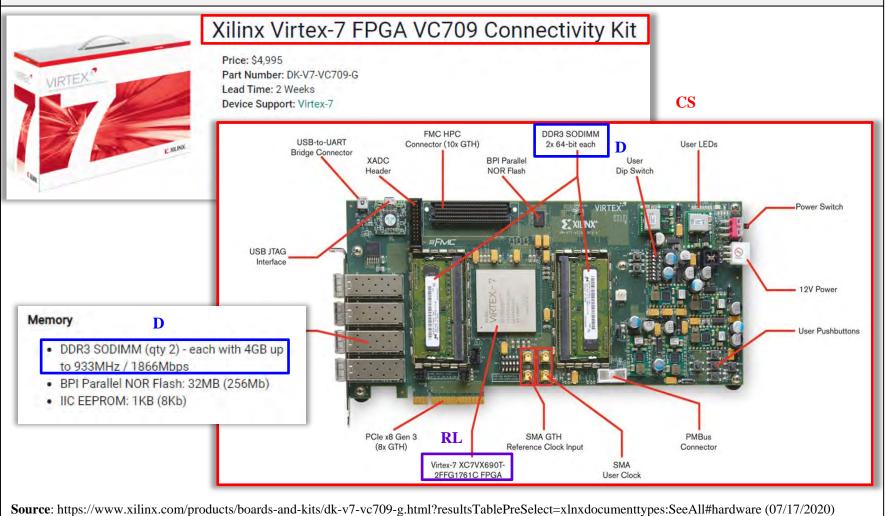

| Virtex-7 Evaluation<br>Kits and Connectivity<br>Kits | VC707, VC709                                       |                                                       |

| Product Family       | Exemplary Device Names                       | Exemplary Part Numbers      |

|----------------------|----------------------------------------------|-----------------------------|

|                      | <b>FFF</b>                                   | and/or Part Number Prefixes |

| Zynq-7000 Evaluation | ZC702, ZC706                                 |                             |

| Kits                 |                                              |                             |

| Kintex UltraScale+   | KU3P, KU5P, KU9P,                            |                             |

| FPGA devices         | KU11P, KU13P, KU15P,                         |                             |

|                      | KU19P                                        |                             |

| Virtex UltraScale+   | VU3P, VU5P, VU7P, VU9P,                      |                             |

| FPGA devices         | VU11P, VU13P, VU19P,                         |                             |

|                      | VU23P, VU27P, VU29P,                         |                             |

|                      | VU31P, VU33P, VU35P,                         |                             |

|                      | VU37P, VU45P, VU47P,                         |                             |

|                      | VU57P                                        |                             |

| Zynq UltraScale+     | ZU2CG, ZU3CG, ZU4CG,                         |                             |

| MPSoC: CG devices    | ZU5CG, ZU6CG, ZU7CG,                         |                             |

|                      | ZU9CG                                        |                             |

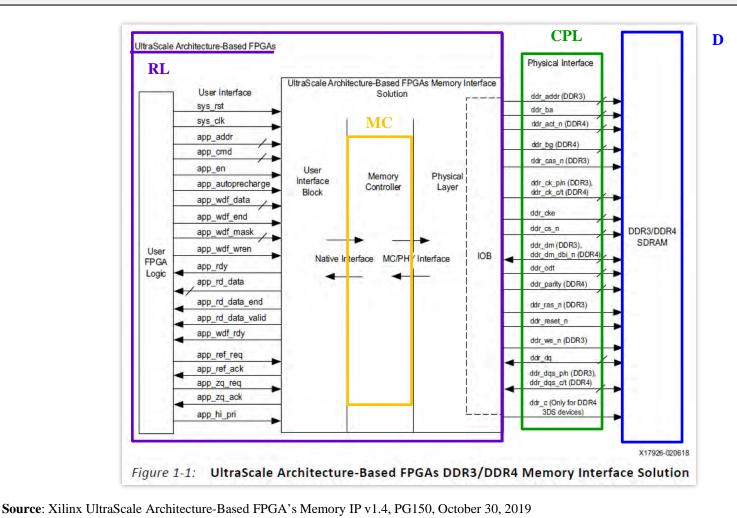

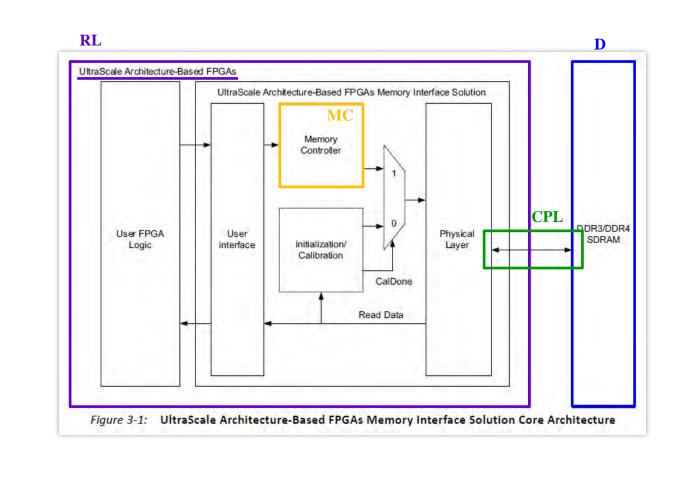

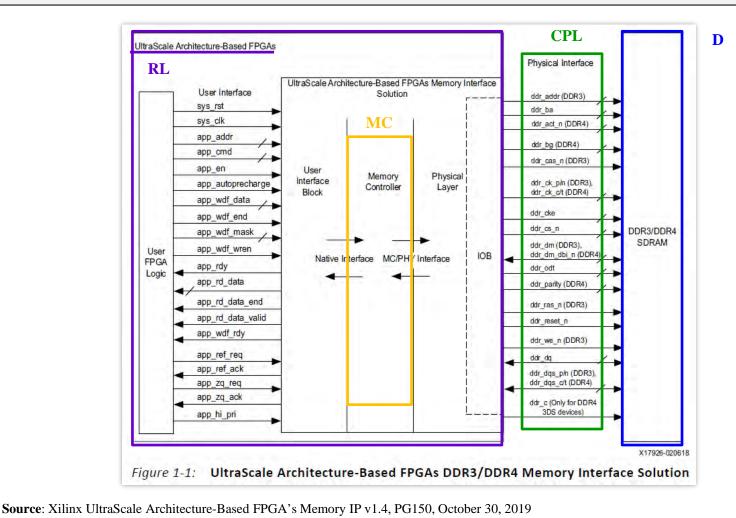

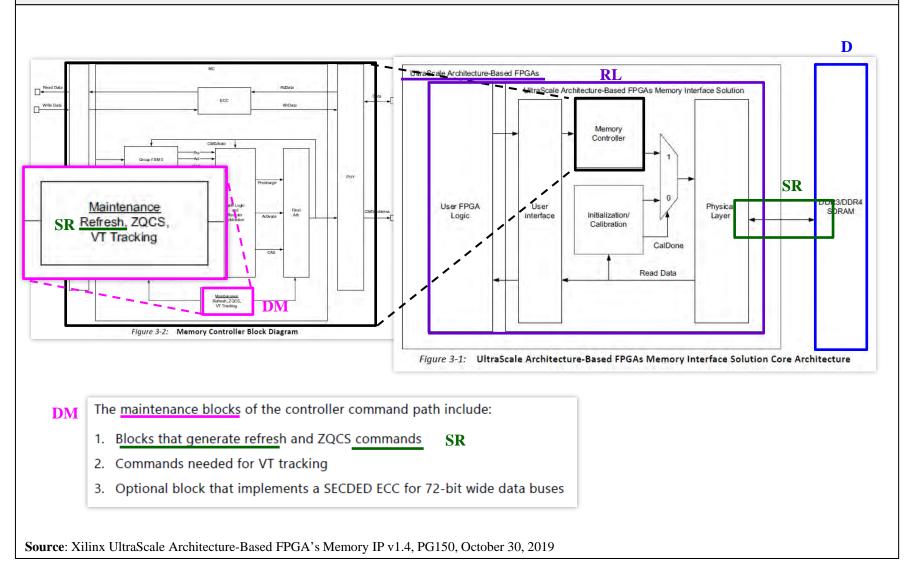

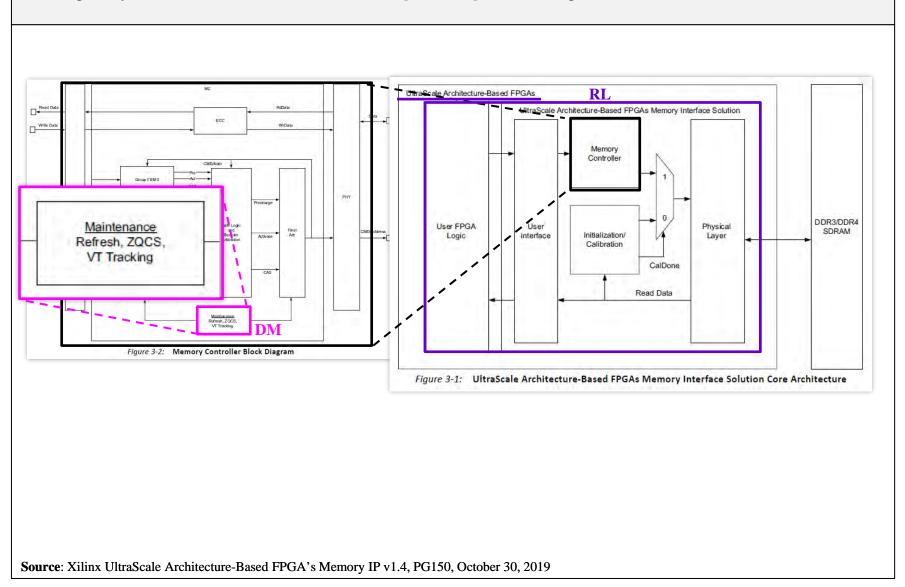

| Zynq UltraScale+     | ZU2EG, ZU3EG, ZU4EG,                         |                             |

| MPSoC: EG devices    | ZU5EG, ZU6EG, ZU7EG,                         |                             |

|                      | ZU9EG, ZU11EG, ZU15EG,                       |                             |

|                      | ZU17EG, ZU19EG                               |                             |

| Zynq UltraScale+     | ZU4EV, ZU5EV, ZU7EV                          |                             |

| MPSoC: EV devices    |                                              |                             |

| Zynq Ultrascale+     | ZU21DR, ZU25DR,                              |                             |

| RFSoC devices        | ZU27DR, ZU28DR,                              |                             |

|                      | ZU29DR, ZU39DR,                              |                             |

|                      | ZU42DR, ZU43DR,                              |                             |

|                      | ZU46DR, ZU47DR,<br>ZU48DR, ZU49DR            |                             |

| Kintex UltraScale    | ,                                            |                             |

| FPGA devices         | KU025, KU035, KU040,<br>KU060, KU085, KU095, |                             |

| IT GA devices        | KU115                                        |                             |

| Virtex UltraScale    | XCVU065, XCVU080,                            |                             |

| FPGA devices         | XCVU095, VCVU125,                            |                             |

|                      | XCVU160, XCVU190,                            |                             |

|                      | XCVU440                                      |                             |

| Spartan 7-Series     |                                              | XC7S6, XC7S15, XC7S25,      |

| FPGA devices         |                                              | XC7S50, XC7S75, XC7S100     |

| Artix 7-Series FPGA  |                                              | XC7A12T, XC7A15T,           |

| devices              |                                              | ХС7А25Т, ХС7А35Т,           |

|                      |                                              | ХС7А50Т, ХС7А75Т,           |

|                      |                                              | XC7A100T, XC7A200T          |

| Kintex 7-Series FPGA |                                              | ХС7К70Т, ХС7К160Т,          |

| devices              |                                              | XC7K325T, XCE7K325T,        |

|                      |                                              | XC7K355T, XCE7K355T,        |

|                      |                                              | ХС7К410Т, ХСЕ7К410Т,        |

| Product Family       | Exemplary Device Names     | Exemplary Part Numbers      |

|----------------------|----------------------------|-----------------------------|

|                      |                            | and/or Part Number Prefixes |

|                      |                            | XC7K420T, XCE7K420T,        |

|                      |                            | XC7K480T, XCE7K480T         |

| Virtex 7-Series FPGA |                            | XC7V585T, XCE7V585T,        |

| devices              |                            | ХС7V2000Т, ХС7VХ330Т,       |

|                      |                            | XCE7VX330T, XC7VX415T,      |

|                      |                            | XCE7VX415T, XC7VX485T,      |

|                      |                            | XCE7VX485T, XC7VX550T,      |

|                      |                            | XCE7VX550T, XC7VX690T,      |

|                      |                            | XCE7VX690T, XC7VX980T,      |

|                      |                            | XCE7VX980T, XCVX1140T,      |

|                      |                            | ХС7VH580Т, ХС7VH870Т        |

| Zynq-7000 SoC        | Z-7007S, Z-7012S, Z-7014S, | XC7Z007S, XC7Z012S,         |

| devices              | Z-7010, Z-7015, Z-7020,    | XC7Z014S, XC7Z010,          |

|                      | Z-7030, Z-7035, Z-7045,    | XC7Z015, XC7Z020, XC7Z030,  |

|                      | Z-7100                     | XC7Z035, XC7Z045,           |

|                      |                            | XC7Z100                     |

28. Each of the Accused Products includes an FPGA.

29. In contrast to a purpose-built chip which is designed with a single function in mind and then hardwired to implement it, an FPGA is more flexible.

30. An FPGA can be programmed in the field, after it has been plugged into a socket on a PC board.

31. FPGAs are based around a matrix of configurable logic blocks ("CLBs") connected via programmable interconnects.

32. FPGAs can be reprogrammed to desired application or functionality requirements after

manufacturing. This feature distinguishes FPGAs from Application Specific Integrated

Circuits (ASICs), which are custom manufactured for specific design tasks.

33. Today's FPGAs easily push the 500 MHz performance barrier.

34. Programming an FPGA is a matter of connecting CLBs to create the desired logical

functions (AND, OR, XOR, and so forth) or storage elements (flip-flops and shift registers).

35. Unlike a CPU which is primarily serial (with a few parallel elements) and has fixed-size instructions and data paths (typically 32 or 64 bit), an FPGA can be programmed to perform many operations in parallel, and the operations themselves can be of almost any width, large or small.

36. The highly parallelized model in FPGAs is ideal for building custom accelerators to process compute-intensive problems.

37. An FPGA has the potential to provide a 30x or greater speedup to many types of genomics, seismic analysis, financial risk analysis, big data search, and encryption algorithms and applications.

38. The Alveo U200 provides up to 90x higher performance than CPUs on key workloads at 1/3 the cost. *See* <u>https://www.xilinx.com/publications/product-briefs/alveo-product-brief.pdf.</u>

39. The Alveo U280 provides up to 3,000 times higher throughput than CPUs on key workloads such as Key-Value-Store. *See* <u>https://www.xilinx.com/publications/product-brief.pdf</u>.

40. Defendant's customers can use FPGAs to accelerate its applications more than 30x when compared with servers that use CPUs alone.

41. The speed increases referenced in the prior four paragraphs are a result of the FPGAs handling compute-intensive, deeply pipelined, hardware-accelerated operations, which also allows for highly parallelized computing.

## V. MARKING AND NOTICE

## A. Marking and Constructive Notice to Defendant.

42. SRC Computers complied with 35 U.S.C. § 287 by (i) placing the required notice on all, or substantially all, of its products made, offered for sale, sold, or imported into the United States, or (ii) providing actual notice to Defendant.

43. For example, SRC Computers placed notices such as the following on all, or substantially all, of its products since at least February 19, 2013:<sup>1</sup>

44. The website listed in the notice, WWW.SRCCOMP.COM/

TECHPUBS/PATENTEDTECH.ASP, stated the following:

<sup>1</sup>

*E.g.*, https://web.archive.org/web/20100930014237/http://www.srccomp.com/techpubs/pat entedtech.asp.

# **SRC<sup>®</sup> PATENTED TECHNOLOGY**

SRC Computers holds fundamental U.S. and foreign patents covering hardware and software techniques for vastly accelerating data processing through the use of reconfigurable elements comprising one or more Direct Execution Logic blocks operating in conjunction with one or more commodity microprocessors.

SRC patented technology, with filing dates back to 1997, also includes a number of general applications of Direct Execution Logic computing systems for parallelizing the execution of user-defined algorithms including acceleration of web site access and processing.

SRC Computers has exclusive rights to the following patents:

## B. Actual Notice to Defendant.

45. Xilinx is well-aware of the patent asserted in this action and that instrumentalities accused herein infringe that patent.

46. On or around February 22, 2013, counsel for SRC Computers sent a notice letter to Xilinx advising that "Our client has recently become aware of Xilinx' Zynq-7000 All Programmable SoC devices which are stated to integrate an ARM® dual-core Cortex<sup>TM</sup>-A9 CPU as an application processor unit in conjunction with programmable logic. From the information presently available to us, these devices may possibly involve SRC Computers' patented technology."

47. Between July 2015 and November 2015 SRC Computers and Xilinx communicated regarding a potential acquisition by Xilinx of SRC Computers and/or its intellectual property ("IP"). Persons involved on behalf of Xilinx included Greer Person, Ron Satori, Nate Gazdik, Michael White, and Ivo Bolsens. Persons involved on behalf of SRC Computers included Brandon Freeman and Jon Huppenthal.

48. A third party, 3LP Advisors, LLC ("3LP"), assisted with discussions on behalf of SRC Computers.

49. In order to assist Xilinx with reviewing SRC Computers' patent portfolio, 3LP provided Xilinx with a list of SRC Computers' IP on or around October 1, 2015.

50. On October 18, 2017, SRC Labs sued Amazon Web Services, Inc., Amazon.com, Inc., and VADATA, Inc. (collectively the "Amazon Defendants") alleging infringement of five patents, including the '311 patent. *SRC Labs, LLC v. Amazon Web Services, Inc.*, No. 1-17-cv-01227 (E.D. Va.). The complaint (the "Amazon Complaint") filed in that case (the "Amazon Case") alleged that the Amazon Defendants' products infringed the '311 patent based on usage of Xilinx FPGA products.

51. Moreover, specifically, the Amazon Complaint included—as Exhibit J—a publiclyavailable claim chart showing how the Amazon Defendants' product EC2 F1 Instance infringed the '311 patent based on its usage of a Xilinx UltraScale+ FPGA. Plaintiff accuses that device of infringing the '311 patent in this Second Amended Complaint and accused said device of infringement in its Original Complaint and First Amended Complaint.

52. On or around January 8, 2018, SRC Labs, LLC served Xilinx with a subpoena in the Amazon Case. That subpoena explicitly referenced the '311 patent, providing Xilinx with further notice of the patent.

53. After learning of the '311 patent, and that its products infringed that patent, on July 13, 2018 Xilinx filed a petition for *inter partes* review, requesting that the Board of Patent Trials and Appeals cancel claims 1 through 5 and 8 through 10 of the '311 patent. IPR2018-01395 (hereinafter "the Xilinx IPR"), Paper No. 1. In its petition, Xilinx noted the complaint against the Amazon Defendants and admitted that "Amazon and Xilinx have a customer/supplier

relationship" and that "Xilinx Ultrascale+ FPGAs and its Vivado Design Suite are referenced in the SRC Labs complaint . . ." That petition was denied on January 23, 2019. IPR201801395, Paper No. 17.

54. The district court case against the Amazon Defendants was transferred to the Western District of Washington on March 1, 2018. *SRC Labs, LLC et al v. Amazon Web Services*, Inc., No. 2-18-cv-00317 (W.D. Wa.).

### VI. THE PATENT

## A. Asserted Patent is Owned by SRC.

55. On January 22, 2020, DirectStream assigned both the '311 patent to SRC. The assignment was recorded with the USPTO on January 24, 2020 at Reel/Frame 051615/0344.

56. All maintenance fees have been paid to the USPTO to keep the '311 patent enforceable for its full term.

## B. Description of the Asserted Patent.

57. The '311 patent is entitled "System and method for retaining DRAM data when reprogramming reconfigurable devices with DRAM memory controllers" and issued on October 6, 2015.

58. A true and correct copy of the '311 patent is attached as Exhibit A.

59. The '311 patent is valid and enforceable.

## VII. COUNT ONE: DIRECT INFRINGEMENT OF THE '311 PATENT

60. Plaintiff incorporates by reference all paragraphs above as though set forth herein.

61. Defendant has at no time, either expressly or impliedly, been licensed under the '311 patent.

62. Defendant has and continues to directly infringe the '311 patent by making, using, offering for sale, selling, and/or importing in or into the United States in violation of 35 U.S.C.

§ 271(a) the Accused Products. For example, on information and belief Defendant tests, manufactures, and uses each of the Accused Products in an infringing manner at least in order to (1) ensure that functionality such as that appearing in SRC's claim charts attached hereto, including but not limited to those portions of the charts describing partial reconfiguration, works as described and (2) provide support regarding said reconfiguration to its customers, members of its Partner Program, such as its Premier Partners, Certified Partners, Alliance Partners, and Accelerator Partners (*see* <u>https://www.xilinx.com/alliance.html</u>) and members of its University Program (*see* <u>https://www.xilinx.com/support/university.html</u>).

63. Defendant's direct infringement of the '311 patent by the Accused Products has caused, and will continue to cause, substantial and irreparable damage to Plaintiff. Plaintiff is therefore entitled to an award of damages adequate to compensate for Defendant's infringement, but not less than a reasonable royalty, together with pre- and post-judgment interest and costs as fixed by the Court under 35 U.S.C. § 284.

64. Plaintiff adopts, and incorporates by reference, as if fully stated herein, **Exhibits B through E**, which are claim charts that describe and demonstrate how the Accused Products infringe exemplary claims of the '311 patent. These charts collectively show that Xilinx infringes at least claims 1, 3, 9, and 10 of the '311 patent.

## VIII. COUNT TWO: INDIRECT INFRINGEMENT OF THE '311 PATENT

65. Plaintiff incorporates by reference all paragraphs above as though set forth herein.

66. Defendant induces infringement under 35 U.S.C. § 271(b) by actively and knowingly aiding and abetting direct infringement by its users.

67. As discussed in § V.B, Defendant received actual and constructive notice of the '311 patent.

68. Defendant learned of its infringement of the '311 patent at least as a result of the filing of the Original Complaint and the First Amended Complaint in this case as well as the filing of this Second Amended Complaint.

69. Defendant also learned that its products infringe the '311 patent as a result of the Amazon Complaint and/or the Amazon Case.

70. Through at least the filing of the Original Complaint, the First Amended Complaint, and this Second Amended Complaint, and the claim charts attached to those complaints, Defendant learned that its actions would result in users of the Accused Products infringing the '311 patent.

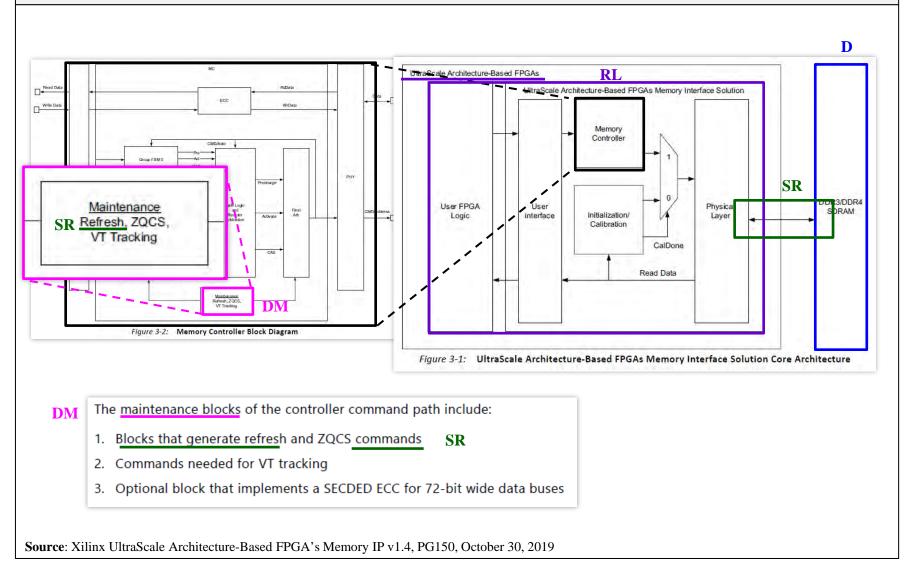

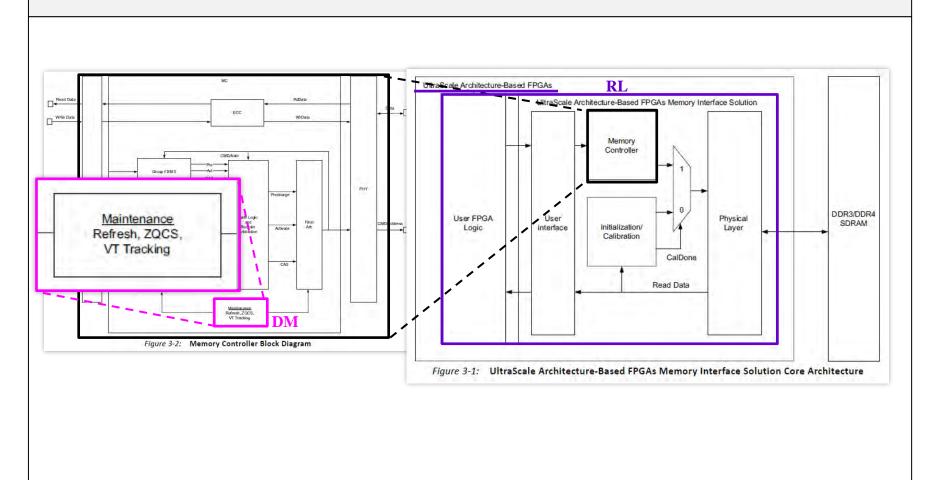

71. For example, the claim charts attached to the complaints show how Defendant's UltraScale Architecture-Based FPGA's Memory IP v1.4 LogiCORE IP Product Guide, PG150 provides explicit instructions on using the '311 Accused Products in an infringing manner, such as through partial reconfiguration.

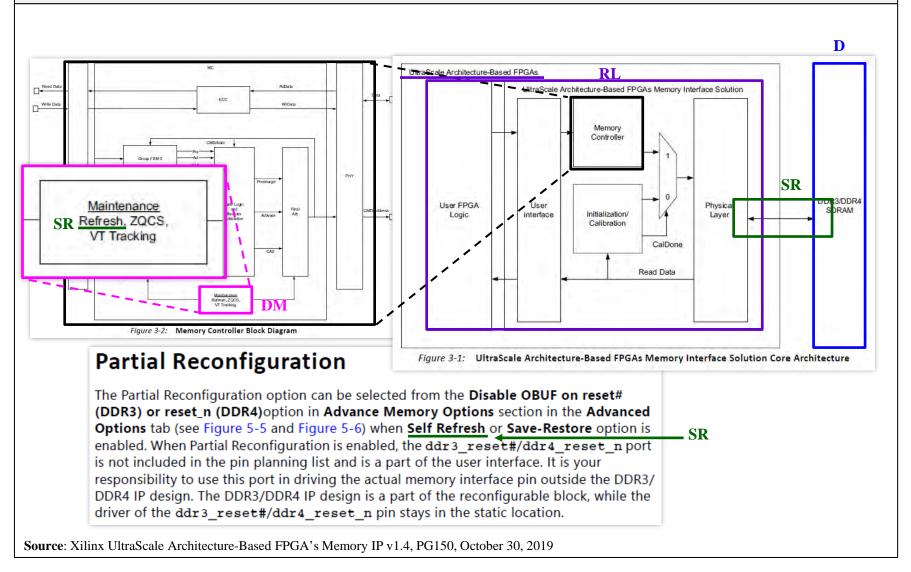

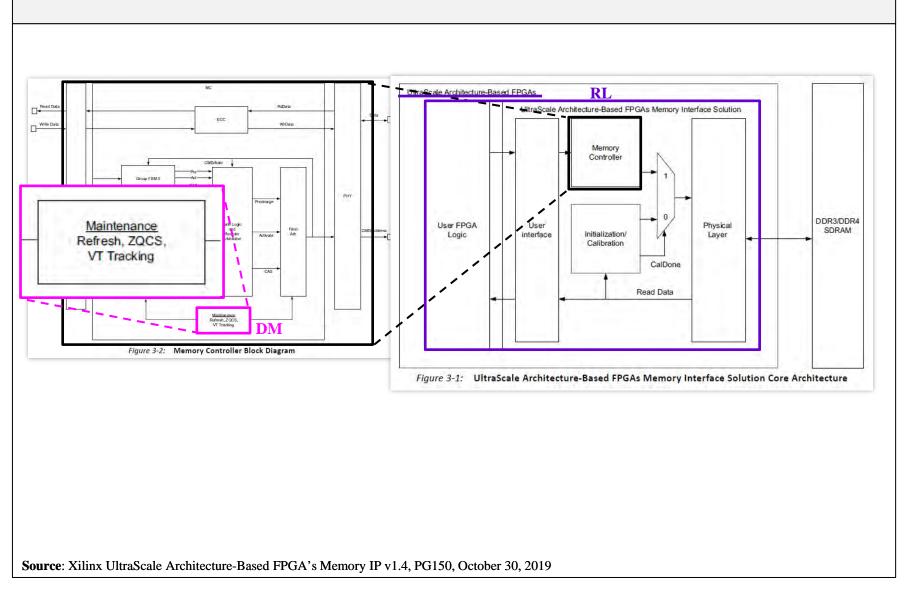

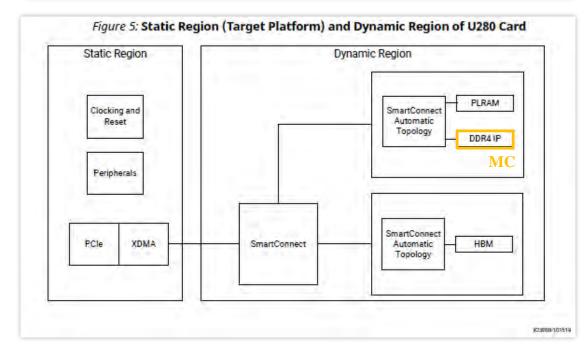

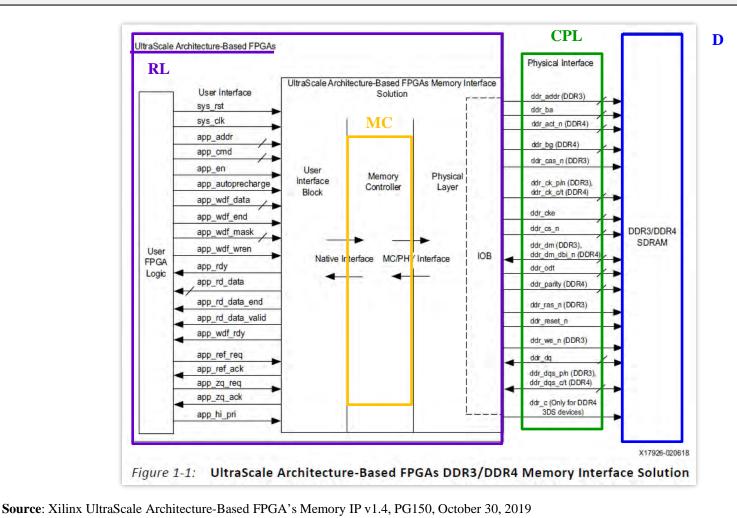

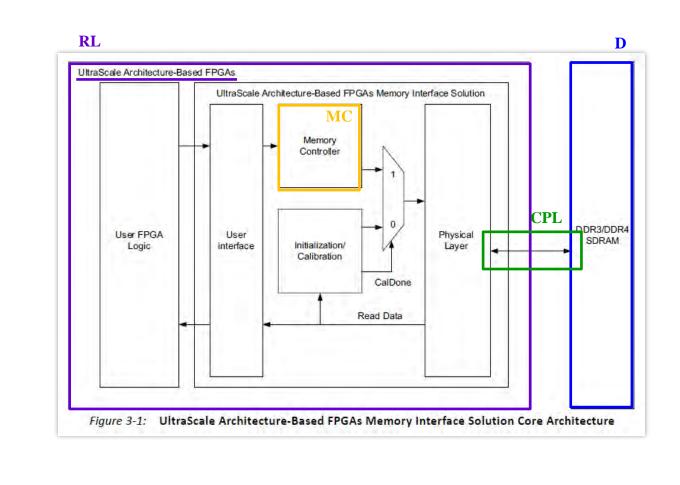

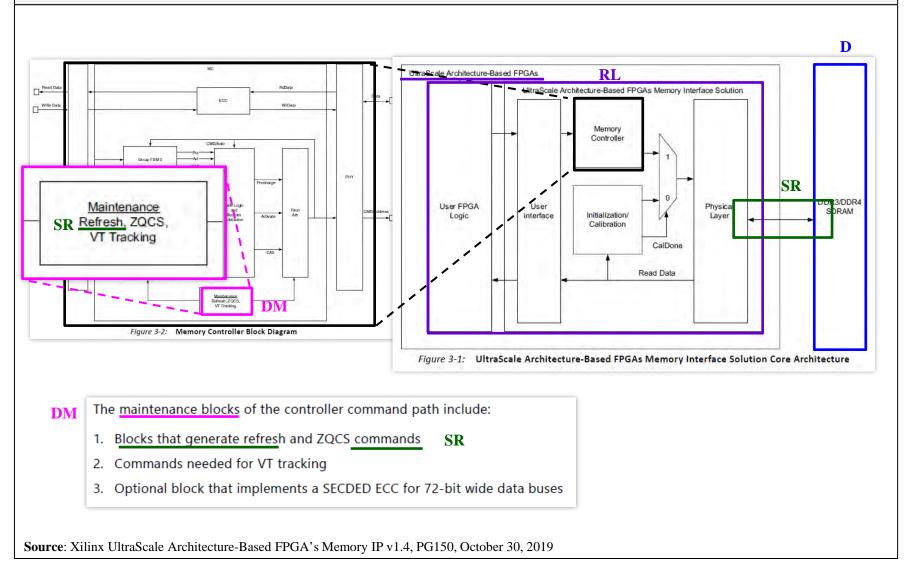

72. Defendant's UltraScale Architecture-Based FPGA's Memory IP v1.4 LogiCORE IP core described in its UltraScale Architecture-Based FPGA's Memory IP v1.4 LogiCORE IP Product Guide, PG150 provides a complete solution for interfacing external DRAM memories to the user FPGA logic. One component of this Memory IP is a memory controller with a maintenance block – both are implemented as part of the reconfigurable processor (FPGA). One of the functions this maintenance block supports is "Self Refresh." The "Self Refresh" feature keeps the DRAM in self-refresh mode; for instance, during partial reconfiguration.

73. Moreover, Defendant provides guides such as that described above, as well as training and support to its customers, members of its Partner Program, such as its Premier Partners, Certified Partners, Alliance Partners, and Accelerator Partners (*see*

https://www.xilinx.com/alliance.html) and members of its University Program (see https://www.xilinx.com/support/university.html).

74. Xilinx teaches users to use the Accused Products in an infringing manner, such as that shown by partial reconfiguration in SRC's claim charts.

75. Xilinx actively provides support services for its products. An important part of Xilinx's support services is the Xilinx Community Portal. *See*

<u>https://www.xilinx.com/community.html.</u> Xilinx hosts forums where members can ask questions and receive support both from Xilinx engineers and fellow members.

76. Defendant induces infringement of the '311 patent by marketing the Accused Products and providing LogiCORE IP cores, documentation (i.e., the UltraScale Architecture-Based FPGA's Memory IP v1.4 LogiCORE IP Product Guide, PG150), training, and support (i.e. through its Partner Program, and support for non-program members) on how to use said products in ways that infringe the '311 patent.

77. For example, Defendant induces infringement by providing Kits that allow users to develop, simulate, debug, and compile FGPA applications. Defendant actively provides support services for its Kits, and other products, directly and through its Community Forum, in which Xilinx engineers provide support to users.

78. Defendant specifically intends for users of its products to infringe and knows that its acts will result in patent infringement.

## IX. COUNT SIX: WILLFUL INFRINGEMENT OF THE '311 PATENT

79. Plaintiff incorporates by reference all paragraphs above as though set forth herein.80. Defendant has and continues to willfully infringe the '311 patent.

81. As discussed in § V.B herein, Defendant has long had knowledge of the '311 patent and that its products infringe that patent.

82. Even if Defendant had not had such knowledge previously, Defendant would learn of the '311 patent and its infringement as a result of the filing of Plaintiff's Original Complaint, the First Amended Complaint, and this Second Amended Complaint, and this district does not require pre-suit knowledge to establish willfulness. *DermaFocus LLC v. Ulthera, Inc.*, 201 F. Supp. 3d 465, 473 (D. Del. 2016).

83. Despite knowing of the '311 patent, Defendant continued and continues making, using, offering for sale, and selling the Accused Products resulting in infringement as discussed in Counts One and Two herein. At least because of its knowledge of the '311 patent and its claims, Defendant knew or should have known that its conduct resulted in infringement of several claims of the '311 patent. Moreover, Defendant was provided information regarding its infringement in the Original Complaint, the First Amended Complaint, and this Second Amended Complaint.

84. Defendant has continued its infringement of the '311 patent despite its knowing that claims 1 through 5 and 8 through 10 of the '311 patent were held valid on January 23, 2019 in the Xilinx IPR.

85. Therefore, Defendant's infringement was intentional or knowing. Defendant knows or should know that its continued activities result in infringement of the '311 patent.

86. Defendant's actions have not been consistent with the standards of behavior in its industry.

87. Defendant made no effort to avoid infringing the '311 patent.

88. Defendant's infringement of the '311 patent is willful, deliberate, and/or consciously wrongful, and therefore Plaintiff should receive enhanced damages up to three times the amount of actual damages for Defendant's willful infringement under 35 U.S.C. § 284.

## X. CONCLUSION

89. Plaintiff is entitled to recover from Defendant the damages sustained by SRC as a result of Xilinx's wrongful acts in an amount subject to proof at trial, which, by law, cannot be less than a reasonable royalty, together with interest and costs as fixed by this Court.

90. Plaintiff has incurred and will incur attorneys' fees, costs, and expenses in the prosecution of this action.

91. Plaintiff reserves the right to amend, supplement, or modify its allegations of infringement as facts regarding such allegations arise during the course of this case.

## XI. JURY DEMAND

92. Plaintiff hereby demands a trial by jury for all causes of action.

## XII. PRAYER FOR RELIEF

Plaintiff requests the following relief:

A. A judgment that Defendant has infringed and continues to infringe the '311 patent;

B. A judgment and order requiring Defendant to pay Plaintiff damages under 35 U.S.C. § 284, including treble damages for willful infringement as provided by 35 U.S.C. § 284, and supplemental damages for any continuing post-verdict infringement up until entry of the final judgment with an accounting as needed;

C. A judgment and order requiring Defendant to pay Plaintiff pre-judgment and postjudgment interest on the damages awarded;

D. A judgment and order awarding a compulsory ongoing royalty; and

E. Such other and further relief as the Court deems just and equitable.

#### PLAINTIFF'S SECOND AMENDED COMPLAINT FOR PATENT INFRINGEMENT - Page 16

Dated: March 18, 2021

Respectfully submitted,

<u>/s/ Stamatios Stamoulis</u> Stamatios Stamoulis (#4606) Richard C. Weinblatt (#5080) Two Fox Point Centre 6 Denny Road, Suite 307 Wilmington, DE 19809 Tel: (302) 999-1540 stamoulis@swdelaw.com weinblatt@swdelaw.com

SHORE CHAN DEPUMPO LLP Michael W. Shore\* (mshore@shorechan.com) Alfonso Garcia Chan\* (achan@shorechan.com) Ari B. Rafilson\* (arafilson@shorechan.com) William D. Ellerman\* (wellerman@shorechan.com) Paul T. Beeler\* (pbeeler@shorechan.com)

901 Main Street, Suite 3300 Dallas, TX 75202 Tel: (214) 593-9110 SHORE CHAN DEPUMPO LLP 901 Main Street, Suite 3300 Dallas, Texas 75202 Telephone (214) 593-9110 Facsimile (214) 593-9111

Counsel for Plaintiff FG SRC LLC

\* Admitted pro hac vice

Case 1:20-cv-00601-LPS Document 48 Filed 03/22/21 Page 18 of 113 PageID #: 1785

# EXHIBIT A

Case 1:20-cv-00601-LPS Document 48 File

US009153311B1

# (12) United States Patent

## Tewalt

#### (54) SYSTEM AND METHOD FOR RETAINING DRAM DATA WHEN REPROGRAMMING RECONFIGURABLE DEVICES WITH DRAM MEMORY CONTROLLERS

- (71) Applicant: **SRC Computers, LLC.**, Colorado Springs, CO (US)

- (72) Inventor: Timothy J. Tewalt, Larkspur, CO (US)

- (73) Assignee: **SRC Computers, LLC**, Colorado Springs, CO (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 14/288,094

- (22) Filed: May 27, 2014

- (51) Int. Cl. *G11C 7/00* (2006.01) *G11C 11/406* (2006.01)

- (52) U.S. Cl.

- CPC ...... *G11C 11/40615* (2013.01) (58) Field of Classification Search

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 6,026,459 A  | 2/2000  | Huppenthal        |

|--------------|---------|-------------------|

| 6,076,152 A  |         | Huppenthal et al. |

| 6,247,110 B1 | 6/2001  | Huppenthal et al. |

| 6,295,598 B1 | 9/2001  | Bertoni et al.    |

| 6,339,819 B1 | 1/2002  | Huppenthal et al. |

| 6,356,983 B1 | 3/2002  | Parks             |

| 6,434,687 B1 | 8/2002  | Huppenthal        |

| 6,594,736 B1 | 7/2003  | Parks             |

| 6,836,823 B2 | 12/2004 | Burton            |

|              |         |                   |

## (10) Patent No.: US 9,153,311 B1

### (45) **Date of Patent:** Oct. 6, 2015

| 6,941,539 B2 | 9/2005  | Hammes            |

|--------------|---------|-------------------|

| 6,961,841 B2 | 11/2005 | Huppenthal et al. |

| 6,964,029 B2 | 11/2005 | Poznanovic et al. |

| 6,983,456 B2 | 1/2006  | Poznanovic et al. |

| 6,996,656 B2 | 2/2006  | Burton            |

| 7,003,593 B2 | 2/2006  | Huppenthal et al. |

| 7,124,211 B2 | 10/2006 | Dickson et al.    |

| 7,134,120 B2 | 11/2006 | Hammes            |

| 7,149,867 B2 | 12/2006 | Poznanovic et al. |

| 7,155,602 B2 | 12/2006 | Poznanovic        |

| 7,155,708 B2 | 12/2006 | Hammes et al.     |

| 7,167,976 B2 | 1/2007  | Poznanovic        |

| 7,197,575 B2 | 3/2007  | Huppenthal et al. |

| 7,225,324 B2 | 5/2007  | Huppenthal et al. |

| 7,237,091 B2 | 6/2007  | Huppenthal et al. |

| 7,299,458 B2 | 11/2007 | Hammes            |

|              |         |                   |

(Continued)

#### OTHER PUBLICATIONS

Allan, Graham, "DDR IP Integration: How to Avoid Landmines in this Quickly Changing Landscape", Chip Design, Jun./Jul. 2007, pp. 20-22.

#### (Continued)

Primary Examiner — Hoai V Ho (74) Attorney, Agent, or Firm — Peter J. Meza; William J. Kubida; Hogan Lovells US LLP

#### (57) **ABSTRACT**

A system and method for retaining dynamic random access memory (DRAM) data when reprogramming reconfigurable devices with DRAM memory controllers such as field programmable gate arrays (FPGAs). The DRAM memory controller is utilized in concert with an internally or externally located data maintenance block wherein the FPGA drives the majority of the DRAM input/output (I/O) and the data maintenance block drives the self-refresh command inputs. Even though the FPGA reconfigures and the majority of the DRAM inputs are tri-stated, the data maintenance block provides stable input levels on the self-refresh command inputs.

#### 19 Claims, 2 Drawing Sheets

## US 9,153,311 B1

Page 2

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 7,373,440 | B2 | 5/2008  | Huppenthal et al. |

|-----------|----|---------|-------------------|

| 7,406,573 | B2 | 7/2008  | Huppenthal et al. |

| 7,421,524 | B2 | 9/2008  | Huppenthal et al. |

| 7,424,552 | B2 | 9/2008  | Burton            |

| 7,565,461 | B2 | 7/2009  | Huppenthal et al. |

| 7,620,800 |    | 11/2009 | Huppenthal et al. |

| 7,680,968 | B2 | 3/2010  | Burton            |

| 7,703,085 | B2 | 4/2010  | Poznanovic et al. |

| 7,890,686 | B2 | 2/2011  | Conner            |

| 8,589,666 B    | 2 11/2013 | Hammes            |

|----------------|-----------|-------------------|

| 8,713,518 B    | 2 4/2014  | Pointer et al.    |

| 2012/0117318 A | 1 5/2012  | Burton et al.     |

| 2013/0157639 A | .1 6/2013 | Huppenthal et al. |

| 2014/0211579 A | 1* 7/2014 | Lovelace          |

#### OTHER PUBLICATIONS

Wilson, Ron, "DRAM Controllers for System Designers", Altera Corporation Articles, 2012, 8 pages.

\* cited by examiner

```

U.S. Patent

```

Oct. 6, 2015

Oct. 6, 2015

Sheet 2 of 2

#### US 9,153,311 B1

5

#### SYSTEM AND METHOD FOR RETAINING DRAM DATA WHEN REPROGRAMMING RECONFIGURABLE DEVICES WITH DRAM MEMORY CONTROLLERS

#### BACKGROUND OF THE INVENTION

The present invention relates, in general, to the field of reconfigurable computing systems. More particularly, the present invention relates to a system and method for retaining <sup>10</sup> dynamic random access memory (DRAM) data when reprogramming reconfigurable devices with DRAM memory controllers.

The majority of today's programmable logic designs 15 include a DRAM based memory solution at the heart of their memory subsystem. Today's DRAM devices are significantly faster than previous generation's, albeit at the cost of requiring increasingly complex and resource intensive memory controllers. One example is in double data rate 3 and 4 (DDR3 20 and DDR4) controllers which require read and write calibration logic. This added logic was not necessary when using previous versions of DRAM (e.g. DDR and DDR2. As a result, companies are forced to absorb substantial design costs and increased project completion times when designing 25 proprietary DRAM controllers utilizing modern DRAM technology.

In order to mitigate design engineering costs and verification time, it is very common for field programmable gate array (FPGA) designers to implement vendor provided <sup>30</sup> memory controller intellectual property (IP) when including DRAM based memory solutions in their designs. See, for example, Allan, Graham; "DDR IP Integration: How to Avoid Landmines in this Quickly Changing Landscape"; Chip Design, June/July 2007; pp 20-22 and Wilson, Ron; "DRAM <sup>35</sup> Controllers for System Designers"; Altera Corporation Articles, 2012.

FPGA designers tend to choose device manufacturer IP designs because they are proven, tested and have the incredible benefit of significantly reduced design costs and project <sup>40</sup> completion times. Many times there is the added benefit of exploiting specialized circuitry within the programmable device to increase controller performance, which is not always readily apparent when designing a controller from scratch. <sup>45</sup>

The downside to using factory supplied IP memory controllers is that there is little flexibility when trying to modify operating characteristics. A significant problem arises in reconfigurable computing when the FPGA is reprogrammed during a live application and the memory controller tri-states <sup>50</sup> all inputs and outputs (I/O) between the FPGA device and the DRAM. The result is corrupted data in the memory subsystem. Therefore, dynamically reconfigurable processors are excluded as viable computing options, especially in regard to database applications or context switch processing. <sup>55</sup> The reason for this is that the time it takes to copy the entire contents of DRAM data and preserve it in another part of the system, reconfigure the processor, then finally retrieve the data and restore it in DRAM is just too excessive.

#### SUMMARY OF THE INVENTION

Disclosed herein is a system and method for preserving DRAM memory contents when a reconfigurable device, for example an FPGA having a DRAM memory controller, is 65 reconfigured, reprogrammed or otherwise powered down. When an FPGA is reprogrammed, the DRAM inputs are 2

tri-stated including self-refresh command signals. Indeterminate states on the reset or clock enable inputs results in DRAM data corruption.

In accordance with the system and method of the present invention, an FPGA based DRAM controller is utilized in concert with an internally or externally located data maintenance block. In operation, the FPGA drives the majority of the DRAM input/output (I/O) and the data maintenance block drives the self-refresh command inputs. Even though the FPGA reconfigures and the majority of the DRAM inputs are tri-stated, the data maintenance block provides stable input levels on the self-refresh command inputs.

Functionally, the data maintenance block does not contain the memory controller and therefore has no point of reference for when and how to initiate the self-refresh commands, particularly the DRAM self-refresh mode. As also disclosed herein, a communication port is implemented between the FPGA and the data maintenance block that allows the memory controller in the FPGA to direct the self-refresh commands to the DRAM via the data maintenance block. Specifically, this entails when to put the DRAM into selfrefresh mode and preserve the data in memory.

At this point, the DRAM data has been preserved throughout the FPGA reconfiguration via the self-refresh mode initiated by the data maintenance block, but the DRAM controller must now re-establish write/read timing windows and will corrupt specific address contents with guaranteed write and read data required during the calibration/leveling process. Consequently, using the self-refresh capability of DRAM alone is not adequate for maintaining data integrity during reconfiguration. (It should be noted that the memory addresses used during calibration/leveling are known and typically detailed in the controller IP specification).

In order to effectuate this, the system transmits a "reconfiguration request" to the DRAM controller. Once received, glue logic surrounding the FPGA vendor provided memory controller IP issues read requests to the controller specifying address locations used during the calibration/leveling process. As data is retrieved from the DRAM, it is transmitted via the communication port from the FPGA device to a block of storage space residing within the data maintenance block itself or another location in the system.

Once the process is complete, the data maintenance block sends a self-refresh command to the DRAM and transmits an 45 acknowledge signal back to the FPGA. The data maintenance block recognizes this as an FPGA reconfiguration condition versus an FPGA initial power up condition and retains this state for later use.

Once the FPGA has been reprogrammed, the DRAM controller has re-established calibration settings and several specific addresses in the DRAM have been corrupted with guaranteed write/read data patterns. At this point, glue logic surrounding the vendor memory controller IP is advised by the data maintenance block (through the communication 55 port) that it has awakened from either an initial power up condition or a reconfiguration condition. If a reconfiguration condition is detected, and before processing incoming DMA requests, the controller retrieves stored DRAM data from the data maintenance block (again through the communication 60 port) and writes it back to the specific address locations corrupted during the calibration/leveling process. Once complete, the DRAM controller in the FPGA is free to begin servicing system memory requests in the traditional fashion.

Among the benefits provided in conjunction with the system and method of the present invention is that since the data maintenance block functions to hold the DRAM in self-refresh mode, the FPGA is free to be reprogrammed to perform 10

a very application-specific computing job that may not require DRAM. This means all the device resources previously reserved for creating a DRAM controller are now free to be used for different functions.

Further, the overall computer system benefits from the 5 present invention because data previously stored in DRAM has now been preserved and is available for use by the next application that needs it. This leads to the fact that computing solutions requiring a series of specific data manipulation tasks now have the ability to be implemented in a small reconfigurable processor. Each application performs its intended function and data is passed from application to application between reconfiguration periods via the DRAM.

Importantly, it should also be noted that the DRAM data contents are retained even if the reconfigurable device is 15 powered down. This is especially critical, for example, when the system and method of the present invention is implemented in mobile devices.

Particularly disclosed herein is a system and method for preserving DRAM data contents when reconfiguring a device 20 containing one or more DRAM controllers. Also particularly disclosed herein is a system and method for preserving DRAM data contents in a reconfigurable computing environment when the programmable device is reconfigured with a new design that does not include a DRAM controller. Further 25 disclosed herein is a system and method for passing DRAM data between sequential computing tasks in a reconfigurable computing environment as well as system and method for preserving DRAM contents when the reconfigurable device is powered down.

Also particularly disclosed herein is a computer system which comprises a DRAM memory, a reconfigurable logic device having a memory controller coupled to selected inputs and outputs of the DRAM memory and a data maintenance block coupled to the reconfigurable logic device and self- 35 refresh command inputs of the DRAM memory. The data maintenance block is operative to provide stable input levels on the self-refresh command inputs while the reconfigurable logic device is reconfigured.

Still further particularly disclosed herein is a method for 40 preserving the contents of a DRAM memory associated with a reconfigurable device having a memory controller. The method comprises providing a data maintenance block coupled to the reconfigurable device, coupling the data maintenance block to self-refresh command inputs of the DRAM 45 memory, storing data received from the reconfigurable device at the data maintenance block and maintaining stable input levels on the self-refresh command inputs while the reconfigurable logic device is reconfigured.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The aforementioned and other features and objects of the present invention and the manner of attaining them will become more apparent and the invention itself will be best 55 understood by reference to the following description of a preferred embodiment taken in conjunction with the accompanying drawings, wherein:

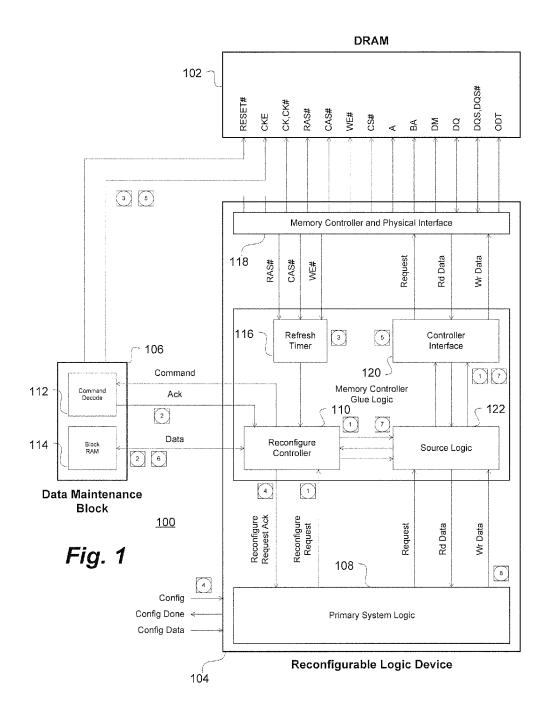

FIG. 1 is a functional block diagram of a computer subsystem comprising a reconfigurable logic device having a 60 reconfigurable DRAM controller with associated DRAM memory and illustrating the data maintenance block of the present invention for retaining DRAM data when the logic device is reconfigured; and

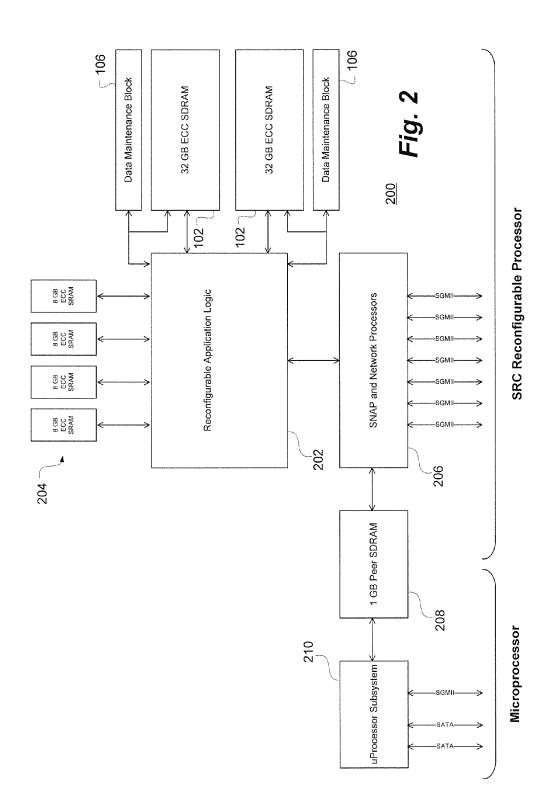

FIG. 2 is a block diagram of a reconfigurable computer 65 system, such as that available from SRC Computers, LLC, assignee of the present invention, incorporating a pair of data

4

maintenance blocks and DRAM memory in accordance with the system and method of the present invention in association with reconfigurable application logic.

#### DESCRIPTION OF A REPRESENTATIVE EMBODIMENT

With reference now to FIG. 1, a functional block diagram of a computer subsystem 100 comprising a DRAM memory 102 and reconfigurable logic device 104 is shown. In a representative embodiment of the present invention, the reconfigurable logic device 104 may comprise a field programmable gate array (FPGA). However, it should be noted that the reconfigurable logic device 104 may comprise any and all forms of reconfigurable logic devices including hybrid devices, such as a reconfigurable logic device with partial reconfiguration capabilities or an application specific integrated circuit (ASIC) device with reprogrammable regions contained within the chip.

Also illustrated is a data maintenance block 106 in accordance with the present invention for retaining DRAM memory 102 data when the logic device 104 is reconfigured during operation of the computer subsystem 100. In a representative embodiment of the present invention, the data maintenance block 106 may be conveniently provided as a complex programmable logic device (CPLD) or other separate integrated circuit device or, in alternative embodiments, may be provided as a portion of an FPGA comprising the reconfigurable logic device 104.

As illustrated, the reconfigurable logic device 104 comprises a primary system logic block 108 which issues a reconfigure request command to a reconfigure controller 110 and receives a reconfigure request acknowledgement (Ack) signal in return. The reconfigure controller 110, in turn, issues a command to the command decode block 112 of the data maintenance block 106 and receives an acknowledgement (Ack) signal in return. A block RAM portion 114 of the data maintenance block 106 exchanges data with the reconfigure controller 110.

The reconfigure controller 110 receives an input from a refresh timer 116 which is coupled to receive row address select (RAS#), column address select (CAS#) and write enable (WE#) signals from a memory controller and physical interface block 118. The memory controller and physical interface block 118 also provides the RAS#, CAS# and WE# signals to the DRAM memory 102 as well as clock (CR, CK#), chip select (CS#), address (A), bank address (BA), data mask (DM) and on-die termination (ODT) input signals. Bididrectional data (DQ) input/output (I/O) and differential 50 data strobe signals (DQS/DQS#) are exchanged between the DRAM memory 102 and the memory controller and physical interface block 118 as shown. The data maintenance block 106 is coupled to the DRAM memory 102 to supply reset (RESET#) and clock enable (CKE#) signals thereto.

The memory controller and physical interface block 118 responds to a request from the controller interface 120 to provide data read from the DRAM memory 102 (Rd Data) and to receive data to be written to the DRAM memory 102 (Wr Data) as shown. A source logic block 122 is coupled to the controller interface 120 as well as the reconfigure controller 110 as also illustrated. The source logic block 122 receives a data request from the primary system logic block 108 and supplies data read from the DRAM memory 102 while receiving data to be written thereto.

As indicated by the operation at numeral 1, a reconfiguration request is received at the reconfigure controller 110 from the primary system logic block 108 of the reconfigurable US 9,153,311 B1

logic device **104**. The reconfigure controller **110** initiates direct memory access (DMA) read requests to memory addresses used in a calibration/leveling sequence after the reconfigurable logic device **104** is reconfigured. Returned data is stored in a small section of block RAM (not shown) in 5 the reconfigure controller **110**.

As indicated by the operation at numeral 2, the reconfigure Controller 110 stores its block RAM contents in another small section of block RAM 114 located in the data maintenance block 106. When complete, the data maintenance block 10 106 asserts an acknowledge signal from its command decode block 112. At the operation indicated by numeral 3, the reconfigure controller 110 detects a refresh command from the refresh timer 116, waits a refresh cycle time ( $t_{RFC}$ ) and instructs the data maintenance block 106 to de-assert CKE to 15 the DRAM memory 102.

The reconfigure controller **110** asserts the Reconfigure Request Ack signal at the operation indicated by numeral **4** and the reconfigurable logic device **104** is reconfigured. As indicated by the operation at numeral **5**, the reconfigure controller **110** recognizes a post-reconfigure condition (Ack=High), holds the memory controller and physical interface **118** in reset and instructs the data maintenance block **106** to assert CKE to the DRAM memory **102**. The memory controller and physical interface **118** is then released from 25 reset and initializes the DRAM memory **102**.

At the operation indicated by numeral **6**, the reconfigure controller **110** retrieves the data maintenance block **106** block RAM **114** contents and stores it in a small section of block RAM (not shown) in the reconfigure controller **110**. The 30 reconfigure controller **110** detects that the memory controller and physical interface **118** and DRAM memory **102** initialization is complete at the operation indicated by numeral **7** and initiates DMA write requests to restore the memory contents corrupted during the calibration/leveling sequence with 35 the data values read prior to reconfiguration. At the operation indicated by numeral **8**, the memory controller and physical interface **118** glue logic (comprising reconfigure controller **110**, refresh timer **116**, controller interface **120** and source logic block **122**) resumes DMA activity with the primary 40 system logic **108** in a conventional fashion.

It should be noted certain of the aforementioned operational steps may, in fact, operate substantially concurrently. Further, while functionally accurate, some of the operational steps enumerated have been listed out of order to provide 45 logical continuity to the overall operation and to facilitate comprehensibility of the process. In a particular implementation of the system and method of the present invention, one or more of the operational steps disclosed may be conveniently re-ordered to increase overall hardware efficiency. 50 Moreover, steps which can serve to facilitate relatively seamless integration in an active application can be provided in addition to those described as may be desired.

With reference additionally now to FIG. **2**, a block diagram of a reconfigurable computer system **200** is illustrated incorporating a pair of data maintenance blocks **106** and DRAM memory **102** in accordance with the system and method of the present invention in association with reconfigurable application logic **202**. In this representative embodiment of a reconfigurable computer system **200**, the DRAM memory **102** is 60 illustrated in the form of **32** GB error correction code (ECC) synchronous dynamic random access memory (SDRAM).

The reconfigurable application logic **202** is coupled to the data maintenance blocks **106** and DRAM memory **102** as depicted and described previously with respect to the preced- 65 ing figure and is also illustrated as being coupled to a number of 8 GB ECC static random access memory (SRAM) memory

6

modules **204**. The reconfigurable application logic **202** is also coupled to an SRC Computers, LLC SNAP<sup>TM</sup> and network processors block **206** having a number of serial gigabit media independent interface (SGMII) links as shown. It should be noted that the DRAM memory **102** controller in the reconfigurable application block **202** may be omitted upon subsequent reconfigurations as the DRAM memory **102** data contents will be maintained in the data maintenance blocks **106**.

The SNAP and network processors block **206** shares equal read/write access to a 1 GB peer SDRAM system memory **208** along with a microprocessor subsystem **210**. The microprocessor subsystem **210**, as illustrated, also comprises an SGMII link as well as a pair of serial advanced technology attachment (SATA) interfaces.

For continuity and clarity of the description herein, the term "FPGA" has been used in conjunction with the representative embodiment of the system and method of the present invention and refers to just one type of reconfigurable logic device. However, it should be noted that the concept disclosed herein is applicable to any and all forms of reconfigurable logic devices including hybrid devices, inclusive of reconfigurable logic devices with partial reconfiguration capabilities or an ASIC device with reprogrammable regions contained within the chip.

Representative embodiments of dynamically reconfigurable computing systems incorporating the DRAM memory 102, reconfigurable logic device 104, associated microprocessors and programming techniques are disclosed in one or more of the following United States Patents and United States Patent Publications to SRC Computers LLC, assignee of the present invention, the disclosures of which are herein specifically incorporated by this reference in their entirety: U.S. Pat. No. 6,026,459; U.S. Pat. No. 6,076,152; U.S. Pat. No. 6,247, 110; U.S. Pat. No. 6,295,598; U.S. Pat. No. 6,339,819; U.S. Pat. No. 6,356,983; U.S. Pat. No. 6,434,687; U.S. Pat. No. 6,594,736; U.S. Pat. No. 6,836,823; U.S. Pat. No. 6,941,539; U.S. Pat. No. 6,961,841; U.S. Pat. No. 6,964,029; U.S. Pat. No. 6,983,456; U.S. Pat. No. 6,996,656; U.S. Pat. No. 7,003, 593; U.S. Pat. No. 7,124,211; U.S. Pat. No. 7,134,120; U.S. Pat. No. 7,149,867; U.S. Pat. No. 7,155,602; U.S. Pat. No. 7,155,708; U.S. Pat. No. 7,167,976; U.S. Pat. No. 7,197,575; U.S. Pat. No. 7,225,324; U.S. Pat. No. 7,237,091; U.S. Pat. No. 7,299,458; U.S. Pat. No. 7,373,440; U.S. Pat. No. 7,406, 573; U.S. Pat. No. 7,421,524; U.S. Pat. No. 7,424,552; U.S. Pat. No. 7,565,461; U.S. Pat. No. 7,620,800; U.S. Pat. No. 7,680,968; U.S. Pat. No. 7,703,085; U.S. Pat. No. 7,890,686; U.S. Pat. No. 8,589,666; U.S. Pat. Pub. No. 2012/0117318; U.S. Pat. Pub. No. 2012/0117535; and U.S. Pat. Pub. No. 2013/0157639.

While there have been described above the principles of the present invention in conjunction with specific apparatus and methods, it is to be clearly understood that the foregoing description is made only by way of example and not as a limitation to the scope of the invention. Particularly, it is recognized that the teachings of the foregoing disclosure will suggest other modifications to those persons skilled in the relevant art. Such modifications may involve other features which are already known per se and which may be used instead of or in addition to features already described herein. Although claims have been formulated in this application to particular combinations of features, it should be understood that the scope of the disclosure herein also includes any novel feature or any novel combination of features disclosed either explicitly or implicitly or any generalization or modification thereof which would be apparent to persons skilled in the relevant art, whether or not such relates to the same invention as presently claimed in any claim and whether or not it miti-

#### US 9,153,311 B1

-5

gates any or all of the same technical problems as confronted by the present invention. The applicants hereby reserve the right to formulate new claims to such features and/or combinations of such features during the prosecution of the present application or of any further application derived therefrom.

As used herein, the terms "comprises", "comprising", or any other variation thereof, are intended to cover a nonexclusive inclusion, such that a process, method, article, or apparatus that comprises a recitation of certain elements does not necessarily include only those elements but may include 10 other elements not expressly recited or inherent to such process, method, article or apparatus. None of the description in the present application should be read as implying that any particular element, step, or function is an essential element which must be included in the claim scope and THE SCOPE 15 OF THE PATENTED SUBJECT MATTER IS DEFINED ONLY BY THE CLAIMS AS ALLOWED. Moreover, none of the appended claims are intended to invoke paragraph six of 35 U.S.C. Sect. 112 unless the exact phrase "means for" is employed and is followed by a participle. 20

What is claimed is:

**1**. A computer system comprising:

a DRAM memory;

- a reconfigurable logic device having a memory controller <sup>25</sup> coupled to selected inputs and outputs of said DRAM memory; and

- a data maintenance block coupled to said reconfigurable logic device and self-refresh command inputs of said DRAM memory, said data maintenance block operative <sup>30</sup> to provide stable input levels on said self-refresh command inputs while said reconfigurable logic device is reconfigured.

2. The computer system of claim 1 wherein said DRAM memory comprises DDR3 compliant memory devices.

**3**. The computer system of claim **1** wherein said reconfigurable logic device comprises an FPGA.

**4**. The computer system of claim **1** wherein said data maintenance block comprises a command decode portion coupled to a reconfigure controller of said reconfigurable logic device. <sup>40</sup>

**5**. The computer system of claim **4** wherein said command decode portion of said data maintenance block is operative in response to a command from said reconfigure controller and provides an acknowledgement signal in response.

**6**. The computer system of claim **1** wherein said data main-<sup>45</sup> tenance block comprises a memory block coupled to a reconfigure controller of said reconfigurable logic device.

7. The computer system of claim **6** wherein said memory block is operative to retain data received from said reconfigure controller of said reconfigurable logic device. 50

**8**. The computer system of claim **1** wherein said data maintenance block comprises a CPLD.

**9**. The computer system of claim **1** wherein said reconfigurable logic device comprises said data maintenance block.

8

**10**. The computer system of claim **1** wherein said data maintenance block is operable to hold said DRAM memory in self-refresh mode while said reconfigurable logic device is reconfigured.

**11**. A method for preserving contents of a DRAM memory associated with a reconfigurable device having a memory controller comprising:

- providing a data maintenance block coupled to said reconfigurable device;

- coupling said data maintenance block to self-refresh command inputs of said DRAM memory;

- storing data received from said reconfigurable device at said data maintenance block; and

- maintaining stable input levels on said self-refresh command inputs while said reconfigurable logic device is reconfigured.

**12**. The method of claim **11** wherein said step of providing comprises:

providing a command decode portion of said data maintenance block coupled to receive commands from said reconfigurable device and return acknowledgment signals in response thereto.

**13**. The method of claim **11** wherein said step of storing comprises:

providing a memory block in said data maintenance block for storing said data received from said reconfigurable device and returning said data to said reconfigurable device upon completion of a reconfiguration function.

14. The method of claim 11 wherein said step of storing comprises:

providing a memory block in said data maintenance block for storing said data received directly from said DRAM memory and returning said data directly to said DRAM memory upon completion of a reconfiguration function.

**15**. The method of claim **11** wherein said step of providing <sub>35</sub> said data maintenance block comprises:

providing a portion of said reconfigurable device as said data maintenance block.

**16**. The method of claim **11** wherein said step of providing said data maintenance block comprises:

providing a CPLD as said data maintenance block.

17. The method of claim 11 wherein said step of providing said data maintenance block comprises:

- providing a block RAM for storing said data received from said reconfigurable device; and

- providing a command decode portion responsive to said reconfigurable device and coupled to said reset and lock enable inputs of said DRAM memory.

18. The method of claim 11 further comprising:

passing said data between sequential computing tasks in a reconfigurable computing environment.

19. The method of claim 11 further comprising:

preserving said data at said data maintenance block while said reconfigurable logic device is powered down.

\* \* \* \* \*

Case 1:20-cv-00601-LPS Document 48 Filed 03/22/21 Page 27 of 113 PageID #: 1794

# EXHIBIT B

| (12) | United States Patent<br>Tewalt                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (10) Patent No.: US 9,153,311 B1<br>(45) Date of Patent: Oct. 6, 2015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (54) | SYSTEM AND METHOD FOR RETAINING<br>DRAM DATA WHEN REPROGRAMMING<br>RECONFIGURABLE DEVICES WITH DRAM<br>MEMORY CONTROLLERS                                                                                                                                                                                                                                                                                                                                                              | 6.941,559 B2 9.2005 Hammes<br>6.961,341 B2 11.2005 Huppenhal et al.<br>6.984,025 B2 11.2005 Poznanovic et al.<br>6.984,645 B2 11.2006 Poznanovic et al.<br>6.996,656 B2 2.2006 Burton<br>7.003.593 B2 2.2006 Huppenhal et al.                                                                                                                                                                                                                                                                                                                                |

| (71) | Applicant: SRC Computers, LLC., Colorado<br>Springs, CO (US)                                                                                                                                                                                                                                                                                                                                                                                                                           | 7,124,211 B2 10/2006 Dickson et al.<br>7,134,120 B2 11/2006 Hammes<br>7,149,867 B2 12/2006 Poznanovic et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (72) | Inventor: Timothy J. Tewalt, Larkspur, CO (US)                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7,155,602 B2 12/2006 Poznanovic<br>7,155,708 B2 12/2006 Hammes et al.<br>7,167,976 B2 1/2007 Poznanovic                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (73) | Assignee: SRC Computers, LLC, Colorado<br>Springs, CO (US)                                                                                                                                                                                                                                                                                                                                                                                                                             | 7,107,976 BZ 1/2007 Poznanovic<br>7,197,575 BZ 3/2007 Huppenthal et al.<br>7,225,324 BZ 5/2007 Huppenthal et al.<br>7,237,091 BZ 6/2007 Huppenthal et al.                                                                                                                                                                                                                                                                                                                                                                                                    |

| (*)  | Notice: Subject to any disclaimer, the term of this<br>patent is extended or adjusted under 35<br>U.S.C. 154(b) by 0 days.                                                                                                                                                                                                                                                                                                                                                             | 7,299,458 B2 11/2007 Hammes<br>(Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (21) | Appl. No.: 14/288,094                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OTHER PUBLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | Filed: May 27, 2014                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Allan, Graham, "DDR IP Integration: How to Avoid Landmines ir<br>this Quickly Changing Landscape", Chip Design, Jun./Jul. 2007, pp                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | Int. Cl.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20-22.<br>(Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | GIIC 700         (2006.01)           GIIC 11/406         (2006.01)           US. CL.         GIIC 11/40615 (2013.01)           Field of Classification Search         56/222           USPC                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | U.S. PATENT DOCUMENTS<br>6,026,49 A 2:2000 Hoppenhal of al.<br>6,026,49 B 2:000 Hoppenhal of al.<br>6,025,49 B 10 2:000 Hoppenhal of al.<br>6,255,59 B 11 9:2001 Hoppenhal of al.<br>6,356,69 B 11 9:2002 Hoppenhal of al.<br>6,356,69 B 13:3002 Hoppenhal of al.<br>6,356,69 B 14:3003 Hoppenhal<br>6,356,69 B 14:2003 Hoppenhal<br>6,356,69 B 14:2003 Hoppenhal | devices with DRAM memory controllers with as field pro-<br>grammable gate arrays (FPGAs). The DRAM memory con-<br>troller is utilized in concert with an internally or externally<br>located data maintenance block wherein the FPGA drives the<br>majority of the DRAM input/cutput (IG) and the data main-<br>tenance block drives the self-effesh command inputs. Free<br>though the FPGA reconfigures and the majority of the DRAM<br>inputs are tristed, the data maintenance block, providee<br>suble input levels on the self-refresh command inputs. |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

**Title:** SYSTEM AND METHOD FOR RETAINING DRAM DATA WHEN REPROGRAMMING RECONFIGURABLE DEVICES WITH DRAM MEMORY CONTROLLERS

Priority Date: May 27, 2014

**Filed Date:** May 27, 2014

**Issued Date:** Oct. 06, 2015

Expiration Date: May 27, 2034

**Inventor:** Timothy J. Tewalt

**Exemplary Claims:** 1, 3, 9, 10

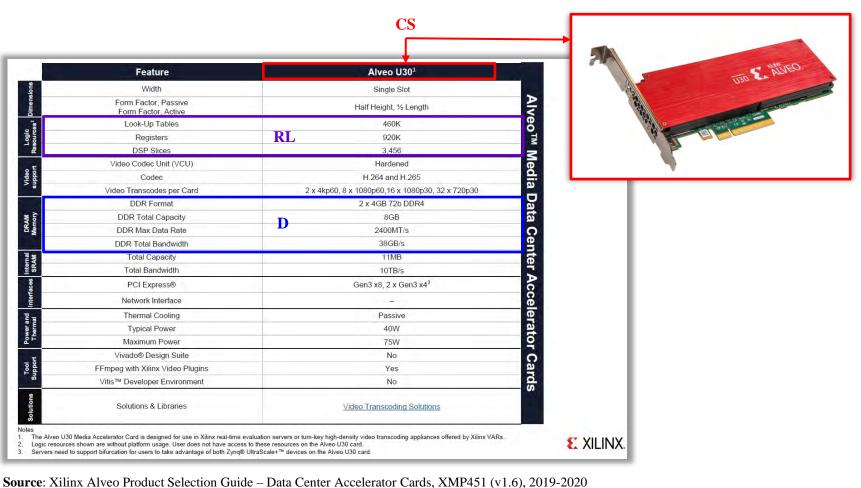

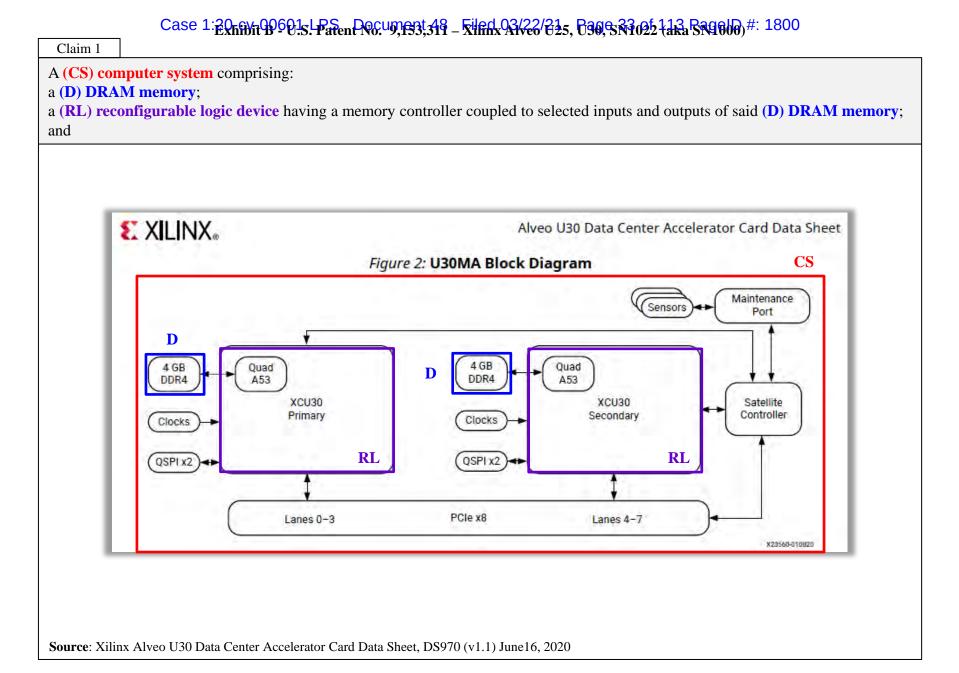

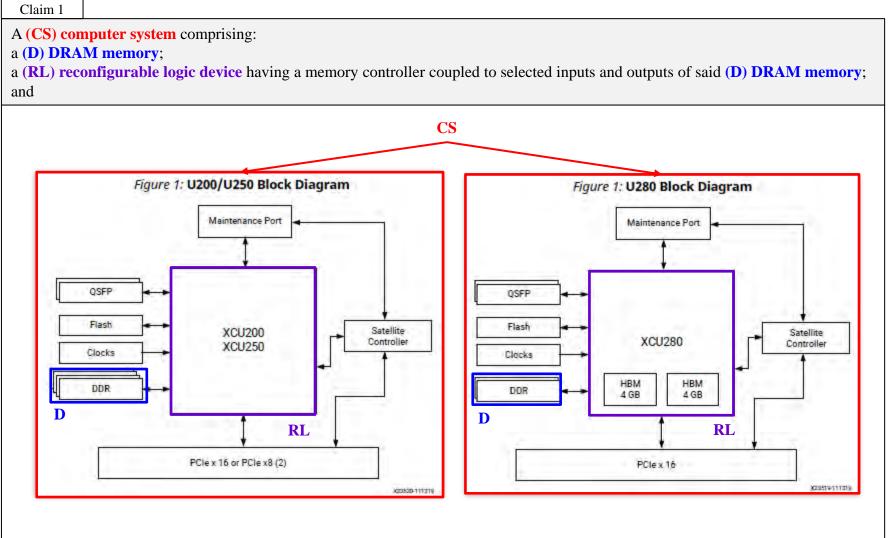

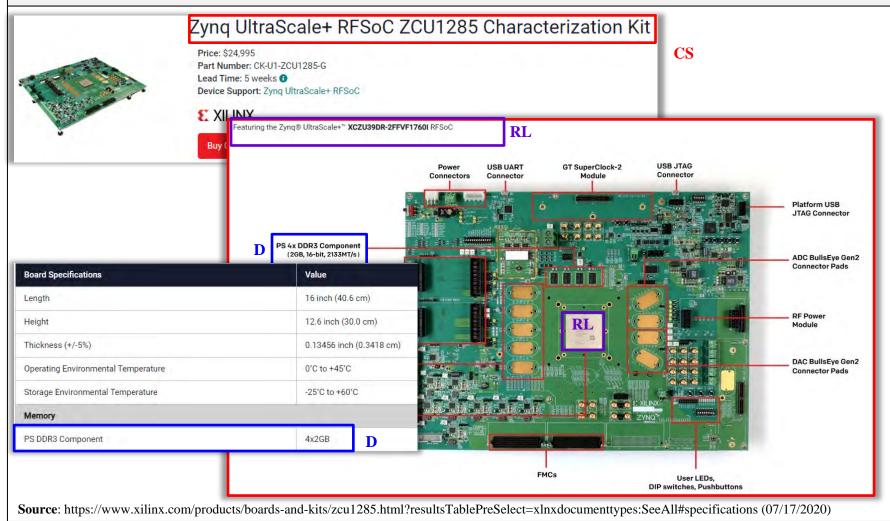

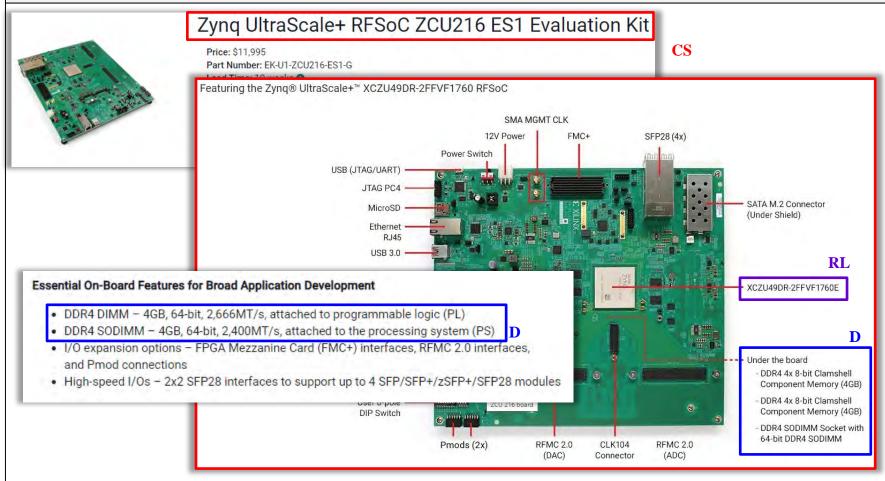

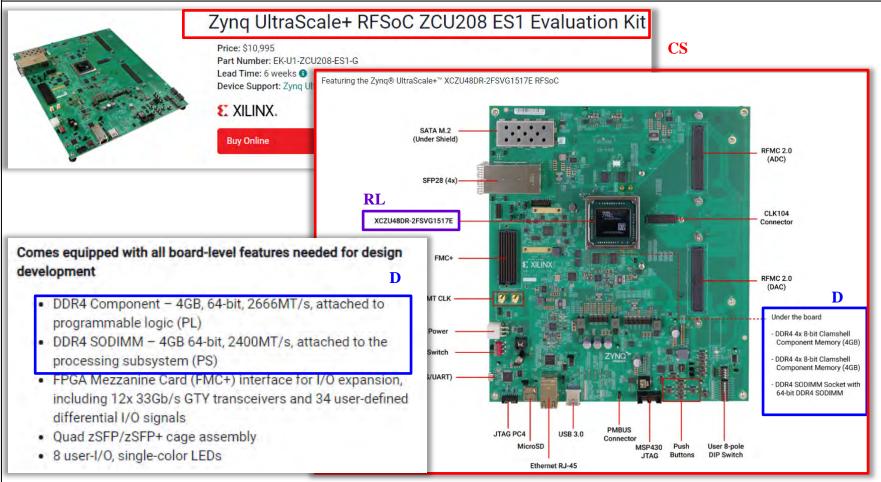

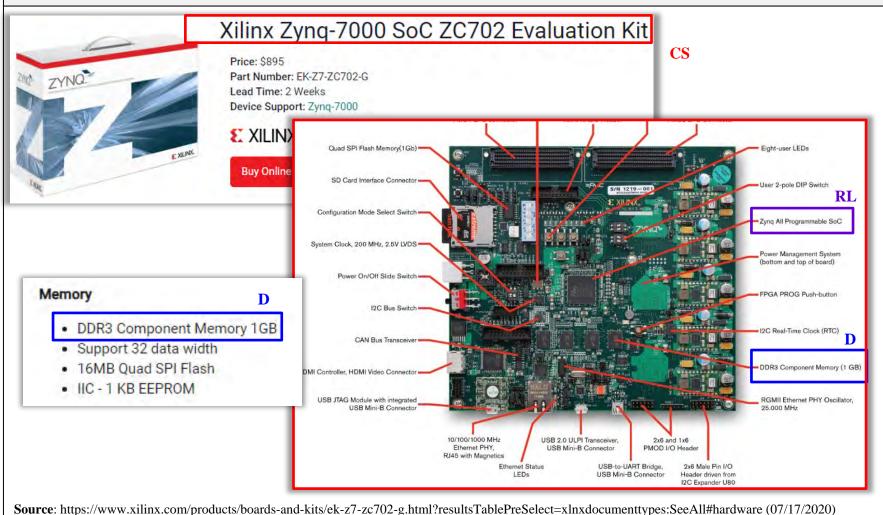

A (CS) computer system comprising:

a (D) DRAM memory;

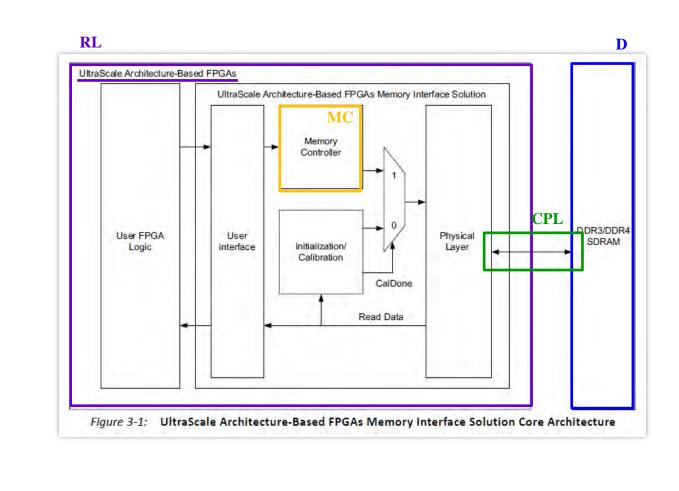

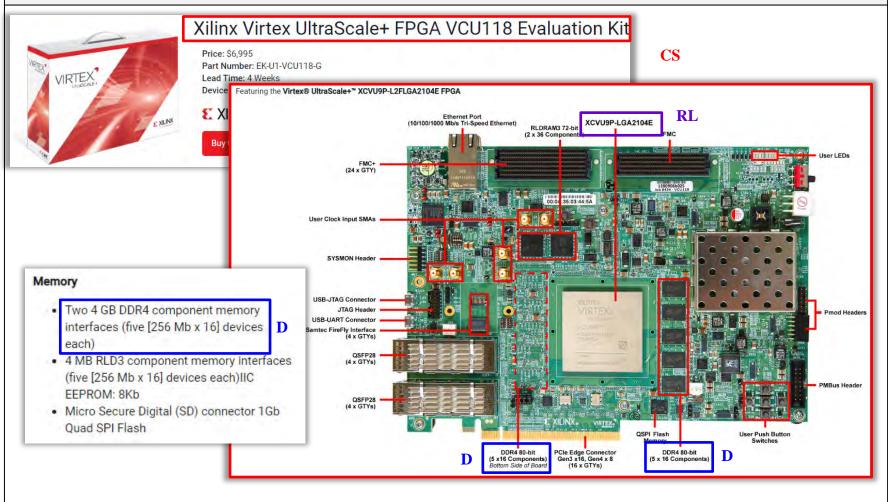

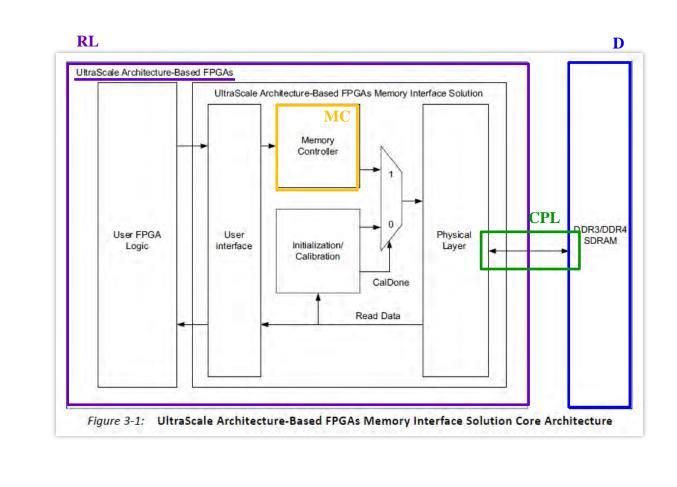

a (RL) reconfigurable logic device having a (MC) memory controller (CPL) coupled to selected inputs and outputs of said (D) DRAM memory; and

a (DM) data maintenance block coupled to said (RL) reconfigurable logic device and (SR) self-refresh command inputs of said (D) DRAM memory,

said (DM) data maintenance block (SIL) operative to provide stable input levels on said (SR) self-refresh command inputs while said (RL) reconfigurable logic device is (R) reconfigured.

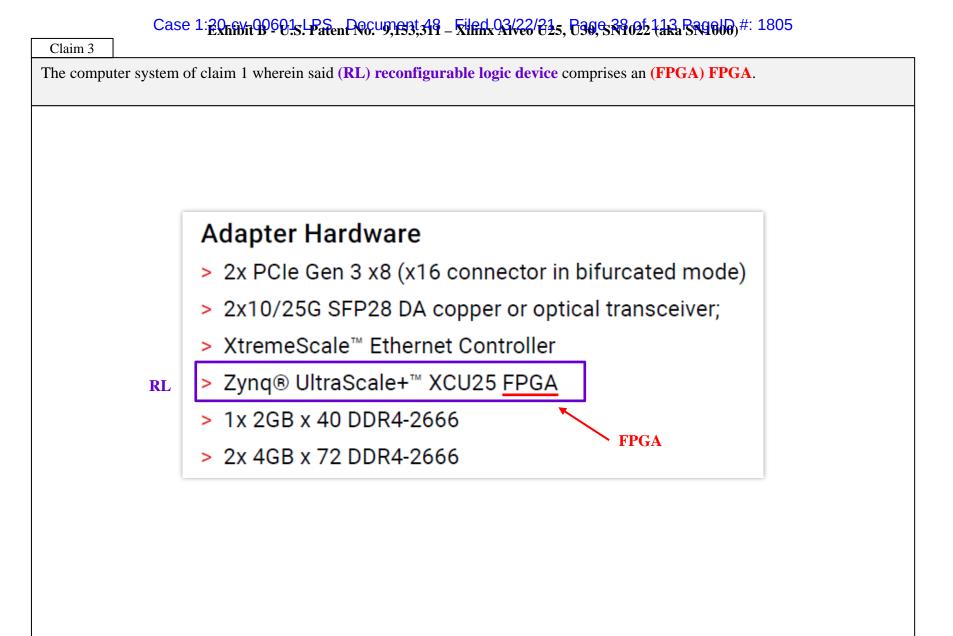

# Claim 3

The computer system of claim 1 wherein said (RL) reconfigurable logic device comprises an (FPGA) FPGA.

# Claim 9

The computer system of claim 1 wherein said (**RL**) reconfigurable logic device comprises said (**DM**) data maintenance block.

# Claim 10