# IN THE UNITED STATES DISTRICT COURT FOR THE EASTERN DISTRICT OF TEXAS MARSHALL DIVISION

RAMPART ASSET MANAGEMENT LLC, § Plaintiff, § v. § TEXAS INSTRUMENTS, INC., § Defendant. §

Case No.

JURY TRIAL DEMANDED

# **COMPLAINT FOR PATENT INFRINGEMENT**

Plaintiff Rampart Asset Management LLC ("Rampart" or "Plaintiff") for its Complaint against Defendant Texas Instruments, Inc., ("Defendant") alleges as follows:

# THE PARTIES

1. Rampart is a limited liability company organized and existing under the laws of the State of Texas, with its principal place of business located at 133 East Tyler Street, Longview, Texas, 75601.

2. Upon information and belief, Defendant Texas Instruments, Inc. ("TI") is a publicly traded corporation organized and existing under the laws of the State of Delaware, with its principal place of business located at 12500 TI Boulevard, Dallas, Texas 75243.

3. On information and belief, TI is a technology company in the business of researching, developing, making, using, and selling semiconductor products, including the TI-branded products accused of infringement in this case by Rampart (the "Accused Products" defined below).

### **JURISDICTION**

4. This is an action for patent infringement arising under the patent laws of the United States, 35 U.S.C. §§ 1, *et seq.* This Court has jurisdiction over this action pursuant to 28 U.S.C. §§ 1331 and 1338(a) and 1367.

5. This Court has personal jurisdiction over the Defendant consistent with the requirements of the Due Process Clause of the United States Constitution and the Texas Long Arm Statute. Defendant TI has its principal place of business in Dallas, Texas, where it employs more than 20,000 employees.

6. TI has, thereby, committed acts of direct infringement in the United States and in this District in violation of Rampart's intellectual property rights.

7. Venue is proper in this Judicial District pursuant to 28 U.S.C. §§ 1391(b) and 1400(b) because Defendant is subject to personal jurisdiction in this District, has committed acts of patent infringement in this District, and has a regular and established place of business in this District, including at least a commercial manufacturing facility located at 6412 U.S. Highway 75, Sherman, Texas, 75090. In addition to its existing facilities in this District, Texas Instruments has, upon information and belief, commenced its construction activities with respect to a new \$30 billion chip manufacturing facility also located in this District. Further, upon information and belief, Defendant has previously admitted or not contested proper venue in this District in other patent infringement actions.

### PATENTS-IN-SUIT

8. On June 14, 2016, the United States Patent and Trademark Office duly and legally issued U.S. Patent No. 9,367,248 (the "248 Patent") entitled "Memory Component with Pattern

# Case 2:22-cv-00024-JRG-RSP Document 1 Filed 01/21/22 Page 3 of 80 PageID #: 3

Register Circuitry to Provide Data Patterns for Calibration." A true and correct copy of the '248 Patent is attached as Exhibit A.

9. On August 1, 2017, the United States Patent and Trademark Office duly and legally issued U.S. Patent No. 9,721,642 (the "'642 Patent") entitled "Memory Component with Pattern Register Circuitry to Provide Data Patterns for Calibration." A true and correct copy of the '642 Patent is attached as Exhibit B.

10. On January 29, 2019, the United States Patent and Trademark Office duly and legally issued U.S. Patent No. 10,192,609 (the "609 Patent") entitled "Memory Component with Pattern Register Circuitry to Provide Data Patterns for Calibration." A true and correct copy of the '609 Patent is attached as Exhibit C.

11. On May 29, 2007, the United States Patent and Trademark Office duly and legally issued U.S. Patent No. 7,225,311 (the "311 Patent") entitled "Method and Apparatus for Coordinating Memory Operations Among Diversely-Located Memory Components." A true and correct copy of the '311 Patent is attached as Exhibit D.

12. On July 3, 2012, the United States Patent and Trademark Office duly and legally issued U.S. Patent No. 8,214,616 (the "616 Patent") entitled "Memory Controller Device Having Timing Offset Capability." A true and correct copy of the '616 Patent is attached as Exhibit E.

13. On June 25, 2013, the United States Patent and Trademark Office duly and legally issued U.S. Patent No. 8,472,511 (the "511 Patent") entitled "Selectable-Tap Equalizer." A true and correct copy of the '511 Patent is attached as Exhibit F.

14. Rampart is the sole and exclusive owner of all right, title, and interest in the'248 Patent, the '642 Patent, the '609 Patent, the '311 Patent, the '616 Patent, and the '511 Patent, (collectively, the "Patents-in-Suit"), and holds the exclusive right to take all actions necessary to

enforce its rights to the Patents-in-Suit, including the filing of this patent infringement lawsuit. Rampart also has the right to recover all damages for past, present, and future infringement of the Patents-in-Suit and to seek injunctive relief as appropriate under the law.

15. Rampart has at all times complied with the marking provisions of 35 U.S.C. § 287 with respect to the Patents-in-Suit.

# **FACTUAL ALLEGATIONS**

16. The Patents-in-Suit generally cover systems and methods for coordinating memory operations and providing data patterns for calibration of memory systems.

17. The '248 Patent generally relates to the field of digital circuits and, more particularly, to an apparatus and method for phase adjustment and memory device signaling systems. The technology described in the '248 Patent was developed by Craig E. Hampel, Richard E. Perego, Stefanos Sidiropoulos, Ely K. Tsern, and Frederick A. Ware. By way of example, this technology is implemented today in memory systems that adjust the phase of data signals to compensate for phase offset variations between devices during normal operation.

18. The '642 Patent generally relates to the field of digital circuits and, more particularly, to an apparatus and method for phase adjustment and memory device signaling systems. The technology described in the '642 Patent was developed by Craig E. Hampel, Richard E. Perego, Stefanos Sidiropoulos, Ely K. Tsern, and Frederick A. Ware. By way of example, this technology is implemented today in memory systems that adjust the phase of data signals to compensate for phase offset variations between devices during normal operation.

19. The '609 Patent generally relates to the field of digital circuits and, more particularly, to an apparatus and method for phase adjustment and memory device signaling systems. The technology described in the '609 Patent was developed by Craig E. Hampel, Richard

# Case 2:22-cv-00024-JRG-RSP Document 1 Filed 01/21/22 Page 5 of 80 PageID #: 5

E. Perego, Stefanos Sidiropoulos, Ely K. Tsern, and Frederick A. Ware. By way of example, this technology is implemented today in memory systems that adjust the phase of data signals to compensate for phase offset variations between devices during normal operation.

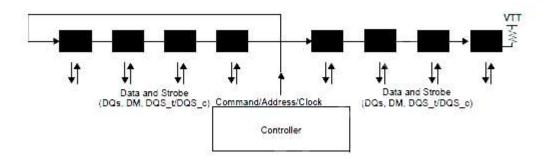

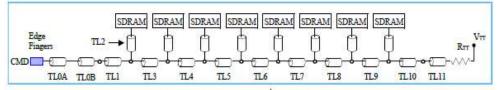

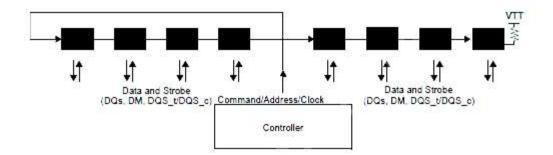

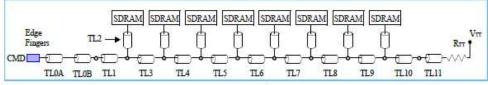

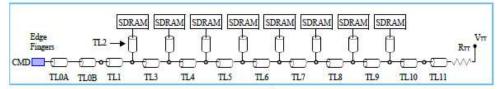

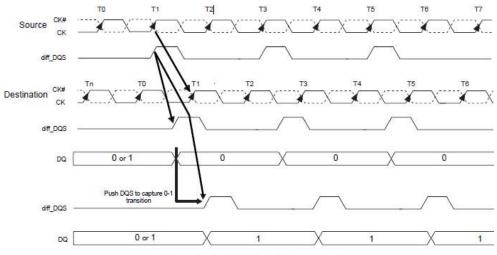

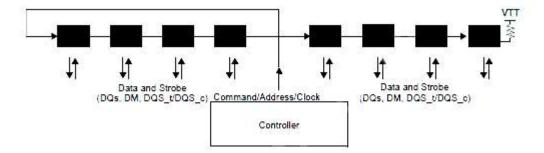

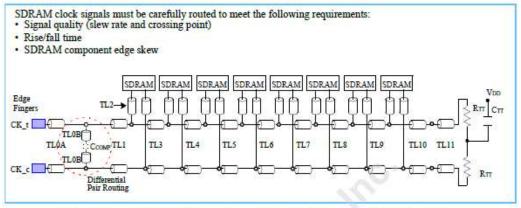

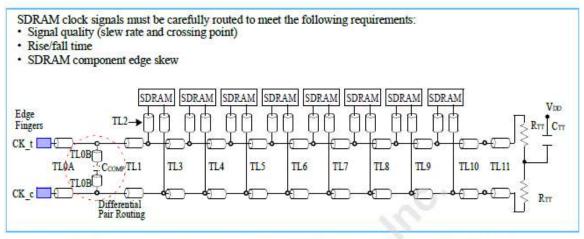

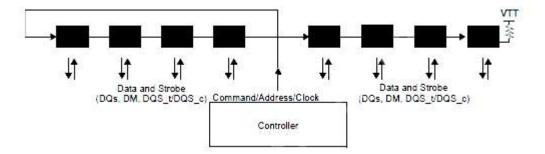

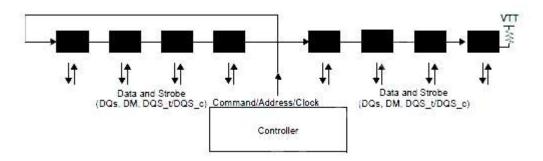

20. The '311 Patent generally relates to information storage and retrieval and, more specifically, to coordinating memory operations among diversely-located memory components. The technology described in the '311 Patent was developed by Frederick A. Ware, Ely K. Tsern, Richard E. Perego, and Craig E. Hampel. By way of example, this technology is implemented today in memory systems that configure multiple memory components to account for address bus and data bus propagation delays.

21. The '616 Patent generally relates to information storage and retrieval and, more specifically, to coordinating memory operations among diversely-located memory components. The technology described in the '616 Patent was developed by Frederick A. Ware, Ely K. Tsern, Richard E. Perego, and Craig E. Hampel. By way of example, this technology is implemented today in memory systems that configure multiple memory components to account for address bus and data bus propagation delays.

22. The '511 Patent generally relates to high speed signaling within and between integrated circuit devices and, more particularly, to reducing latent signal distortions in high speed signaling systems. The technology described in the '511 Patent was developed by Jared L. Zerbe, Vladimir M. Stojanovic, and Fred F. Chen. By way of example, this technology is implemented today in memory systems that perform iterative testing of signal wires and use pass/fail to correctly set a parameter during initialization.

23. TI has infringed and is continuing to infringe one or more of the Patents-in-Suit by making, using, selling, offering to sell, and/or importing, and by actively inducing others to make,

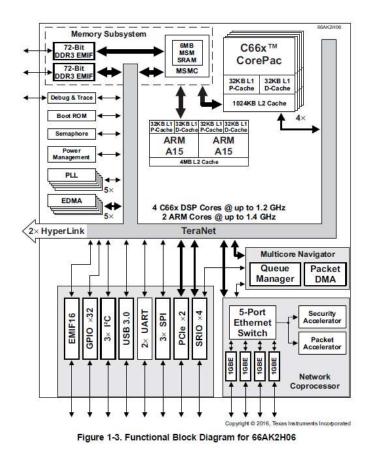

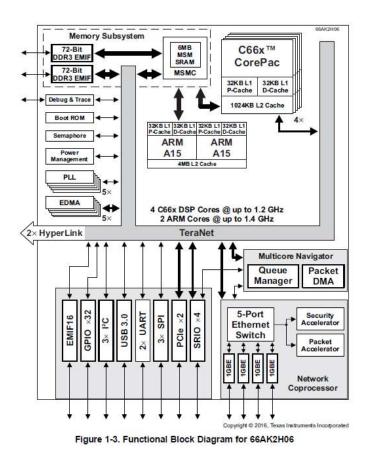

use, sell, offer to sell, and/or import memory controllers that support one or more of the DDR3, DDR3L, and DDR4 (the "Accused Products"). Such products include, but are not limited to, the TI DRA780, DRA781, DRA782, DRA783, DRA784, DRA785, DRA786, DRA787, DRA788, TMS320C6655, TMS320C6657, 66AK2G12, 66AK2H06, 66AK2H12, 66AK2H14, DRA744P, DRA745P, DRA746P, DRA750P, DRA751P, DRA752P, DRA754P, DRA755P, DRA756P, DRA710, DRA712, DRA714, DRA716, DRA724, DRA722, DRA725, DRA767P, DRA77xP, DRA790, DRA791, DRA793, DRA797, TDA2P-ABZ, TDA2P-ACD, TDA2EG-17, TDA2EG, TDA2EGABC, TDA2HF, TDA2SX, TDA2SG, TDA2SA, TDA2HG, TDA2HV, TDA2LF, AM4372, AM4376, AM4377, AM4378, AM4379, AM5748, AM5749, AM5706, AM5708, AM5716, AM5718, AM5726, AM5728, AM5729, AM6441, AM6442, AM6421, AM6412, and AM6411 Sitara Processors

# <u>COUNT I</u> (Infringement of the '248 Patent)

24. Paragraphs 1 through 23 are incorporated by reference as if fully set forth herein.

25. Rampart has not licensed or otherwise authorized Defendant to make, use, offer for sale, sell, or import any products that embody the inventions of the '248 Patent.

26. Defendant has and continues to directly infringe the '248 Patent, either literally or under the doctrine of equivalents, without authority and in violation of 35 U.S.C. § 271, by making, using, offering to sell, selling, and/or importing into the United States the Accused Products including, but not limited to, products supporting DDR4 external memories, such as the TI AM6442, AM6441, AM6421, AM6412, and AM6411 Sitara Processors.

27. For example, Defendant has and continues to directly infringe at least Claim 1 of the '248 Patent by making, using, offering to sell, selling, and/or importing into the United States products that include a memory controller that complies with the DDR4 standard. For example,

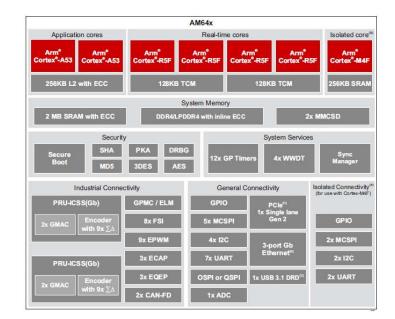

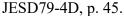

the TI AM6442 processor includes DDR4 memory controllers capable of controlling a memory system consisting of DDR4 SDRAM memory integrated circuits, each of which is compliant with the JEDEC standard JESD79-4, as shown by the AM64x Sitara Processors Datasheet, SPRSP56B, dated August 2021, p.5:

# Memory subsystem:

- Up to 2MB of On-chip RAM (OCSRAM) with SECDED ECC:

- Can be divided into smaller banks in increments of 256KB for as many as 8 separate memory banks

- Each memory bank can be allocated to a single core to facilitate software task partitioning

- DDR Subsystem (DDRSS)

- Supports LPDDR4, DDR4 memory types

- 16-Bit data bus with inline ECC

- Supports speeds up to 1600 MT/s

AM64x Sitara Processors Datasheet, SPRSP56B, August 2021, p. 1.

| FEATURES                                                                                | REFERENCE<br>NAME | AM6442                                  | AM6441                                 | AM6422           | AM6421                                 | AM6412      | AM6411      |  |

|-----------------------------------------------------------------------------------------|-------------------|-----------------------------------------|----------------------------------------|------------------|----------------------------------------|-------------|-------------|--|

| CTRLMMR_WKUP_JTAG_DEVICE_ID[31:13] DEVICE_ID register<br>bit field value <sup>(1)</sup> |                   | D: 0x19464<br>E: 0x19465<br>F: 0x19466  | D: 0x19264<br>E: 0x19265<br>F: 0x19266 | C: 0x19423       | D: 0x19224<br>E: 0x19225<br>F: 0x19226 | C: 0x19403  | C: 0x19203  |  |

| PROCESSORS AND ACCELERATORS                                                             |                   | 10<br>10                                | 517 - 55<br>51                         |                  | ° °                                    | λ           |             |  |

| Speed Grades                                                                            | -                 |                                         | en 20.                                 | See Ta           | ible 7-1                               |             | 12          |  |

| Arm Cortex-A53 Microprocessor Subsystem                                                 | Arm A53           | Dual Core                               | Single Core                            | Dual Core        | Single Core                            | Dual Core   | Single Core |  |

| Arm Cortex-R5F                                                                          | Arm R5F           | 2 x<br>Dual Core                        | 2 x<br>Dual Core                       | 1 x<br>Dual Core | 1 ×<br>Dual Core                       | Single Core | Single Core |  |

| Arm Cortex-M4F                                                                          | Arm M4F           | Single Core                             |                                        |                  |                                        |             | 3           |  |

| Device Management Security Controller                                                   | DMSC-L            | ŝ.                                      |                                        | Y                | es                                     |             |             |  |

| Cryto Accelerators                                                                      | Security          | Yes                                     |                                        |                  |                                        |             |             |  |

| MCU domain with Arm Cortex-M4F                                                          | Safety            | Yes                                     |                                        |                  |                                        |             |             |  |

| PROGRAM AND DATA STORAGE                                                                | Act 416. 3        |                                         |                                        |                  |                                        |             |             |  |

| On-Chip Shared Memory (RAM) in MAIN Domain                                              | OCSRAM            | 2MB                                     |                                        |                  |                                        |             |             |  |

| R5F Tightly Coupled Memory (TCM)                                                        | TCM               | 256KB                                   | 256KB                                  | 256KB            | 256KB                                  | 128KB       | 128KB       |  |

| On-Chip Shared Memory (RAM) in M4F Domain                                               | MCU_MSRAM         | 256KB                                   |                                        |                  |                                        |             |             |  |

| DDR4/LPDDR4 DDR Subsystem                                                               | DDRSS             | Up to 2GB (16-bit data) with inline ECC |                                        |                  |                                        |             |             |  |

### Table 5-1. Device Comparison

AM64x Sitara Processors Datasheet, SPRSP56B, August 2021, p. 7.

28. The required characteristics of DDR4 memories and memory systems and, therefore, of DDR4 memory controllers and their encompassing integrated circuits are defined by JEDEC in a collection of publicly available standards. In particular, standard JESD79-4 is the standard defining DDR4 SDRAMs, and JESD79-4D is the latest version of that standard, dated July 2021:

This document defines the DDR4 SDRAM specification, including features, functionalities, AC and DC characteristics, packages, and ball/signal assignments. The purpose of this Standard is to define the minimum set of requirements for JEDEC compliant 2 Gb through 16 Gb for x4, x8, and x16 DDR4 SDRAM devices. This standard was created based on the DDR3 standards (JESD79-3) and some aspects of the DDR and DDR2 standards (JESD79, JESD79-2).

JESD79-4D, p. 1.

29. The Accused Products including DDR4 memory controllers include a first circuit to transmit commands to the memory component, the commands including a read command that specifies data to be accessed from a memory core of the memory component. DDR4 SDRAM memory controllers, including the TI AM6442 processor, include a first circuit which is a driver circuit that sends commands to the DDR4 SDRAM using certain pins (*e.g.*, DDR0\_RAS\_n, DDR0\_CAS\_n, and DDR0\_WE\_n). One such command is a read command that specifies the data to be accessed from a memory core.

## 6.3.2 DDRSS 6.3.2.1 MAIN Domain

| SIGNAL NAME  | PIN TYPE | DESCRIPTION                      | ALV |

|--------------|----------|----------------------------------|-----|

| DDR0_ACT_n   | 0        | DDRSS Activation Command         | H2  |

| DDR0_ALERT_n | 10       | DDRSS Alert                      | H1  |

| DDR0_CAS_n   | 0        | DDRSS Column Address Strobe      | J5  |

| DDR0_PAR     | 0        | DDRSS Command and Address Parity | К5  |

| DDR0_RAS_n   | 0        | DDRSS Row Address Strobe         | F6  |

| DDR0_WE_n    | 0        | DDRSS Write Enable               | H4  |

AM64x Sitara Processors Datasheet, SPRSP56B, August 2021, p. 74.

JESD79-4 calls these signals at the DDR4 SDRAMs RAS\_n/A16, CAS\_n/A15, and WE\_n/A14.

# 2.7 Pinout Description

### Table 3 — Pinout Description

| Symbol                             | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                                  |       | The oper particular synance is marked by programmed to exame the Linear.                                                                                                                                                                                                                                                                                                        |

| ACT_n                              | Input | Activation Command Input : ACT_n defines the Activation command being entered along<br>with CS_n. The input into RAS_n/A16, CAS_n/A15 and WE_n/A14 will be considered as<br>Row Address A16, A15 and A14                                                                                                                                                                        |

| RAS_n/A16. CAS_n/<br>A15. WE_n/A14 | Input | Command Inputs: RAS_n/A18, CAS_n/A15 and WE_n/A14 (along with CS_n) define the<br>command being entered. Those pins have multi function. For example, for activation<br>with ACT_n Low, those are Addressing like A16,A15 and A14 but for non-activation<br>command with ACT_n High, those are Command pins for Read, Write and other<br>command defined in command truth table |

|                                    |       | command defined in command truth table<br>Input Data Mack and Data Rus Inversion: DM in is an input mask signal for write dat                                                                                                                                                                                                                                                   |

JESD79-4D p. 5.

#### 4.1 Command Truth Table

(a) Note 1,2,3 and 4 apply to the entire Command truth table

(b) Note 5 applies to all Read/Write commands.

[BG=Bank Group Address, BA=Bank Address, RA=Row Address, CA=Column Address, BC\_n=Burst Chop, X=Don't Care, V=Valid].

| the second second                               | Starrowski.       | C                      | KE               |      | -     |               |               | 01-1         |             | in a second |       |              |                     |            |       |        |

|-------------------------------------------------|-------------------|------------------------|------------------|------|-------|---------------|---------------|--------------|-------------|-------------|-------|--------------|---------------------|------------|-------|--------|

| Function                                        | Abbrevia-<br>tion | Previ-<br>ous<br>Cycle | Current<br>Cycle | C8_n | ACT_n | RAS_n<br>/A16 | CA8_n<br>JA16 | WE_N'<br>A14 | 800-<br>801 | BA0-<br>BA1 | C2-C0 | A12/<br>B0_0 | A17,<br>A13,<br>A11 | A10/<br>AP | 8A-0A | NOTE   |

| Mode Register Set                               | MRS               | н                      | н                | L    | н     | L             | L             | L            | BG          | BA          | ٧     |              | OP C                | ode        |       | 12     |

| Refresh                                         | REF               | н                      | н                | L    | н     | L             | L             | Н            | ٧           | ٧           | ٧     | V            | ٧                   | V          | V     | 8      |

| Self Refresh Entry                              | SRE               | н                      | L                | L    | н     | L             | L             | н            | ٧           | ٧           | V     | V            | ٧                   | ٧          | ٧     | 7,9    |

| Self Refresh Exit                               | SRX               | 1                      | н                | н    | Х     | X             | Х             | Х            | х           | Х           | Х     | Х            | Х                   | X          | X     | 7.8.9  |

| Self Refresh Exit                               | SRA               |                        |                  | L    | н     | н             | н             | н            | V           | ٧           | ٧     | V            | ٧                   | ۷          | ٧     | 10     |

| Single Bank Precharge                           | PRE               | H                      | н                | L    | н     | L             | н             | L            | BG          | BA          | ٧     | V            | ٧                   | L          | V     | S .    |

| Precharge all Banks                             | PREA              | H                      | н                | L    | н     | L             | н             | L            | V           | ٧           | ٧     | ٧            | ٧                   | н          | V     |        |

| RFU                                             | RFU               | н                      | н                | L    | н     | L             | н             | н            |             |             |       | RFU          |                     |            |       |        |

| Bank Activate                                   | ACT               | н                      | Н                | L    | L     | Row A         | Addres        | s (RA)       | BG          | BA          | ٧     | Roy          | v Addr              | ess (F     | (AS   | 8      |

| Write (Fixed BL8 or BC4)                        | WR                | н                      | н                | L    | н     | н             | L             | L            | BG          | BA          | ۷     | V            | ۷                   | L          | CA    | į.     |

| Write (BC4, on the Fly)                         | WRS4              | н                      | н                | L    | н     | н             | L             | L            | BG          | BA          | V     | L            | ٧                   | L          | CA    | 2      |

| Write (BL8, on the Fly)                         | WRS8              | н                      | н                | L    | н     | н             | L             | L            | BG          | BA          | ٧     | н            | ٧                   | L          | CA    | 5      |

| Write with Auto Precharge<br>(Fixed BL8 or BC4) | WRA               | н                      | н                | E.S. | н     | H             | E             | L            | BG          | BA          | v     | V            | v                   | н          | CA    | 2      |

| Write with Auto Precharge<br>(BC4, on the Fly)  | WRAS4             | н                      | н                | L    | н     | H             | E.            | L            | BG          | BA          | v     | Æ            | ٧                   | н          | CA    | 5<br>2 |

| Write with Auto Precharge<br>(BL8, on the Fly)  | WRAS8             | H                      | н                | L    | н     | н             | L             | L            | BG          | BA          | ٧     | н            | ٧                   | н          | CA    |        |

| Read (Fixed BL8 or BC4)                         | RD                | н                      | н                | L    | H     | н             | L             | н            | BG          | BA          | V     | V            | V                   | L          | CA    |        |

| Read (BC4, on the Fly)                          | RDS4              | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | ٧     | L            | ٧                   | L          | CA    |        |

| Read (BL8, on the Fly)                          | RDS8              | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | ٧     | н            | ٧                   | L          | CA    | ŝ      |

| Read with Auto Precharge<br>(Fixed BL8 or BC4)  | RDA               | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | ٧     | ٧            | ٧                   | н          | CA    |        |

| Read with Auto Precharge<br>(BC4, on the Fly)   | RDAS4             | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | ٧     | L            | ٧                   | н          | CA    |        |

| Read with Auto Precharge<br>(BL8, on the Fly)   | RDAS8             | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | ٧     | н            | ۷                   | н          | CA    |        |

| No Operation                                    | NUP               | н                      | н                | L    | н     | н             | н             | н            | v           | v           | v     | v            | v                   | v          | v     | 10     |

| Device Deselected                               | DES               | н                      | н                | н    | Х     | х             | Х             | Х            | Х           | Х           | Х     | Х            | Х                   | Х          | Х     | 8      |

| Power Down Entry                                | PDE               | н                      | L                | н    | Х     | Х             | Х             | Х            | Х           | Х           | Х     | X            | X                   | х          | Х     | 6      |

| Power Down Exit                                 | PDX               | L                      | н                | н    | X     | X             | X             | Х            | х           | Х           | X     | X            | X                   | X          | X     | 6      |

| ZQ calibration Long                             | ZQCL              | н                      | н                | L    | н     | н             | н             | L            | ٧           | V           | V     | V            | ٧                   | н          | V     |        |

| ZQ calibration Short                            | ZQCS              | н                      | н                | 1    | н     | н             | н             | 1            | v           | V           | V     | V            | V                   | 1          | V     | ĕ      |

Table 35 — Command Truth Table

# JESD79-4D, p. 29.

Among the commands that DDR4 SDRAMs can respond to are Read commands. A Read command is provided to a DDR4 SDRAM by sending a command in which ACT\_n is H, RAS\_n/A16 is H, CAS\_n/A15 is L, and WE\_n/A14 is H, where H and L represent voltage levels representing logic states, as defined in Section 8 of JESD79-4. A Read command presented to a DDR4 SDRAM causes it to convey an addressed memory location to its pins for conveyance to the memory controller, as described in Section 4.24 of JESD79-4.

# JESD79-4D, p. 96.

The DDR4 SDRAMs have a memory core consisting of 16 banks. Read operations are burst

oriented, beginning at a selected location within the memory code:

# 3.2 Basic Functionality

The DDR4 SDRAM is a high-speed dynamic random-access memory internally configured as sixteen-banks, 4 bank group with 4 banks for each bank group for x4/x8 and eight-banks, 2 bank group with 4 banks for each bankgroup for x16 DRAM.

The DDR4 SDRAM uses a 8n prefetch architecture to achieve high-speed operation. The 8n prefetch architecture is combined with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write operation for the DDR4 SDRAM consists of a single 8n-bit wide, four clock data transfer at the internal DRAM core and eight corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.

Read and write operation to the DDR4 SDRAM are burst oriented, start at a selected location, and continue for a burst length of eight or a 'chopped' burst of four in a programmed sequence. Operation begins with the registration of an ACTIVATE Command, which is then followed by a Read or Write command. The address bits registered coincident with the ACTIVATE Command are used to select the bank and row to be activated (BG0-BG1 in x4/8 and BG0 in x16 select the bankgroup; BA0-BA1 select the bank; A0-A17 select the row; refer to "DDR4 SDRAM Addressing" on Section 2.8 for specific requirements). The address bits registered coincident with the Read or Write command are used to select the starting column location for the burst operation, determine if the auto precharge command is to be issued (via A10), and select BC4 or BL8 mode 'on the fly' (via A12) if enabled in the mode register.

# JESD79-4D, p. 11.

30. Additionally, the Accused Products including DDR4 memory controllers, including

the TI AM6442 processor, include a second circuit to receive data sent by the memory component

via an external bus, the data sent by the memory component in response to the read command. A

read command presented to a DDR4 SDRAM causes the DDR4 SDRAM to convey an addressed

memory location to its pins for conveyance to the memory controller, as described in Section 4.24 of JESD79-4.

JESD79-4D, p. 96.

The DQ lines are defined as Data Input/Output lines that bi-directionally carry data into and out of the DRAM. For Read commands, the data is output on the DQ lines and conveyed on an external bus comprised of signal traces to the memory controller. The DQ pins of the DDR4 SDRAMs are connected to DDR0 DQ pins via said external bus.

| Table 3 — Pinout Description (Cont'd) |

|---------------------------------------|

|---------------------------------------|

| Symbol | Туре           | Function                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DQ     | Input / Output | Data Input/ Output: Bi-directional data bus. If CRC is enabled via Mode register then CRC code is added at the end of Data Burst. Any DQ from DQ0-DQ3 may indicate the internal Vref level during test via Mode Register Setting MR4 A4=High. During this mode, RTT value should be set to Hi-Z. Refer to vendor specific datasheets to determine which DQ is used. |  |  |  |  |

JESD79-4D, p. 6.

| SIGNAL NAME | PIN TYPE | DESCRIPTION | ALV |  |

|-------------|----------|-------------|-----|--|

| DDR0_DQ0    | 10       | DDRSS Data  | A3  |  |

| DDR0_DQ1    | 10       | DDRSS Data  | A2  |  |

| DDR0_DQ2    | 10       | DDRSS Data  | B5  |  |

| DDR0_DQ3    | 10       | DDRSS Data  | A4  |  |

| DDR0_DQ4    | 10       | DDRSS Data  | B3  |  |

| DDR0_DQ5    | 10       | DDRSS Data  | C4  |  |

| DDR0_DQ6    | 10       | DDRSS Data  | C2  |  |

| DDR0_DQ7    | 10       | DDRSS Data  | 84  |  |

| DDR0_DQ8    | 10       | DDRSS Data  | N5  |  |

| DDR0_DQ9    | 10       | DDRSS Data  | L4  |  |

| DDR0_DQ10   | 10       | DDRSS Data  | L2  |  |

| DDR0_DQ11   | 10       | DDRSS Data  | M3  |  |

| DDR0_DQ12   | 10       | DDRSS Data  | N4  |  |

| DDR0_DQ13   | 10       | DDRSS Data  | N3  |  |

| DDR0_DQ14   | 10       | DDRSS Data  | M4  |  |

| DDR0_DQ15   | 10       | DDRSS Data  | N2  |  |

#### 6.3.2 DDRSS 6.3.2.1 MAIN Domain

AM64x Sitara Processors Datasheet, SPRSP56B, August 2021, pp. 74-75.

These pins located in the DDR4 SDRAM Memory Interface within the Accused Products, including the AM6442 processor, necessarily have a second circuit to receive the data being sent from the memory component as a result of a Read command.

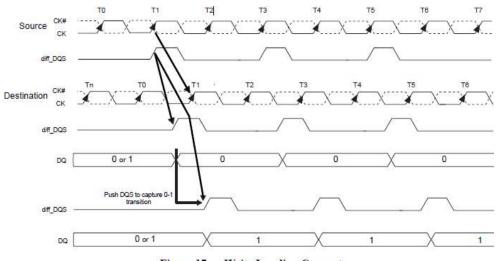

31. Additionally, the Accused Products including DDR4 memory controllers, including the TI AM6442 processor, include calibration circuitry, operable during calibration, to receive at least a first data pattern and a second data pattern from the memory component. DDR4 SDRAMs include a calibration mode called DQ Read Training. Read Training is performed as part of powerup initialization:

#### 3.3.1 Power-up Initialization Sequence

The following sequence is required for POWER UP and Initialization and is shown in Figure 7.

JESD79-4D, pp. 11-12.

<sup>1.</sup> Apply power (RESET\_n and TEN are recommended to be maintained below 0.2 x VDD; all other inputs may be undefined). RESET\_n needs to be maintained below 0.2 x VDD for minimum 200us with stable power and TEN needs to be maintained below 0.2 x VDD for minimum 700us with stable power. CKE is pulled "Low" anytime before RESET\_n being de-asserted (min. time 10ns). The power voltage ramp time between 300mV to V<sub>DD</sub> min must be no greater than 200ms; and during the ramp, V<sub>DD</sub>  $\geq$ V<sub>DDQ</sub> and (V<sub>DD</sub>-V<sub>DDQ</sub>) < 0.3volts. VPP must ramp at the same time or earlier than VDD and VPP must be equal to or higher than VDD at all times.

<sup>15.</sup> The DDR4 SDRAM is now ready for read/Write training (include Vref training and Write leveling).

32. Read DQ Training is the mechanism by which the DDR4 memory controllers,

including the TI AM6442, adjust their receive timing to reliably capture read data from the memory components. The circuitry in the DDR4 memory controller coupled to the DQ receivers that calibrates the DQ receivers is the claimed calibration circuitry.

33. Additionally, the Accused Products including DDR4 memory controllers include

pattern register circuitry. In DDR4 SDRAMs the Multi-Purpose Register (MPR) is a collection of

4-four 8-bit registers that provide the data source for DQ Training data patterns.

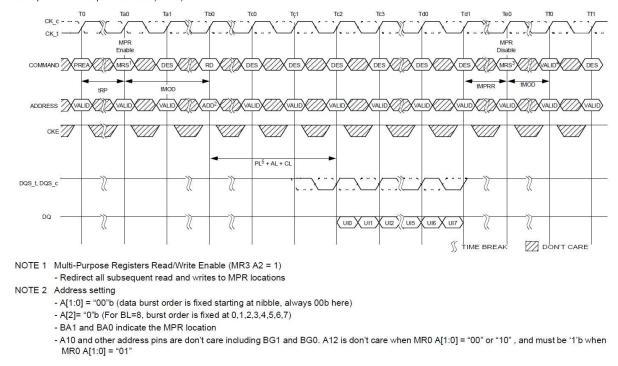

# 4.10 Multi Purpose Register

# 4.10.1 DQ Training with MPR

The DDR4 DRAM contains four 8bit programmable MPR registers used for DQ bit pattern storage. These registers once programmed are activated with MRS read commands to drive the MPR bits on to the DQ bus during link training.

And DDR4 SDRAM only supports following command, MRS, RD, RDA WR, WRA, DES, REF and Reset during MPR enable Mode: MR3 [A2 = 1].

Note that in MPR mode RDA/WRA has the same functionality as a READ/WRITE command which means the auto precharge part of RDA/WRA is ignored. Power-Down mode and Self-Refresh command also is not allowed during MPR enable Mode. No other command can be issued within tRFC after REF command and 1x Refresh is only allowed when MPR mode is Enable. During MPR operations, MPR read or write sequence must be complete prior to a refresh command.

JESD79-4D, p. 43.

The contents of at least two of the MPRs are the first data pattern and the second data pattern in

the memory component. The MPR functional unit, including the two MPRs, is thus the pattern

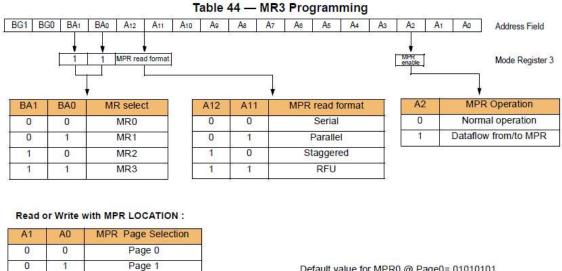

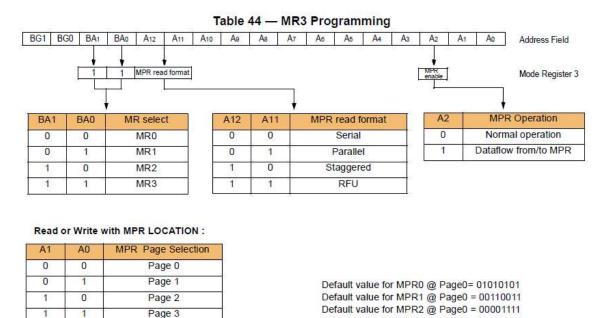

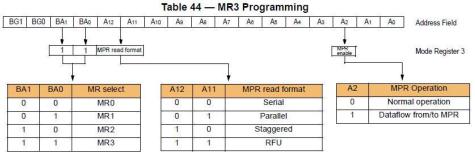

register circuitry. Mode register 3 (MR3) in the DDR4 SDRAMs is used to control the

programming of the MPR registers:

# 4.10.2 MR3 definition

Mode register MR3 controls the Multi-Purpose Registers (MPR) used for training. MR3 is written by asserting CS\_n, RAS\_n/A16, CAS\_n/A15 and WE\_n/A14 low, ACT\_n, BA0 and BA1 high and BG1<sup>1</sup> and BG0 low while controlling the states of the address pins according to Table 44.

| Default value for MPR0 @ Page0= 01010101  |

|-------------------------------------------|

| Default value for MPR1 @ Page0 = 00110011 |

| Default value for MPR2 @ Page0 = 00001111 |

| Default value for MPR3 @ Page0 = 00000000 |

## JESD79-4D, p. 43.

1

1

0

1

Page 2

Page 3

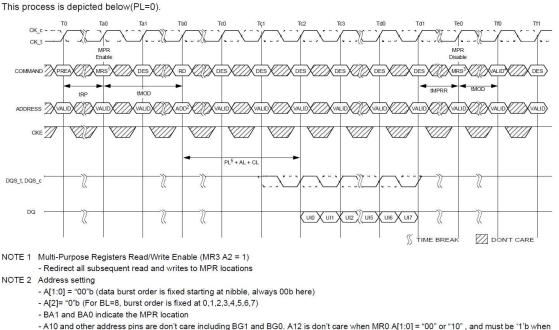

The command that sets the MR3 mode register A2 bit to 1 to direct dataflow to be to and from the MPR from and onto the DQ pins is a precursor to the read command that causes the contents of the MPR to flow onto DQ pins of the DDR4 SDRAM. In DQ Training, the memory controller can use the default values of the different MPR registers, or program them to other values. These values are communicated from the DDR4 SDRAM memory components to the memory controller on the DQ external bus as a result of MPR Read operations:

# 4.10.3 MPR Reads

MPR reads are supported using BL8 and BC4(Fixed) modes. BC4 on the fly is not supported for MPR reads.

In MPR Mode:

Reads (back-to-back) from Page 0 may use tCCD\_S or tCCD\_L timing between read commands; Reads (back-to-back) from Pages 1, 2, or 3 may not use tCCD\_S timing between read commands; tCCD\_L must be used for timing between read commands MPR reads using BC4;

BA1 and BA0 indicate the MPR location within the selected page in MPR Mode.

A10 and other address pins are don't care including BG1 and BG0.

Read commands for BC4 are supported with starting column address of A2:A0 of '000' and '100'.

Data Bus Inversion (DBI) is not allowed during MPR Read operation. During MPR Read, DRAM ignores Read DBI Enable setting in MR5 bit A12 in MPR mode.

DDR4 MPR mode is enabled by programming bit A2=1 and then reads are done from a specific MPR location. MPR location is specified with the Read command using Bank address bits BA1 and BA0.

Each MPR location is 8 bit wide.

# JESD79-4D, p. 44.

Read command

- A[1:0] = '00'b (data burst order is fixed starting at nibble, always 00b here)

- A[2]= '0'b (For BL=8, burst order is fixed at 0,1,2,3,4,5,6,7)

- (For BC=4, burst order is fixed at 0,1,2,3,T,T,T,T)

or

- A[2]= 1 (For BL=8 : Not Support)

- (For BC=4, burst order is fixed at 4,5,6,7,T,T,T,T)

- A12/BC= 0 or 1 : Burst length supports only BL8 and BC4(Fixed), not supports BC4(OTF).

When MR0 A[1:0] is set "01", A12/BC must be always '1'b in MPR read commands (BL8 only).

- BA1 and BA0 indicate the MPR location

- A10 and other address pins are don't care including BG1and BG0

# JESD79-4D, p. 44.

Memory controller repeats these calibration reads until read data capture at memory controller is optimized. Read MPR location can be a different location as specified by the Read command

JESD79-4D, p. 44.

### 4.10.3 MPR Reads (cont'd)

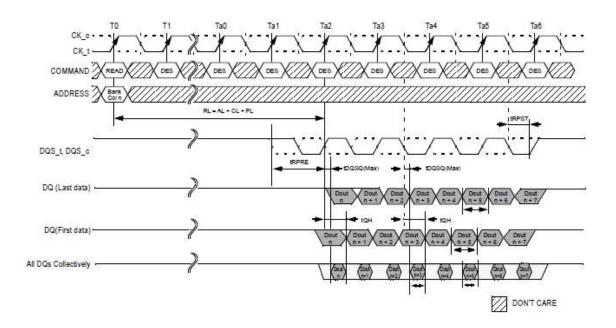

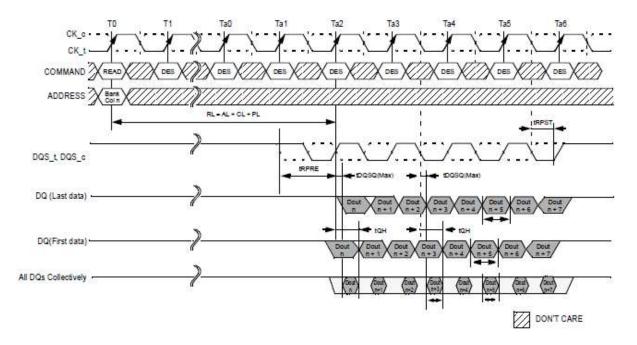

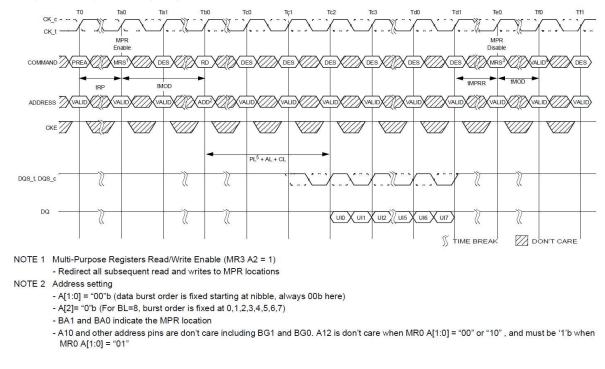

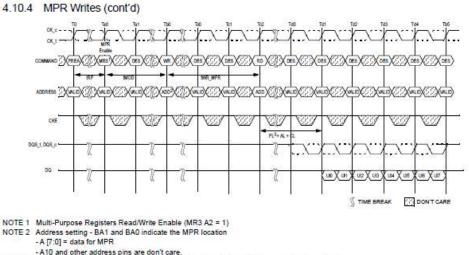

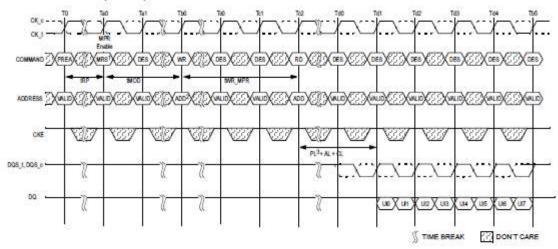

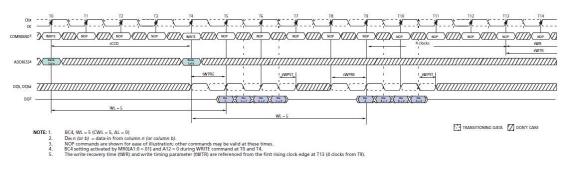

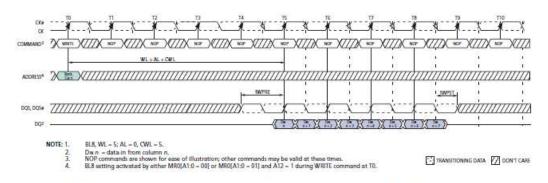

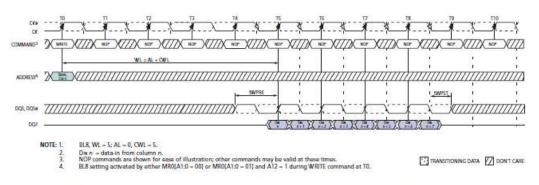

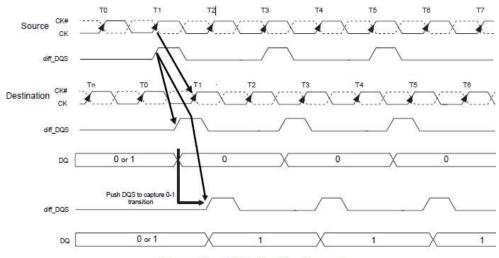

This process is depicted below(PL=0).

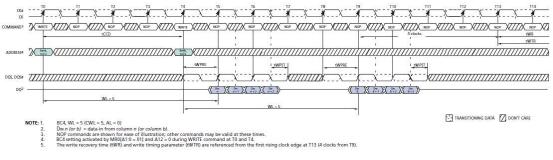

JESD79-4D, p. 45.

Once the MR3 A2 bit is set to 0, a selected one of the first data pattern and the second data pattern is transmitted by the memory component from an MPR register onto the external bus in response to a RD (Read) command. Once such command is, illustrated above, being provided to the memory component at time Tb0.

34. Defendant has and continues to indirectly infringe one or more claims of the '248 Patent by knowingly and intentionally inducing others, including TI customers and end-users, to directly infringe, either literally or under the doctrine of equivalents, by making, using, offering to sell, selling, and/or importing into the United States the Accused Products.

35. Defendant, with knowledge that these products, or the use thereof, infringe the '248 Patent at least as of the date of this Complaint, knowingly and intentionally induced, and continues to knowingly and intentionally induce, direct infringement of the '248 Patent by providing these products to end-users for use in an infringing manner.

36. Rampart has suffered damages as a result of Defendant's direct and indirect infringement of the '248 Patent in an amount to be proved at trial.

37. Rampart has suffered, and will continue to suffer, irreparable harm as a result of Defendant's infringement of the '248 Patent for which there is no adequate remedy at law, unless Defendant's infringement is enjoined by this Court.

# <u>COUNT II</u> (Infringement of the '642 Patent)

38. Paragraphs 1 through 23 are incorporated by reference as if fully set forth herein.

39. Rampart has not licensed or otherwise authorized Defendant to make, use, offer for sale, sell, or import any products that embody the inventions of the '642 Patent.

40. Defendant has and continues to directly infringe the '642 Patent, either literally or under the doctrine of equivalents, without authority and in violation of 35 U.S.C. § 271, by making, using, offering to sell, selling, and/or importing into the United States the Accused Products including, but not limited to, products supporting DDR4 external memories, such as the TI AM6442, AM6441, AM6421, AM6412, and AM6411 Sitara Processors.

41. For example, Defendant has and continues to directly infringe at least Claim 1 of the '642 Patent by making, using, offering to sell, selling, and/or importing into the United States products that include a memory controller that complies with the DDR4 standard. For example, the TI AM6442 includes DDR4 external memory controllers capable of controlling a memory system consisting of DDR4 SDRAMs, each of which is compliant with the JEDEC standard JESD79-4, as shown by the AM64x Sitara Processors Datasheet, SPRSP56B (dated August, 2021) p.5:

|                                                                                        |                                              | AM64x                                                |                                                                                  |                                                                   |

|----------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Application cores                                                                      |                                              | Isolated core <sup>(A)</sup>                         |                                                                                  |                                                                   |

| Arm <sup>e</sup> Arm <sup>e</sup><br>Cortex <sup>e</sup> -A53 Cortex <sup>e</sup> -A53 | Arm <sup>e</sup><br>Cortex <sup>e</sup> -R5F | Arm <sup>e</sup> A<br>cortex <sup>e</sup> -R5F Corte | urm <sup>e</sup> Arm <sup>e</sup><br>ex <sup>e</sup> -R5F Cortex <sup>e</sup> -R | Arm <sup>e</sup><br>Cortex <sup>e</sup> -M4F                      |

| 256KB L2 with ECC                                                                      | 128KB T                                      | см                                                   | 128KB TCM                                                                        | 256KB SRAM                                                        |

|                                                                                        | S                                            | stem Memory                                          |                                                                                  |                                                                   |

| 2 MB SRAM with ECC                                                                     | DDR4/LPD                                     | DR4 with inline ECC                                  | 2                                                                                | X MMCSD                                                           |

| Securit                                                                                | У                                            |                                                      | System Service                                                                   | es                                                                |

| Secure<br>Boot MD5                                                                     | PKA DRB<br>3DES AES                          | 12x GP Tim                                           | ers 4x WWDT                                                                      | Sync<br>Manager                                                   |

| Industrial Conne                                                                       | ctivity                                      | General C                                            | Connectivity                                                                     | Isolated Connectivity <sup>(A)</sup><br>(for use with Contex-M4F) |

| PRU-ICSS(Gb)                                                                           | GPMC / ELM                                   | GPIO                                                 | PCle <sup>rci</sup>                                                              | (                                                                 |

| 2x GMAC Encoder<br>with 9x ∑∆                                                          | 8x FSI                                       | 5x MCSPI                                             | 1x Single lane<br>Gen 2                                                          | GPIO                                                              |

|                                                                                        | 9x EPWM                                      | 4x 12C                                               | 3-port Gb                                                                        | 2x MCSPI                                                          |

| PRU-ICSS(Gb)                                                                           | 3x ECAP                                      | 7x UART                                              | Ethernet"                                                                        | 2x 12C                                                            |

| 2x GMAC Encoder                                                                        | 3x EQEP                                      | OSPI or QSPI                                         | 1x USB 3.1 DRD <sup>ro</sup>                                                     | 2x UART                                                           |

| with 9x 2                                                                              | 2x CAN-FD                                    | 1x ADC                                               |                                                                                  |                                                                   |

# Memory subsystem:

- Up to 2MB of On-chip RAM (OCSRAM) with SECDED ECC:

- Can be divided into smaller banks in increments of 256KB for as many as 8 separate memory banks

- Each memory bank can be allocated to a single core to facilitate software task partitioning

- DDR Subsystem (DDRSS)

- Supports LPDDR4, DDR4 memory types

- 16-Bit data bus with inline ECC

- Supports speeds up to 1600 MT/s

# AM64x Sitara Processors Datasheet, SPRSP56B, August 2021, page 1.

|                                                                         | Table 5           | -1. Device                              | Comparis                               | on               |                                        |             |             |

|-------------------------------------------------------------------------|-------------------|-----------------------------------------|----------------------------------------|------------------|----------------------------------------|-------------|-------------|

| FEATURES                                                                | REFERENCE<br>NAME | AM6442                                  | AM6441                                 | AM6422           | AM6421                                 | AM6412      | AM6411      |

| CTRLMMR_WKUP_JTAG_DEVICE_ID[31:13] DE<br>bit field value <sup>(1)</sup> | VICE_ID register  | D: 0x19464<br>E: 0x19465<br>F: 0x19466  | D: 0x19264<br>E: 0x19265<br>F: 0x19266 | C: 0x19423       | D: 0x19224<br>E: 0x19225<br>F: 0x19226 | C: 0x19403  | C: 0x19203  |

| PROCESSORS AND ACCELERATORS                                             |                   | 0-<br>10                                | tar et                                 |                  |                                        | đ.          |             |

| Speed Grades                                                            | -                 |                                         | <i>m</i> – 21                          | See Ta           | able 7-1                               |             |             |

| Arm Cortex-A53 Microprocessor Subsystem                                 | Arm A53           | Dual Core                               | Single Core                            | Dual Core        | Single Core                            | Dual Core   | Single Core |

| Arm Cortex-R5F                                                          | Arm R5F           | 2 x<br>Dual Core                        | 2 x<br>Dual Core                       | 1 x<br>Dual Core | 1 x<br>Dual Core                       | Single Core | Single Core |

| Arm Cortex-M4F                                                          | Arm M4F           | Single Core                             |                                        |                  |                                        | 3           |             |

| Device Management Security Controller                                   | DMSC-L            | Yes                                     |                                        |                  |                                        |             |             |

| Cryto Accelerators                                                      | Security          | Yes                                     |                                        |                  |                                        |             |             |

| MCU domain with Arm Cortex-M4F                                          | Safety            | Yes                                     |                                        |                  |                                        |             |             |

| PROGRAM AND DATA STORAGE                                                | tel file d        | 12                                      |                                        |                  |                                        |             |             |

| On-Chip Shared Memory (RAM) in MAIN Domain                              | OCSRAM            | 2MB                                     |                                        |                  |                                        |             | 74          |

| R5F Tightly Coupled Memory (TCM)                                        | TCM               | 256KB                                   | 256KB                                  | 256KB            | 256KB                                  | 128KB       | 128KB       |

| On-Chip Shared Memory (RAM) in M4F Domain                               | MCU_MSRAM         | 256KB                                   |                                        |                  |                                        |             |             |

| DDR4/LPDDR4 DDR Subsystem                                               | DDRSS             | Up to 2GB (16-bit data) with inline ECC |                                        |                  |                                        |             |             |

AM64x Sitara Processors Datasheet, SPRSP56B, August 2021, page 7.

42. The required characteristics of DDR4 memories and memory systems and, therefore, of DDR4 memory controllers and their encompassing integrated circuits are defined by JEDEC in a collection of publicly available standards. In particular, standard JESD79-4 is the standard defining DDR4 SDRAMs, and JESD79-4D is the latest version of that standard, dated July 2021.

This document defines the DDR4 SDRAM specification, including features, functionalities, AC and DC characteristics, packages, and ball/signal assignments. The purpose of this Standard is to define the minimum set of requirements for JEDEC compliant 2 Gb through 16 Gb for x4, x8, and x16 DDR4 SDRAM devices. This standard was created based on the DDR3 standards (JESD79-3) and some aspects of the DDR and DDR2 standards (JESD79, JESD79-2).

JESD79-4D page 1.

43. The Accused Products including DDR4 memory controllers, including the TI AM6442, include a first circuit to transmit commands to the memory component, the commands including a Read command that specifies data to be accessed from a memory core of the memory component. DDR4 SDRAM memory controllers, including the TI AM6442 processor, include a first circuit, which is a driver circuit that sends commands to the DDR4 SDRAMs by outputting signals onto command pins DDR0\_RAS\_n, DDR0\_CAS\_n, and DDR0\_WE\_n:

| 6.3.2 DDRSS         |

|---------------------|

| 6.3.2.1 MAIN Domain |

| Table 6-3. DDRSS0 Signal Descriptions |          |                                  |     |  |  |  |

|---------------------------------------|----------|----------------------------------|-----|--|--|--|

| SIGNAL NAME                           | PIN TYPE | DESCRIPTION                      | ALV |  |  |  |

| DDR0_ACT_n                            | 0        | DDRSS Activation Command         | H2  |  |  |  |

| DDR0_ALERT_n                          | 10       | DDRSS Alert                      | H1  |  |  |  |

| DDR0_CAS_n                            | 0        | DDRSS Column Address Strobe      | J5  |  |  |  |

| DDR0_PAR                              | 0        | DDRSS Command and Address Parity | K5  |  |  |  |

| DDR0_RAS_n                            | 0        | DDRSS Row Address Strobe         | F6  |  |  |  |

| DDR0_WE_n                             | 0        | DDRSS Write Enable               | H4  |  |  |  |

|                                       | 2 2      |                                  |     |  |  |  |

AM64x Sitara Processors Datasheet, SPRSP56B, August 2021, p. 74.

JESD79-4 refers to these signals at the DDR4 SDRAMs, as RAS\_n/A16, CAS\_n/A15, and WE\_n/A14.

#### 2.7 **Pinout Description**

### Table 3 — Pinout Description

| Туре  | Function                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | the east but not as Braces a next is bradianated to assess that Theorem                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Input | Activation Command Input : ACT_n defines the Activation command being entered along<br>with CS_n. The input into RAS_n/A16, CAS_n/A15 and WE_n/A14 will be considered as<br>Row Address A16, A15 and A14                                                                                                                                                                        |  |  |  |  |  |

| Input | Command Inputs: RAS_n/A16, CAS_n/A15 and WE_n/A14 (along with CS_n) define the<br>command being entered. Those pins have multi function. For example, for activation<br>with ACT_n Low, those are Addressing like A16,A15 and A14 but for non-activation<br>command with ACT_n High, those are Command pins for Read, Write and other<br>command defined in command truth table |  |  |  |  |  |

|       | Input                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

# JESD79-4D p. 5.

#### Command Truth Table 4.1

(a) Note 1.2.3 and 4 apply to the entire Command truth table (b) Note 5 applies to all Read/Write commands.

[BG=Bank Group Address, BA=Bank Address, RA=Row Address, CA=Column Address, BC\_n=Burst Chop, X=Don't Care, V=Valid].

|                                                 | 10                | 0                      | KE               |      | -     |               |               |              |             | -           |       |              | 1                   |            |       | -      |

|-------------------------------------------------|-------------------|------------------------|------------------|------|-------|---------------|---------------|--------------|-------------|-------------|-------|--------------|---------------------|------------|-------|--------|

| Function                                        | Abbrevia-<br>tion | Previ-<br>cus<br>Cycle | Current<br>Cycle | C8_n | ACT_n | RA8_n<br>/A18 | CA8_n<br>JA15 | WE_N'<br>A14 | 800-<br>801 | BA0-<br>BA1 | C2-C0 | A12/<br>BC_n | A17,<br>A13,<br>A11 | A10/<br>AP | A0-A8 | NOT    |

| Mode Register Set                               | MRS               | н                      | н                | L    | н     | L             | L             | L            | BG          | BA          | ٧     |              | OP C                | ode        |       | 12     |

| Refresh                                         | REF               | н                      | н                | L    | н     | L             | L             | н            | ٧           | V           | ٧     | V            | ٧                   | V          | V     | 2      |

| Self Refresh Entry                              | SRE               | н                      | L                | L    | н     | L             | L             | н            | ٧           | ٧           | ٧     | V            | V                   | ٧          | ٧     | 7,9    |

| Self Refresh Exit                               | SRX               | L                      | н                | н    | Х     | X             | Х             | Х            | х           | Х           | Х     | Х            | Х                   | X          | X     | 7.8.9  |

| Seit Retresh Exit                               | SKA               |                        |                  | L    | н     | н             | н             | н            | ٧           | ٧           | ٧     | V            | ٧                   | ۷          | ٧     | 10     |

| Single Bank Precharge                           | PRE               | H                      | н                | L    | н     | L             | н             | L.           | BG          | BA          | ٧     | V            | ٧                   | L          | V     | S.     |

| Precharge all Banks                             | PREA              | н                      | н                | L    | н     | L             | н             | L            | V           | ٧           | ٧     | ٧            | ٧                   | н          | ٧     |        |

| RFU                                             | RFU               | н                      | н                | L    | н     | L             | н             | н            |             |             |       | RFU          |                     |            |       |        |

| Bank Activate                                   | ACT               | н                      | Н                | L    | L     | Row A         | ddres         | s (RA)       | BG          | BA          | ٧     | Roy          | w Addr              | ess (F     | RA)   | 8      |

| Write (Fixed BL8 or BC4)                        | WR                | н                      | н                | L    | н     | н             | L             | L            | BG          | BA          | ٧     | V            | ٧                   | L          | CA    | 8      |

| Write (BC4, on the Fly)                         | WRS4              | н                      | н                | L    | н     | н             | L             | L            | BG          | BA          | ٧     | L            | V                   | L          | CA    | j.     |

| Write (BL8, on the Fly)                         | WRS8              | H                      | н                | L    | н     | н             | L             | L            | BG          | BA          | ٧     | н            | ٧                   | L          | CA    | š –    |

| Write with Auto Precharge<br>(Fixed BL8 or BC4) | WRA               | н                      | н                | ε.   | н     | н             | £.            | L            | BG          | BA          | v     | v            | v                   | н          | CA    | 2      |

| Write with Auto Precharge<br>(BC4, on the Fly)  | WRAS4             | н                      | н                | L    | н     | H             | L:            | L            | BG          | BA          | ٧     | Ŀ            | ٧                   | н          | CA    | 8<br>9 |

| Write with Auto Precharge<br>(BL8, on the Fly)  | WRAS8             | н                      | н                | L    | н     | н             | L             | L            | BG          | BA          | ٧     | н            | ٧                   | н          | CA    | ,      |

| Read (Fixed BL8 or BC4)                         | RD                | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | V     | V            | V                   | L          | CA    |        |

| Read (BC4, on the Fly)                          | RDS4              | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | ٧     | L            | ٧                   | L          | CA    | ×      |

| Read (BL8, on the Fly)                          | RDS8              | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | ٧     | н            | ٧                   | L          | CA    | ŝ.     |

| Read with Auto Precharge<br>(Fixed BL8 or BC4)  | RDA               | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | ٧     | ٧            | ٧                   | н          | CA    |        |

| Read with Auto Precharge<br>(BC4, on the Fly)   | RDAS4             | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | ٧     | L            | ٧                   | н          | CA    |        |

| Read with Auto Precharge<br>(BL8, on the Fly)   | RDAS8             | н                      | н                | L    | н     | н             | L             | н            | BG          | BA          | ٧     | н            | ٧                   | н          | CA    |        |

| No Operation                                    | NUP               | н                      | н                | L    | н     | н             | н             | н            | v           | V           | v     | v            | v                   | v          | v     | 10     |

| Device Deselected                               | DES               | н                      | н                | н    | Х     | х             | Х             | Х            | Х           | Х           | х     | Х            | Х                   | Х          | Х     | 2      |

| Power Down Entry                                | PDE               | н                      | L                | н    | X     | х             | х             | Х            | Х           | Х           | Х     | Х            | Х                   | х          | Х     | 6      |

| Power Down Exit                                 | PDX               | L                      | н                | н    | X     | X             | Х             | х            | X           | Х           | X     | X            | X                   | X          | X     | 6      |

| ZQ calibration Long                             | ZQCL              | н                      | н                | L    | н     | н             | н             | L            | V           | V           | V     | V            | ٧                   | н          | V     |        |

| ZQ calibration Short                            | ZQCS              | н                      | н                | 1    | н     | н             | н             | 1            | v           | V           | V     | V            | V                   | L          | V     | č      |

#### Table 35 — Command Truth Table

JESD79-4D, p. 29.

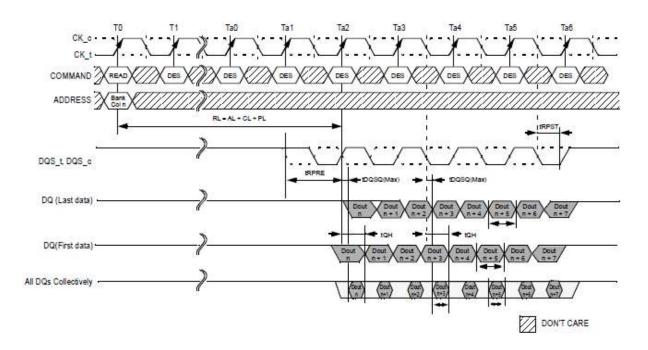

44. The Accused Products including DDR4 memory controllers include circuits that drive these command signals toward the DDR4 SDRAMs. Among the commands that DDR4 SDRAMs can respond to are Read commands. A Read command is provided to a DDR4 SDRAM by sending a command in which ACT\_n is H, RAS\_n/A16 is H, CAS\_n/A15 is L, and WE\_n/A14 is H, where H and L represent voltage levels representing logic states, as defined in section 8 of JESD79-4. A Read command presented to a DDR4 SDRAM causes it to convey an addressed memory location to its pins for conveyance to the memory controller, as described in Section 4.24 of JESD79-4:

# JESD79-4D, p. 96.

The DDR4 SDRAMs have a memory core consisting of 16 banks. Read operations are burst oriented, beginning at a selected location within the memory code:

# 3.2 Basic Functionality

The DDR4 SDRAM is a high-speed dynamic random-access memory internally configured as sixteen-banks, 4 bank group with 4 banks for each bank group for x4/x8 and eight-banks, 2 bank group with 4 banks for each bankgroup for x16 DRAM.

The DDR4 SDRAM uses a 8n prefetch architecture to achieve high-speed operation. The 8n prefetch architecture is combined with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write operation for the DDR4 SDRAM consists of a single 8n-bit wide, four clock data transfer at the internal DRAM core and eight corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.

Read and write operation to the DDR4 SDRAM are burst oriented, start at a selected location, and continue for a burst length of eight or a 'chopped' burst of four in a programmed sequence. Operation begins with the registration of an ACTIVATE Command, which is then followed by a Read or Write command. The address bits registered coincident with the ACTIVATE Command are used to select the bank and row to be activated (BG0-BG1 in x4/8 and BG0 in x16 select the bankgroup; BA0-BA1 select the bank; A0-A17 select the row; refer to "DDR4 SDRAM Addressing" on Section 2.8 for specific requirements). The address bits registered coincident with the Read or Write command are used to select the starting column location for the burst operation, determine if the auto precharge command is to be issued (via A10), and select BC4 or BL8 mode 'on the fly' (via A12) if enabled in the mode register.

# JESD79-4D, pg. 11.

45. Additionally, the Accused Products including DDR4 memory controllers, including the TI AM6442, include a second circuit to receive data sent by the memory component via an external bus, the data sent by the memory component in response to the Read command. A Read command presented to a DDR4 SDRAM by DDR4 SDRAM memory controllers, causes the DDR4 SDRAM to convey an addressed memory location to its pins for conveyance to the memory controller, as described in Section 4.24 of JESD79-4. The Accused Products, including the TI AM6442, necessarily have a second circuit to receive the data being sent from the memory component as a result of a Read command.

# JESD79-4D, p. 96.

The DQ lines are defined as Data Input/Output lines that bi-directionally carry data into and out of the DRAM. For Read commands, the data is output on the DQ lines and conveyed on an external bus comprised of signal traces to the memory controller. The DQ pins of the DDR4 SDRAMs are connected to DDR0\_DQ pins via said external bus. These pins in the DDR SDRAM Memory Interface necessarily have circuitry within the AM6442 processor to receive the data being sent from the memory component as a result of a read command. This circuitry is the second circuit.

#### Table 3 — Pinout Description (Cont'd)

| Symbol | Туре           | Function                                                                                                                                                                                                                                                                                                                                                           |

|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ     | Input / Output | Data Input/ Output: Bi-directional data bus. If CRC is enabled via Mode register then CRC code is added at the end of Data Burst. Any DQ from DQ0~DQ3 may indicate the internal Vref level during test via Mode Register Setting MR4 A4=High. During this mode RTT value should be set to Hi-Z. Refer to vendor specific datasheets to determine which DQ is used. |

JESD79-4D, p. 6.

| SIGNAL NAME | PIN TYPE | DESCRIPTION | ALV |  |

|-------------|----------|-------------|-----|--|

|             |          | 2200111011  |     |  |

|             | -        |             | -   |  |

| DDR0_DQ0    | 10       | DDRSS Data  | A3  |  |

| DDR0_DQ1    | 10       | DDRSS Data  | A2  |  |

| DDR0_DQ2    | IO       | DDRSS Data  | B5  |  |

|             |          |             | ÷.  |  |

| DDR0_DQ3    | 10       | DDRSS Data  | A4  |  |

| DDR0_DQ4    | 10       | DDRSS Data  | B3  |  |

| DDR0_DQ5    | 10       | DDRSS Data  | C4  |  |

| DDR0_DQ8    | 10       | DDRSS Data  | C2  |  |

| DDR0_DQ7    | 10       | DDRSS Data  | B4  |  |

| DDR0_DQ8    | 10       | DDRSS Data  | N5  |  |

| DDR0_DQ9    | 10       | DDRSS Data  | L4  |  |

| DDR0_DQ10   | 10       | DDRSS Data  | L2  |  |

| DDR0_DQ11   | 10       | DDRSS Data  | M3  |  |

| DDR0_DQ12   | 10       | DDRSS Data  | N4  |  |

| DDR0_DQ13   | 10       | DDRSS Data  | N3  |  |

| DDR0_DQ14   | 10       | DDRSS Data  | M4  |  |

| DDR0 DQ15   | 10       | DDRSS Data  | N2  |  |

#### 6.3.2 DDRSS 6.3.2.1 MAIN Domain

AM64x Sitara Processors Datasheet, SPRSP56B, August 2021, pp. 74-75.

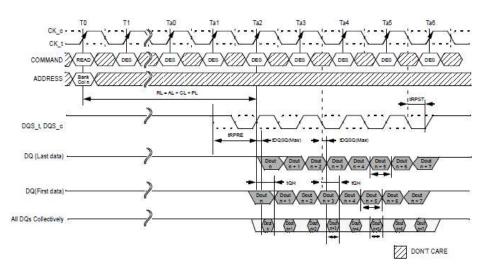

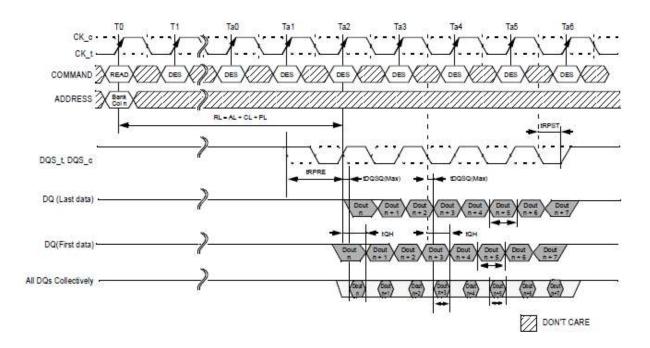

46. Additionally, the Accused Products including DDR4 memory controllers, including the TI AM6442, include calibration circuitry, operable during calibration, to receive from the memory component, in response to one of the commands, a pattern selected from at least one of a first data pattern and a second data pattern and to, based on the selected pattern, adjust a timing of a timing reference signal for sampling the data at the second receive circuit, wherein the timing of the timing reference signal is initially set using an initial calibration sequence and then updated during one or more subsequent calibration sequences. DDR4 SDRAMs include a calibration mode called DQ Read Training (also known as Read Leveling). Read Training is performed as part of power-up initialization:

# 3.3.1 Power-up Initialization Sequence

The following sequence is required for POWER UP and Initialization and is shown in Figure 7.

15. The DDR4 SDRAM is now ready for read/Write training (include Vref training and Write leveling).

# JESD79-4D, pp. 11-12.

47. Read DQ Training is the mechanism by which the DDR4 memory controllers,

including the TI AM6442, adjust their receive timing to reliably capture read data from the memory

components. The circuitry in the DDR4 memory controller coupled to the DQ receivers that

calibrates the DQ receivers is the claimed calibration circuitry.

48. Additionally, the Accused Products including DDR4 memory controllers include

pattern register circuitry. The Multi-Purpose Register (MPR) is a collection of 4-four 8-bit

registers that provide the data source for DQ Training data patterns.

# 4.10 Multi Purpose Register

## 4.10.1 DQ Training with MPR

The DDR4 DRAM contains four 8bit programmable MPR registers used for DQ bit pattern storage. These registers once programmed are activated with MRS read commands to drive the MPR bits on to the DQ bus during link training.

And DDR4 SDRAM only supports following command, MRS, RD, RDA WR, WRA, DES, REF and Reset during MPR enable Mode: MR3 [A2 = 1].

Note that in MPR mode RDA/WRA has the same functionality as a READ/WRITE command which means the auto precharge part of RDA/WRA is ignored. Power-Down mode and Self-Refresh command also is not allowed during MPR enable Mode. No other command can be issued within tRFC after REF command and 1x Refresh is only allowed when MPR mode is Enable. During MPR operations, MPR read or write sequence must be complete prior to a refresh command.

JESD79-4D, p. 43.

The contents of at least two of the MPRs are the first data pattern and the second data pattern in

the memory component. Mode register 3 (MR3) in the DDR4 SDRAMs is used to control the

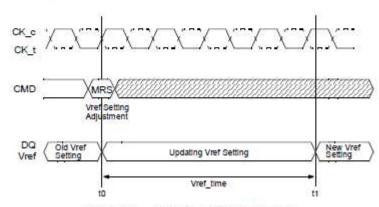

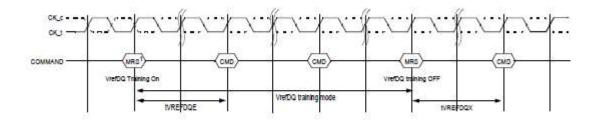

programming of the MPR registers: