# IN THE UNITED STATES DISTRICT COURT FOR THE DISTRICT OF DELAWARE

TEXASLDPC INC.,

Plaintiff,

v.

BROADCOM INC., LSI CORPORATION, AVAGO TECHNOLOGIES U.S. INC.

Defendants.

C.A. No. 18-1966-SB

**JURY TRIAL DEMANDED**

REDACTED

# THIRD AMENDED COMPLAINT FOR PATENT INFRINGEMENT

Plaintiff TexasLDPC Inc. (the "Plaintiff" or "TexasLDPC"), by and through its attorneys, for its Third Amended Complaint for patent and copyright infringement against Broadcom Inc., LSI Corporation, and Avago Technologies U.S. Inc. (collectively, the "Defendants"), hereby alleges as follows:

#### THE PARTIES

- 1. Plaintiff TexasLDPC Inc. is a Texas Corporation with its principal place of business located at 1920 W Villa Maria Rd #301, Bryan, Texas 77807.

- 2. TexasLDPC designs and markets LDPC solutions for use in the Flash, Hard Disk, Wi-Fi, 5G, and NVM technologies under the name Symbyon Systems (www.symbyon.com).

- 3. TexasLDPC has received funding from the National Science Foundation (both SBIR Phase 1 and Phase 2 funding) to apply LDPC technology to Flash Memory storage systems.

- 4. On information and belief, Broadcom Inc. is a Delaware corporation with its principal place of business located at 1320 Ridder Park Drive San Jose, California 95131.

- 5. On information and belief, Broadcom Inc. conducts business operations throughout the United States, including in the State of Delaware.

- 6. On information and belief, LSI Corporation ("LSI") is a Delaware corporation headquartered at 1320 Ridder Park Drive, San Jose, California 95131. LSI designs, develops, and supplies storage and networking integrated circuits.

- 7. On information and belief, LSI conducts business operations throughout the United States, including in the State of Delaware.

- 8. On information and belief Avago Technologies U.S. Inc. ("Avago U.S.") is a Delaware corporation headquartered at 1320 Ridder Park Drive, San Jose, California 95131. Since March 2015, Avago U.S. has handled the U.S. sale and distribution of LSI products.

- 9. On information and belief, Avago U.S. conducts business operations throughout the United States, including in the State of Delaware.

- 10. On information and belief, LSI was formed as a result of the merger of LSI Logic Corporation and Agere Systems Inc. in 2007. Avago Technologies Limited then acquired LSI in 2014.

- 11. On information and belief, LSI and Avago U.S. are both wholly owned indirect subsidiaries of holding company Avago Technologies Limited.

- 12. On information and belief, Avago Technologies Limited is a wholly owned indirect subsidiary of holding company Broadcom Inc. (formerly known as Broadcom Limited).

- 13. On information and belief, LSI was acquired by Avago Technologies Ltd. ("Avago"), a Singapore Corporation, in 2014.

- 14. On information and belief, Avago acquired Broadcom Corporation, a California Corporation, in 2016, and adopted the name Broadcom Limited. On information and belief, Broadcom Limited was redomiciled in the United States as Broadcom Inc. in 2018. Broadcom

Inc. is a designer, developer, and global supplier of products based on analog and digital semiconductor technologies.

- 15. Defendants Broadcom Inc., LSI, and Avago U.S. will be referred to herein as the Defendants, which shall be understood to refer to them collectively or individually as supported by the context of any particular statement or allegation.

- 16. On information and belief, Defendants, alone or through other subsidiaries as agents, collectively operate a worldwide design, manufacturing, and sales operation that operates collectively to design, engineer, market, and sell Accused Products.

- 17. On information and belief, Defendants, alone or through other subsidiaries as agents, market and sell Accused Products to customers both in the United States and elsewhere around the world.

- 18. On information and belief, Defendants, alone or through other subsidiaries as agents, mostly manufacturing the Accused Products in Asia.

- 19. On information and belief, a majority of the Accused Products sold by Defendants, alone or through other subsidiaries as agents, outside of the United States are sold with Defendants' knowledge and intention of those Accused Products being incorporated as components within customers' end-user products.

- 20. On information and belief, a majority of the Accused Products sold by

Defendants, alone or through other subsidiaries as agents, outside of the United States are sold

with Defendants' knowledge that their customers' end-user products containing the Accused

Products will be imported into the United States to be used in an infringing manner in the United

States.

21. LSI Logic Corporation, Agere Systems Inc., Avago Technologies Limited, and Broadcom Limited will be referred to herein as the Broadcom Predecessor Entities, which shall be understood to refer to them collectively or individually, along with the Defendants, as supported by the context of any particular statement or allegation.

# **JURISDICTION AND VENUE**

- 22. Plaintiff's patent infringement claims arise under the Patent Laws of the United States, 35 U.S.C. §§ 100 *et seq*. This Court has jurisdiction over the subject matter of this action under 28 U.S.C. §§ 1331 and 1338(a).

- 23. Plaintiff's copyright infringement claims arise under the Copyright Laws of the United States, 17 U.S.C. §§ 101, *et seq*. This Court has exclusive subject matter jurisdiction over the copyright claims under 28 U.S.C. § 1331 and 1338 and 17 U.S.C. § 501(a).

- 24. This Court has personal jurisdiction over Defendants Avago Technologies U.S. Inc., LSI Corporation, and Broadcom, Inc. ("Defendants") because the Defendants are Delaware corporations.

- 25. Defendants are registered to do business in the State of Delaware.

- 26. Corporation Service Company, 251 Little Falls Drive, Wilmington, DE 19808, serves as Defendants' Registered Agent in the State of Delaware.

- 27. The Court has personal jurisdiction over Defendants because Defendants are incorporated in this judicial district and because, on information and belief, Defendants have regularly and systematically transacted business in this judicial district, directly or through intermediaries, and/or committed acts of infringement in this judicial district. Defendants have also placed infringing products into the stream of commerce by shipping those products into this district or knowing that the products would be shipped into this District.

- 28. Affiliates and subsidiaries of Defendants provide a distribution channel of infringing products within this Judicial District and the U.S. nationally.

- 29. Affiliates and subsidiaries of Defendants place infringing products into the stream of commerce knowing they will be sold and used in the State of Delaware and elsewhere in the United States and economically benefits from the retail sale of infringing products in the State of Delaware.

- 30. Defendants alone or through other subsidiaries as agents, make the Accused Products and supplies and/or make available the Accused Products to companies that further market and sell the Accused Products and products containing the Accused Products.

- 31. The division of labor between making, manufacturing, marketing and sales amongst all of the Defendants and their distributors amounts to an organized association, establishing a distribution channel for the Accused Products in the United States.

- 32. Defendants know or can reasonably foresee that a termination point of the distribution channel targeted to the United States includes this Judicial District (as further described below).

- 33. Venue is proper in this judicial district pursuant to 28 U.S.C. §1400(b) for the Defendants.

- 34. As noted above, Defendants (individually or in concert with one another) have committed and continue to commit acts of infringement under Fed. R. Civ. P. 4(k)(2) and within this Judicial District giving rise to this action.

#### **PATENTS-IN-SUIT**

35. On August 9, 2013, United States Patent No. 8,418,023 ("the '023 Patent"), entitled "Low Density Parity Check Decoder For Irregular LDPC Codes," was duly and legally

issued by the United States Patent and Trademark Office ("PTO"). A true and correct copy of the '023 Patent is attached hereto as **Exhibit A**.

- 36. On October 8, 2013, United States Patent No. 8,555,140 ("the '140 Patent"), entitled "Low Density Parity Check Decoder For Irregular LDPC Codes," was duly and legally issued by the PTO. A true and correct copy of the '140 Patent is attached hereto as **Exhibit B**.

- 37. On August 18, 2015, United States Patent No. 9,112,530 ("the '530 Patent"), entitled "Low Density Parity Check Decoder," was duly and legally issued by the PTO. A true and correct copy of the '530 Patent is attached hereto as **Exhibit C**.

- 38. On January 22, 2013, United States Patent No. 8,359,522 ("the '522 Patent"), entitled "Low Density Parity Check Decoder For Regular LDPC Codes," was duly and legally issued by the PTO. A true and correct copy of the '522 Patent is attached hereto as **Exhibit D**.

- 39. On February 18, 2014, United States Patent No. 8,656,250 ("the '250 Patent"), entitled "Low Density Parity Check Decoder For Irregular LDPC Codes," was duly and legally issued by the PTO. A true and correct copy of the '250 Patent is attached hereto as **Exhibit E**.

- 40. On November 27, 2018, United States Patent No. 10,141,950 ("the '950 Patent"), entitled "Low Density Parity Check Decoder," was duly and legally issued by the PTO. A true and correct copy of the '950 Patent is attached hereto as **Exhibit F**.

- 41. The '023, '140, '530, '522, '250, and '950 Patents are collectively referred to herein as the "Patents-in-Suit."

- 42. The Patents-in-Suit are each assigned by their named inventors, Dr. Kiran Gunnam ("Dr. Gunnam"), and Dr. Gwan S. Choi, to the Texas A&M University System (TAMUS).

43. Plaintiff is the exclusive licensee of each of the Patents-in-Suit pursuant to a license agreement between TAMUS and Plaintiff, executed on June 18, 2015 (the "TAMUS License Agreement"). Pursuant to the TAMUS License Agreement, Plaintiff has the exclusive and sole right (subject a pre-existing license) to practice the Patents-in-Suit, grant sub-licenses thereto, and sue and recover damages for the past, present, and future infringement of the Patents-in-Suit.

# **COPYRIGHTS-IN-SUIT**

44. Dr. Gunnam, while an employee of Texas A&M Engineering Experiment Station ("TEES"), a subdivision of TAMUS, working under the guidance and review from Dr. Choi, an employee of TEES, expended time, intellectual effort, and capital to create a computer program work entitled "Source Code for Certain Low Density Parity Check Algorithms" (the "LDPC Algorithms Source Code Work").

|                           | Title of Work: | Source Code for Certain Low Density Parity Check Algorithms                        |

|---------------------------|----------------|------------------------------------------------------------------------------------|

| Completion/Pub<br>Year of |                | 2007                                                                               |

| Author —                  |                |                                                                                    |

|                           | Author:        | The Texas A&M University System                                                    |

| Aut                       | hor Created:   | computer program                                                                   |

| Work n                    | ade for hire:  | Yes                                                                                |

|                           | Domiciled in:  | United States                                                                      |

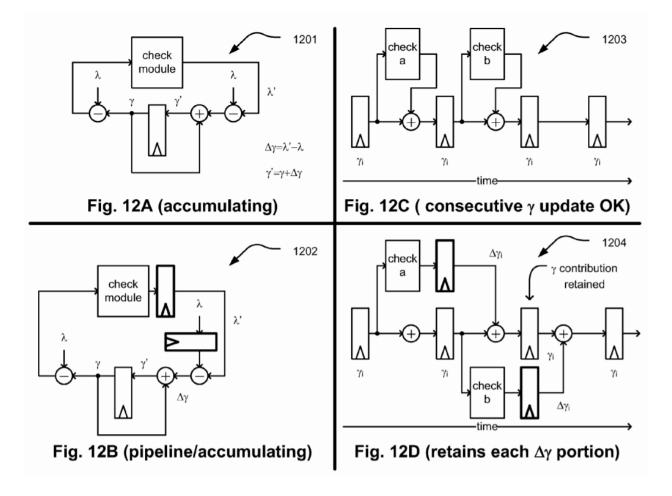

| Copyright claima          | int —          | 598500000000000000000000000000000000000                                            |

| Copyrig                   | ht Claimant:   | The Texas A&M University System                                                    |

|                           |                | 301 Tarrow, John B. Connally Bldg., College Station, TX, 77840-7896, United States |

45. As shown above, TAMUS registered its copyright in and to the LDPC Algorithms

Source Code Work with the United States Copyright Office, and was granted U.S. Copyright

Registration No. TXu 1-842-620, which issued on February 11, 2013. Attached hereto as

Exhibit G is a copy of Registration No. TXu 1-842-620.

# Case 1:18-cv-01966-SB Document 249 Filed 05/04/22 Page 8 of 157 PageID #: 10031 HIGHLY CONFIDENTIAL SUBJECT TO PROTECTIVE ORDER

46. Dr. Gunnam, while an employee of TEES, a subdivision of TAMUS, working under the guidance and review from Dr. Choi, an employee of TEES, expended time, intellectual effort, and capital to create a computer program work entitled "Low Density Parity Check Decoder" (the "LDPC Decoder Program Work").

| Title               |                                                                                                             |

|---------------------|-------------------------------------------------------------------------------------------------------------|

| Title of            | Work: Low Density Parity Check Decoder                                                                      |

| Completion/Publicat | ion                                                                                                         |

| Year of Com         | ppletion: 2008                                                                                              |

| Author              |                                                                                                             |

| • Author (          | Author: Texas A&M Engineering Experiment Station Created: computer program                                  |

| Work made           | 지수 있다면 가는 것이 보면서 하는 경기 때문에 가는 사람들이 가는 것이 되었다.                                                               |

|                     | theu in. Office states                                                                                      |

| Copyright Claimant  |                                                                                                             |

| Copyright Cl        | laimant: Texas A&M Engineering Experiment Station 3470 TAMU, College Station, TX, 77843-3470, United States |

- 47. As shown above, TEES registered its copyright in and to the LDPC Decoder Program Work with the United States Copyright Office, and was granted U.S. Copyright Registration No. TXu 2-001-020, which issued on October 12, 2015. Attached hereto as **Exhibit H** is a copy of Registration No. TXu 2-001-020.

- 48. Dr. Gunnam, while an employee of TEES, a subdivision of TAMUS, working under the guidance and review from Dr. Choi, an employee of TEES, expended time, intellectual effort, and capital to create a computer program work entitled "Source Code for Low Density Parity Check Decoder and Its Modules" (the "LDPC Decoder Source Code Work").

| Title    |                                                                       |                                                                                                       |        |  |

|----------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------|--|

|          | Title of Work:                                                        | Source Code for Low Density Parity Check Decoder and Its Me                                           | odules |  |

| Complet  | tion/Publication                                                      |                                                                                                       | 5 2 12 |  |

|          | Year of Completion:                                                   | 2007                                                                                                  |        |  |

| Author   |                                                                       |                                                                                                       | 2 81 4 |  |

|          | Author:     Author Created:     Work made for hire:     Domiciled in: | Texas A&M Engineering Experiment Station computer program Yes United States                           |        |  |

| Copyrigi | ht Claimant                                                           | <i>y</i>                                                                                              |        |  |

|          | Copyright Claimant:                                                   | Texas A&M Engineering Experiment Station<br>3369 TAMU, College Station, TX, 77843-3369, United States |        |  |

- 49. As shown above, TEES registered its copyright in and to the LDPC Decoder Source Code Work with the United States Copyright Office, and was granted U.S. Copyright Registration No. TXu 2-033-302, which issued on November 29, 2016. Attached hereto as **Exhibit I** is a copy of Registration No. TXu 2-033-302.

- 50. Collectively TAMUS' LDPC Algorithms Source Code Work, LDPC Decoder Program Work, and LDPC Decoder Source Code Work constitute the "TAMUS Copyrighted Works." Pursuant to the TAMUS License Agreement, Plaintiff has been granted by TAMUS an exclusive license and right to reproduce, distribute, publicly display and perform, and make derivative works from the TAMUS Copyrighted Works, grant sublicenses thereto, and to sue for infringement of the copyrights in the TAMUS Copyrighted Works, including the exclusive right to collect damages for past, present, and future infringement of those copyrights.

- 51. The TAMUS Copyrighted Works were marked with copyright notifications informing any reader that the works were copyrighted thus making any copying by Defendants willful.

52. Defendant LSI was also notified by Dr. Gunnam that the TAMUS Copyrighted Works were property of TAMUS and could not be copied or used without a license.

### FACTUAL BACKGROUND

#### **Development of the Patented Technology**

- 53. Each of the Patents-in-Suit is directed to improved designs and methods for using low-density parity check code ("LDPC") decoders.

- 54. LDPC decoders decode data that has been encoded using an LDPC code, a type of error correcting code. By encoding data in this fashion, digital electronic devices can transmit data over a noisy channel, while being able to detect and correct errors. As a result, such devices are able to operate at substantially higher data rates than would otherwise be possible.

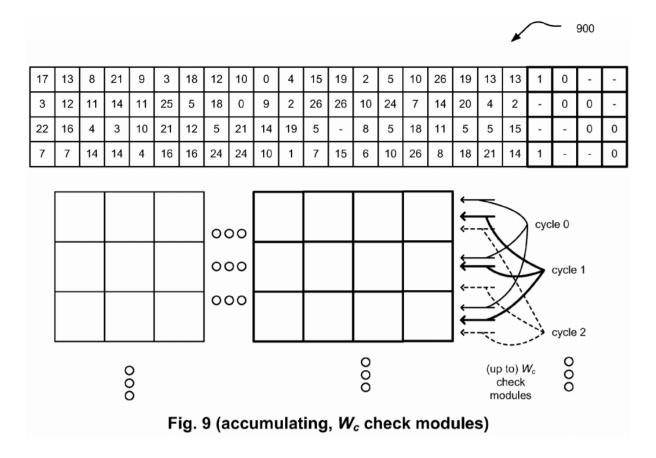

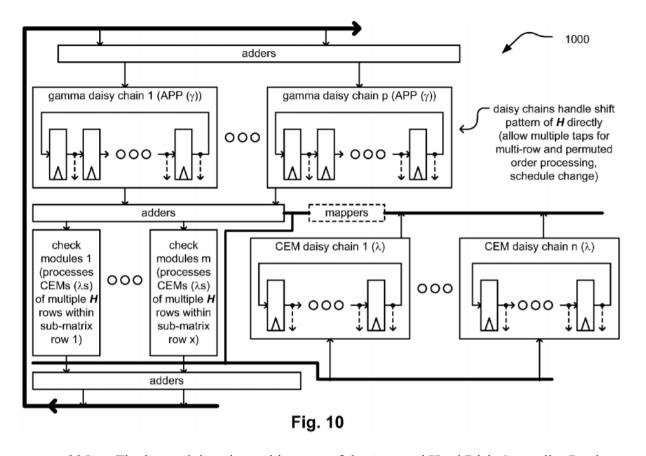

- 55. The Patents-in-Suit improve upon prior LDPC decoder technology by providing decoder designs and techniques that are faster, more compact, and more energy efficient than prior art designs. These designs were developed by Dr. Kiran Gunnam, then a doctoral student at Texas A&M University (TAMU), working under the supervision of his thesis advisor, Prof. Gwan Choi. Dr. Gunnam and Prof. Choi discovered techniques to optimize the then-conventional algorithms and circuit architectures for LDPC decoders so that they used less memory and avoided redundant calculations. Dr. Gunnam and Prof. Choi first described aspects of their new design in a technical report entitled "A Low Power Architecture for Min-Sum Decoding of LDPC Codes," TAMU-ECE-2006-02 (the "Low Power Architecture" report), which is available at <a href="https://cesg.tamu.edu/techreports/">https://cesg.tamu.edu/techreports/</a>, and issued in May, 2006.

- 56. Subsequent to the issuance of the Low Power Architecture report, Dr. Gunnam and Prof. Choi published and presented extensively about aspects and applications of their new LDPC decoder designs, including in the following publications and presentations:

- Gunnam, et al., "VLSI Architectures for Layered Decoding for Irregular LDPC Codes of WiMax," 2007 IEEE International Conference on Communications (Glasgow, UK, June 2007).

- Gunnam, et al., "Decoding of Quasi-cyclic LDPC Codes Using an On-the-Fly Computation," 2006 Asilomar Conference on Signals, Systems and Computers (Pacific Grove, CA, October 2006).

- Gunnam, "Area and Energy Efficient VLSI Architectures for Low-Density Party-Check Decoders Using On-the-Fly Computation, Ph.D Thesis, Texas A&M University, December, 2006.

- Gunnam, et al., "VLSI Architectures for Turbo Decoding Message Passing Using Min-Sum for Rate-Compatible Array LDPC Codes," 2007 2<sup>nd</sup> Int'l Symposium on Wireless Pervasive Computing, (San Juan, PR, Feb. 2007).

- Gunnam, et al., "Multi-Rate Layered Decoder Architecture for Block LDPC Codes of the IEEE 802.11n Wireless Standard." 2007 IEEE International Symposium on Circuits and Systems, (New Orleans, LA, May 2007).

- 57. On May 1, 2007, less than one year after the issuance of the Low Power Architecture report, Dr. Gunnam and Prof. Choi filed a provisional patent application with the United States Patent and Trademark Office ("USPTO"), bearing application number 60/915,320 (the "320 provisional application"). Each of the Patents-in-Suit claims priority to the '320 provisional application, and at least some of the claims therein therefore entitled to a priority date of at least as early as May 1, 2007.

#### **Development of the Copyrighted Works**

58. During the course of his doctoral research, Dr. Gunnam built and tested specific decoding algorithms, decoder scheduling algorithms, decoder hardware architecture, microarchitecture, and circuit designs that implement the teachings of the Patents-in-Suit. Dr. Gunnam created simulation models for these designs in MATLAB code, and design descriptions in RTL code, a hardware description language. Each of the TAMUS Copyrighted Works comprise and share much of the same or substantially the same core Register Transfer Level (RTL) and MATLAB code reflecting Dr. Gunnam's circuit designs decoding algorithms, decoder scheduling algorithms, decoder hardware architecture, micro-architecture, and circuit designs. RTL and MATLAB code provides chip designers with tool for modelling LDPC decoder designs and for describing the physical implementation of LDPC decoders in integrated circuit chips. The TAMUS RTL code – written in Verilog Hardware Description Language (HDL) language – can be input into a logic synthesis tool which in turn creates the gate-level abstraction of the design that is used for all downstream physical chip implementation. The TAMUS MATLAB code can be generally broken into two categories for performing two unique functions: (1) MATLAB code related to RTL source code including (a) micro-code generation and scheduling parameters that provides information on decoder scheduling for TAMUS RTL designs and (b) automated RTL code generation to support the desired parallelization, pipelining and LDPC matrices; and (2) MATLAB code related to modeling including: (a) reference bit accurate verification models and (b) higher level simulation models to verify the performance of the decoder. The TAMUS Copyrighted Works thus represent a collection of directly written RTL source code that can be synthesized into gate level netlists for physical integrated circuit implementation, MATLAB source code that generates additional synthesizable RTL source code to support specific LDPC matrices, desired parallelization and throughput, micro-code and

scheduling parameters for decoder, MATLAB models that serve as reference for verification of RTL code and for error correction performance, all for uniquely implementing Dr. Gunnam's LDPC decoder designs.

# Dr. Gunnam's Employment with LSI and LSI's Willful Infringement of the Patents-in-Suit and the TAMUS Copyrighted Works

- 59. Dr. Gunnam completed his doctoral work at TAMU in December, 2006. In January, 2008, Dr. Gunnam was hired by LSI to work on advanced LDPC decoder designs for the next generation of LSI's TrueStore hard disk drive (HDD) controller chips. LSI was aware of Dr. Gunnam's prior work on advanced designs in this area, and specifically hired him so that he could help them evaluate those designs for possible incorporation into their next generation of HDD controller chips.

- 60. Prior to and immediately upon arriving at LSI, Dr. Gunnam informed LSI that the advanced LDPC decoder designs that he had developed while at TAMU represented the intellectual property of TAMUS, and that LSI would need to obtain a license from TAMUS if LSI wished to exploit Dr. Gunnam's designs in a commercial product. At the time Dr. Gunnam joined LSI, the decoder design for the newest generation of HDD controllers, code named Mamba, had been frozen, and Dr. Gunnam was eventually invited to work on a subsequent generation design, code named McLaren.

- 61. In order to help LSI evaluate whether his advanced LDPC decoder designs were suitable for use in the McLaren design, Dr. Gunnam provided LSI with simulation models and circuit design files that he had created while at TAMU, and which are components of the TAMUS Copyrighted Works. Dr. Gunnam provided these files to LSI with the express understanding that if LSI decided to use these designs, it would need to obtain a license from TAMUS.

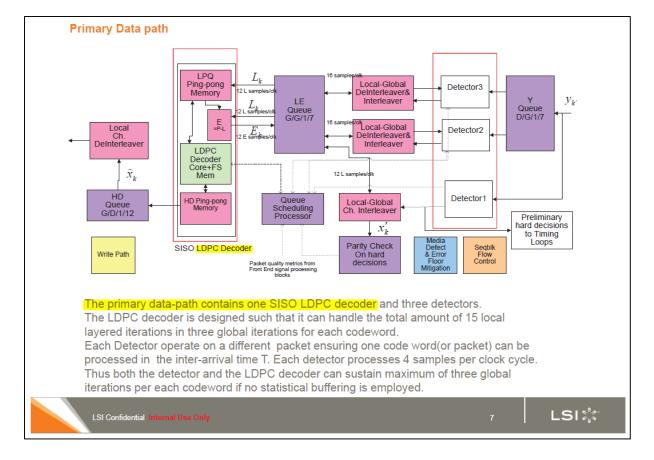

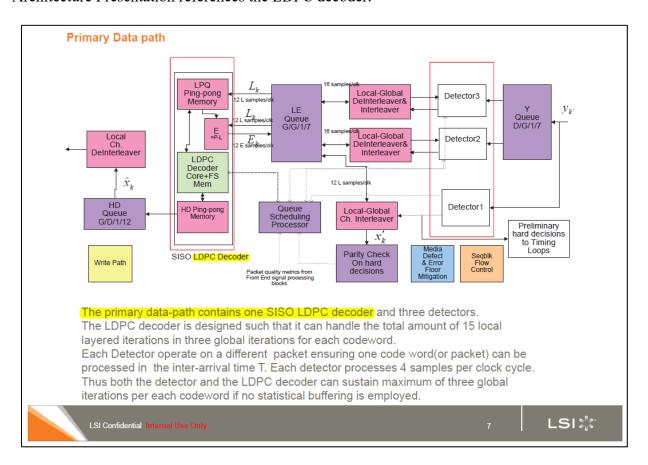

- 62. Although LSI held licensing discussions with TAMUS in the 2008 time period, LSI refused TAMUS' licensing terms and did not obtain a license from TAMUS for Dr. Gunnam's advanced LDPC decoder designs.

- 63. Despite not having obtained a license, LSI continued to investigate using Dr. Gunnam's LDPC decoder designs. In early 2009, Dr. Gunnam was assigned to work on the design of the McLaren LDPC decoder as the architect, under the supervision of Dr. Shaohua Yang ("Dr. Yang") and working closely with a design team led by Yen Johnson ("Mr. Johnson"). Also working under Mr. Johnson was Mr. Madhu Kalluri ("Mr. Kalluri"), a circuit designer and Ms. Lei Chen ("Ms. Chen"), a circuit designer. As part of the design process for the McLaren LDPC decoder, Mr. Kalluri and Ms. Chen worked with TAMUS RTL hardware design files and MATLAB design and simulation files that had been provided to LSI by Dr. Gunnam, and that were part of the TAMUS Copyrighted Works. Mr. Johnson, Mr. Kalluri, Ms. Chen and Dr. Gunnam were all aware that the hardware design files and simulation files were copyrighted by TAMUS and that LSI would need to obtain a license to use them.

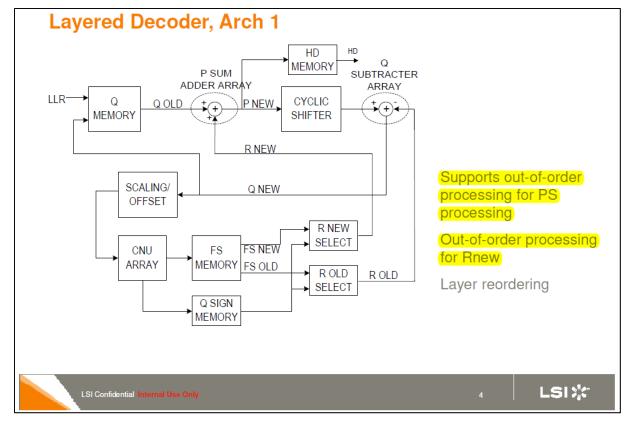

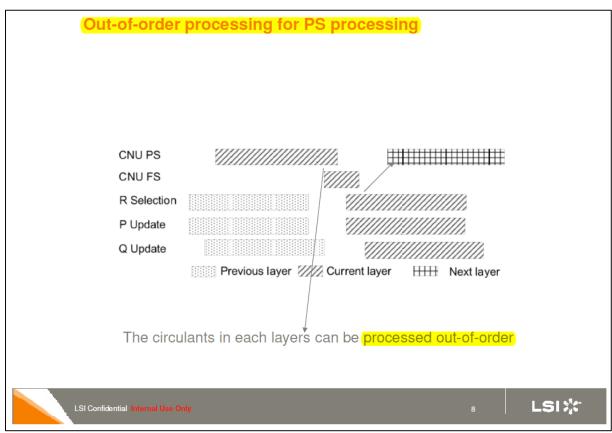

- 64. Despite this knowledge, Mr. Kalluri and Ms. Chen were directed to superficially modify the RTL and MATLAB code that had been provided by Dr. Gunnam, while maintaining the same basic program structure sequence and organization as the original works. Specifically, Mr. Kalluri and Ms. Chen copied substantially line-by-line the program modules common to the TAMUS Copyrighted Works, changing only variable names to disguise the blatant infringement. Mr. Kalluri and Ms. Chen copied, for example, core RTL modules such as LDPC\_Decoder\_Top.v, Layered\_Update\_Module.v, Q\_Computation\_Module.v, P\_Computation\_Module.v, R\_Selection.v, and Convergence\_Check\_2C\_delta\_hd.v, LUM Control.v and MATALAB files such as Gen\_LDPC\_Decoder\_parameters\_header.m,

Gen decoder verilog WiMax Sc96 rcs C2.m, Shifter4x Model.m, and premux switch expander.m, while making only trivial changes to variable names. The supposed rewrite made to much of the RTL and MATLAB modules amounted to nothing more than changing, for example, the variable used to refer to the message from the check node from 'R' to some other variable. Indeed, the so-called LDPC decoder "top" was unchanged, the decoder control used the very same parameters, control signals and core logic were not changed, and numerous other unique and esoteric aspects of the TAMUS code were untouched. In addition, LSI designers' supposed rewrite of both the RTL and MATLAB code used the very same module hierarchy common to the TAMUS Copyrighted Works, again changing only the names of certain modules. In doing so, LSI created new simulation and design files that had in all material respects the very same, structure, sequence and organization as the TAMUS Copyrighted Works and are thus substantially similar to the TAMUS Copyrighted Works. There are many, if not limitless, ways that a circuit designer could construct the simulation and hardware design software to receive, assemble, calculate, retain, correlate, and produce useful information to carry out Dr. Gunnam's LDPC decoder designs, but LSI simply pirated the particular expression of those ideas as laid out in the TAMUS Copyrighted Works. The LSI "rewrite" therefore constituted unauthorized non-literal copies of the TAMUS Copyrighted Works and unauthorized derivative works derived from the TAMUS Copyrighted Works. Upon information and belief, LSI, and subsequently Broadcom Inc., continued to use the TAMUS Copyrighted Works, the initial LSI "rewrite", and further non-literal copies or derived works in their continuing research and development efforts concerning LDPC decoders used in HDD and SSD controllers and Wi-Fi products. For instance, Ms. Chen modified the TAMUS Copyrighted Works and LSI derived works for subsequent chip variations after McLaren. See, e.g.,

https://www.linkedin.com/in/lei-chen-5a3709b/ (Ms. Chen's Linkedin profile, noting that she implemented Dr. Gunnam's novel LDPC decoders in Verilog while at LSI) LSI, and subsequently Broadcom Inc. thereby infringed TAMUS' copyrights in the TAMUS Copyrighted Works by: (a) making further modifications of the TAMUS Copyrighted Works and or the LSI derived works (and thus making non-literal copies and derived works), and (b) copying the TAMUS Copyrighted Works, the LSI derived works, or further non-literal copies or derived works by loading said works into computer memories (and thereby making literal copies in said computer memories). Upon information and belief, such infringements continue up through the present day.

- 65. In 2009 and 2010, Dr. Gunnam continued to work at LSI on the architecture for the McLaren LDPC decoder and, with LSI's knowledge and approval, incorporated key features from his advanced design work at TAMU into the LSI design. During this period, Dr. Gunnum repeatedly reminded LSI management of its obligation to obtain a license from TAMUS if it wished to use his designs.

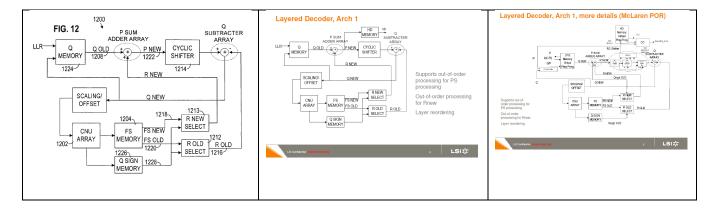

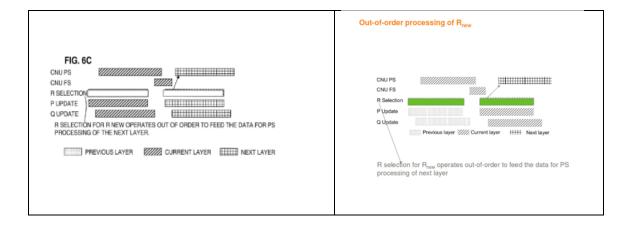

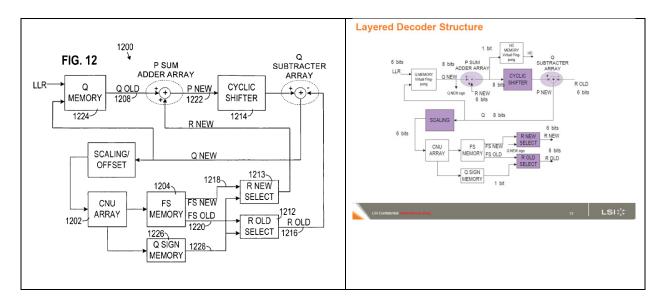

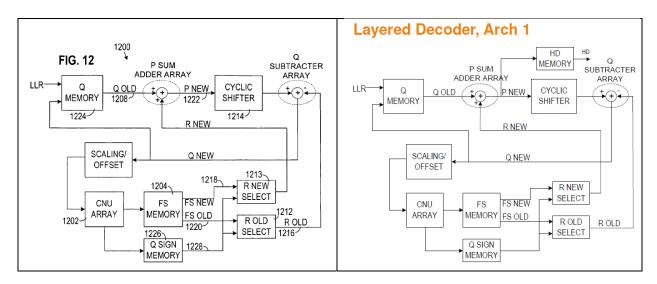

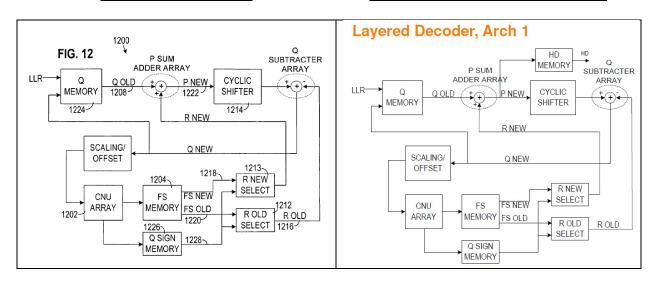

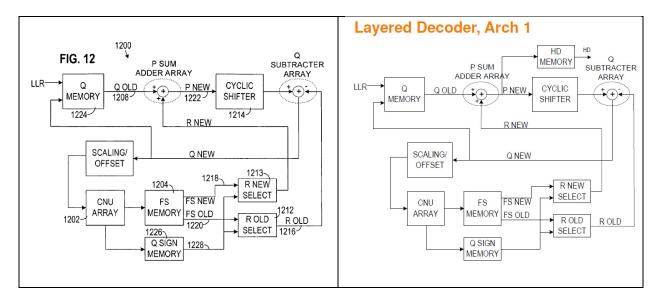

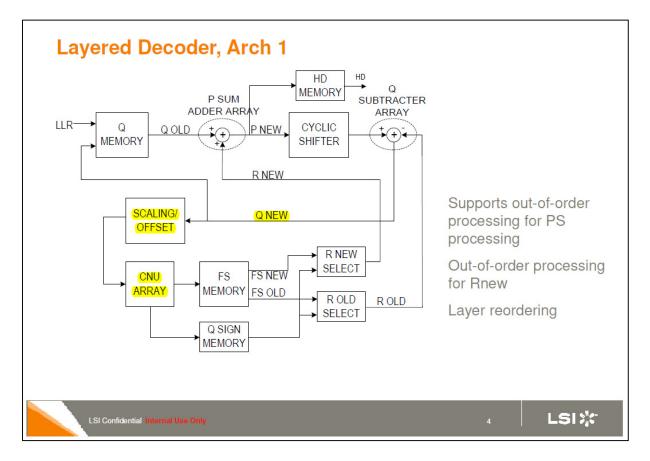

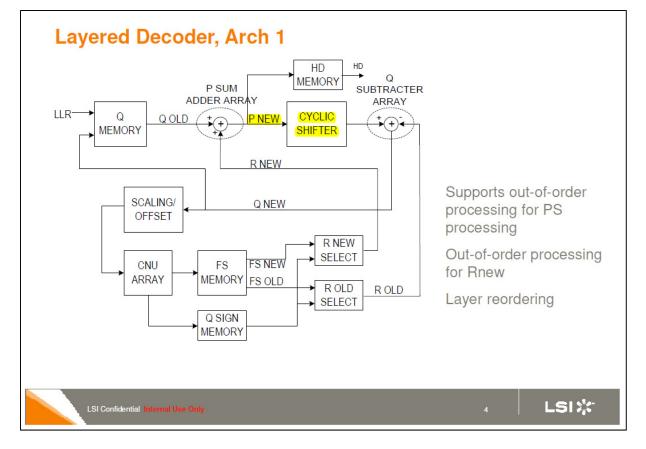

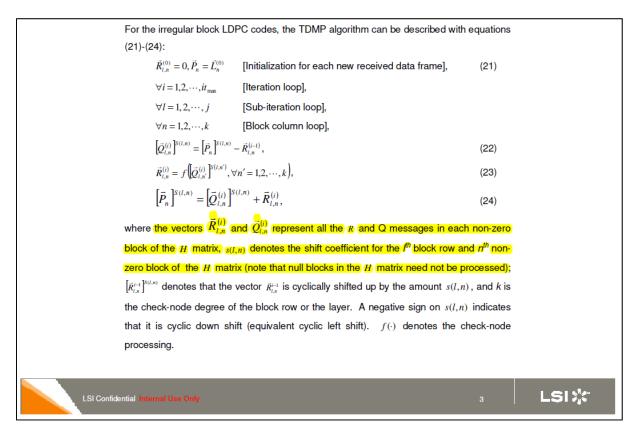

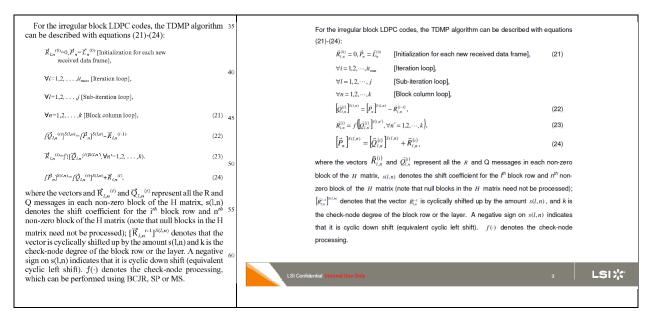

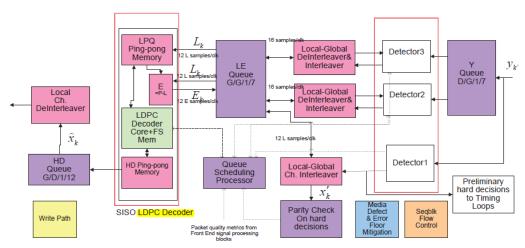

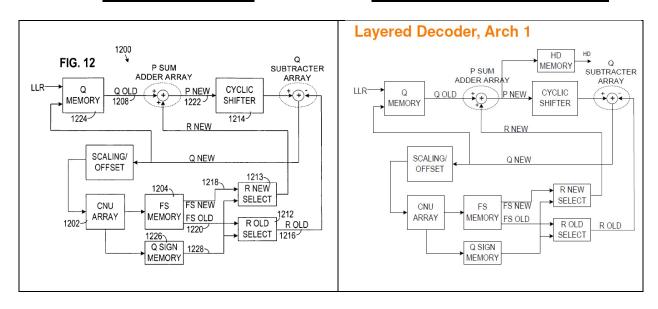

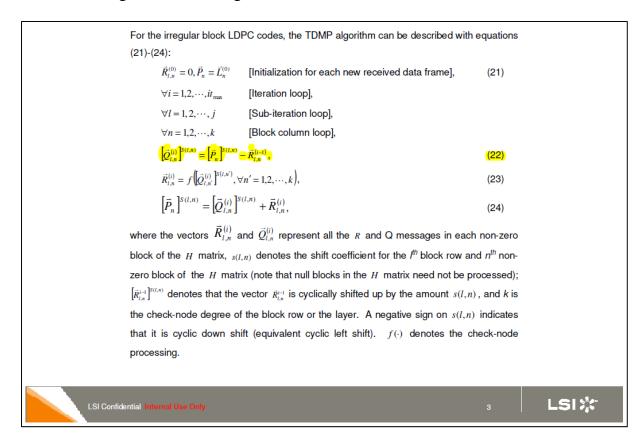

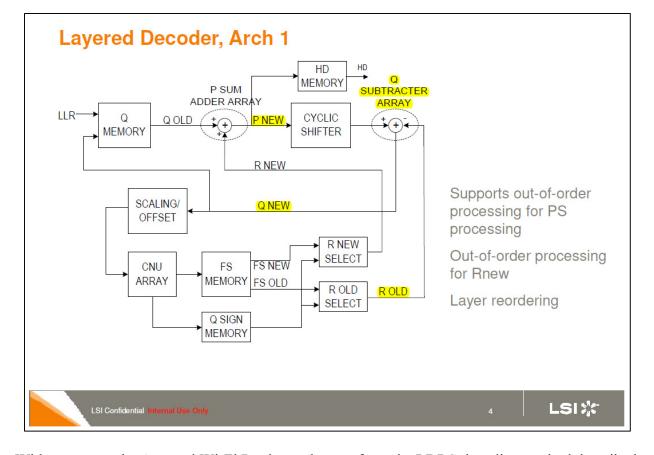

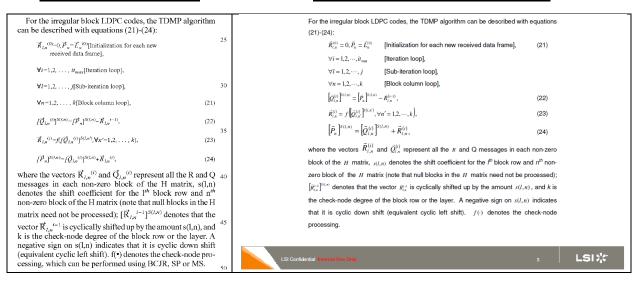

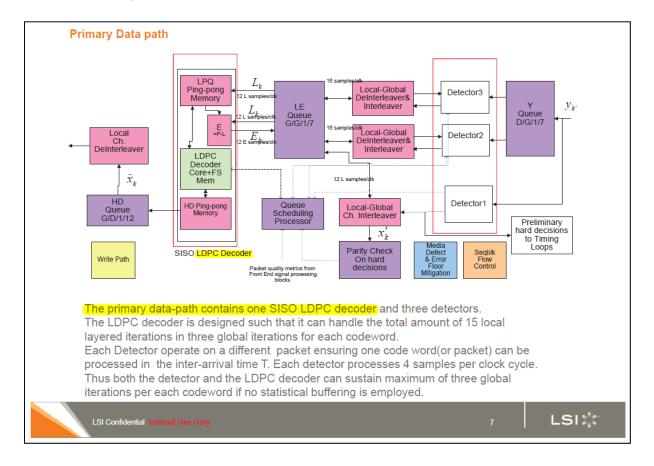

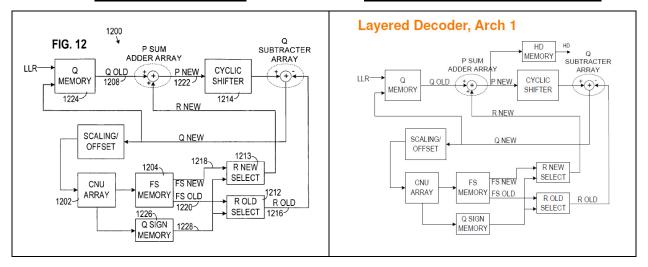

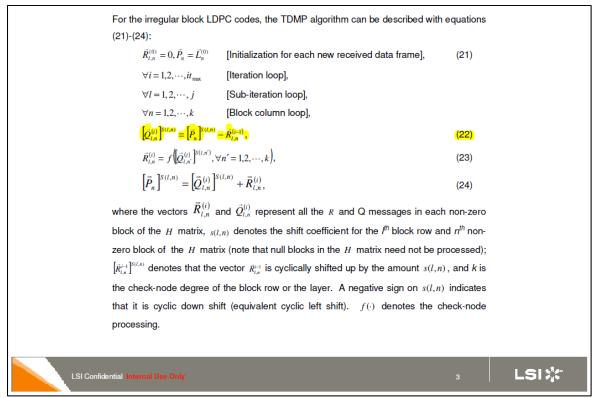

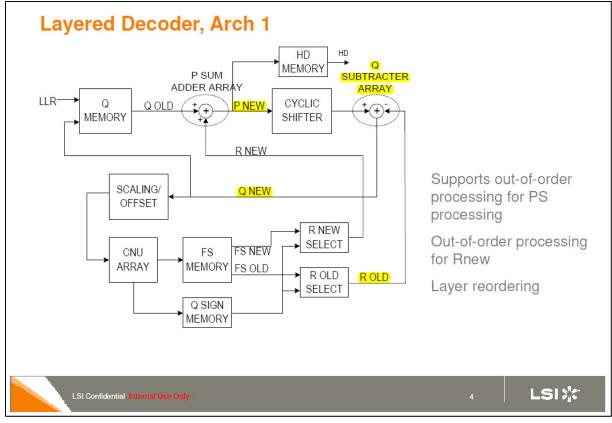

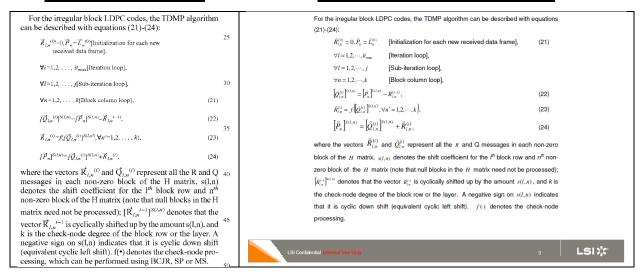

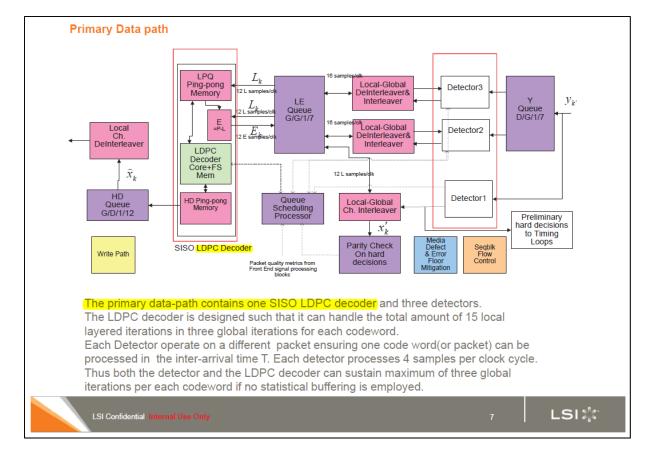

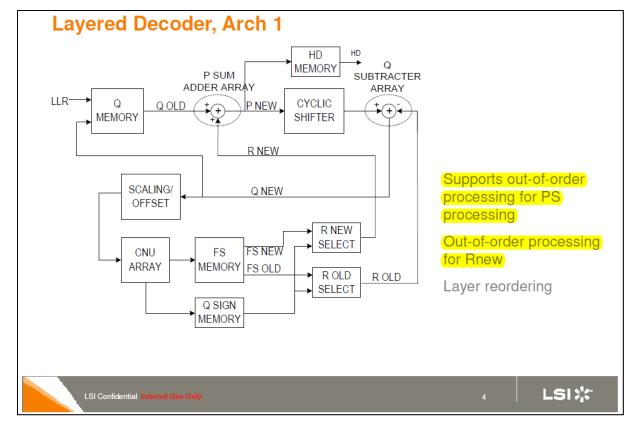

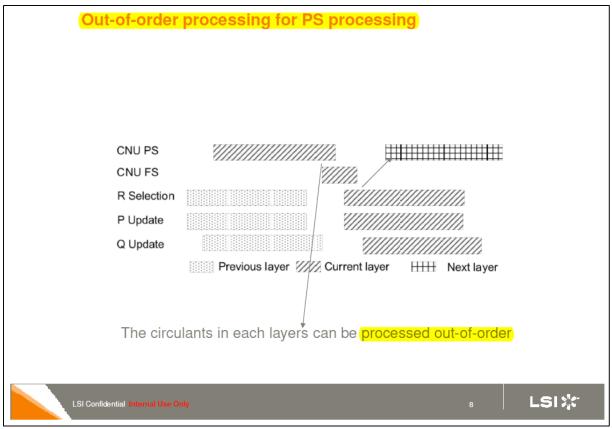

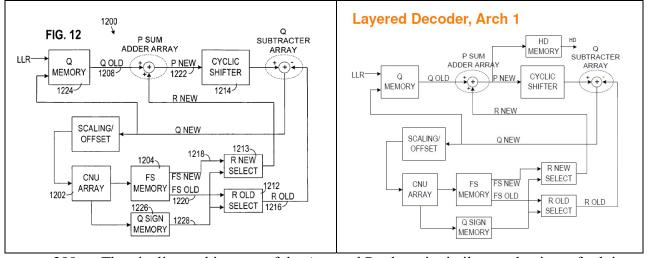

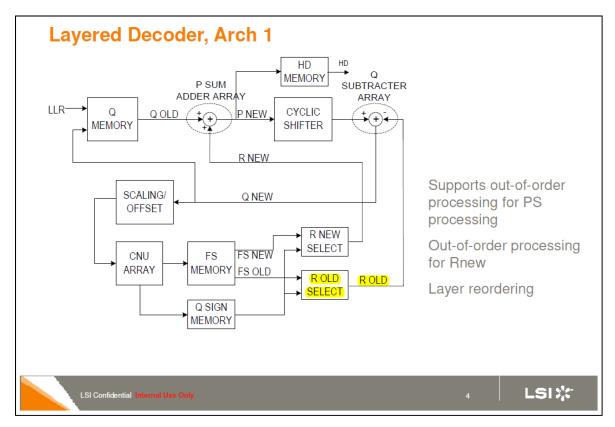

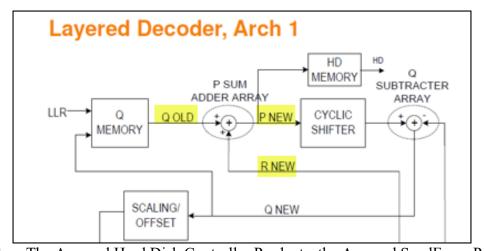

- 66. On August 21, 2009, Dr. Gunnam created an internal LSI presentation entitled "Layered Decoder for LDPC Codes with Zero Matrices" (the "Zero Matrices Presentation"). A copy of this presentation is available on the internet at <a href="https://www.scribd.com/document/367470390/read-channel-overview-part-1">https://www.scribd.com/document/367470390/read-channel-overview-part-1</a>. Dr. Gunnam's Zero Matrices Presentation described Dr. Gunnam's advanced architectural design for an LDPC Decoder developed at TAMU, a design that was essentially identical to the design in the then-pending patent applications that had been filed by Dr. Gunnam and Prof. Choi, which had been published by the USPTO on November 6, 2008 (Publication No. 2008/0276156A1, the "156 Publication"). The table below shows Figure 12 from the '156 Publication, the basic decoder

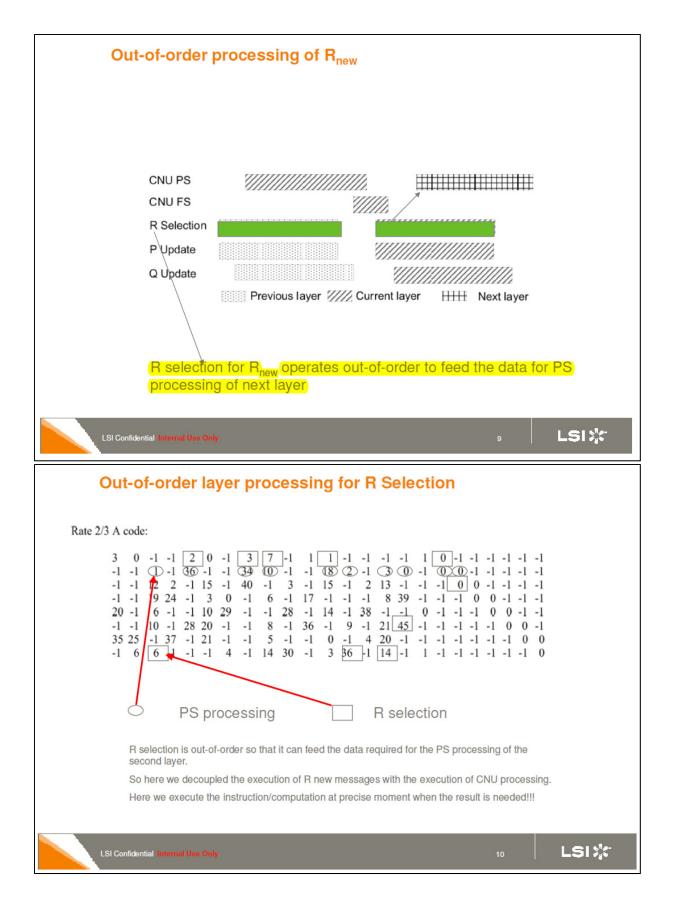

architecture described in Dr. Gunnam's Zero Matrices Presentation, and a further elaboration of that design labelled as McLaren "POR" (Plan of Record).

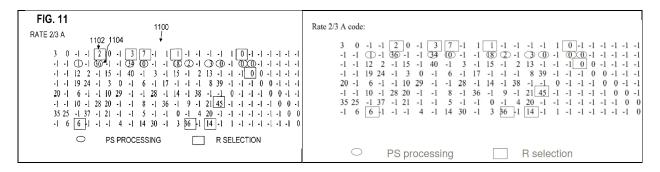

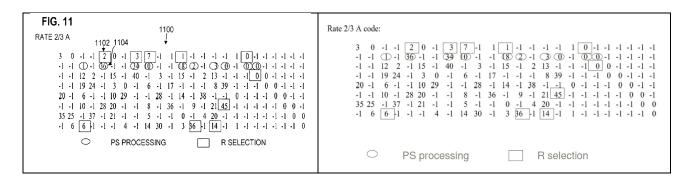

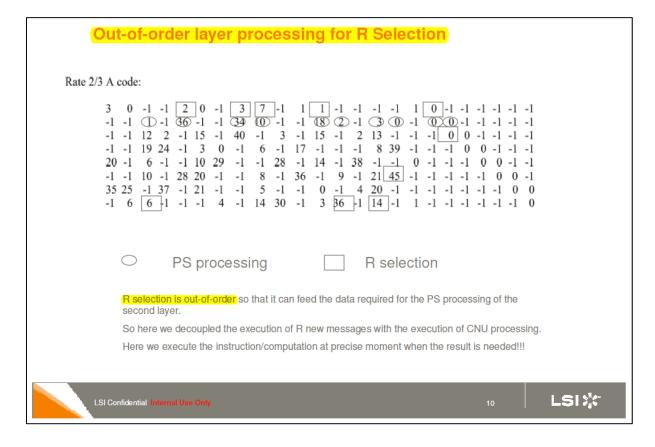

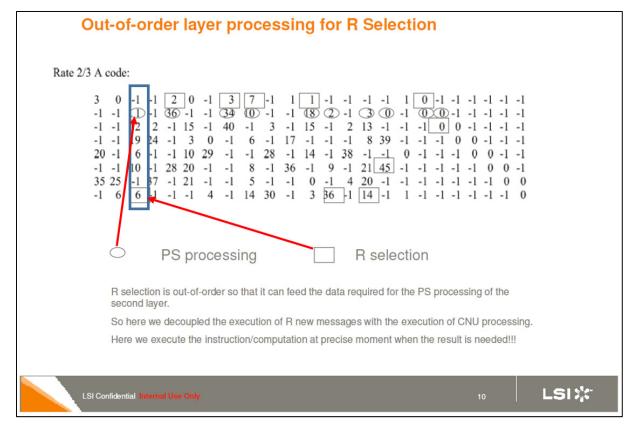

67. Dr. Gunnam's Zero Matrices Presentation included significant additional detail regarding the design of the LDPC decoder that was derived directly from the '156 Publication, as shown in the table below.

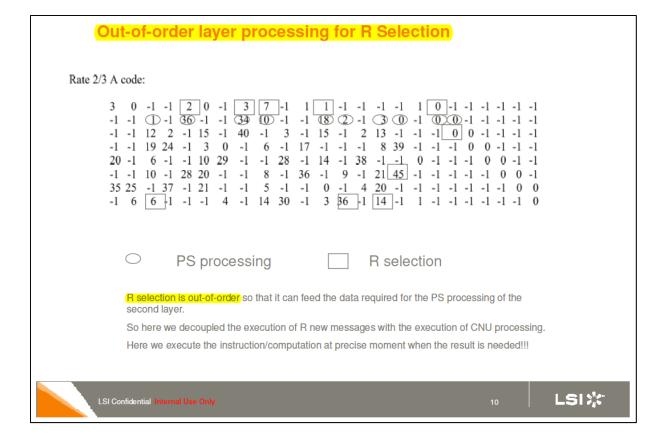

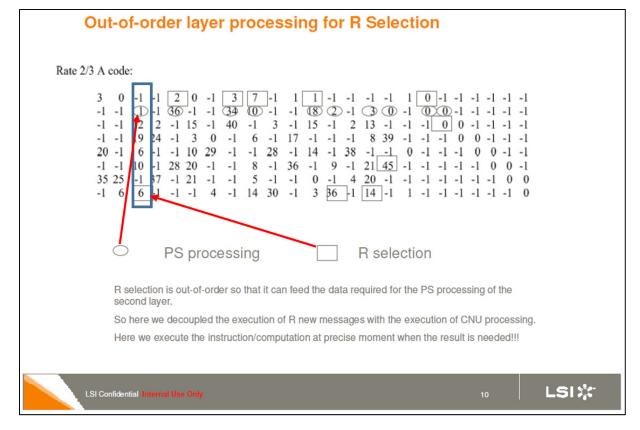

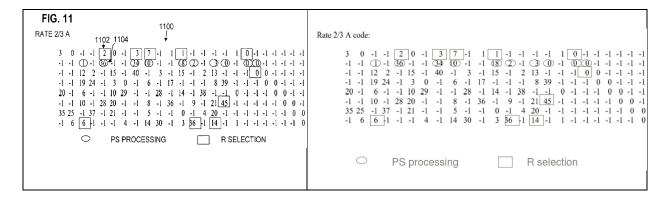

| '156 Publication                                                                                                                                                                                                                                                                                                                                                                                                                                     | Zero Matrices Presentation                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIG. 11  RATE 2/3 A  1100  3 0 -1 -1 2 0 -1 3 7 -1 1 1 -1 -1 -1 1 0 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1                                                                                                                                                                                                                                                                                                                                           | Out-of-order layer processing for R Selection  Rate 2/3 A code:  3 0 -1 -1 2 0 -1 3 7 -1 1 1 -1 -1 -1 1 0 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1                                                                                                                                                                                                                                                  |

| -1 -1 19 24 -1 3 0 -1 6 -1 17 -1 -1 -1 8 39 -1 -1 -1 0 0 -1 -1 -1 20 -1 1 1 29 -1 -1 -1 -1 20 -1 1 1 29 -1 -1 -1 -1 20 -1 -1 -1 -1 0 0 -1 -1 -1 -1 1 10 -1 28 20 -1 -1 8 -1 36 -1 9 -1 2 1 4 5 1 -1 -1 -1 -1 -1 0 0 -1 -1 -1 -1 1 1 0 0 -1 35 25 -1 37 -1 21 -1 -1 5 -1 -1 0 0 -1 3 5 25 -1 37 -1 21 -1 -1 -1 5 -1 -1 0 0 -1 3 5 25 -1 37 -1 21 -1 -1 -1 -1 -1 0 0 -1 35 25 -1 37 -1 21 -1 -1 -1 -1 -1 -1 0 0 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 | 20 -1 6 -1 -1 10 29 -1 -1 28 -1 14 -1 38 -1 -1 0 -1 -1 -1 0 0 -1 -1 -1 -1 10 -1 28 20 -1 -1 8 -1 36 -1 9 -1 21 45 1 -1 -1 -1 -1 -1 0 0 -1 -1 35 25 -1 37 -1 21 -1 -1 5 -1 -1 0 -1 4 20 -1 -1 -1 -1 -1 -1 -1 0 0 -1 6 6 1 -1 -1 4 -1 14 30 -1 3 5 5 1 14 -1 1 -1 -1 -1 -1 -1 0 0 -1 6 6 1 -1 -1 4 -1 14 30 -1 3 5 6 1 14 -1 1 -1 -1 -1 -1 -1 -1 0 0 -1 6 6 1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 -1 - |

| O PS PROCESSING R SELECTION                                                                                                                                                                                                                                                                                                                                                                                                                          | R selection is out-of-order so that it can feed the data required for the PS processing of the second layer.  So here we decoupled the execution of R new messages with the execution of CNU processing. Here we execute the instruction computation at precise moment when the result is needed!!!                                                                                               |

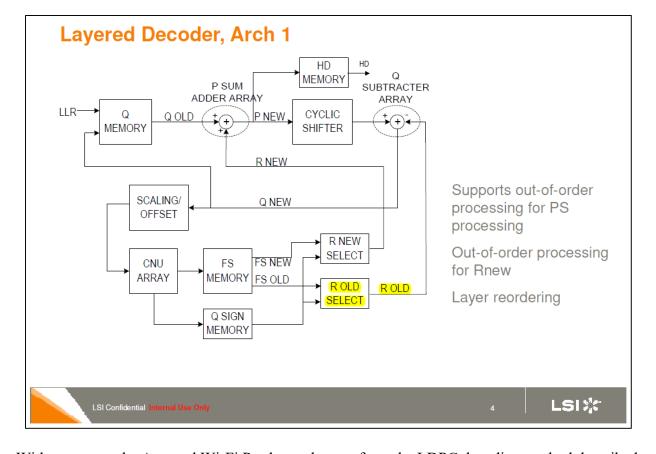

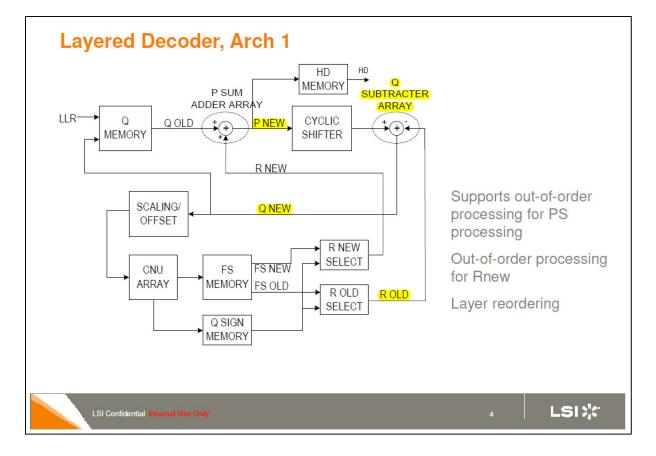

- 68. On August 26, 2009, Dr. Gunnam, along with LSI colleagues Dr. Yan Hang and Mr. Kalluri, made a presentation entitled LDPC Decoder Reevaluation ("Reevaluation Presentation"). A copy of this presentation is available on the internet at <a href="https://www.scribd.com/document/367470390/read-channel-overview-part-1">https://www.scribd.com/document/367470390/read-channel-overview-part-1</a>. The presentation explained that the "current option McLaren is the layered decoder with layer re-ordering and out-of-order processing," two key concepts from Dr. Gunnam's TAMU design. The presentation further stated that "we would like to re-evaluate the LDPC decoder options for McLaren due to non-technical issues." Upon information and belief, the "non-technical issues" that led to the re-evaluation of Dr. Gunnam's TAMU design was the understanding by LSI management that Dr. Gunnam's design was the subject of TAMUS pending patent applications and copyrights and that the use of that design would necessitate obtaining a license from TAMU.

- 69. The Reevaluation Presentation ("the presentation") described testing and modelling of five different alternatives to Dr. Gunnam's LDPC Decoder design. As shown in the table below, the presentation concluded that there were no viable alternatives to using Dr. Gunnam's design, and recommended staying with the existing design.

# McLaren LDPC Decoder Re-Evaluation

|                                                                              | Feasibility                                                                       | Area delta Compared to Optimized layered decoder         | Other Impact                                                   | Action Item                                            | Owner                             | ETA      |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------|-----------------------------------|----------|

| Item 1:<br>NLD-30 local<br>iterations                                        | Not Feasible                                                                      | Upto 1 mm^2<br>(based on<br>Madhu's latest<br>estimates) | No SNR loss<br>For code 17<br>Small SNR<br>loss<br>For code 12 | Evaluate<br>area                                       | Madhu, Nirav,<br>Hao, Yang, Kiran | 08/28/09 |

| Item 2:<br>LD-with fewer<br>local iterations &<br>constraints                | Not Feasible                                                                      |                                                          | More SNR<br>loss                                               | Assess<br>constraint,<br>feasibility, needed<br>effort | Zongwang                          |          |

| Item 3:<br>Delayed layered<br>decoding                                       | Not Feasible                                                                      | 0.2-0.3 mm^2                                             | Expect SNR<br>loss of 0.05-<br>0.1dB(still<br>looking into)    | Code up & simulate                                     | Kiran, Yang                       | 08/28/09 |

| Item 4:<br>Selective<br>processing,<br>(Snooze & wake<br>up,<br>Skip layers) | Expect gains of around 15% which are not sufficient to address the current issue. |                                                          |                                                                | Code up & simulate                                     | Yang,<br>Kiran                    |          |

| Item 5:<br>Shuffled Column<br>decoder                                        | Not feasible due to huge area increase                                            |                                                          |                                                                |                                                        | Kiran                             |          |

- 70. In making its recommendation, the presentation noted that "other options have an area penalty of up to 1mm^2 or the SNR loss of more than 0.4dB." In other words, the other alternatives would take up more area, or would be less effective in correcting errors, than Dr. Gunnam's design. Upon information and belief, LSI considered those alternatives commercially unacceptable to Dr. Gunnam's design.

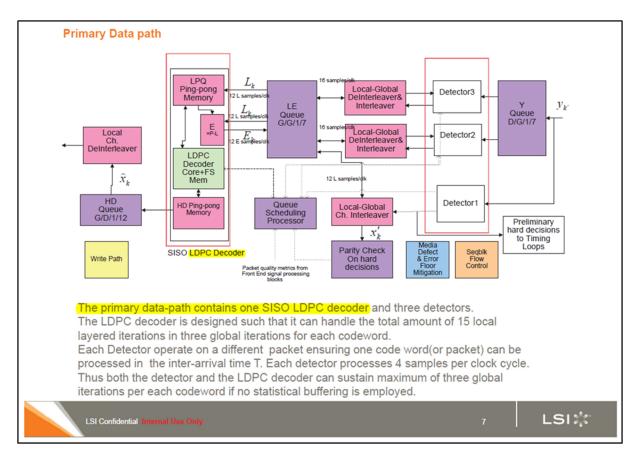

- 71. On October 13, 2009, an LSI team comprised of Dr. Gunnam, Dr. Yang, and Dr. Zongwang Li, made an internal presentation to LSI entitled "McLaren Client Server Architecture/Scheduling" ("Client Server Presentation"). A copy of this presentation is available on the internet at <a href="https://www.scribd.com/document/367470390/read-channel-overview-part-1">https://www.scribd.com/document/367470390/read-channel-overview-part-1</a>. The Client Server Presentation, key features of the McLaren LDPC Decoder designs are discussed, and the decoder design is described as follows:

- New Decoder architecture: Use of layered decoder optimized based on "On-the-fly Computation" to minimize memory, logic requirements and remove the pipeline idle cycles and memory access conflicts associated with conventional layered/non-layered decoder designs. The decoder is highly optimized for area and high speed saving upto 1 mm<sup>2</sup> while compared to other implementations.

- 72. This description of the McLaren LDPC decoder included key features of the advanced decoder design developed by Dr. Gunnam at TAMU, including "on-the-fly computation to minimize memory, logic requirements and remove pipeline idle cycles and memory access conflicts associated with conventional layered/non-layered decoder designs."

- 73. Moreover, the architectural drawing included in the October 13, 2009 presentation was virtually identical to the corresponding drawing (FIG. 12) contained in specification of the Patents-in-Suit, a version of which had been published by the USPTO on November 6, 2008 (Publication No. 2008/0276156A1, the "'156 Publication").

#### '156 Publication at FIG. 12

# **LSI's Client Server Presentation**

74. LSI management was extremely pleased with the work that Dr. Gunnam did on the LDPC decoder design for the McLaren chip. In his 2009 annual performance review, Dr.

Gunnam's manager, Dr. Yang, gave him an overall descriptor of "Exceeds Expectations," and stated as follows:

Kiran is the team member who worked hardest literally in the team around the clock. He has demonstrated the highest level of innovation in hardware architecture and decoder algorithm, the Mclaren codec hardware architecture and algorithm is a very smart architecture which sizes -1mm2 less than any alternative than we have evaluated for the same LDPC code matrix. Kiran innovated the whole read path architecture and half of the write path architecture. The key inventions are the local-global interleaver architecture, layered decoder architecture, and codec integration.

Kiran also worked closely with more than 10 designers (in both Shanghai and Milpitas) on a hourly bases on various modules in the Mclaren channel. He has discovered hundreds of issues and addressed them during the early development stage.

- 75. Upon information and belief, LSI management finalized the design for the McLaren TrueStore HDD controller chip in 2010, and included patented features of Dr. Gunnam's LDPC decoder design in the final design. During 2010, Dr. Gunnam made repeated requests to LSI management to approach TAMUS to obtain a license for the TAMUS intellectual property that he knew to be incorporated into that design. LSI failed to act upon those requests and never obtained a license from TAMUS, despite its awareness at the time that at its McLaren design incorporated TAMUS intellectual property. LSI's actions caused Dr. Gunnam to become increasingly frustrated with LSI's failure to properly license the TAMUS intellectual property it was using in the McLaren design.

- 76. On December 21, 2010, Dr. Gunnam wrote an e-mail to certain managers at LSI entitled: "Some important legal and ethical issues." The e-mail pointed out that the LDPC decoder design used in the McLaren design "reads on claims" in his and Dr. Choi's pending, published, patent applications, which, as discussed above, these certain managers were intimately familiar. Dr. Gunnam also stated that the layered decoder architecture proposed for Spyder, the code-name for the generation of HDD controller chips after McLaren, also read on claims in the pending applications. Dr. Gunnam's e-mail urged LSI to "look for a way to license the" pending patent applications. The email also notes that Dr. Gunnam had informed Dr. Yang

(now Director of Read Channel Backend Architecture at Broadcom) that LSI needed to attain a license from Texas A&M. The December 2010 email also stated that Dr. Yang had informed Dr. Gunnam to refrain from listing the Texas A&M patent applications on LSI's internal wiki system related to the McLaren product.

- 77. In March of 2011, Dr. Gunnam was given his performance review for 2010. In this review, he was reprimanded for the December 21, 2010 e-mail because the e-mail supposedly "compromis[ed] the competitiveness of LSI's recent read channel [i.e., HDD controller] products by putting all possible/suspected IP infringements on record."

- 78. Shortly after receiving this review, Dr. Gunnam decided to leave his employment with LSI, and resigned in March, 2011.

- 79. After leaving LSI, Dr. Gunnam continued to be concerned that LSI was using TAMUS intellectual property without a license.

- 80. On April 27, 2012, Dr. Gunnam contacted Dr. Yuan Xing Lee ("Dr. Lee"), Dr. George Mathew ("Dr. Mathew"), and Mr. Johnson Yen ("Mr. Yen") at their official LSI email addresses to inform them of the pending patent applications for the '023 and '522 Patents.

- 81. At the time, Dr. Lee was a Vice President in charge of engineering at LSI, Dr. Mathew was a manager at LSI, and Mr. Yen was a senior engineering manager at LSI.

- 82. As part of this email, Dr. Gunnam again informed LSI that "claims read on several features of non-layered decoder and significant design of layered decoders (for the products I directly worked on as well as the products that are/being made based on my earlier work)."

- 83. Dr. Lee, Dr. Mathew, and Mr. Yen all received Dr. Gunnam's April 27, 2012 e-mail.

- 84. On information and belief, Dr. Lee called a meeting at LSI to discuss LSI's use of TAMUS' intellectual property in its products after receiving Dr. Gunnam's April 27, 2012 email. On information and belief, at least Dr. Lee and Mr. Kalluri attended this meeting.

- 85. On information and belief, LSI took no actions to stop LSI's infringement of the Patents-in-Suit after receiving Dr. Gunnam's April 27, 2012 email.

- 86. Thereafter, when the '522 Patent issued on January 22, 2013, Dr. Gunnam wrote an e-mail to Dr. Lee, Dr. Mathew, and Mr. Yen, notifying them the patent had issued, and that it covered several features of several implemented LSI decoders, including McLaren and Spyder.

- 87. Dr. Lee, Dr. Mathew, and Mr. Yen received Dr. Gunnam's January 22, 2013 e-mail.

- 88. None of these individuals acknowledged Dr. Gunnam's email, nor, upon information and belief, did they take any actions to ensure that the McLaren and Spyder chips were not infringing the '522 Patent.

- 89. On information and belief, LSI took no actions to stop LSI's infringement of the Patents-in-Suit after receiving Dr. Gunnam's January 22, 2013 email.

- 90. On January 31, 2014, Dr. Gunnam wrote again to Dr. Lee, informing him that the '023 and '140 Patents had issued, and that the '250 Patent was about to issue on February 18, 2014.

- 91. In that January 31, 2014 email, Dr. Gunnam reminded Dr. Lee that he had repeatedly discussed with him and other LSI managers over the years that the TAMUS patents disclose key features of LDPC decoders that had been incorporated into LSI's designs, that those decoder designs were "based on the material from these patents and patent applications," and that "the issued and pending patents cover several features of several implemented and planned

layered and non-layered decoders as part of the read channel ICs [i.e., the McLaren and Spyder disk controller chips]." Dr. Gunnam specifically identified claims 1-98 of the '522 Patent, claims 1-30 of the '023 Patent, claims 1-22 of the '140 Patent, and claims 1-54 of the soon-to-issue '250 Patent as covering features in the McLaren and Spyder products.

- 92. In the January 21, 2014 email to Dr. Lee, Dr. Gunnam also informed him that RTL code used by LSI to develop its LDPC decoder designs was based on TAMUS RTL code (which is a part of the TAMUS Copyrighted Works) and had similar structure, sequence, organization, and variables to that code. Dr. Gunnam advised Dr. Lee that this use of TAMUS RTL code could create a "copyright issue" for LSI.

- 93. Dr. Lee took no actions to stop LSI's use of Texas A&M's source code after receiving Dr. Gunnam's January 21, 2014 email.

- 94. Dr. Lee received Dr. Gunnam's January 31, 2014 e-mail.

- 95. On information and belief, LSI took no actions to stop LSI's infringement of the Patents-in-Suit after receiving Dr. Gunnam's January 31, 2014 email.

- 96. On information and belief, LSI, Avago, and now Broadcom Inc. have taken no efforts to cease or mitigate infringement of the Patents-in-Suit or the TAMUS Copyrighted Works.

#### Defendants apply the Texas A&M Technology to SSD Controller Products

- 97. In January 2012, LSI acquired SandForce, Inc, a maker of solid state drive ("SSD") controller products.

- 98. In 2014, LSI introduced Sandforce controllers using LSI's SHIELD technology.

- 99. In 2014, Mr. Kent Smith ("Mr. Smith"), an employee of LSI's Flash Components Division gave an interview (available at <a href="https://www.electronicdesign.com/memory/interview-kent-smith-addresses-error-correction-and-flash-storage-technology">https://www.electronicdesign.com/memory/interview-kent-smith-addresses-error-correction-and-flash-storage-technology</a>).

- 100. While being interviewed in 2014, Mr. Smith stated the following: "LSI's first implementation of LDPC codes was to correct errors in the magnet media of hard disk drives. LSI TrueStore read channels with LDPC iterative decoding technology have been shipping in high volume for HDDs since 2010. This experience and engineering expertise are leveraged in SHIELD error correction technology."

- 101. On information and belief, LSI incorporated features of the McLaren LDPC decoder design that are derived from, and covered by, the TAMUS Patents-in-Suit into Sandforce Controllers at least by 2013, including at least the SandForce SF3700 flash controller family and other SandForce controllers with SHEILD technology ("the Accused SandForce Products").

- 102. On information and belief, LSI sold its SandForce line to Seagate in late 2014.

- 103. Sales of the SandForce SF3700 prior to this sale of the SandForce line to Seagate were made after LSI received notice of at least the '522 Patent and had knowledge of their infringement of it.

- 104. On information and belief, Broadcom Inc. acquired Densbits, Inc. in December 2015.

- 105. On information and belief, Densbits designs and manufactures SSD controller products.

- 106. On information and belief, following Broadcom Inc.'s acquisition of Densbits,

Broadcom Inc. assigned several individuals associated with the development of LSI's TrueStore

products to work on improving the SSD controller technology purchased from Densbits.

- 107. On information and belief, Defendants and/or the Broadcom Predecessor Entities have incorporated features of the McLaren LDPC decoder design that are covered by the TAMUS Patents-in-Suit into Densbits' SSD controllers (the "Accused Densbits Products") and sold them to customers.

#### Defendants apply the Texas A&M Technology to Wi-Fi Products

- 108. Andrew J. Blanksby holds the title of Distinguished Engineer at Broadcom Inc., and his LinkedIn page states that he "lead[s] development of Low-Density Parity-Check (LDPC) technology for WLAN used in all major smart phones, tablets, and access points by companies such as Apple, Samsung, and LG."

- 109. In litigation between the California Institute of Technology and Broadcom concerning Broadcom's infringement of other LDPC technology, Dr. Blanksby stated that he has been employed by Broadcom since 2005 and that he leads the development of the LDPC technology used in Broadcom's products. *See California Institute of Technology v. Broadcom Limited et al.*, No. 2:16-cv-03714, D.I. 707-3 (Declaration of Dr. Andrew Blanksby), filed October 1, 2018, at paragraph 4. In that Declaration, Dr. Blanskby also noted that he is the named inventor on multiple LDPC patents and that at least some of his LDPC patents relate to Broadcom's products. *See id* at paragraph 5 ("As a lead developer of LDPC technologies for Broadcom, I have become familiar with patents and patent claims. I am a named inventor on more than twenty issued United States patents, the majority of which relate to LDPC encoder and

decoder technology, and it is within my normal responsibility to understand how such patents may (or may not) relate to Broadcom's products.").

- 110. Alvin L. Lin holds the title of Design Engineer at Broadcom and has been employed by Broadcom since 2006. Public information from the aforementioned *California Technical Institute v. Broadcom* litigation notes that Mr. Lin was also involved in the design of Broadcom products that use LDPC technology.

- 111. Andrew Blanksby and Alvin Lin are the named co-named inventors on multiple patents that are directed towards LDPC technology and originally assigned to Broadcom Corporation, one of the Broadcom Predecessor Entities. These patents issued from applications filed while both named co-inventors worked at Broadcom.

- 112. Blanksby and Lin are named as co-inventors on United States Patent No. 8,341,488, entitled "Accumulating LDPC (Low Density Parity Check) Decoder" ("the '488 patent"), which issued to Broadcom Corp. on December 25, 2012. The '488 patent claims priority to two provisional applications, provisional application No. 61/086,081, filed on August 4, 2008 ("the '081 application") and provisional application No. 61/086,097, filed on August 4, 2008 ("the '097 application"), while both named co-inventors were employed at Broadcom.

- 113. The '488 patent describes an LDPC decoder architecture that would, if operated, practice the inventions described in at least Claim 18 of the '140 Patent.

- 114. Blanksby and Lin are also co-inventors on United States Patent No. 8,341,489, entitled "Permuted Accelerated LDPC (Low Density Parity Check) Decoder" ("the '489 patent"), which also issued to Broadcom Corp. on December 25, 2012. The '489 patent, like the '488 patent, claims priority to the '081 application and the '097 application.

- 115. The '489 patent describes an LDPC decoder architecture that would, if operated, practice the inventions described in at least Claim 85 of the '522 Patent and Claim 17 of the '250 Patent.

- 116. Broadcom boasts that it incorporates its patented technology into its products. *See, e.g.*, <a href="https://investors.broadcom.com/static-files/f81d3fbb-755c-44a7-ab4d-8b5fe16633fb">https://investors.broadcom.com/static-files/f81d3fbb-755c-44a7-ab4d-8b5fe16633fb</a>, exemplary 2019 Broadcom From 10-K, at page 11 ("We focus our patent application program to a greater extent on those inventions and improvements that we believe are likely to be incorporated into our products, as contrasted with more basic research").

- 117. Wi-Fi IEEE standards 802.11ac and 802.11ad support LDPC coding and decoding, and Wi-Fi chipsets sold by Broadcom must support LDPC decoding.

- 118. Broadcom advertises Wi-Fi products, like the exemplary BCM4350 "5G WiFi 802.11ac Client" as both compliant with IEEE Wi-Fi standards and supporting LDPC decoding. *See, e.g.*, <a href="https://www.broadcom.com/products/wireless/wireless-lan-infrastructure/bcm4350/">https://www.broadcom.com/products/wireless/wireless-lan-infrastructure/bcm4350/</a> ("802.11ac-compliant . . . low-density parity check codes (LDPC)").

- LDPC-related litigation with the California Institute of Technology, in its promotional literature, and upon information and belief, Broadcom chipsets that support 802.11ac, 802.11ad, 802.11ax (to include Wi-Fi6 and 6e) and incorporate LDPC decoder designs, including the exemplary BCM4350 and all other 802.11ac- 802.11ad, 802.11ax-compliant, Wi-Fi6, or WiFi6E compliant Broadcom products that have an LDPC decoder (hereinafter the "Accused Wi-Fi Products"), incorporate designs described in the '488 patent and the '489 patent, and therefore infringe at least Claim 85 of the '522 Patent, Claim 17 of the '250 Patent, and Claim 18 of the '140 Patent. Accused Wi-Fi Products include but are not limited to BCM6710, BCM6755, BCM47622,

BCM6752, BCM6750, BCM43684, BCM43694, BCM47452, BCM43525, BCM4366, BCM4350, BCM43162, BCM61755, BCM4335, BCM43460, BCM43526, BCM4360, BCM4389, BCM43456, BCM4375, BCM43516, BCM43556, BCM43558, BCM43566, BCM43569, BCM43462, BCM43465, BCM4352, BCM43520, BCM4356, BCM43567, BCM43570, BCM4358, BCM43598, BCM43602, BCM4365E, BCM4366E, BCM20130, BCM6705, BCM43692, BCM43693, BCM43698, BCM43751, BCM43752, BCM4378, BCM4391, BCM43353, BCM4339, BCM4345, BCM43455, BCM4354, BCM43572, BCM4359, BCM4361, BCM4371, BCM4373, BCM4377, BCM47189, BCM53573, and BCM43142.

121. The Accused Hard Disk Controller Products, the Accused SandForce Products, the Accused Densbits Products, and the Accused Wi-Fi Products are collectively referred to as the "Accused Products."

# (Infringement under 35 U.S.C. § 271 of U.S. Patent No. 8,418,023)

- 122. Plaintiff repeats and re-alleges the paragraphs above as if fully set forth herein.

- 123. The '023 Patent is valid, enforceable, and was duly issued on August 9, 2013 in full compliance with Title 35 of the United States Code.

- 124. On information and belief, in violation of 35 U.S.C. § 271, Defendants and/or the Broadcom Predecessor Entities have infringed, contributed to the infringement of, and/or induced others to infringe the '023 Patent, either literally or under the doctrine of equivalents, by, among other things, making, using, offering for sale, selling, selling infringing products abroad with knowledge and intent that the infringing products be imported into the United States by others, and/or importing into the United States unlicensed systems and/or products in a manner that infringes Claims 1-30 of the '023 Patent.

- 125. On information and belief, Defendants and/or the Broadcom Predecessor Entities have directly infringed the '023 Patent, for example, by making, using, selling, offering to sell, and/or importing into the United States the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products, which meet each and every limitation of at least Claim 1 of the '023 Patent, in violation of Plaintiff's patent rights and without Plaintiff's license or authority. Non-limiting examples of such infringement are provided below, based on the limited information currently available to Plaintiff.

- 126. Claim 1 of the '023 Patent recites as follows:

- 1. A low density parity check code decoder, comprising:

a control unit that controls decoder processing, the control unit configured to:

cause the decoder to process blocks of a low density parity check ("LDPC") matrix out of order; and

schedule computation of R messages for a first non-zero block and computation of P messages and Q messages for a second non-zero block such that R messages for the first non-zero block are generated while processing the second non-zero block based on a determination of need for the R messages for the computation of P and Q messages for the second non-zero block;

wherein the first non-zero block and the second non-zero block are in a same column of the matrix.

127. On information and belief, the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products satisfy each and every limitation of Claim 1 of the '023 Patent. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products include a low density parity check code decoder. For example, an LSI presentation dated October 13, 2009 entitled: "Mclaren Client Server Architecture/Scheduling" (hereinafter, the "McLaren Architecture Presentation") references the LDPC decoder.

- 128. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products include a control unit that controls decoder processing, and as set forth below, that control unit is configured to perform the actions required of the claimed control unit.

- 129. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products cause the decoder to process blocks of an LDPC matrix out of order. For example, an LSI presentation dated August 21, 2009 entitled: "Layered Decoder for LDPC Codes with Zero Matrices" (hereinafter, the "Layered Decoder Presentation") references out of order processing and includes many figures taken directly from the '023 Patent.

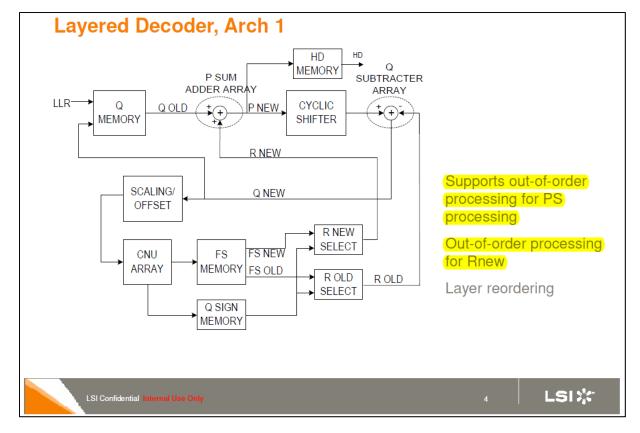

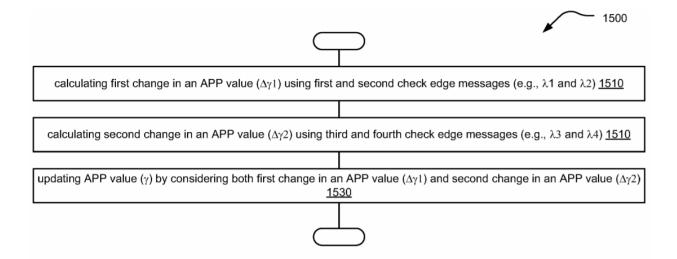

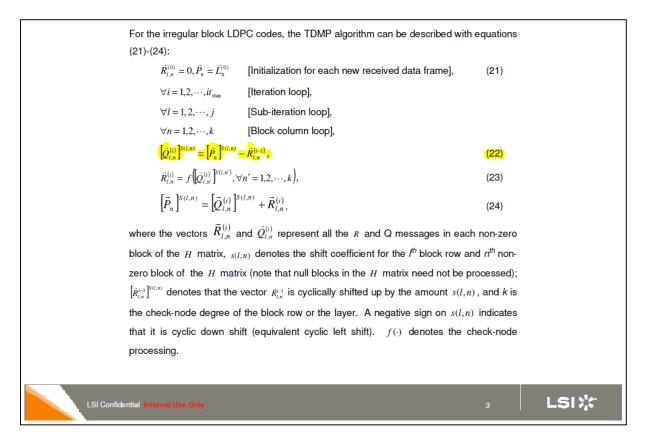

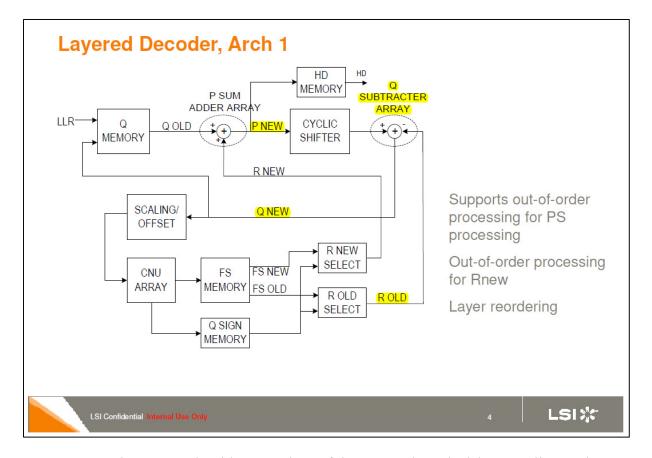

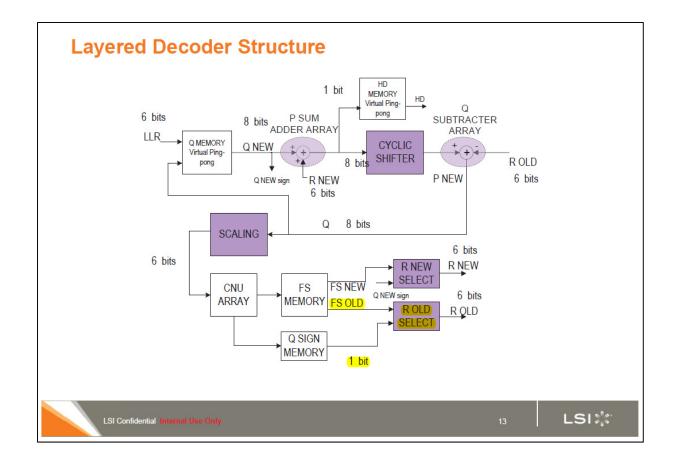

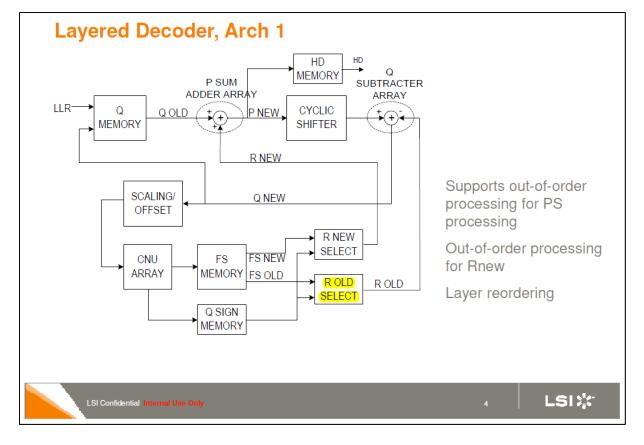

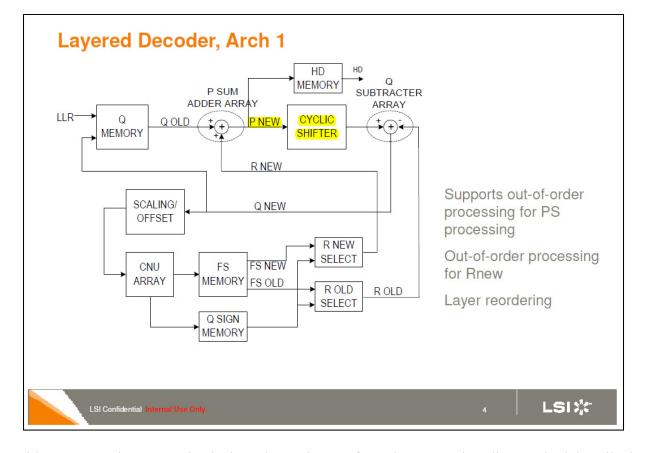

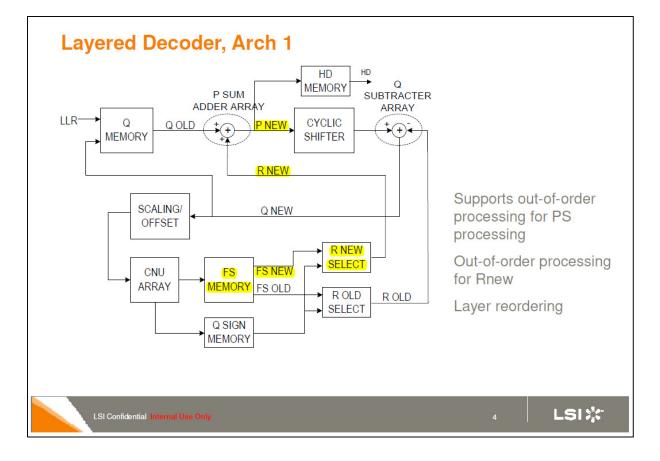

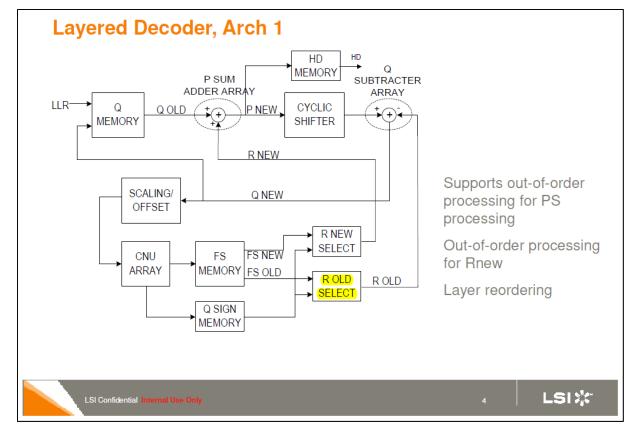

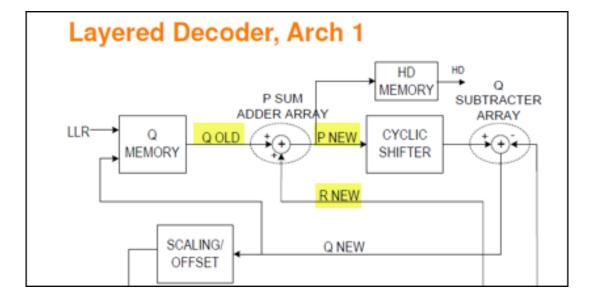

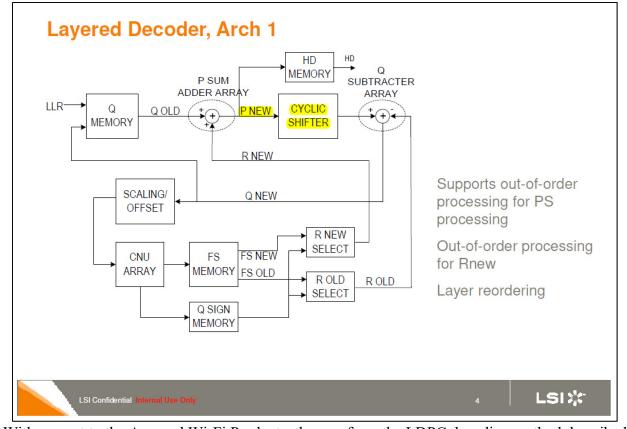

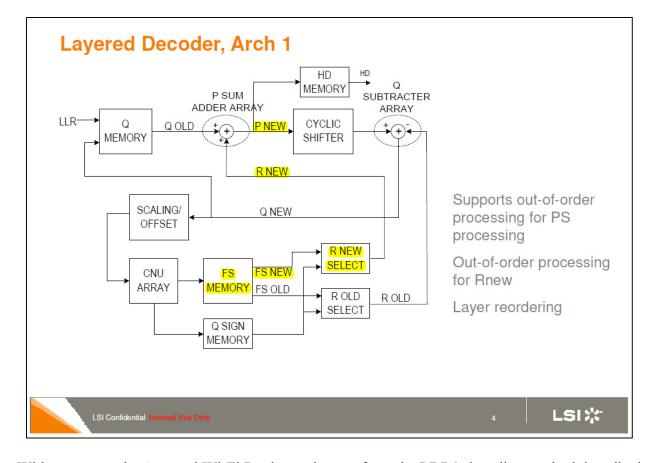

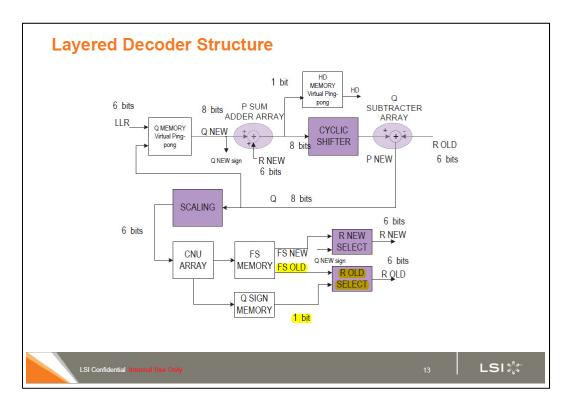

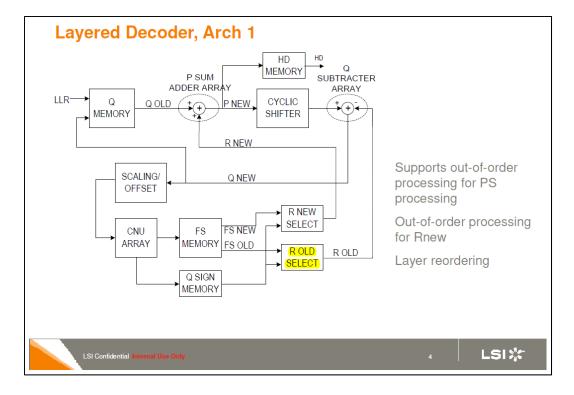

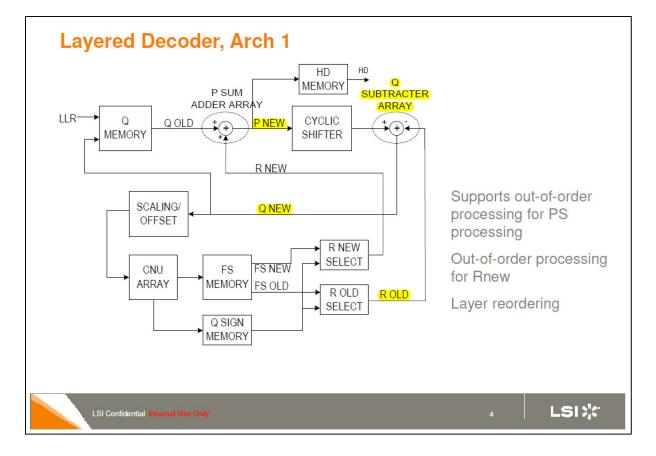

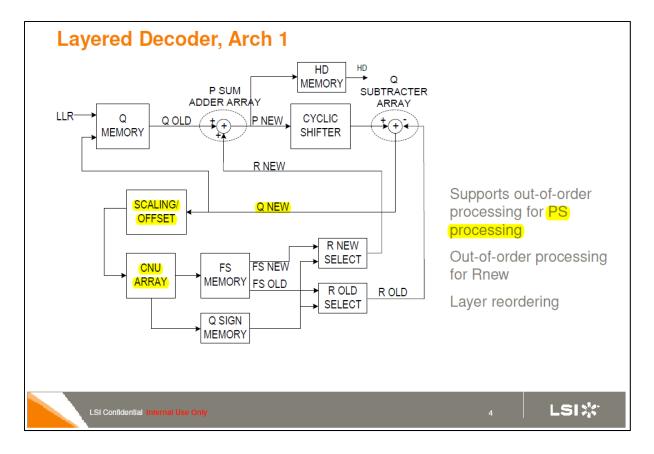

130. The layered decoder architecture of the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products is identical in relevant respects to what is set forth in the '023 Patent.

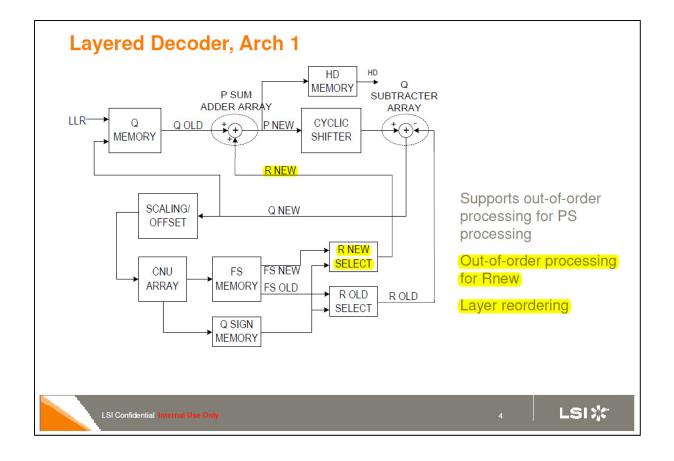

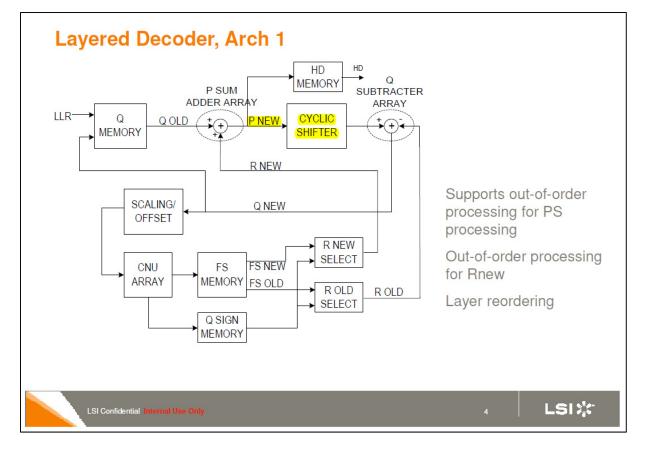

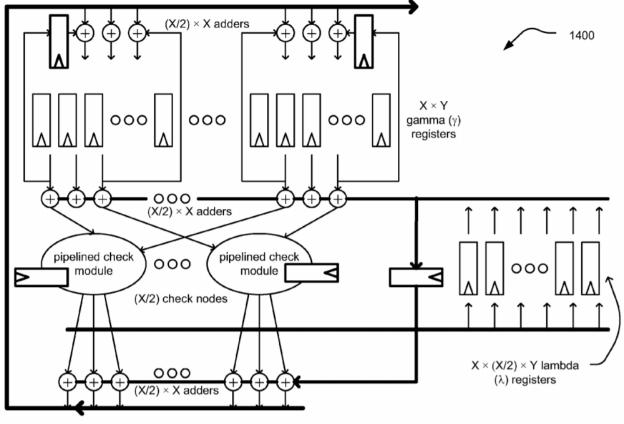

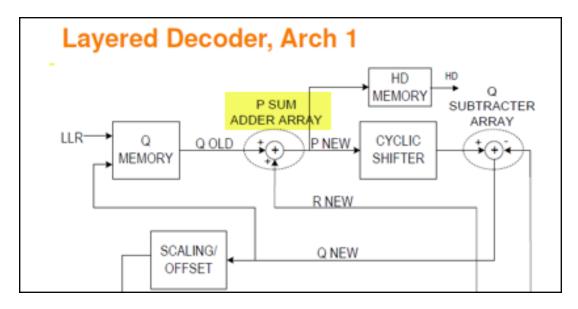

# **'023 Patent at FIG. 12**

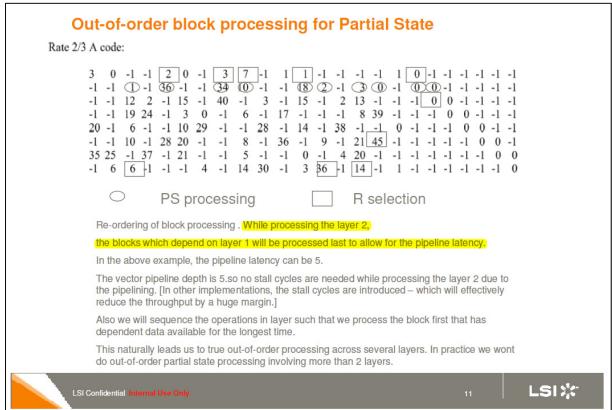

# **Layered Decoder Presentation at 4**

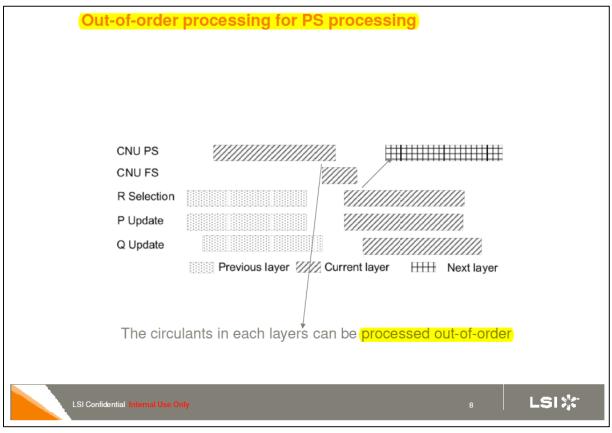

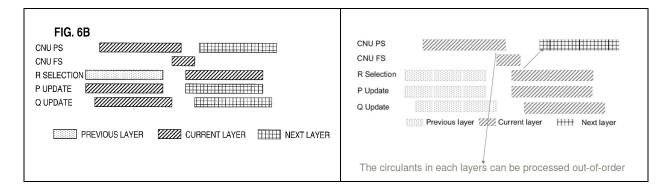

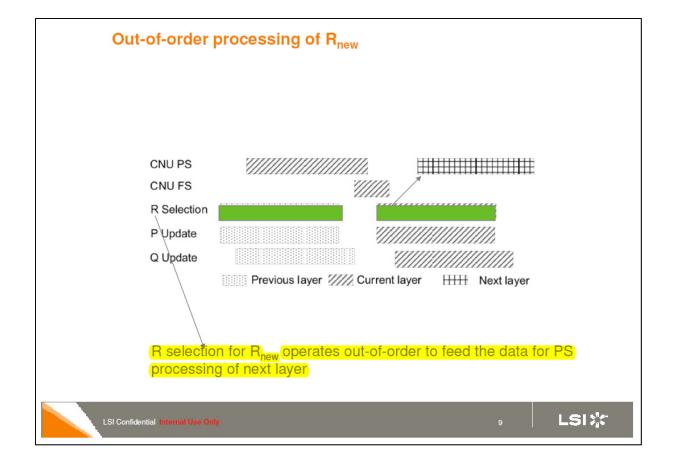

131. The pipeline architecture of the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products is similar to what is set forth in the '023 Patent.

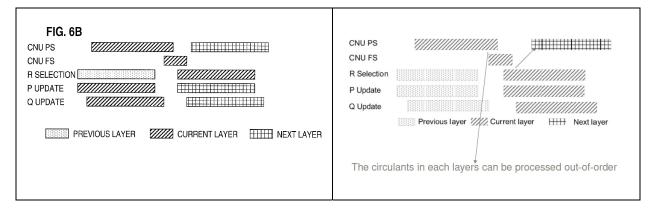

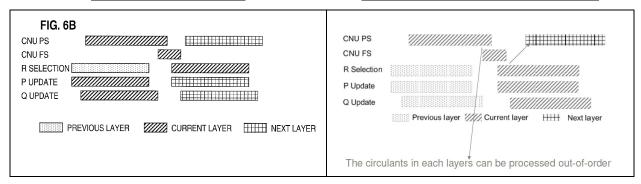

'023 Patent at FIG. 6B

**Layered Decoder Presentation at 8**

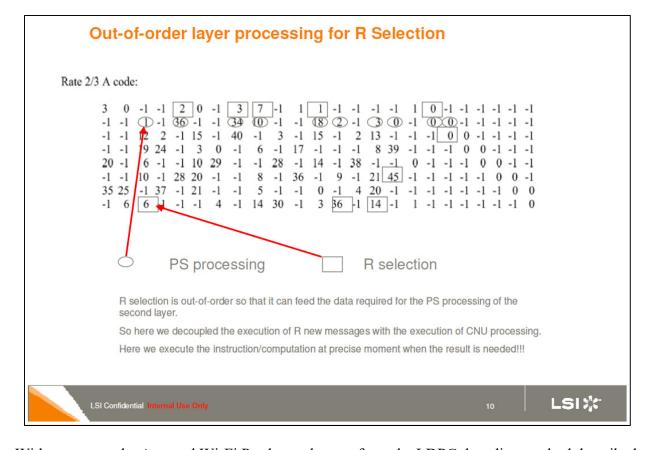

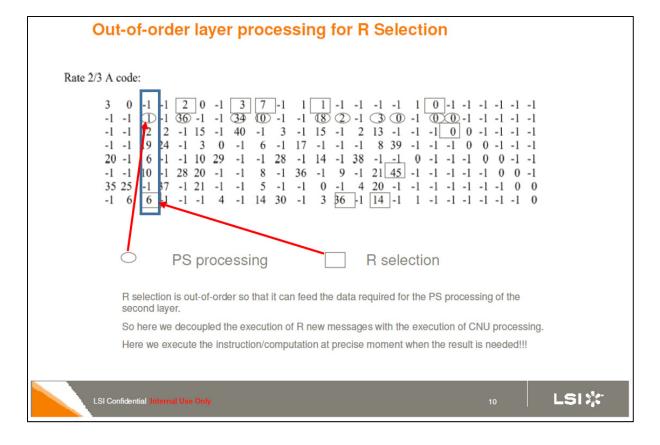

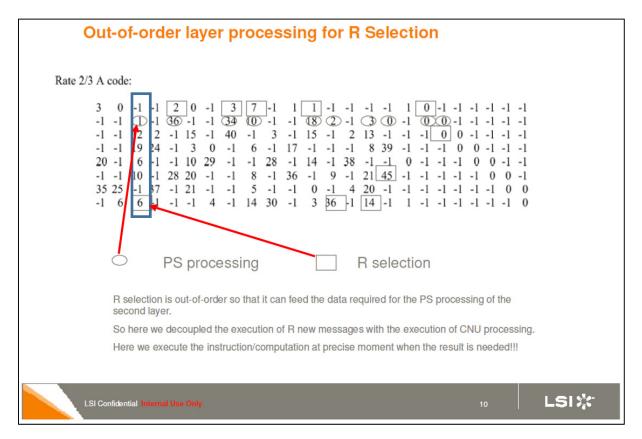

132. The exemplary Rate 2/3 A code of the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products is identical to what is set forth in the '023 Patent.

**'023 Patent at FIG. 11**

**Layered Decoder Presentation at 10**

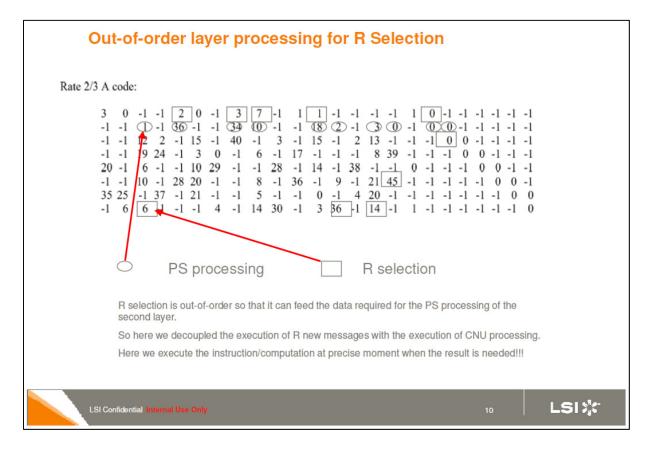

133. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products schedule computation of R messages for a first non-zero block and computation of P messages and Q messages for a second non-zero block. For example, the Layered Decoder Presentation discloses that the computation of the R messages ("R

SELECTION") are for a first non-zero block and the computation of the P messages and the Q messages are for a second non-zero block.

134. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products schedule computations such that R messages for the first non-zero block are generated while processing the second non-zero block, based on a determination of need for the R messages for the computation of P and Q messages for the second non-zero block. For example, the Layered Decoder Presentation discloses that the R selection is out-of-order so that it can feed the data required for the P and Q message computation of the second layer.

| Out-of-order layer processing for R Selection                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rate 2/3 A code:                                                                                                                                                                                                                                                                                      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                  |

| PS processing     R selection                                                                                                                                                                                                                                                                         |

| R selection is out-of-order so that it can feed the data required for the PS processing of the second layer.  So here we decoupled the execution of R new messages with the execution of CNU processing.  Here we execute the instruction/computation at precise moment when the result is needed!!!) |

| LSI Confidential Internal Use Only                                                                                                                                                                                                                                                                    |

135. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products include wherein the first non-zero block and the second non-zero block are in a same column of the matrix. For example, the Layered Decoder Presentation discloses a matrix wherein the first non-zero block and the second non-zero block are in a same column.

- 136. Claim 18 of the '023 Patent recites as follows:

- 18. A method for decoding a low density parity check code, comprising:

processing blocks of a low density parity check ("LDPC") matrix out of order; and

scheduling computation of R messages for a first non-zero block and computation of P messages and Q messages for a second non-zero block such that R messages for the first non-zero block are generated while processing the second non-zero block based on a determination of need for the R messages for the computation of P and Q messages for the second non-zero block;

wherein the first non-zero block and the second non-zero block are in a same column of the matrix.

137. On information and belief, the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products satisfy each and every limitation of Claim 18. The Accused Hard Disk Controller Products, the Accused SandForce

Products, and the Accused Densbits Products decode a low density parity check code. *See* ¶¶ 112, 113, *supra*.

- 138. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products process blocks of a LDPC matrix out of order. *See* ¶¶ 112, 115, *supra*.

- 139. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products schedule computation of R messages for a first non-zero block and computation of P messages and Q messages for a second non-zero block. *See* ¶¶ 112, 119, *supra*.

- 140. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products schedule computations such that R messages for the first non-zero block are generated while processing the second non-zero block based on a determination of need for the R messages for the computation of P and Q messages for the second non-zero block. *See* ¶¶ 112, 119-20, *supra*.

- 141. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products schedule computations wherein the first non-zero block and the second non-zero block are in a same column of the matrix. *See* ¶ 112, 121, *supra*.

- 142. In view of the foregoing, the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products directly infringe at least Claims 1-30 of the '023 Patent at least through Defendants' and/or the Broadcom Predecessor Entities' sale, offer for sale, importation, use, and/or testing of the Accused Products.

- 143. On information and belief, Defendants and/or the Broadcom Predecessor Entities have taken active steps to induce infringement by others of at least Claims 1-30 of the '023

Patent in violation of 35 U.S.C. §271(b), including, for example, by (a) inducing manufacturers to practice the claimed inventions when testing the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products, and (b) inducing end users to practice the claimed inventions when using the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products. Such active steps include, but are not limited to, selling Accused Hard Disk Controller Products, Accused SandForce Products, and Accused Densbits Products with the knowledge and intent that the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products will be operated by such manufacturers and their customers in accordance with the claimed inventions, as set forth in the Section "EXAMPLES OF DIRECT AND INDIRECT INFRINGEMENT" below.

144. On information and belief, Defendants and/or the Broadcom Predecessor Entities have known or should have known that such activities induce others to directly infringe one or more of at least Claims 1-30 of the '023 Patent. For example, Defendants and/or the Broadcom Predecessor Entities should have known that their actions induced others to directly infringe as of the date it became aware of the issuance of the '023 Patent on or about April 9, 2013, and in any event no later than the date it was advised of the issuance of the '023 Patent by Dr. Gunnam on January 31, 2014. Defendants and/or the Broadcom Predecessor Entities were further informed that the technology in the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products infringed the '023 Patent, and Defendants and/or the Broadcom Predecessor Entities have knowingly and purposefully continued to exploit the patented technology, despite knowing that it was covered by the '023

Case 1:18-cv-01966-SB Document 249 Filed 05/04/22 Page 41 of 157 PageID #: 10064

HIGHLY CONFIDENTIAL SUBJECT TO PROTECTIVE ORDER

Patent, as set forth in the Section "EXAMPLES OF DIRECT AND INDIRECT INFRINGEMENT" below.

- On information and belief, Defendants and/or the Broadcom Predecessor Entities 145. have contributed to the infringement of at least Claims 1-30 of the '023 Patent by others, including consumer/end-user use of the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products, in violation of 35 U.S.C. § 271(c). Acts by Defendants and/or the Broadcom Predecessor Entities that have contributed to the infringement of others include, but are not limited to, the sale, offer for sale, and/or import by Defendants of the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products. Such Accused Hard Disk Controller Products, Accused SandForce Products, and Accused Densbits Products are especially made for or adapted for use to infringe, and are not a staple article of commerce and are not suitable for substantial noninfringing use. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products are apparatuses for use in practicing the inventions patented in Claims 1-30 of the '023 Patent, and are at least a material part of those claimed inventions, as set forth in the Section "EXAMPLES OF DIRECT AND INDIRECT INFRINGEMENT" below.

- 146. As also described above, Defendants and/or the Broadcom Predecessor Entities have, on information and belief, been on notice of the '023 Patent since it issued on April 9, 2013 and in any event were on notice as of no later than January 31, 2014.

- 147. In addition, Defendants and/or the Broadcom Predecessor Entities have been on notice since the filing and/or service of Plaintiff's original Complaint. (*See* D.I. 1, 5) Defendants have further been aware that use of the Accused Hard Disk Controller Products, the Accused

SandForce Products, and the Accused Densbits Products necessarily practice the inventions in Claims 1-30 of the '023 Patent.

- 148. The Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products are especially made for or adapted for use to infringe, and are not a staple article of commerce, and are not suitable for substantial non-infringing use. By way of example, the use of the LDPC decoders included in the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products is necessary to use the accused products for their intended purpose (decoding data from a hard disk drive, solid state drive, or wireless digital transmission), and the LDPC decoders necessarily practice the claimed inventions when they decode data. Accordingly, the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products do not have a substantial use that does not entail practicing the claimed inventions. On information and belief, the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products cannot be used but to infringe the '023 Patent.

- 149. Despite Defendants' and/or the Broadcom Predecessor Entities' knowledge and notice of the '023 Patent and their ongoing infringement, Defendants and/or the Broadcom Predecessor Entities have continued to manufacture, use, sell, offer for sale, and/or import the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products in a manner that willfully infringes the '023 Patent, and on information and belief, continue to sell and/or offer for sale the Accused Hard Disk Controller Products, the Accused SandForce Products, and the Accused Densbits Products to the United States market. On information and belief, nearly all of Dr. Gunnam's work, *inter alia*, at LSI was centered on the TAMUS' '320 provisional application. On information and belief, LSI recognized its

competitive disadvantage from not having acquired the rights to the Patents-in-Suit for itself, and embarked on a course of action where it filed and prosecuted numerous patents, based on Dr. Gunnam's work concerning the TAMUS '320 provisional application.

See https://www.google.com/search?tbm=pts&ei=lR4QXM-

.+No.+12%2F113%2C729+filed+on+May+1%2C+2008&gs\_l=psy-

ab.3...95601.99862.0.100208.3.3.0.0.0.0.128.258.2j1.3.0....0...1c.1.64.psy-

ab..0.0.0....0.OmH6jRmYHJo; see also

https://www.google.com/search?tbm=pts&ei=jB4QXODdHdC60PEP0qC4-

<u>A4&q=Ser.+No.+12%2F113%2C755+filed+on+May+1%2C+2008&oq=Ser.+No.+12%2F113%</u>2C755+filed+on+May+1%2C+2008&gs\_l=psy-

ab.3...7529.7728.0.8111.2.2.0.0.0.0.81.149.2.2.0....0...1c.1.64.psy-ab..0.0.0....0.UBEXLdczJgA.

On information and belief, LSI filed and prosecuted these patents despite Dr. Gunnam's repeated requests to LSI management for LSI to obtain a license for the TAMUS intellectual property. Defendants' and/or the Broadcom Predecessor Entities' infringement of the '023 Patent has thus been willful, as set forth above. Defendants and/or the Broadcom Predecessor Entities lacked a justifiable belief that they do not infringe the '023 Patent, or that the '023 Patent is invalid or unenforceable, and have acted recklessly in their infringing activity, justifying an increase in the damages to be awarded to Plaintiff up to three times the amount found or assessed, in accordance with 35 U.S.C. § 284.

150. On information and belief, Defendants and/or the Broadcom Predecessor Entities have had actual or constructive knowledge of the '023 Patent since at least April 9, 2013, and in any event no later than January 31, 2014.

- 151. Defendants and/or the Broadcom Predecessor Entities further have had knowledge of the '023 Patent at least as early as the filing and/or service of the original Complaint. (See D.I. 1, 5) Defendants and/or the Broadcom Predecessor Entities know or should know as of the date of filing and/or service of Plaintiff's original Complaint that their actions induced others to directly infringe the '023 Patent and contributed to infringement of the '023 Patent. (See id.)

- 152. This case is rendered an exceptional case at least in light of Defendants' and/or the Broadcom Predecessor Entities' willful infringement of the '023 Patent, justifying an award to Plaintiff of its reasonable attorney fees, in accordance with 35 U.S.C. § 285.

- 153. Plaintiff has no adequate remedy at law for Defendants' and/or the Broadcom Predecessor Entities' acts of infringement. As a direct and proximate result of Defendants' and/or the Broadcom Predecessor Entities' acts of infringement, Plaintiff has suffered and continues to suffer damages and irreparable harm. Unless Defendants' and/or the Broadcom Predecessor Entities' acts of infringement are enjoined by this Court, Plaintiff will continue to be damaged and irreparably harmed.

- 154. Defendants' and/or the Broadcom Predecessor Entities' infringement of the '023 Patent have damaged and continue to damage Plaintiff in an amount yet to be determined, of at least a reasonable royalty and/or lost profits that Plaintiff would have made but for Defendants' and/or the Broadcom Predecessor Entities' infringement acts.

# COUNT II (Infringement under 35 U.S.C. § 271 of U.S. Patent No. 8,555,140)

- 155. Plaintiff repeats and re-alleges the paragraphs above as if fully set forth herein.

- 156. The '140 Patent is valid, enforceable, and was duly issued on October 8, 2013 in full compliance with Title 35 of the United States Code.

- 157. On information and belief, in violation of 35 U.S.C. § 271, Defendants and/or the Broadcom Predecessor Entities have infringed, contributed to the infringement of, and/or induced others to infringe the '140 Patent, either literally or under the doctrine of equivalents, by, among other things, making, using, offering for sale, selling, selling infringing products abroad with knowledge and intent that the infringing products be imported into the United States by others, and/or importing into the United States unlicensed systems and/or products in a manner that infringes at least Claims 7-12 and 18-22 of the '140 Patent.