# UNITED STATES DISTRICT COURT FOR THE WESTERN DISTRICT OF TEXAS WACO DIVISION

INTELLECTUAL VENTURES I LLC and INTELLECTUAL VENTURES II LLC,

Civil Action No. 6:23-CV-0068-ADA

Plaintiff,

v.

JURY TRIAL DEMANDED

LENOVO GROUP LIMITED,

Defendant.

# FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT

Plaintiffs, Intellectual Ventures I LLC ("Intellectual Ventures I") Intellectual Ventures II LLC ("Intellectual Ventures II") (together "IV"), for its complaint against Defendant Lenovo Group Limited ("LGL") hereby allege:

# THE PARTIES

1. Intellectual Ventures I is a Delaware limited liability company having its principal place of business located at 3150 139<sup>th</sup> Avenue SE, Bellevue, Washington 98005.

2. Intellectual Ventures II is a Delaware limited liability company having its principal place of business located at 3150 139<sup>th</sup> Avenue SE, Bellevue, Washington 98005.

3. Upon information and belief, LGL is a foreign corporation organized and existing under the laws of China, with its principal place of business located a No. 6 Chuang Ye Road, Haidian District, Shangdi Information Industry Base, Beijing, 10085, China and may be served pursuant to the provisions of the Hague Convention. Upon information and belief, LGL also has a principal place of business located at Lincoln House, 23<sup>rd</sup> Floor, Taikoo Place, 979 King's Road, Quarry Bay, Hong Kong, S.A.R.

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 2 of 125

4. Upon information and belief, LGL is the parent company of a multinational conglomerate that operates under the name "Lenovo" and refers to itself and its subsidiaries as the "Group." LGL purports to be a US\$60 billion Fortune Global 500 company serving customers in 180 markets around the world, including within the United States where it is a leading manufacturer and seller of laptop computers, desktop computers, smartphones, and tablets. Upon information and belief, each member of the "Group" is directly or indirectly a wholly owned subsidiary of LGL, which is the parent corporation or otherwise controls each member. These entities are collectively referred to herein as "Lenovo".

5. Upon information and belief, LGL and each member of the "Group" are part of the same corporate structure and distribution chain and have acted in concert with respect to the facts alleged herein such that any act of LGL is attributable to every other member and vice versa.

# NATURE OF THE ACTION, JURISDICTION, AND VENUE

6. IV brings this action for patent infringement pursuant to 35 U.S.C. § 271, *et seq*. This Court has subject matter jurisdiction under 28 U.S.C. §§ 1331 and 1338(a).

7. This Court has personal jurisdiction over LGL. LGL conducts business and has committed acts of direct and indirect infringement in this District, the State of Texas, and elsewhere in the United States. Moreover, LGL actively directs its activities to customers located in the State of Texas and this District.

8. For example, on information and belief Lenovo Group members, acting at the direction of LGL, sell within this District, the State of Texas and elsewhere in the United States products accused of infringement in this case.

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 3 of 125

9. Venue is proper in this District under 28 U.S.C. § 1391(c) because LGL is a foreign corporation. In addition, LGL has committed acts of patent infringement in this District and IV has suffered harm in this District.

# FACTUAL BACKGROUND

10. Intellectual Ventures Management, LLC ("Intellectual Ventures") was founded in 2000. Intellectual Ventures fosters inventions and facilitates the filing of patent applications for those inventions; collaborates with others to develop and patent inventions; and acquires and licenses patents from individual inventors, universities, corporations, and other institutions. A significant aspect of Intellectual Ventures' business is managing the plaintiffs in this case, Intellectual Ventures I and Intellectual Ventures II.

11. One founder of Intellectual Ventures is Nathan Myhrvold, who worked at Microsoft from 1986 until 2000 in a variety of executive positions, culminating in his appointment as the company's first Chief Technology Officer ("CTO") in 1996. While at Microsoft, Dr. Myhrvold founded Microsoft Research in 1991 and was one of the world's foremost software experts. Between 1986 and 2000, Microsoft became the world's largest technology company.

12. Under Dr. Myhrvold's leadership, Intellectual Ventures acquired thousands of patents covering many important inventions of the Internet era, including many pertaining to the networked computers that comprise the Internet. Many of these inventions coincided with Dr. Myhrvold's successful tenure at Microsoft.

#### **Remote Network Device Management**

13. One area of particular and continuing importance in the Internet era is the remote management of networked devices. Device security management specifically, which is the management of devices with the goal of protecting them from harm and unauthorized use, is

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 4 of 125

becoming more important with every passing year. Secure management of remotely located devices is essential for reliable, dependable, and highly available systems that are resilient to attack, responsive to customers' needs and affordable to operate.

14. Historically, the combination of remote management and secure management were not coextensive. As a result, networked devices were traditionally managed by physically isolating them, either individually or in small groups, from other parts of the network. An administrator for example, would typically co-locate several devices and limit physical access of those devices to select authorized employees. Any management of the devices would have to be performed while one of those employees was physically present with the devices. Such solutions became costprohibitive, in terms of both time and personnel, as networks grew and expanded over geographically dispersed areas.

15. When it became no longer feasible to have an administrator present at the location of every device in the network, many network administrators began allowing authorized employees to perform remote maintenance on networked devices. Enabling a device for remote management avoids the cost and delay of dispatching a person to the remote site, however, could potentially allow a determined intruder to utilize the remote access means for an attack if the remote management solution is not highly secure.

16. Remote management of network devices was performed over either "in-band" or "out-of-band" network connections. "In-band" management occurred over the same network that user data traversed, meaning that management data and user data flowed over the same network. "Out-of-band" management occurred using a means other than the network utilized for user data. Both "in-band" and "out-of-band" management did not have the appropriate level of security to prevent against potential attacks.

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 5 of 125

17. A disadvantage of out-of-band management arose because it bypassed several important network security systems that were employed by user data networks. These systems included virtual private networks (VPNs), firewalls, access control lists (ACLs) and authentication servers. As a result, out-of-band management made the network and its connected devices more vulnerable, in some ways, against malicious attacks.

18. In-band management also has its challenges. One is the comingling of user data and management data. Comingling of user and management data provides an opportunity for rogues to compromise management data from within the network itself, particularly if the administrator failed to implement a robust authentication scheme for other authorized administrators or employees. VPNs existed, which protected management data while it flowed over the in-band network, but even with VPNs, there was commingling of user data and management data in the device itself. In another example, existing authentication schemes, such as placing sole reliance on HTTPS authentication, were not always as robust as they needed to be. Problems such as comingling and authentication could be addressed by adding additional devices that implemented these features, which would be placed within or near the managed device. But such other devices would add cost and occupy extra space.

19. To overcome these obstacles, Engedi Technologies ("Engedi"), an early developer of network security solutions focused on secure remote management technology, and the original assignee of the patents-in-suit, developed the Secure Remote Management System (SRM). SRM provided an authenticated and encrypted secure tunnel between an SRM appliance co-located with a managed device, and a centralized network management center. These secure

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 6 of 125

network tunnels provided multi-pathed communication capability for the remote management of network devices.<sup>1</sup>

20. SRM provided in-band and out-of-band secured network connections from the SRM appliance to the network management center, thus making available multiple and diverse robust paths for reporting status information to monitoring stations or allowing for remote configuration of the device. Compared to prior designs, this diverse and robust multi-path capability was a significant advantage.

21. Defendant makes, uses, and sells servers and network devices that include embedded secure management processors marketed under the Integrated Management Module II ("IMM2") and XClarity Controller ("XCC") brands (collectively "accused processors"), as well as purpose-built software that supports operation of the accused processors. These accused processors and purpose-built software are embedded in Defendant's ThinkSystem, System x, and Flex System x, and BladeCenter servers, among others, as well as other solutions based on the aforementioned servers.

# Microprocessor Clocking

22. Another area of particular and continuing importance in the computer era is that, as microprocessors grow in frequency and dimension, microprocessor clocks have become increasingly limited by wire delays. For example, the Pentium III microprocessor broke the 1 GHz barrier in 2000, and speeds have continued to increase ever since. At the same time, due to issues of reliability and performance, wire dimensions have been scaled in successive process generations

<sup>1</sup> For instance as described by Engedi at: <u>https://web.archive.org/web/20050309054746/http://www.engedi.net/focus.htm</u> and <u>https://web.archive.org/web/20050130064915/http://www.engedi.net/documents/SecureRemote</u> <u>Management\_ver2p5.pdf</u>

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 7 of 125

more conservatively than transistor dimensions. The result of these frequency and dimensional trends is that microprocessor clock speeds became increasingly limited by wire delays, so much so that some of the subsequent microprocessors, e.g., the Pentium IV, had pipeline stages solely dedicated to moving clock signals across the chip.

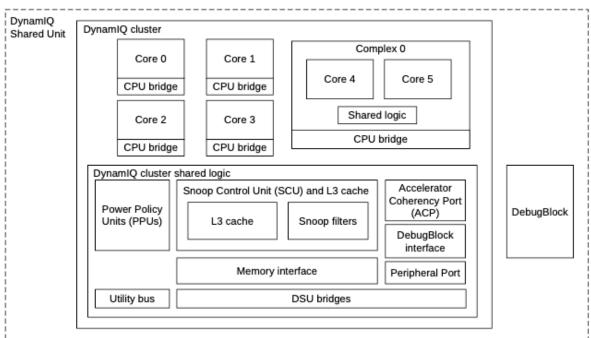

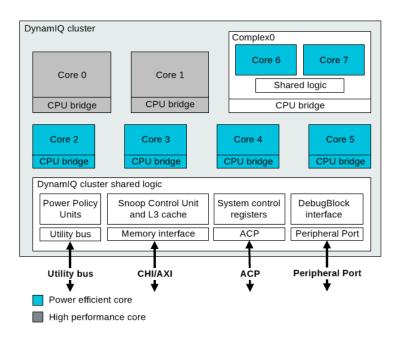

23. Furthermore, a growing challenge has been to distribute the clock across a progressively larger die to increasing numbers of latches while meeting a decreasing clock skew budget. Researchers concluded that in order to continue the pace of clock frequency increases, microprocessor designers would be forced to abandon singly clocked globally synchronous systems in favor of some form of asynchrony.

24. Although purely asynchronous systems have the potential for higher performance and lower power compared to their synchronous counterparts, major corporations in the early 2000s were initially reluctant to fully migrate to asynchronous design methodologies. Two major reasons for this reluctance were the immaturity of asynchronous design tools relative to those in the synchronous domain, and the cost and risk of moving away from the mature design infrastructures rooted in synchronous systems that have been successfully used to create many generations of microprocessor products.

25. To address the issues identified above, David H. Albonesi led a team of professors and graduate students at the University of Rochester in developing a multiple clock domain microarchitecture that uses a globally asynchronous, locally synchronous clocking style.

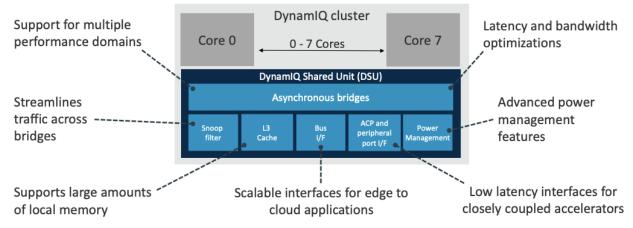

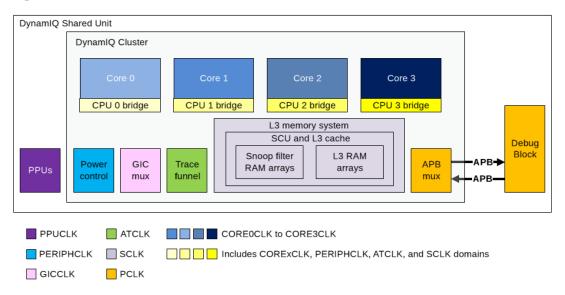

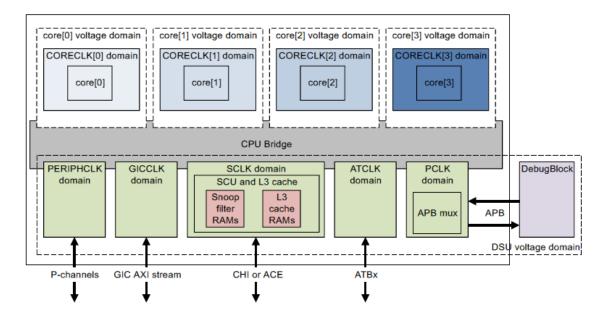

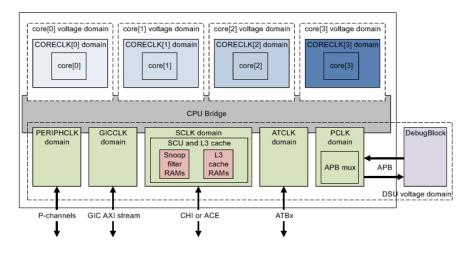

26. Defendant makes, uses, and sells devices that include embedded ARM Cortex-Axx processors, as well as purpose-built software that supports operation of those processors.

# **Cyclic Diversity**

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 8 of 125

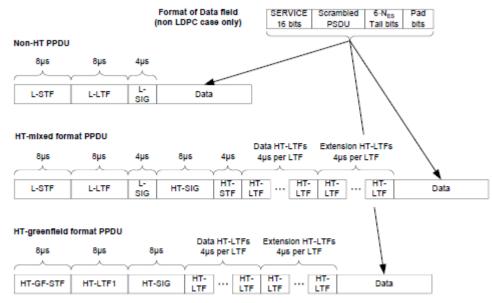

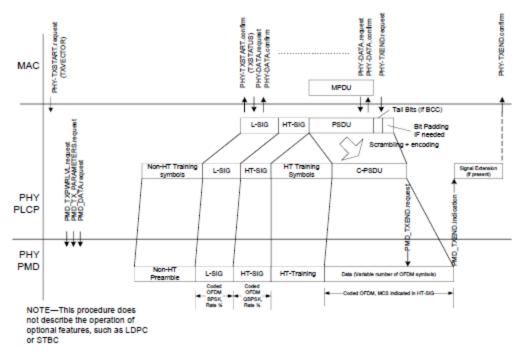

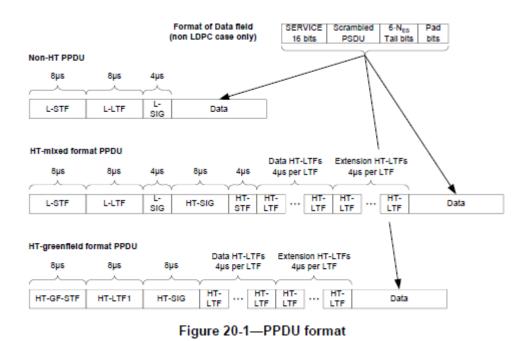

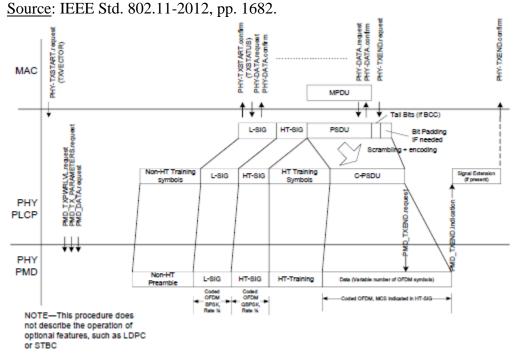

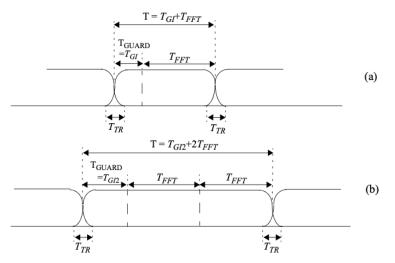

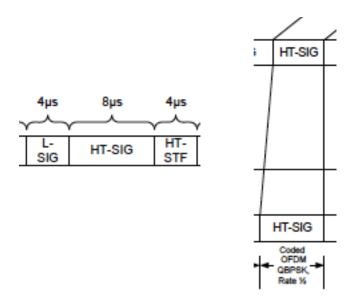

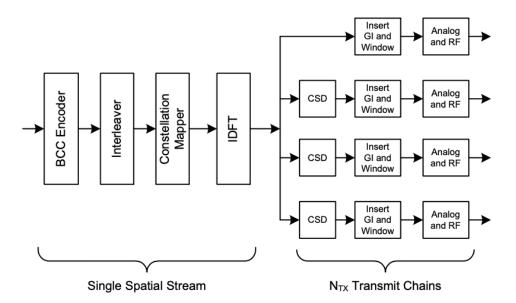

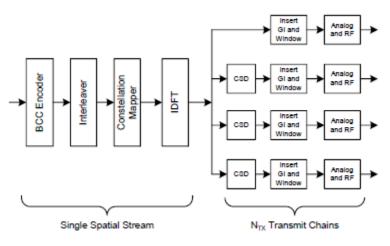

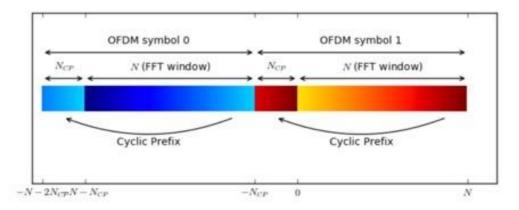

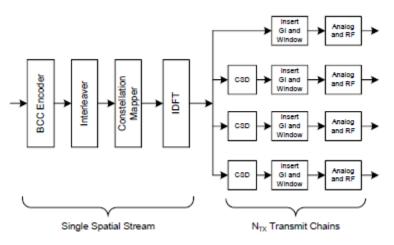

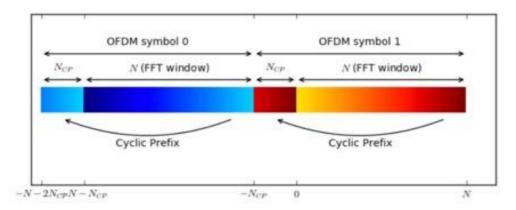

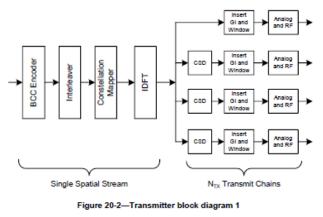

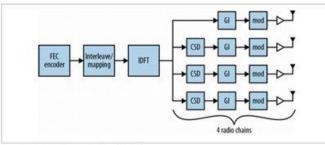

27. A further area of importance in today's computing environments is that as wireless communications systems are widely deployed to provide various types of communications, demand for increased data rates has skyrocketed. This has led wireless system providers to develop new techniques for increasing data rates within the limited available radio frequency (RF) spectrum. One of these advancements has been the use of orthogonal frequency division multiplexing (OFDM) transmission. In OFDM transmissions, a radio channel is divided into a large number of closely spaced subchannels, an outgoing bitstream representing data to be transmitted is divided into multiple sub-bitstreams, and each sub-bitstream is transmitted over a subchannel in parallel with other sub-bitstreams that are each transmitted over their respective subchannels. Each such sub-bitstream is comprised of a series of symbols, that is, a waveform of the communication channel that persists for a fixed period of time, and from which data can be extracted by taking samples (i.e., measuring segments) of that waveform. Each of the symbols is separated by a guard interval (a gap in time between successive symbols that provides a buffer making transmission channels more resilient against the effects of a multipath propagation). The main advantages of OFDM is its ability to cope with severe channel conditions (e.g., signal fading, echoes, and interference).

28. As technology continued to advance, demand for increased speed and reduced interference resulted in the implementation of further improvements such as using multiple antennas in a single device, sometimes referred to as multiple input, multiple output (MIMO), which enables simultaneous or substantially simultaneous transmission of multiple bitstreams/sub-bitstreams in the same RF spectrum. When combined with OFDM, MIMO increases speed and improves reliability, however, it also introduces challenges, particularly when a multi-antenna MIMO enabled transmitter is communicating with a single antenna single input, single output

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 9 of 125

(SISO), receiver device. For example, signals transmitted from the MIMO transmitter may follow direct paths and multipaths to the SIS receiver, which can result in constructive interference (when multiple signals interact with one another to increase their amplitudes) or destructive interference (when multiple signals interact with one another to decrease their amplitudes), thus increasing packet error rates and causing other unwanted behavior that degraded the network quality.

29. One way that prior art systems addressed these inefficiencies was by implementing linear diversity schemes in which the transmission of one signal from a MIMO system is delayed relative to another signal from the MIMO system. Linear diversity schemes tend to reduce constructive and destructive interference by temporally decorrelating the transmissions of two signals, but they resulted in other problems such as one of the signals occupying the other's guard interval.

30. To address the inefficiencies set out above, cyclic diversity schemes were implemented (e.g., the cyclic-delay diversity scheme). In the cyclic-delay diversity scheme each of two or more transmitters send the same data in a respective stream of symbols, but cyclically offset one spatial stream vis-a-vis the other by a defined number of samples resulting in a circular shift of all the samples in a particular symbol (or part thereof). By introducing a relatively small cyclic delay to a first transmitted MIMO signal relative to a second transmitted MIMO signals, those of skill in the art were able to substantially reduce the problems set out above. But, by introducing a small cyclic delay between the first and second MIMO signals, upon receipt sometimes the receiver would be unable to determine whether the cyclic delay was intentional or caused by environmental or other factors. This inability in turn led to the receiver incorrectly assuming an attempt by the transmitter to beamform, which occurs when antennas are intentionally electronically steered to adjust the phase and amplitude of a transmitted signal at each antenna,

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 10 of 125

such that the signals combine constructively in the desired direction and destructively in other directions. That is, small cyclic delays were causing unintentional beamforming.

31. To address these and other problems in the art Mark Webster and Michael Seals, at the time engineers for Conexant Systems, developed improved systems and methods of wireless communication, which include, but are not limited to, an improved signal transmitting system capable of manipulating OFDM data packets and data streams using a cyclic diversity scheme based on cyclic advancement rather than cyclic delay, thereby improving packet reception performance and reducing packet error rates, among other benefits.

32. Defendant makes, uses, and sells devices that include embedded wireless 802.11n, 802.11ac and 802.11ax compliant chipsets configured to use MIMO and OFDMA with a cyclic shift diversity feature compliant with the respective 802.11 standard, such as the Motorola edge + smartphones.

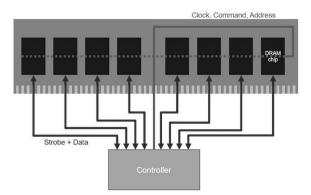

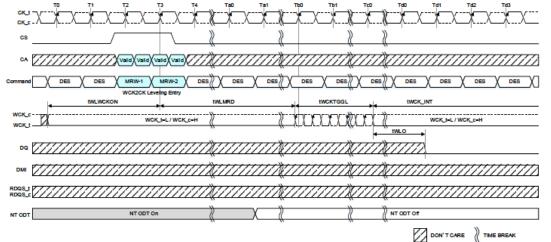

# **Intra-cycle Timing Relationships in Integrated Circuits**

33. An additional area of continued importance is the design and fabrication of highperformance signaling mechanisms for digital integrated circuit devices. For example, with respect to high-performance memory integrated circuit devices (e.g., Double Data Rate ("DDR")) memory, ensuring the reliability in the design and fabrication of high-performance memory modules had become problematic for many OEMs by 2003. The slower memory bus speeds prior to 2003 had allowed significant specification margins in the design and fabrication of a given memory module. As memory bus speeds began approaching those supported by the Double Data Rate 2 ("DDR2") standard in 2003 however, the industry recognized that their designs required ever more exacting control of critical timing specifications, and design parameters had to be even more strictly maintained to keep the entire system in balance. A stable DDR memory module had

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 11 of 125

to provide reliability, speed, and proper timing to ensure the overall system (e.g., CPU, bridge components, peripheral busses, etc.) operated at peak performance.

34. Transmeta Corporation ("Transmeta"), a fabless semiconductor company, was founded in 1995 to help address problems such as the ones identified above. Among other things, Transmeta developed low power x86 compatible microprocessors based on a very long instruction word ("VLIW") core and a software layer called Code Morphing Software. Transmeta's initial public offering on November 7, 2000, was the last of the great high-tech IPOs up through 2000, with its opening-day performance not being surpassed until Google Inc.'s IPO in 2004.

35. Transmeta launched its first product, the Crusoe processor, in January 2000, and its second processor, the Efficeon, in October 2003.

36. In October 2006, Transmeta sued Intel Corporation for infringement of ten Transmeta patents covering computer architecture and power efficiency technologies by making, using and selling a variety of microprocessors, including Intel's Pentium III, Pentium 4, Pentium M, Core and Core 2 product lines. One year later, in October 2007, Transmeta and Intel settled the case, with Intel agreeing to pay Transmeta \$150,000,000 up front and an additional \$20,000,000 per year for five years.

37. Transmeta was acquired by Novafor Inc. in January 2009 for \$255,600,000. Intellectual Ventures acquired much of the patent portfolio—including one of the asserted patents discussed below—the following month.

38. Defendant makes, uses, and sells devices that include mobile phones, laptop computers and tablet devices that include Qualcomm processors and LPDDR4, LPDDR4X or LPDDR5 memory.

# THE PATENTS-IN-SUIT

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 12 of 125

39. On January 29, 2008, the PTO issued United States Patent No. 7,325,140 ("the '140 patent"), titled SECURE MANAGEMENT ACCESS CONTROL FOR COMPUTERS, EMBEDDED AND CARD EMBODIMENT.

40. The '140 patent is valid and enforceable.

41. Intellectual Ventures II LLC is the owner and assignee of all rights, title, and interest in the '140 patent, including the rights to grant licenses, to exclude others, and to recover past damages for infringement of that patent.

42. The '140 patent is directed to a remote device management communication system including a secure management access controller embedded within and in direct communication with a managed networked device. The system includes at least one secure management access controller connected to one or more data buses, an out-of-band access connection for connecting network services or remote users with the secure management controller, at least one virtual management interface for connecting the network services or remote users with the secure management interface connection provides logical separation of management data from user data and utilizes user interfaces of the managed network element for the connection to the one or more network services or remote users.

43. On June 25, 2013, the PTO issued United States Patent No. 8,474,016 ("the '016 patent"), titled SECURE MANAGEMENT ACCESS CONTROL FOR COMPUTERS, EMBEDDED AND CARD EMBODIMENT.

44. The '016 patent is valid and enforceable.

45. Intellectual Ventures II LLC is the owner and assignee of all rights, title, and interest in the '016 patent, including the rights to grant licenses, to exclude others, and to recover past damages for infringement of that patent.

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 13 of 125

46. The '016 patent is directed to a computer network management apparatus and method for remotely and securely managing a networked device. The apparatus includes a processor configured to control one or more functions of a network device having a network interface, wherein the network device is configured to receive data requests and an encrypted form of management requests via the network interface, wherein the management requests are from a remote administrator; a first bus; a bus controller coupled to the processor via the first bus, wherein the bus controller is also coupled to a second bus of the network device that is distinct from the first bus; wherein the bus controller is configured to receive the encrypted form of the management requests to the processor via the first bus; wherein the processor is configured to decrypt the encrypted form of the management requests; wherein the network device includes a processor configured to facilitate operation of the network device; and wherein the processor of the apparatus is distinct from the processor included in the network device.

47. The inventions claimed in the '140 and '016 patents were conceived by Jeffrey Alan Carley during his time as CTO and Co-Founder of Engedi. As noted above, Engedi created a secure remote management system to meet the need for a cost saving, highly secure method to access and manage remotely located devices in a distributed network. The system had a particular focus on preventing malicious attacks from insiders and resiliency in the event of path failures. Mr. Carley was an integral part of Engedi's technology development, architecting and overseeing the entire process, including managing funding, vendor and partner relationships and intellectual property growth. He has over 25 years of experience in the computer networking industry with major strengths in hybrid cloud networking, network architecture design and implementation, and network security and management at companies such as AIS, Pearson, TEKsystems, HPE, Modis,

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 14 of 125

MCI and IBM. Mr. Carley also holds the National Security Agency (NSA) InfoSec Assessment Management Methodology (IAM) certification and is a member of the IEEE, the Computer Society of the IEEE, the Information Systems Security Association and the Center for Internet Security. He is currently a Cloud Infrastructure Consultant at Applied Information Sciences and resides in Colorado Springs, Colorado.

48. On August 8, 2006, the United States Patent and Trademark Office issued United States Patent No. 7,089,443 ("the '443 patent"), titled MULTIPLE CLOCK DOMAIN MICROPROCESSOR. The '443 patent is valid and enforceable.

49. Intellectual Ventures II LLC is the exclusive licensee of the '443 patent and has the right to sue and recover damages for any current or past infringement of the '443 patent.

50. The '443 patent is directed to a multiple clock domain ("MCD") microarchitecture. In an MCD microprocessor, each functional block operates with a separately generated clock, while synchronizing circuits ensure reliable inter-domain communication.

51. The inventions claimed in the '443 patent were conceived by David Albonesi, Greg Semeraro, Grigorios Magklis, Michael L. Scott, Rajeev Balasubramonian and Sandhya Dwarkadas at the University of Rochester. The first named inventor, Dr. Albonesi, is currently a full professor and the Associate Director of the School of Electrical and Computer Engineering at Cornell University, where he focuses on power-efficient computer architecture.

52. On November 24, 2009, the United States Patent and Trademark Office issued United States Patent No. 7,623,439 ("the '439 patent"), titled CYCLIC DIVERSITY SYSTEMS AND METHODS. The '439 patent is valid and enforceable.

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 15 of 125

53. Intellectual Ventures I LLC is the owner and assignee of all rights, title, and interest in the '439 patent, including the rights to grant licenses, to exclude others, and to recover past damages for infringement of that patent.

54. The '439 patent is directed to a system and method for transmitting OFDM signals from a multiple antenna transmitting device. The system is able to manipulate an OFDM signal using a cyclic advancement scheme whereby a portion of sampled symbol data from packets comprising the OFDM signal are shifted (advanced) into the guard interval of the packet relative to a first non-shifted version of the packet. The system and method then allow for the substantially simultaneous transmission of the respective packets from different antenna in the transmitting device, thereby allowing a receiver to more easily acquire and correlate the received data.

55. The inventions claimed in the '439 patent were conceived by Mark Webster and Michael Seals, both of whom were engineers at Conexant Systems, a well-known software developer and fabless semiconductor company specializing in developing technology for voice and audio processing. Mr. Webster is currently employed by L3Harris Technologies as a Senior Scientist, while Mr. Seals is a Principal Systems Engineer at Thales Group.

56. On January 12, 2010, the United States Patent and Trademark Office issued United States Patent No. 7,646,835 ("the '835 patent"), titled METHOD AND SYSTEM FOR AUTOMATICALLY CALIBRATING INTRA-CYCLE TIMING RELATIONSHIPS FOR SAMPLING SIGNALS FOR AN INTEGRATED CIRCUIT DEVICE. The '835 patent is valid and enforceable.

57. Intellectual Ventures II LLC is the owner and assignee of all rights, title, and interest in the '835 patent, including the rights to grant licenses, to exclude others, and to recover past damages for infringement of that patent.

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 16 of 125

58. The '835 patent is directed to the automatic calibration of intra-cycle timing relationships between command signals, data signals, and sampling signals for an integrated circuit device, including the generation of command signals to access an integrated circuit component; the accessing of data signals to convey data for the integrated circuit component; the accessing of sampling signals to control sampling of the data signals; and systematically altering a phase shift of the command signals, a phase shift of the data signals, and a phase shift of the sampling signals to determine a valid operation range of the integrated circuit device, wherein the valid operation range includes an optimal operation point for the integrated circuit device.

59. The inventions claimed in the '835 patent were conceived by Guillermo J. Rozas during his time at Transmeta Corporation.

#### COUNT I

(Defendant's Infringement of U.S. Patent No. 7,325,140)

60. The preceding paragraphs are reincorporated by reference as if fully set forth herein.

61. The '140 patent claims and teaches, *inter alia*, an improved way to provide secure remote management for devices by deeply embedding the necessary secure remote management hardware and software in the managed device itself. The inventions improved upon then-existing remote access/management security techniques by combining such hardware with a virtual management interface for logically separating user data from management data when using inband management techniques. They added critical features to in-band management such as enabling separation of management and user data when administrators used in-band management all the way up to the network port itself. They accomplished this by creating a virtual interface at the physical port that accepts management and user data to keep the two data types segregated from end to end, including within the managed device, and not just on the network. Furthermore,

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 17 of 125

this was accomplished without requiring adding more devices in or around the managed device by embedding the secure remote management hardware and software into the managed device itself. This realized significant costs savings for customers that otherwise would have had to add more devices that took up more space substantially increasing cost. Further security and redundancy improvements were provided by the establishment of a separate purpose-built network connection interface for the secure remote management of the device over an out-of-band connection.

62. More specifically, the claims of the '140 patent recite a remote device management communication system for securely controlling access to management applications and communications to and from said management applications on network devices in a distributed computer network. The system includes one or more network services, one or more secure management access controllers, and one or more managed network devices. Further, the system includes at least one secure management access controller connected to one or more data buses of the managed network device for communication of device management data, as well as an out-of-band access connection means for connecting one or more network services or remote users with the secure management access controller for management of the network device. In addition, the system includes at least one virtual management interface connection means for connecting said one or more network services controller, where the virtual management connection means provides logical separation of management data from user data and utilizes user interfaces of said managed network element for connecting said one or more network services or remote users with the secure management data from user data and utilizes user interfaces of said managed network element for connecting said one or more network services or remote users with the secure management data from user data and utilizes user interfaces of said managed network element for connecting said one or more network services or remote users with the secure management access controller.

63. The system covered by the asserted claims, therefore, differs markedly from the prior systems in use at the time of this invention, which lacked the claimed combination of the secure management access controller connected to a managed network device, an out-of-band

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 18 of 125

connection means for connecting one or more network services or remote users with the secure management access controller, and a virtual management interface connection means for providing logical separation of management data and user data and for utilizing user interfaces of the managed device to also connect one or more network services or remote users with the secure management access controller.

64. Defendant has directly infringed, and continues to directly infringe at least claim 1 of the '140 patent by making, using, testing, selling, offering for sale, and importing into the United States products and services covered by one or more claims of the '140 patent. Defendant's products and services that infringe the '140 patent include all products and services that use an IMM2 or XCC embedded processor, which include the System x, NeXtScale, Flex System, BladeCenter, and ThinkSystem servers series, and any chassis/enclosures such products may be housed in, as well as any other of Defendant's products and services, either alone or in combination, that operate in substantially the same manner (together, the "Accused '140 Products").

65. Claim 1 of the '140 patent is reproduced below:

1. A remote device management communication system for securely controlling access to management applications and communications to and from said management applications on network devices in a distributed computer network that includes one or more network services, one or more secure management access controllers, and one or more managed network devices, the remote device management system comprising:

at least one secure management access controller connected to one or more data bus of said managed network device for the communication of device management data;

an out-of-band access connection means for connecting said one or more network services or remote users with said secure management access controller for management of said network device; and at least one virtual management interface connection means for connecting said one or more network services or remote users with said secure management access controller;

wherein said virtual management interface connection means provides logical separation of management data from user data and utilizes user interfaces of said managed network element for connecting said one or more network services or remote users with said secure management access controller.

66. The Accused '140 Products each provide a remote device management communication system for securely controlling access to management applications and communications to and from said management applications on network devices in a distributed computer network that includes one or more network services, one or more secure management access controllers, and one or more managed network devices. As one example, the Accused '140 Products are network devices, modules and nodes capable of being configured in a distributed computer network, such as the Lenovo ThinkSystem SD650-N V2, ThinkSystem SN550 V2, and ThinkSystem SN550 (Xeon SP Gen 1) servers that support the XCC Standard, SXX Advanced and XCC Enterprise integrated service processors for controlling and securing remote management applications and services as well as communications regarding the same, as seen below:

# Lenovo XClarity Controller

Language: English The Lenovo XClarity Controller (XCC) is the next generation management controller for Lenovo ThinkSystem servers.

- Lenovo XClarity Controller with Intel Xeon SP (1st, 2nd Gen)

- Lenovo XClarity Controller with Intel Xeon SP (3rd Gen) and AMD EPYC (2nd, 3rd Gen)

- Lenovo XClarity Controller REST API reference

The following table lists the server models supported by LXCC Products:

| Lenovo XClarity Controller                                                                   | Server       | models    |

|----------------------------------------------------------------------------------------------|--------------|-----------|

| Lenovo XClarity Controller<br>with Intel Xeon SP (1st, 2nd<br>Gen)                           | • SD530      | • SR570   |

|                                                                                              | • SD650      | • SR590   |

|                                                                                              | • SE350      | • SR630   |

|                                                                                              | • SN550      | • SR650   |

|                                                                                              | • SN850      | • SR670   |

|                                                                                              | • ST250      | • SR850   |

|                                                                                              | • ST258      | • SR850p  |

|                                                                                              | • ST550      | • SR860   |

|                                                                                              | • ST558      | • SR950   |

| Lenovo XClarity Controller<br>with Intel Xeon SP (3rd Gen)<br>and AMD EPYC (2nd, 3rd<br>Gen) | • SD630 V2   | • SR630 V |

|                                                                                              | • SD650 V2   | • SR645   |

|                                                                                              | • SD650-N V2 | • SR650 V |

|                                                                                              | • SN550 V2   | • SR665   |

|                                                                                              | • ST650 V2   | • SR670 V |

|                                                                                              |              | • SR850 V |

|                                                                                              |              | • SR860 V |

# Table 1. Server models supported by LXCC

# Source:

<u>https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.lxca.doc%2Fremotecontrol</u> <u>thinksystem\_use.html</u>

# Server support

The following table shows what level of XCC is included with each ThinkSystem server.

Table 3. Server support

| Server                        | XCC Standard       | XCC Advanced       | XCC Enterprise     |

|-------------------------------|--------------------|--------------------|--------------------|

| ThinkSystem V2 servers        |                    |                    |                    |

| ST650 V2 (7Z74/7Z75)          | Supported          | Supported          | Supported          |

| SR630 V2 (7Z70/7Z71)          | Supported          | Supported          | Supported          |

| SR650 V2 (7Z72/7Z73)          | Supported          | Supported          | Supported          |

| SR670 V2 (7Z22/7Z23)          | Supported          | Upgrade            | Upgrade            |

| SR850 V2 (7D31 / 7D32 / 7D33) | N/A                | N/A                | All models         |

| SR860 V2 (7Z59 / 7Z60)        | N/A                | N/A                | All models         |

| SD630 V2 (7D1K)               | Supported          | Upgrade            | Upgrade            |

| SD650 V2 (7D1M)               | Supported          | Upgrade            | Upgrade            |

| SD650-N V2 (7D1N)             | Supported          | Upgrade            | Upgrade            |

| SN550 V2 (7Z69)               | N/A                | N/A                | All models         |

| ThinkSystem V1 servers        |                    |                    | •                  |

| SE350 ( 7Z46 / 7D1X)          | Supported          | Most models**      | Some models**      |

| ST50 (7Y48/7Y50               | Not supported      | Not supported      | Not supported      |

| ST250 (7Y45/7Y46)             | Most models*       | Upgrade            | Upgrade            |

| SR150 (7Y54)                  | Most models*       | Upgrade            | Upgrade            |

| SR250 (7Y51/7Y52)             | Most models*       | Upgrade            | Upgrade            |

| ST550 (7X09 / 7X10)           | Most models*       | Upgrade            | Upgrade            |

| SR530 (7X07 / 7X08)           | Most models*       | Upgrade            | Upgrade            |

| SR550 (7X03 / 7X04)           | Most models*       | Upgrade            | Upgrade            |

| SR570 (7Y02 / 7Y03)           | Most models*       | Upgrade            | Upgrade            |

| SR590 (7X98 / 7X99)           | Most models*       | Upgrade            | Upgrade            |

| SR630 (7X01 / 7X02)           | Most models*       | Upgrade            | Upgrade            |

| SR635 (7Y98 / 7Y99)           | Not supported      | Not supported      | Not supported      |

| SR645 (7D2Y/7D2X)             | Most models*       | Upgrade            | Upgrade            |

| SR650 (7X05 / 7X06)           | Most models*       | Upgrade            | Upgrade            |

| SR655 (7Y00 / 7Z01)           | Not supported      | Not supported      | Not supported      |

| SR665 (7D2W/7D2V)             | Most models*       | Upgrade            | Upgrade            |

| SR670 (7Y36 / 7Y37 / 7Y38)    | Configure-to-order | Configure-to-order | Configure-to-order |

| SR850 (7X18 / 7X19)           | N/A                | Most models**      | Upgrade            |

| SR850P (7D2F / 2D2G)          | N/A                | N/A                | Most models**      |

| SR860 (7X69 / 7X70)           | N/A                | Most models**      | Upgrade            |

| SR950 (7X11 / 7X12 / 7X13)    | N/A                | N/A                | All models         |

| SD530 (7X21)                  | Most models*       | Upgrade            | Upgrade            |

| SD650 (7X58)                  | Configure-to-order | Configure-to-order | Configure-to-order |

| SN550 (7X16)                  | N/A                | N/A                | All models         |

| SN850 (7X15)                  | N/A                | N/A                | All models         |

#### Part numbers

Models of ThinkSystem servers come with either XClarity Controller Standard, Advanced or Enterprise, depending on the server type and the model. The servers will be delivered with the stated version already active. The following table shows the field upgrades available for models that come with XCC Standard or XCC Advanced.

Source: https://lenovopress.com/lp0880-xcc-support-on-thinksystem-servers

# Lenovo ThinkSystem SD650-N V2 Server

#### Manageability and security

The following powerful systems management features simplify local and remote management of the SD650-N V2 server:

- The server includes an XClarity Controller (XCC) to monitor server availability. Optional upgrade to XCC Advanced to provide remote control (keyboard video mouse) functions. Optional upgrade to XCC Enterprise enables the additional support for the mounting of remote media files (ISO and IMG image files), boot capture, and power capping.

- Lenovo XClarity Administrator offers comprehensive hardware management tools that help to increase uptime, reduce costs and improve productivity through advanced server management capabilities.

- Lenovo XClarity Provisioning Manager, based in UEFI and accessible from F1 during boot, provides system inventory information, graphical UEFI Setup, platform update function, RAID Setup wizard, operating system installation function, and diagnostic functions.

- Support for Lenovo XClarity Energy Manager which captures real-time power and temperature data from the server and provides automated controls to lower energy costs.

# Source: https://lenovopress.lenovo.com/lp1396-thinksystem-sd650-n-v2-server

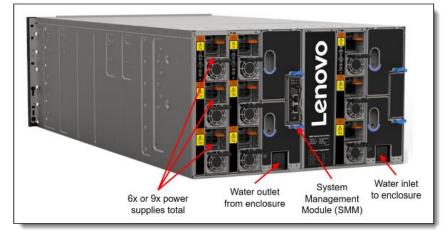

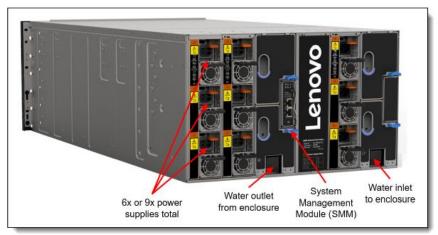

The rear of the enclosure contains the power supplies, cooling water manifolds, and the System Management Module, as shown in the following figure.

Source: https://lenovopress.lenovo.com/lp1396-thinksystem-sd650-n-v2-server

#### System architecture

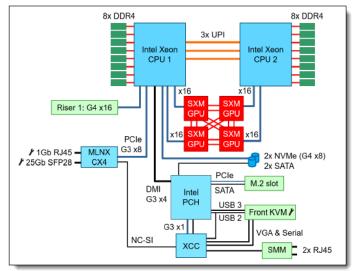

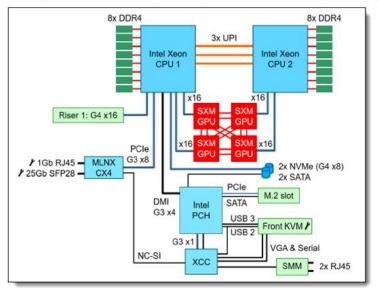

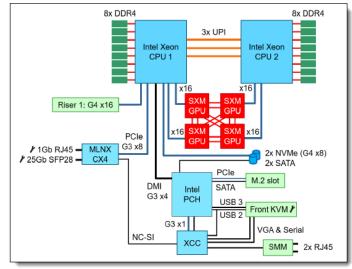

The following figure shows the architectural block diagram of the SD650-N V2 with one PCIe slot and support for two drives. The GPUs each have a PCIe 4.0 x16 connection to the processors.

# Source: https://lenovopress.lenovo.com/lp1396-thinksystem-sd650-n-v2-server

| System<br>Management<br>Module<br>(SMM) | The hot-swappable System Management Module (SMM2) is the management device for the enclosure. Provides integrated systems management functions and controls the power and cooling features of the enclosure. Provides remote browser and CLI-based user interfaces for remote access via the dedicated Gigabit Ethernet port. Remote access is to both the management functions of the enclosure as well as the XClarity Controller (XCC) in each server. |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | The SMM has two Ethernet ports which enables a single incoming Ethernet connection to be daisy chained across 6 enclosures and 36 servers, thereby significantly reducing the number of Ethernet switch ports needed to manage an entire rack of SD650-N V2 servers and enclosures.                                                                                                                                                                       |

| Ports                                   | Two RJ45 port on the rear of the enclosure for 10/100/1000 Ethernet connectivity to the SMM for power and cooling management.                                                                                                                                                                                                                                                                                                                             |

| Systems<br>management                   | Browser-based enclosure management through an Ethernet port on the SMM at the rear of the enclosure. Integrated Ethernet switch provides direct access to the XClarity Controller (XCC) embedded management of the installed servers. Servers provide more management features.                                                                                                                                                                           |

Source: https://lenovopress.lenovo.com/lp1396-thinksystem-sd650-n-v2-server

# Lenovo ThinkSystem SN550 V2 Server

#### Manageability and security

The following powerful systems management features simplify the local and remote management of the SN550 V2:

- Support for Lenovo XClarity Administrator, providing auto-discovery, inventory tracking, monitoring, policy-based firmware updates, address pool management, configuration patterns and operating system installation.

- The server includes an XClarity Controller (XCC) management processor to monitor server availability and perform remote management. XCC Enterprise is supported as standard, which enables remote KVM, mounting of remote media files (ISO and IMG image files), boot capture, and power capping.

- UEFI-based Lenovo XClarity Provisioning Manager, accessible from F1 during boot, provides

system inventory information, graphical UEFI Setup, platform update function, RAID Setup

# Source: https://lenovopress.lenovo.com/lp1397-thinksystem-sn550-v2-server

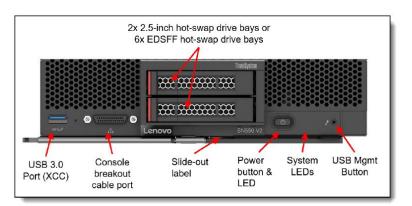

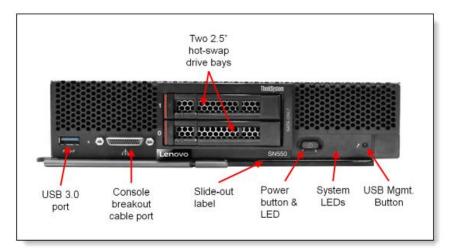

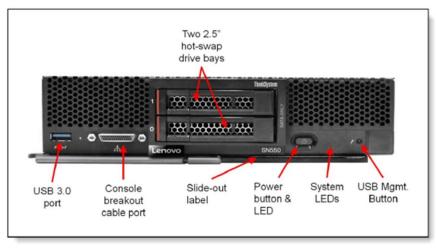

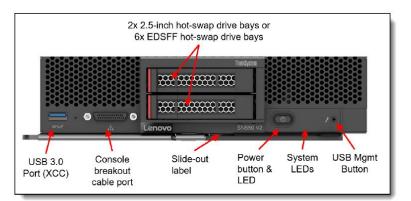

(/assets/images/LP1397/SN550%20V2%20front%20view%20with%20callouts.png) Figure 2. Front view of the ThinkSystem SN550 V2 server

Source: https://lenovopress.lenovo.com/lp1397-thinksystem-sn550-v2-server

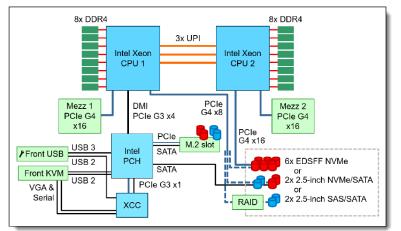

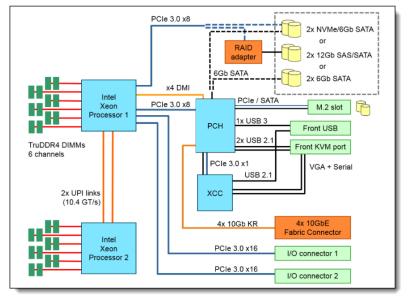

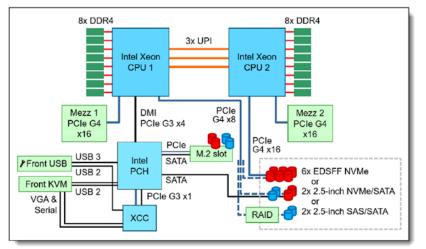

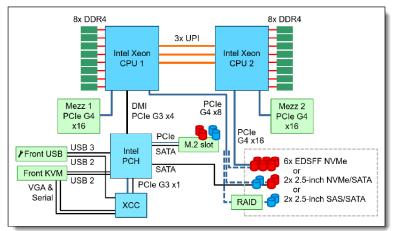

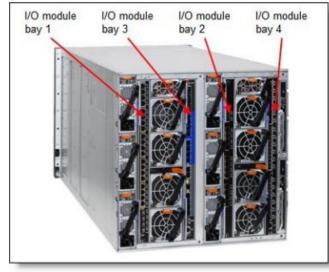

#### System architecture

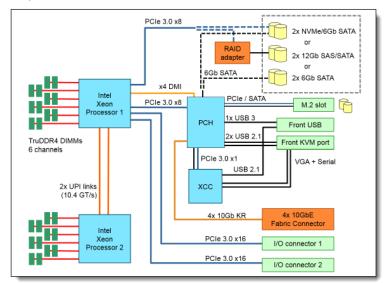

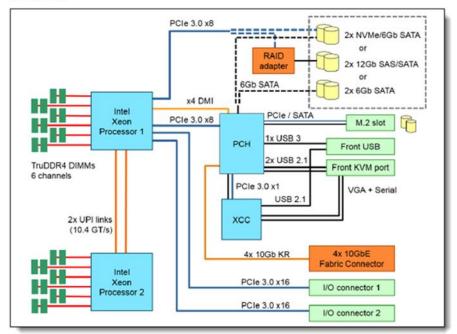

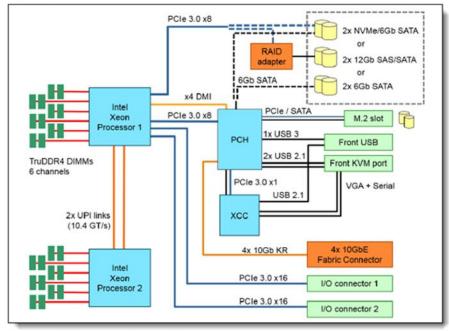

The following figure shows the architectural block diagram of the SN550 V2, showing the major components and their connections.

(/assets/images/LP1397/SN550%20V2%20block%20diagram.png) Figure 5. SN550 V2 system architectural block diagram

Source: https://lenovopress.lenovo.com/lp1397-thinksystem-sn550-v2-server

#### System management

The server contains an integrated service processor, XClarity Controller (XCC), which provides advanced service-processor control, monitoring, and alerting functions. The XCC is based on the Pilot4 XE401 baseboard management controller (BMC) using a dual-core ARM Cortex A9 service processor.

#### Local management

As shown in Figure 2, the SN550 V2 front panel includes a USB port, status indicators, a button to enable management via the USB port and a console breakout cable port. The breakout cable is supplied with the chassis and provides serial, video and two USB 2.0 ports for connecting a local console. The USB ports on the breakout cable support keyboard and mouse; storage devices are not supported.

Source: https://lenovopress.lenovo.com/lp1397-thinksystem-sn550-v2-server

# Lenovo ThinkSystem SN550 Server (Xeon SP Gen 1)

#### Manageability and security

The following powerful systems management features simplify the local and remote management of the SN550:

- Support for Lenovo XClarity Administrator, providing auto-discovery, inventory tracking, monitoring, policy-based firmware updates, address pool management, configuration patterns and operating system installation.

- The server includes an XClarity Controller (XCC) to monitor server availability and perform remote management. XCC Enterprise is supported as standard, which enables remote KVM, mounting of remote media files (ISO and IMG image files), boot capture, and power capping.

- UEFI-based Lenovo XClarity Provisioning Manager, accessible from F1 during boot, provides system inventory information, graphical UEFI Setup, platform update function, RAID Setup wizard, operating system installation function, and diagnostic functions

Source: https://lenovopress.com/lp0637-thinksystem-sn550-server-xeon-sp-gen-1

Figure 2. Front view of the ThinkSystem SN550 Compute Node Source: https://lenovopress.com/lp0637-thinksystem-sn550-server-xeon-sp-gen-1

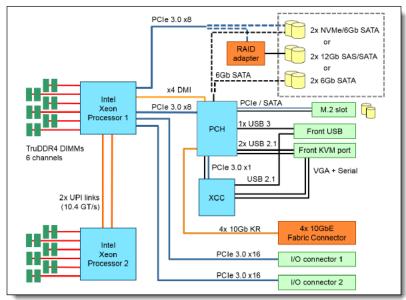

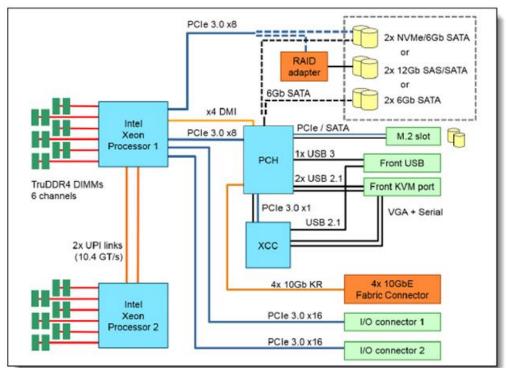

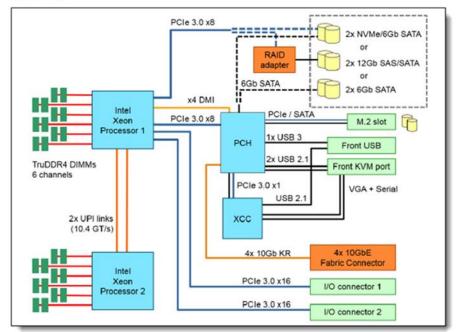

#### System architecture

The following figure shows the architectural block diagram of the SN550, showing the major components and their connections.

Figure 4. SN550 system architectural block diagram Source: https://lenovopress.com/lp0637-thinksystem-sn550-server-xeon-sp-gen-1

#### System Management

The server contains an integrated service processor, XClarity Controller (XCC), which provides advanced service-processor control, monitoring, and alerting functions. The XCC is based on the Pilot4 XE401 baseboard management controller (BMC) using a dual-core ARM Cortex A9 service processor.

#### Local management

As shown in Figure 2, the SN550 front panel includes a USB port, status indicators, a button to enable management via the USB port and a console breakout cable port. The breakout cable supplied with the chassis provides serial, video and a USB port for connecting a local console. The USB ports on the breakout cable support keyboard and mouse; storage devices are not supported.

Source: https://lenovopress.com/lp0637-thinksystem-sn550-server-xeon-sp-gen-1

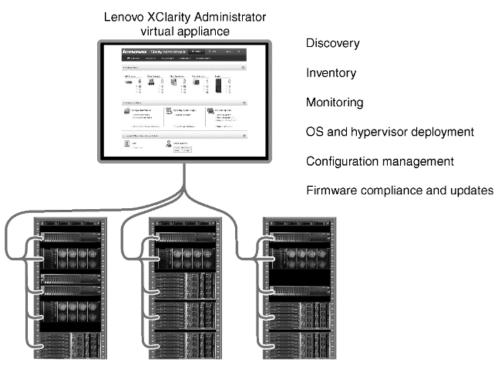

# Lenovo XClarity Administrator™

Centralized resource-management solution designed to reduce complexity, speed response, and enhance the availability of Lenovo ThinkSystem and ThinkAgile solutions.

# Lenovo XClarity Orchestrator

Lenovo XClarity Orchestrator provides centralized monitoring, management, and analytics for environments with large numbers of devices. It leverages existing XClarity Administrator across multiple instances to view overall health, collect device inventory and health summaries, drill down into device details, and view event and audit logs.

Source: https://www.lenovo.com/us/en/data-center/software/management/

<u>Lenovo XClarity Administrator</u> > <u>Managing servers</u>

Language: English 🗸 🗸

# Using remote control

From the Lenovo XClarity Administrator web interface, you can open a remotecontrol session to a managed server as if you were at a local console. You can use the remote-control session to perform operations such as powering on or off the server, and logically mounting a local or remote drive.

# Source:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.lxca.doc%2Fremotecontrol \_thinksystem\_use.html/

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 27 of 125

# Source:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.lxca.doc%2Fremotecontrol\_\_thinksystem\_use.html/

**Note:** The XClarity Administrator does not modify the security settings or cryptographic settings (cryptographic mode and the mode used for secure communications) during the management process. You can modify the cryptographic settings after the system is managed (see <u>Configuring cryptography settings</u>).

# Source:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.lxca.doc%2Fsetup\_manag esystems.html

# 6.3 Lenovo XClarity

Systems management of a cluster includes hardware management, Operating System, and Caffe applications management.

Hardware management uses the Lenovo XClarity Administrator, which is a centralized resource management solution that reduces complexity, speeds up response and enhances the availability of Lenovo server systems and solutions. XClarity is used to install the OS onto new worker nodes; update firmware across the cluster

Source: https://lenovopress.lenovo.com/lp0892.pdf

Lenovo XClarity Administrator provides a central interface to perform the following functions for all managed endpoints.

#### • Hardware management

Lenovo XClarity Administrator provides agent-free hardware management. It can automatically discover manageable endpoints, including Flex System chassis and components, System x, NeXtScale, and ThinkServer servers, and RackSwitch switches. Inventory of the discovered endpoints is also gathered, so an at-a-glance view of the managed hardware inventory and status is possible.

#### Configuration management

You can quickly provision and pre-provision all of your servers using a consistent configuration. Configuration settings (such as local storage, I/O adapters, boot settings, firmware, ports, and IMM and UEFI settings) are saved as a server pattern that can be applied to one or more managed servers. When the server patterns are updated, the changes are automatically deployed to the applied servers.

#### User management

Lenovo XClarity Administrator provides a centralized authentication server to create and manage user accounts and to manage and authenticate user credentials. The authentication server is created automatically when you start the management server for the first time. The user accounts that you create for Lenovo XClarity Administrator are also used to log in to managed chassis and servers.

# Source:

https://cc.cnetcontent.com/inlinecontent/mediaserver/test/14a/7ec/14a7ec57d22b4688923397901 fb26f15/original.pdf

Lenovo XClarity Administrator is a centralized, resource-management solution that simplifies infrastructure management, speeds responses, and enhances the availability of Lenovo® server systems and solutions. It runs as a virtual appliance that automates discovery, inventory, tracking, monitoring, and provisioning for server, network, and storage hardware in a secure environment.

# Source:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.systems.management.xcc.d oc%2Fproduct\_page.html&cp=2\_0

# Implementing a secure environment

Consider the following information when you are evaluating the security requirements for your environment:

- The physical security of your environment is important; limit access to rooms and racks where systems-management hardware is kept.

- Use a software-based firewall to protect your network hardware and data from known and emerging security threats such as viruses and unauthorized access.

- Do not change the default security settings for the network switches and pass-thru modules. The manufacturing default settings for these components disable the use of unsecure protocols and enable the requirement for signed firmware updates.

- The management applications for the CMMs, baseboard management controllers, FSPs, and switches permit only signed firmware-update packages for these components to ensure that only trusted firmware is installed.

- Only the users who are authorized to update firmware components should have firmware-update authority.

- Use the various authorization levels that are available for different users in your environment. Do not allow all users to work with the same supervisor user ID.

- Ensure that your environment meets the following NIST 800-131A criteria to support secure communications:

- Use Secure Sockets Layer (SSL) over the TLS v1.2 protocol.

- Use SHA-256 or stronger hashing functions for digital signatures and SHA-1 or stronger hashing functions for other applications.

- Use RSA-2048 or stronger, or use NIST approved Elliptic Curves that are 224 bits or stronger.

# Source:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.lxca.doc%2Fsecurity\_impl ement.html

<u>Lenovo XClarity Administrator</u> > <u>Managing servers</u>

Language: English 🗸

# Using remote control

From the Lenovo XClarity Administrator web interface, you can open a remotecontrol session to a managed server as if you were at a local console. You can use the remote-control session to perform operations such as powering on or off the server, and logically mounting a local or remote drive.

# Source:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.lxca.doc%2Fremotecontrol \_thinksystem\_use.html/

# **Configuring the Ethernet settings**

The XClarity Controller uses two network controllers. One network controller is connected to the dedicated management port and the other network controller is connected to the shared port. Each of <u>Source</u>:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.systems.management.xcc.d oc%2FNN1ia\_c\_configuringethernet.html

# Controlling access to specific devices

When devices are initially managed by Lenovo XClarity Administrator, a predefined set of role groups have permission to access the devices by default. You change the role groups that can access specific managed devices. When permission is given to certain role groups, only users that are members of those role groups can see and act on those specific devices.

Source:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.lxca.doc%2Faccesscontrol\_setspecificdevices.html

# **Configuring DNS**

Use the information in this topic to view or change XClarity Controller Domain Name System (DNS) settings.

**Note:** In a Flex System, DNS settings cannot be modified on the XClarity Controller. DNS settings are managed by the CMM.

Click  $\ensuremath{\textbf{Network}}$  under  $\ensuremath{\textbf{BMC}}$  Configuration to view or modify XClarity Controller DNS settings.

# Source:

<u>https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.systems.management.xcc.d</u> <u>oc%2FNN1ia\_c\_configuringDNS.html</u>

# Introduction

Most Lenovo ThinkSystem servers contain an integrated service processor, XClarity Controller (XCC), which provides advanced service-processor control, monitoring, and alerting functions. The XCC consolidates the service processor functionality, super I/O, video controller, and remote presence capabilities into a single chip on the server system board. The XCC is based on the Pilot4 XE401 baseboard management controller (BMC) using a dual-core ARM Cortex A9 service processor.

Source: https://lenovopress.com/lp0880-xcc-support-on-thinksystem-servers

# 67. Furthermore, the Accused '140 Products comprise at least one secure

management access controller connected to one or more data buses of said managed network

device for the communication of device management data. For example, the Accused '140

Products include an XCC processor, which controls remote management functions and

communications regarding the same.

# Introduction

Most Lenovo ThinkSystem servers contain an integrated service processor, XClarity Controller (XCC), which provides advanced service-processor control, monitoring, and alerting functions. The XCC consolidates the service processor functionality, super I/O, video controller, and remote presence capabilities into a single chip on the server system board. The XCC is based on the Pilot4 XE401 baseboard management controller (BMC) using a dual-core ARM Cortex A9 service processor.

Source: https://lenovopress.com/lp0880-xcc-support-on-thinksystem-servers

# 6.3 Lenovo XClarity

*Systems management* of a cluster includes hardware management, Operating System, and Caffe applications management.

Hardware management uses the Lenovo XClarity Administrator, which is a centralized resource management solution that reduces complexity, speeds up response and enhances the availability of Lenovo server systems and solutions. XClarity is used to install the OS onto new worker nodes; update firmware across the cluster Source: https://lenovopress.lenovo.com/lp0892.pdf

#### System architecture

The following figure shows the architectural block diagram of the SN550, showing the major components and their connections.

Figure 4. SN550 system architectural block diagram

Source: https://lenovopress.com/lp0637-thinksystem-sn550-server-xeon-sp-gen-1

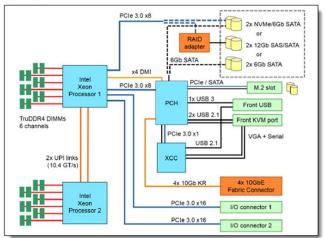

#### System architecture

The following figure shows the architectural block diagram of the SD650-N V2 with one PCIe slot and support for two drives. The GPUs each have a PCIe 4.0 x16 connection to the processors.

Source: https://lenovopress.lenovo.com/lp1397-thinksystem-sn550-v2-server

#### System architecture

The following figure shows the architectural block diagram of the SN550 V2, showing the major components and their connections.

(/assets/images/LP1397/SN550%20V2%20block%20diagram.png) Figure 5. SN550 V2 system architectural block diagram

Source: https://lenovopress.lenovo.com/lp1396-thinksystem-sd650-n-v2-server

# <u>Lenovo XClarity Administrator</u> > <u>Managing servers</u>

Language: English 🗸 🗸

# Using remote control

From the Lenovo XClarity Administrator web interface, you can open a remotecontrol session to a managed server as if you were at a local console. You can use the remote-control session to perform operations such as powering on or off the server, and logically mounting a local or remote drive.

# Source:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.lxca.doc%2Fremotecontrol \_thinksystem\_use.html/

Lenovo XClarity Administrator provides a central interface to perform the following functions for all managed endpoints.

#### Hardware management

Lenovo XClarity Administrator provides agent-free hardware management. It can automatically discover manageable endpoints, including Flex System chassis and components, System x, NeXtScale, and ThinkServer servers, and RackSwitch switches. Inventory of the discovered endpoints is also gathered, so an at-a-glance view of the managed hardware inventory and status is possible.

#### Configuration management

You can quickly provision and pre-provision all of your servers using a consistent configuration. Configuration settings (such as local storage, I/O adapters, boot settings, firmware, ports, and IMM and UEFI settings) are saved as a server pattern that can be applied to one or more managed servers. When the server patterns are updated, the changes are automatically deployed to the applied servers.

#### User management

Lenovo XClarity Administrator provides a centralized authentication server to create and manage user accounts and to manage and authenticate user credentials. The authentication server is created automatically when you start the management server for the first time. The user accounts that you create for Lenovo XClarity Administrator are also used to log in to managed chassis and servers.

# Case 6:23-cv-00068-ADA Document 9 Filed 04/20/23 Page 33 of 125

Source:

https://cc.cnetcontent.com/inlinecontent/mediaserver/test/14a/7ec/14a7ec57d22b4688923397901 fb26f15/original.pdf

68. The Accused '140 Products further comprise an out-of-band access connection

means for connecting said one or more network services or remote users with said secure

management access controller for management of said network device. For example,

connectivity to the XCC processor for remote device management can be over an out-of-band

management connection, giving remote administrators a secure out-of-band management

solution, as illustrated below:

# 6.3 Lenovo XClarity

Systems management of a cluster includes hardware management, Operating System, and Caffe applications management.

Hardware management uses the Lenovo XClarity Administrator, which is a centralized resource management solution that reduces complexity, speeds up response and enhances the availability of Lenovo server systems and solutions. XClarity is used to install the OS onto new worker nodes; update firmware across the cluster Source: https://lenovopress.lenovo.com/lp0892.pdf

Updating a storage HBA controller's firmware through out-of-band(OOB) channels like XCC Web GUI might fail.

#### (where HBA = Host Bus Adapter, XCC = Lenovo XClarity Controller)

When system POST completes, XCC starts to scan each storage controller in the system. If a storage HBA controller does not respond to XCC correctly at that time, XCC will mark it as problematic. Afterwards, if user try to update the controller's firmware through an OOB channel, a failure will occur.

# Source:

https://datacentersupport.lenovo.com/il/en/products/servers/thinksystem/sr650/7x05/solutions/ht 508305

# Introduction

Most Lenovo ThinkSystem servers contain an integrated service processor, XClarity Controller (XCC), which provides advanced service-processor control, monitoring, and alerting functions. The XCC consolidates the service processor functionality, super I/O, video controller, and remote presence capabilities into a single chip on the server system board. The XCC is based on the Pilot4 XE401 baseboard management controller (BMC) using a dual-core ARM Cortex A9 service processor.

Source: https://lenovopress.com/lp0880-xcc-support-on-thinksystem-servers

# Controlling access to specific devices

When devices are initially managed by Lenovo XClarity Administrator, a predefined set of role groups have permission to access the devices by default. You change the role groups that can access specific managed devices. When permission is given to certain role groups, only users that are members of those role groups can see and act on those specific devices.

# Source:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.lxca.doc%2Faccesscontrol\_setspecificdevices.html

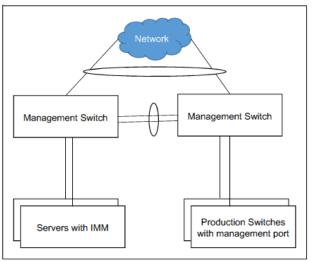

# Isolated management network

The use of a separate management network is always a preferred practice for the isolation of data and management environments. An isolated management network can be used in a lights-out environment to provide out-of-band connectivity to locate and troubleshoot issues that might span across the data network and multiple servers. In today's data centers, this network often consists of a dedicated management switch that uses 1 Gb connectivity.

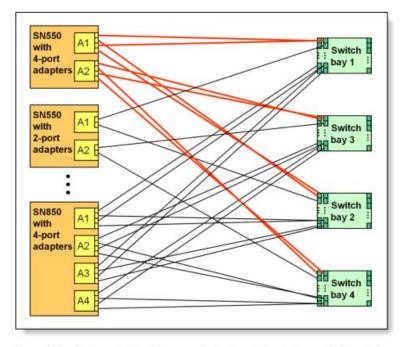

Figure 7 shows Lenovo Switching products that are connecting to a separate 1 Gb Management for out-of-band management. Server management ports (XCC and IMM2), as well as switch management ports, should be connected to this out-of-band network so that they can be reachable in the event of an outage or another issue on the main data network.

Figure 7 Out of Band 1G Management connectivity

Source: https://lenovopress.lenovo.com/lp1068.pdf

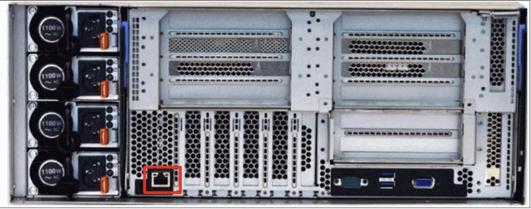

# Configuring a dedicated or shared network port

The SR950 offers two RJ45 ports that you can use to access XCC remotely, either the dedicated management port shown in Figure 5-27 on page 143, or via a port on an installed Ethernet LOM adapter which will be shared with the installed operating system. You select the port by setting Dedicated or Shared for the Network Interface Port in the Network Configuration panel of F1 setup.

Source: https://lenovopress.lenovo.com/lp0746.pdf

# Default local network access to XCC

The default network connection for the XCC on the SR950 is through the System Management port on the back of the server as shown in Figure 5-27.

Figure 5-27 XClarity Controller (XCC) port on the rear of the SR950

The XCC network access label is on the front of the server accessible via a pull-out tab. The label provides the default IPv4 host name and default IPv6 link local address of the XCC. A sample label is shown in Figure 5-28 on page 144.

# Source: https://lenovopress.lenovo.com/lp0746.pdf

69. In addition, the Accused '140 Products include at least one virtual management

interface connection means for connecting said one or more network services or remote users with said secure management controller. For example, connectivity to the XCC processor for remote device management can be over shared network connections via a shared network port, giving remote administrators a secure in-band management solution that virtually separates user and management traffic. Furthermore, in the Accused '140 Products, the virtual management interface connection means provides logical separation of management data from user data and utilizes user interfaces of said managed network element for connecting said one or more network services or remote users with said secure management access controller. For example, the shared network port allows remote administrators to communicate management data and logically separate the user data from the management data via virtualization and VLAN tagging, as seen below:

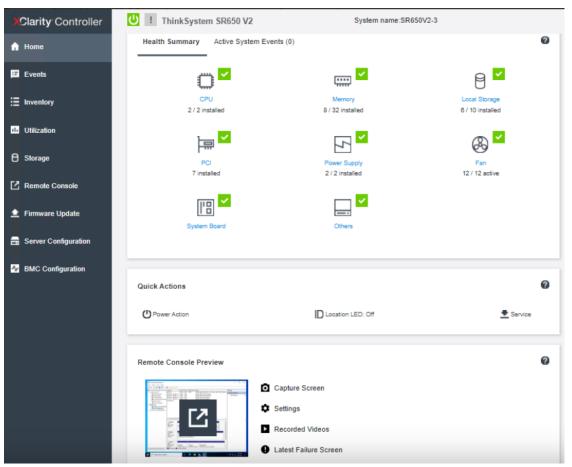

#### **Management interfaces**

There are two ways to access the XCC management processor remotely:

- Command-line interface. To access the CLI interface, use SSH to log in to the management processor.

- Web-based interface. To access the web-based interface, point your browser to the IP address for the management processor. The new intuitive interface includes at-aglance visualizations and simple access to common system actions. The dashboard is shown in the following figure.

Source: https://lenovopress.lenovo.com/lp0880-xcc-support-on-thinksystem-servers

# Configuring a dedicated or shared network port

The SR950 offers two RJ45 ports that you can use to access XCC remotely, either the dedicated management port shown in Figure 5-27 on page 143, or via a port on an installed Ethernet LOM adapter which will be shared with the installed operating system. You select the port by setting Dedicated or Shared for the Network Interface Port in the Network Configuration panel of F1 setup.

Refer to 5.1.1, "Accessing Lenovo XClarity Provisioning Manager" on page 120 for information on how to access the F1 setup options (LXPM). Once in LXPM, you can access this panel by selecting **UEFI Setup**  $\rightarrow$  **BMC Settings**  $\rightarrow$  **Network Settings**, as shown in Figure 5-29.

| XClarity <sup>.</sup><br>Provisioning Manager | ThinkSystem SR950 -[7X12CTO1WW]-                                                     | <b>\$</b>                               |  |

|-----------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------|--|

| VEFI Setup<br>System Information              | Network Interface Port                                                               | Dedicated v                             |  |

| System Settings<br>Date and Time              | Fail-Over Rule<br>Burned-in MAC Address<br>Hostname                                  | Shared 2<br>08-94-EF-40-79-E5           |  |

| Start Options                                 | DHCP Control                                                                         | XCC-7X12-J30005FE DHCP with Fallback  v |  |

| Boot Manager<br>BMC Settings                  | IP Address<br>Subnet Mask                                                            | 255.255.255.0                           |  |

| System Event Logs<br>User Security            | Default Gateway<br>IPv6                                                              | 172.20.58.1                             |  |

| User security                                 | Local Link Address<br>VLAN Support                                                   | FE80:0000:0000:0A94:EFFF:FE40:79E5/64   |  |

|                                               | <ul> <li>Advanced Setting for BMC Ethernet</li> <li>Save Network Settings</li> </ul> | Disable                                 |  |

Figure 5-29 Configuring dedicated or shared XCC port

Source: https://lenovopress.lenovo.com/lp0746.pdf

## XCC dedicated versus shared Ethernet port

When configured as **Dedicated**, you are connecting to the network via the system management port as shown in Figure 5-27 on page 143.

The use of this port allows for easier separation of public and management network traffic. Separating the traffic is done when you connect your public network port to switch ports that belong to a public access virtual LAN (VLAN). The management port is connected to a switch port defined by a separate management VLAN.

When configured as **Shared**, you are sharing network traffic between the management port and on an Ethernet adapter.

Although the Shared configuration eliminates a physical switch port and patch cable configuration, the media access control (MAC) address for the shared Ethernet port and the MAC address for the XCC address through this single network port. This situation means that there are at least two separate IP addresses for the same physical port, which prevents you from configuring the other adapter's Ethernet port in a network team by using 802.3ad load balancing.

To maintain separation between public and management traffic, network teaming software must be used to establish a VLAN to be used by the server to send public-tagged traffic to the network switch. The switch port must be configured as a trunk port to support the public-tagged VLAN traffic and the untagged traffic for the management. The management VLAN must be defined as the native VLAN on the switch port so that its untagged traffic from the switch is accepted by the XCC MAC and dropped by the second Ethernet port's MAC.

Source: https://lenovopress.lenovo.com/lp0746.pdf

## **Configuring the Ethernet settings**

Use the information in this topic to view or change how the XClarity Controller communicates by way of an Ethernet connection.

The XClarity Controller uses two network controllers. One network controller is connected to the dedicated management port and the other network controller is connected to the shared port. Each of the network controllers is assigned its own burned in MAC address. If DHCP is being used to assign an IP address to the XClarity Controller, when a user switches between network ports or when a failover from the dedicated network port to the shared network port occurs, a different IP address may be assigned to the XClarity Controller by the DHCP server. It is recommended that when using DHCP, users should use the host name to access the XClarity Controller rather than relying on an IP address. Even if the XClarity Controller network ports are not changed, the DHCP server could possibly assign a different IP address to the XClarity Controller when the DHCP lease expires, or when the XClarity Controller reboots. If a user needs to access the XClarity Controller using an IP address that will not change, the XClarity Controller should be configured for a static IP address rather than DHCP.

#### Source:

https://sysmgt.lenovofiles.com/help/index.jsp?topic=%2Fcom.lenovo.systems.management.xcc.d oc%2FNN1ia\_c\_configuringethernet.html

After configuring the BMC settings as shown in the scree shot below, XCC access will be activated on the shared NIC if the connection through the XCC dedicated port fails, but the XCC dedicated port will no longer be available after recovering the connection or the connection through the shared NIC fails.

Source: https://support.lenovo.com/in/en/solutions/ht510765-xcc-cannot-be-accessed-from-dedicated-port-after-failover-to-the-shared-nic-lenovo-thinksystem

#### **Configuring advanced Ethernet settings**

Click the **Advanced Ethernet** tab to set additional Ethernet settings.