FILED

January 22, 2024 CLERK, U.S. DISTRICT COURT WESTERN DISTRICT OF TEXAS

CAV

BY:

DEPUTY

## UNITED STATES DISTRICT COURT WESTERN DISTRICT OF TEXAS WACO DIVISION

\$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$

| The CALIFORNIA INSTITUTE OF TECHNOLOGY, |

|-----------------------------------------|

| Plaintiff,                              |

| v.                                      |

| DELL TECHNOLOGIES INC. and DELL INC.,   |

Civil Action No.: 6:20-cv-1042

JURY TRIAL DEMANDED

Defendants.

## SECOND AMENDED COMPLAINT FOR PATENT INFRINGEMENT

Plaintiff the California Institute of Technology ("Caltech" or "Plaintiff"), by and through its undersigned counsel, complains and alleges against Dell Technologies Inc. and Dell Inc. (collectively "Dell" or "Defendants") as follows:

## **NATURE OF THE ACTION**

1. This is a civil action for infringement of U.S. Patent No. 7,116,710 (the "710 patent"), U.S. Patent No. 7,421,032 (the "032 patent"), U.S. Patent No. 7,916,781 (the "781 patent"), and U.S. Patent No. 8,284,833 (the "833 patent") (collectively, "the Asserted Patents") arising under the patent laws of the United States, 35 U.S.C. §§ 1 et seq.

2. In January of 2020, a jury found that Apple Inc.'s ("Apple's") and Broadcom Limited's ("Broadcom's") Wi-Fi products infringed the '710, '032, and '781 patents and awarded Caltech over \$1.1 billion in damages. *Caltech v. Broadcom Limited, et al.*, No. 16-cv-3714-GW, Dkt. No. 2114 (C.D. Cal. Jan. 29, 2020). The Court of Appeals for the Federal Circuit affirmed the findings of the lower court that the Asserted Patents are valid, and that Apple and Broadcom infringed those patents. *Caltech v. Broadcom Limited, et al.*, 25 F.4th 976 (Fed. Cir. 2022). It also remanded the case for a further jury trial to determine damages arising from this infringement. *Id.* As in the case against Apple and Broadcom, Caltech seeks a reasonable royalty from Dell as

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 2 of 117

compensation for its infringement of the '710, '032, and '781 patents. Caltech also seeks a reasonable royalty from Dell as compensation for its infringement of the '833 patent.

## THE PARTIES

3. Caltech is a non-profit private university organized under the laws of the State of California, with its principal place of business at 1200 East California Boulevard, Pasadena, California 91125.

4. Caltech is a world-renowned science and engineering research and education institution, where extraordinary faculty and students seek answers to complex questions, discover new knowledge, lead innovation, and transform our future. To date, 40 Caltech alumni and faculty have won a total of 41 Nobel Prizes. The mission of Caltech is to expand human knowledge and benefit society through research integrated with education. Caltech investigates the most challenging, fundamental problems in science and technology in a singularly collegial, interdisciplinary atmosphere, while educating outstanding students to become creative members of society. Caltech's investment in research has led Caltech to have more inventions disclosed and patents granted per faculty member than any other university in the nation, and to be consistently ranked as having one of the top university patent portfolios in strength and number of patents issued.

5. On information and belief, Dell Technologies Inc. is a Delaware corporation with its principal place of business at One Dell Way, Round Rock, Texas 78682.

6. On information and belief, Dell Inc. is a Delaware corporation with its principal place of business at One Dell Way, Round Rock, Texas 78682. Dell. Inc. has additional offices at 1404 Park Center Dr., Austin, Texas, 701 E. Parmer Lane, Bldg. PS2, Austin, Texas, 12500 Tech Ridge Road, Austin, Texas, 9715 Burnet Road, Austin, Texas, and 4309 Emma Browning Avenue, Austin, Texas.

## JURISDICTION AND VENUE

This Court has jurisdiction over the subject matter of this action under 28 U.S.C.

§§ 1331 and 1338(a).

8. This Court has personal jurisdiction over Dell pursuant to due process and/or the Texas Long Arm Statute because Dell has committed and continues to commit acts of patent

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 3 of 117

infringement, including acts giving rise to this action, within the State of Texas and this District, and because Dell recruits Texas residents, directly or through an intermediary located in this state, for employment inside or outside this state. The Court's exercise of jurisdiction over Dell would not offend traditional notions of fair play and substantial justice because Dell has established minimum contacts with the forum.

9. Venue is proper in this judicial district pursuant to 28 U.S.C. §§ 1391 and 1400 because a substantial part of the events or omissions giving rise to the claims occurred in this District, and Dell has committed acts of infringement and has a regular and established place of business in this District.

10. Dell has committed acts of infringement in this District, directly and/or through intermediaries, by, among other things, making, using, offering to sell, selling, and/or importing products and/or services that infringe the Asserted Patents, as alleged herein.

11. Dell has a regular and established places of business in this District including a shared corporate office at One Dell Way, Round Rock, Texas 78682. Dell is also registered to do business in Texas.

#### CALTECH'S ASSERTED PATENTS

12. On October 3, 2006, the United States Patent Office issued U.S. Patent No. 7,116,710, titled "Serial Concatenation of Interleaved Convolutional Codes Forming Turbo-Like Codes." A true and correct copy of the '710 patent is attached hereto as **Exhibit A**.

13. On September 2, 2008, the United States Patent Office issued U.S. Patent No. 7,421,032, titled "Serial Concatenation of Interleaved Convolutional Codes Forming Turbo-Like Codes." A true and correct copy of the '032 patent is attached hereto as **Exhibit B**. The '032 patent is a continuation of the application that led to the '710 patent.

14. On March 29, 2011, the United States Patent Office issued U.S. Patent No. 7,916,781, titled "Serial Concatenation of Interleaved Convolutional Codes Forming Turbo-Like Codes." A true and correct copy of the '781 patent is attached hereto as **Exhibit C**. The '781 patent is a continuation of the application that led to the '032 patent, which is a continuation of the application that led to the '710 patent.

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 4 of 117

15. On October 9, 2012, the United States Patent Office issued U.S. Patent No. 8,284,833, titled "Serial Concatenation of Interleaved Convolutional Codes Forming Turbo-Like Codes." A true and correct copy of the '833 patent is attached hereto as **Exhibit D**. The '833 patent is a continuation of the application that led to the '781 patent, which is a continuation of the application that led to the '781 patent, which is a continuation that led to the '710 patent.

16. The '710, '032, '781, and '833 patents identify Hui Jin, Aamod Khandekar, and Robert J. McEliece as the inventors.

17. Caltech is the owner of all right, title, and interest in and to each of the Asserted Patents with full and exclusive right to bring suit to enforce the Asserted Patents, including the right to recover for past damages and/or royalties prior to the expiration of the '710, '032, '781, and '833 patents.

18. The Asserted Patents are valid and enforceable.

#### BACKGROUND

## **Caltech's IRA Codes Patents**

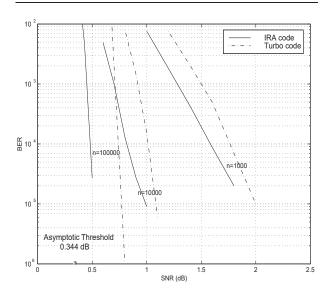

19. The '710, '032, '781, and '833 patents ("IRA Patents") disclose seminal improvements to coding systems and methods. The IRA Patents introduce a new class of error correction codes called "irregular repeat and accumulate codes" (or "IRA codes"). The claimed methods and apparatuses in the IRA Patents are directed to encoders and decoders. For example, the claimed encoders in the IRA Patents generate an IRA "codeword" from message or information bits by reordering irregularly repeated instances of those bits in a randomized but known way and performing other logical operations such as summing and accumulating bits. The claimed decoders in the IRA Patents facilitate recovery of the message or information bits from the codewords even when the codeword have been corrupted by noise such as the noise that is experienced when transmitting a codeword over a wireless communications channel. These IRA codes are at least as effective at correcting errors in transmissions as prior coding techniques such as turbo codes, but use simpler encoding and decoding circuitry and provide other technical and practical advantages,

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 5 of 117

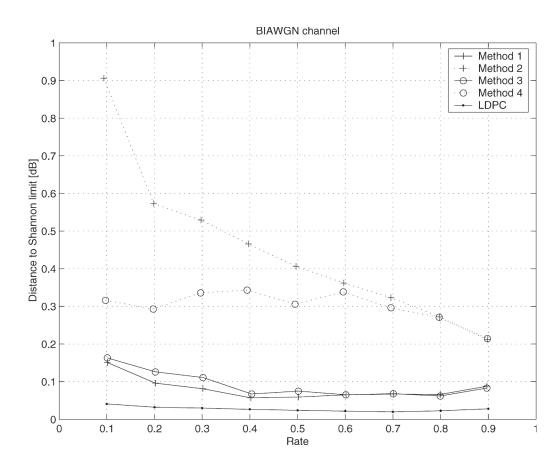

allowing for improved transmission rates and performance. Indeed, the IRA codes disclosed in the IRA Patents enable a transmission rate close to the theoretical limit.

20. The IRA Patents implement these novel IRA codes using novel encoders and decoders. The claims in the IRA Patents enable a person of ordinary skill in the art to implement IRA codes using simple circuitry, providing improved performance over prior art encoders and decoders.

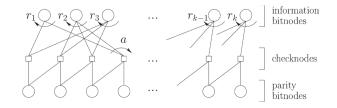

21. In September 2000, the inventors of the IRA Patents published a paper regarding their invention, titled "Irregular Repeat-Accumulate Codes" for the Second International Conference on Turbo Codes (attached hereto as **Exhibit E**). This paper has been widely cited by experts in the field.

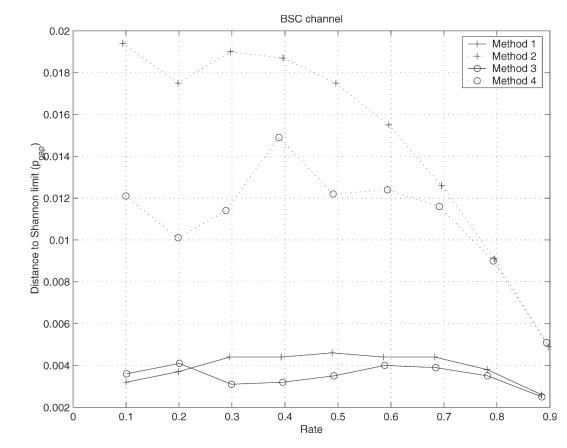

22. The IRA Patents and publications describing IRA codes have been widely recognized and cited by academics and experts in the field of digital communications for their improvements over prior art error correction codes. For example, a paper by Aline Roumy, Souad Guemghar, Giuseppe Caire, and Sergio Verdú praising these IRA codes was published in August 2004 in the IEEE Transactions on Information Theory. This paper, titled "Design Methods for Irregular Repeat-Accumulate Codes," and attached hereto as **Exhibit F**, states:

IRA codes are, in fact, special subclasses of both irregular LDPCs and irregular turbo codes. . . . IRA codes are an appealing choice because the encoder is extremely simple, their performance is quite competitive with that of turbo codes and LDPCs, and they can be decoded with a very-low-complexity iterative decoding scheme.

This paper also notes that, four years after publication of the September 2000 paper, the inventors of the IRA Patents were the only ones to propose a method to design IRA codes.

#### IEEE 802.11 Wi-Fi Standard

23. The Institute of Electrical and Electronics Engineers ("IEEE") has developed standards for wireless communications over local area networks (also referred to as "Wi-Fi"). Wi-Fi usage is widespread in modern electronic products, including smartphones, laptops, routers, televisions, cameras, cars, and other devices that have wireless connections.

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 6 of 117

24. The IEEE standard upon which Wi-Fi is based is IEEE 802.11. The 802.11 standardization process began in the 1990s and the first version of 802.11 was referred to as IEEE 802.11-1997. In the following years, subsequent versions of the 802.11 standard were adopted.

25. One of the key improvements to the 802.11n version of the standard involved a "High Throughput (HT)" mode that is implemented using specific LDPC (Low-Density Parity Check) error correction codes. The same LDPC error correction codes introduced in the 802.11n version of the standard are also implemented in the subsequent 802.11ac version (finalized by IEEE in 2013 and providing the basis for Wi-Fi 5) and 802.11ax version (nearing finalization and providing the basis for Wi-Fi 6) of the standard. The LDPC codes specified by the 802.11n, 802.11ac, and 802.11ax standards may be implemented using Caltech's patented IRA/LDPC encoder and decoder technology.

#### Caltech's Case Against Apple and Broadcom

26. In May 2016, Caltech filed a patent infringement action against Apple and Broadcom in the Central District of California involving the '710, '032, '781, and '833 patents. On January 29, 2020, a jury rendered a verdict finding that Apple's and Broadcom's Wi-Fi products infringed the '710, '032, and '781 Patents and awarded Caltech over \$1.1 billion in damages. *Caltech v. Broadcom et al.*, No. 16-cv-3714-GW, Dkt. No. 2114 (C.D. Cal. Jan. 29, 2020).

27. The trial followed over three years of litigation during which the court dismissed the vast majority of Apple's and Broadcom's defenses and counter-claims. For example, the court denied Apple's and Broadcom's motion for summary judgment seeking to invalidate Caltech's '781 Patent under 35 U.S.C. § 101, and granted Caltech's motion for summary judgment of validity of Caltech's '710 and '032 Patents under 35 U.S.C. § 101. The court also denied Apple and Broadcom's motions for summary judgment of non-infringement.

28. In addition, Apple filed ten *inter partes* review ("IPRs") petitions with the United States Patent and Trademark Office's Patent Trial and Appeal Board ("PTAB") seeking to invalidate the '710, '032, '781, and '833 patents, and the PTAB either denied institution or upheld the patentability of claims in all ten petitions.

#### Dell

29. Dell manufactures, uses, imports, offers for sale, and/or sells Wi-Fi products that incorporate encoders and/or decoders claimed in the Asserted Patents ("Accused Products"). The Accused Products include, but are not limited to, laptops (e.g., Latitude, Vostro, Inspiron, XPS, G-Series, Rugged, Chromebook Enterprise, Education, and Alienware), desktops and all-in-ones (e.g., OptiPlex, Precision, Vostro, Inspiron, and XPS), tablets and 2-in-1s (e.g., XPS, Latitude, Inspiron, Rugged, Chromebook Enterprise, and Education), workstations (e.g., Precision), and thin clients. Upon information and belief, the Accused Products are compliant with the 802.11n, 802.11ac, and/or 802.11ax standards and the LDPC codes defined in those standards.

## COUNT I

## Infringement of the '710 Patent

30. Caltech re-alleges and incorporates by reference the allegations of the preceding paragraphs of this Complaint as if fully set forth herein.

31. In violation of 35 U.S.C. § 271(a), Dell has infringed the '710 patent by making, using, selling, offering for sale, and/or importing into the United States, without authority, the Accused Products which practice each and every limitation of at least claim 20 of the '710 patent. Dell has infringed literally and/or under the doctrine of equivalents.

32. Upon information and belief, the Accused Products comply with the 802.11n, 802.11ac, and/or 802.11ax standards and the 12 LDPC error correction codes defined in those standards. In addition, upon information and belief, the Accused Products are implemented in a manner that not only complies with the 802.11n, 802.11ac, and/or 802.11ax standards, but also infringes the '710 patent. This is because implementations of the 802.11n, 802.11ac, and/or 802.11ax standards that infringe the '710 patent perform substantially fewer computations, have substantially more efficient circuitry, use less memory, consume less semiconductor die area, consume less power, and are otherwise more efficient and cost effective than implementations that do not infringe the '710 patent.

## Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 8 of 117

33. The 12 LDPC codes were originally defined in the 802.11n version of the standard and include three 1/2 rate, three 2/3 rate, three 3/4 rate, and three 5/6 rate LDPC codes as shown in Table 20-14 of the standard below.<sup>1</sup>

| Coding rate<br>(R) | LDPC information block length<br>(bits) | LDPC codeword block length<br>(bits) |

|--------------------|-----------------------------------------|--------------------------------------|

| 1/2                | 972                                     | 1944                                 |

| 1/2                | 648                                     | 1296                                 |

| 1/2                | 324                                     | 648                                  |

| 2/3                | 1296                                    | 1944                                 |

| 2/3                | 864                                     | 1296                                 |

| 2/3                | 432                                     | 648                                  |

| 3/4                | 1458                                    | 1944                                 |

| 3/4                | 972                                     | 1296                                 |

| 3/4                | 486                                     | 648                                  |

| 5/6                | 1620                                    | 1944                                 |

| 5/6                | 1080                                    | 1296                                 |

| 5/6                | 540                                     | 648                                  |

Table 20-14—LDPC parameters

34. On information and belief, the Accused Products encode information or message bits using an LDPC encoder that supports the 12 LDPC codes defined in the standards. The LDPC encoder encodes the information or message bits to generate a codeword as described in Section 20.3.11.6.3 of the 802.11n standard shown below:<sup>2</sup>

<sup>&</sup>lt;sup>1</sup> See IEEE 802.11n-2009 at § 20.3.11.6.2 (emphasis added); see also 802.11-2012 at § 20.3.11.7.2.

<sup>&</sup>lt;sup>2</sup> See IEEE 802.11n-2009 at § 20.3.11.6.3(emphasis added); see also IEEE 802.11-2012 at § 20.3.11.7.3.

#### 20.3.11.6.3 LDPC encoder

For each of the three available codeword block lengths, the LDPC encoder supports rate 1/2, rate 2/3, rate 3/4, and rate 5/6 encoding. The LDPC encoder is systematic, i.e., it encodes an information block,  $c=(i_0,i_1,...,i_{(k-1)})$ , of size *k*, into a codeword, **c**, of size *n*,  $c=(i_0,i_1,...,i_{(k-1)}, p_0, p_1,..., p_{(n-k-1)})$ , by adding *n*–*k* parity bits obtained so that  $\mathbf{H} \times \mathbf{c}^T = \mathbf{0}$ , where **H** is an  $(n-k) \times n$  parity-check matrix. The selection of the codeword block length (*n*) is achieved via the LDPC PPDU encoding process described in 20.3.11.6.5.

35. On information and belief, the LDPC encoders in the Accused Products encode information or message bits in accordance with the 12 parity-check matrices defined in the 802.11n standard. A parity-check matrix H for each of the 12 block sizes and code rates is defined in Tables R.1 to R.3 of the 802.11n. The parity-check matrix for one of the 12 LDPC codes is shown below.<sup>3</sup>

Table R.1 defines the matrix prototypes of the parity-check matrices for a codeword block length n=648 bits, with a subblock size Z=27 bits.

| Table R.1—Matrix prototypes for codeword block length <i>n</i> =648 bits, |

|---------------------------------------------------------------------------|

| subblock size is <b>Z</b> = 27 bits                                       |

| * * *                                                                     |

| (c) |    |    |    |   |    |    |    |    |    |    |   |    |    |   |    |    |    |         |

|-----|----|----|----|---|----|----|----|----|----|----|---|----|----|---|----|----|----|---------|

| 16  | 17 | 22 | 24 | 9 | 3  | 14 | -  | 4  | 2  | 7  | - | 26 | -  | 2 | -  | 21 | -  | 10      |

| 25  | 12 | 12 | 3  | 3 | 26 | 6  | 21 | -  | 15 | 22 | - | 15 | -  | 4 | -  | -  | 16 | - 0 0   |

|     |    |    |    |   |    |    |    |    |    |    |   |    |    |   |    |    |    | 0 0     |

|     |    |    |    |   |    |    |    |    |    |    |   |    |    |   |    |    |    | 0 0 0 - |

| 24  | 5  | 26 | 7  | 1 | -  | -  | 15 | 24 | 15 | -  | 8 | -  | 13 | - | 13 | -  | 11 | 0 0     |

| 2   |    |    |    |   |    |    |    |    |    |    |   |    |    |   |    |    |    | 1 0     |

36. Each parity-check matrix includes a left-hand side that corresponds to information or message bits, and a right-hand side that corresponds to parity bits. In the parity-check matrix shown above, the left-hand side that corresponds to information or message bits includes columns 1-18, and the right-hand side that corresponds to the parity bits includes columns 19-24. The left-hand side is structured in a way that corresponds to the use of irregular repetition, scrambling and summing in the encoding process, while the right-hand side is structured in a way that corresponds to using accumulation in the encoding process. Further, the left-hand side is structured in a way

<sup>&</sup>lt;sup>3</sup> See IEEE 802.11n-2009 at Annex R, Table R.1; see also IEEE 802.11-2012 at Annex F, Table F-1.

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 10 of 117

that corresponds to the use of a low-density generator matrix for performing operations of irregular repetition, scrambling and summing.

37. On information and belief, the LDPC encoders in the Accused Products are implemented in a manner that meets each and every limitation of claim 20 of the '710 patent. This is because implementations of the 802.11n, 802.11ac, and/or 802.11ax standards that infringe claim 20 of the '710 patent perform substantially fewer computations, have substantially more efficient circuitry, use less memory, consume less semiconductor die area, consume less power and are otherwise more efficient and cost effective than implementations that do not infringe this claim. The LDPC encoders in the Accused Products are coders. The LDPC encoders in the Accused Products include first coders which are low-density generator matrix coders and correspond to the left-hand sides of the parity-check matrices. The first coders have an input configured to receive a stream of bits (e.g., information or message bits). The first coders repeat the stream of bits irregularly and scramble the repeated bits. The irregular repetition and scrambling that occurs in the LDPC encoders in the Accused Products corresponds to the irregular repetition and scrambling depicted in the left-hand sides of the parity-check matrices.

38. On information and belief, the LDPC encoders in the Accused Products include second coders which correspond to the right-hand sides of the parity-check matrices. The second coders encode bits output from the first coder at a rate within 10% of one. The encoding of output bits at a rate within 10% of one that occurs in the LDPC encoders in the Accused Products corresponds to the accumulation depicted in the right-hand sides of the parity-check matrices.

39. Dell is not licensed or otherwise authorized to practice the claims of the '710 patent.

40. By reason of Dell's infringement, Caltech has suffered substantial damages.

41. Caltech is entitled to recover the damages sustained as a result of Dell's wrongful acts in an amount subject to proof at trial.

42. Caltech has complied with the requirements of 35 U.S.C. § 287(a) at least because neither Caltech nor any party that has held a license to the '710 patent have made, offered for sale, or sold any products in the United States subject to the marking requirements of 35 U.S.C. § 287(a).

43. Dell's infringement of the '710 patent is exceptional and entitles Caltech to attorneys' fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

## COUNT II

## Infringement of the '032 Patent

44. Caltech re-alleges and incorporates by reference the allegations of the preceding paragraphs of this Complaint as if fully set forth herein.

45. In violation of 35 U.S.C. § 271(a), Dell has infringed the '032 patent by making, using, selling, offering for sale, and/or importing into the United States, without authority, the Accused Products which practice each and every limitation of at least claim 11 of the '032 patent. Dell has infringed literally and/or under the doctrine of equivalents.

46. Upon information and belief, the Accused Products comply with the 802.11n, 802.11ac, and/or 802.11ax standards and the 12 LDPC error correction codes defined in those standards. In addition, upon information and belief, the Accused Products are implemented in a manner that not only complies with the 802.11n, 802.11ac, and/or 802.11ax standards, but also infringes the '032 Patent. This is because implementations of the 802.11n, 802.11ac, and/or 802.11ax standards that infringe the '032 patent perform substantially fewer computations, have substantially more efficient circuitry, use less memory, consume less semiconductor die area, consume less power, and are otherwise more efficient and cost effective than implementations that do not infringe the '032 patent.

47. The 12 LDPC codes were originally defined in the 802.11n version of the standard and include three 1/2 rate, three 2/3 rate, three 3/4 rate, and three 5/6 rate LDPC codes as shown in Table 20-14 of the standard below.<sup>4</sup>

<sup>&</sup>lt;sup>4</sup> See IEEE 802.11n-2009 at § 20.3.11.6.2 (emphasis added); see also 802.11-2012 at § 20.3.11.7.2.

| Coding rate<br>(R) | LDPC information block length<br>(bits) | LDPC codeword block length<br>(bits) |

|--------------------|-----------------------------------------|--------------------------------------|

| 1/2                | 972                                     | 1944                                 |

| 1/2                | 648                                     | 1296                                 |

| 1/2                | 324                                     | 648                                  |

| 2/3                | 1296                                    | 1944                                 |

| 2/3                | 864                                     | 1296                                 |

| 2/3                | 432                                     | 648                                  |

| 3/4                | 1458                                    | 1944                                 |

| 3/4                | 972                                     | 1296                                 |

| 3/4                | 486                                     | 648                                  |

| 5/6                | 1620                                    | 1944                                 |

| 5/6                | 1080                                    | 1296                                 |

| 5/6                | 540                                     | 648                                  |

## Table 20-14—LDPC parameters

48. On information and belief, the Accused Products encode information or message bits using an LDPC encoder that supports the 12 LDPC codes defined in the standards. The LDPC encoder encodes the information or message bits to generate a codeword as described in Section 20.3.11.6.3 of the 802.11n standard shown below:<sup>5</sup>

## 20.3.11.6.3 LDPC encoder

For each of the three available codeword block lengths, the LDPC encoder supports rate 1/2, rate 2/3, rate 3/4, and rate 5/6 encoding. The LDPC encoder is systematic, i.e., it encodes an information block,  $c=(i_0,i_1,...,i_{(k-1)})$ , of size *k*, into a codeword, **c**, of size *n*,  $c=(i_0,i_1,...,i_{(k-1)}, p_0, p_1,..., p_{(n-k-1)})$ , by adding *n*-*k* parity bits obtained so that  $\mathbf{H} \times \mathbf{c}^T = \mathbf{0}$ , where **H** is an  $(n-k) \times n$  parity-check matrix. The selection of the codeword block length (*n*) is achieved via the LDPC PPDU encoding process described in 20.3.11.6.5.

<sup>&</sup>lt;sup>5</sup> See IEEE 802.11n-2009 at § 20.3.11.6.3(emphasis added); see also IEEE 802.11-2012 at § 20.3.11.7.3.

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 13 of 117

49. On information and belief, the LDPC encoders in the Accused Products encode information or message bits in accordance with the 12 parity-check matrices defined in the 802.11n standard. A parity-check matrix H for each of the 12 block sizes and code rates is defined in Tables R.1 to R.3 of the 802.11n. The parity-check matrix for one of the 12 LDPC codes is shown below.<sup>6</sup>

|     | * * * |       |       |       |     |    |    |    |    |    |    |    |    |   |    |    |    |         |

|-----|-------|-------|-------|-------|-----|----|----|----|----|----|----|----|----|---|----|----|----|---------|

| (c) | Codi  | ing r | ate R | x = 3 | /4. |    |    |    |    |    |    |    |    |   |    |    |    |         |

| 16  | 17    | 22    | 24    | 9     | 3   | 14 | -  | 4  | 2  | 7  | -  | 26 | -  | 2 | -  | 21 | -  | 10      |

| 25  | 12    | 12    | 3     | 3     | 26  | 6  | 21 |    |    | 22 | -  | 15 | -  | 4 | -  | -  | 16 | - 0 0   |

| 25  | 18    | 26    | 16    | 22    | 23  | 9  | -  | 0  | -  | 4  | -  | 4  | -  | 8 | 23 | 11 | -  | 0 0     |

| 9   | 7     | 0     | 1     | 17    | -   | -  | 7  | 3  | -  | 3  | 23 | -  | 16 | - | -  | 21 | -  | 0 0 0 - |

| 24  | 5     | 26    | 7     | 1     | -   | -  | 15 | 24 | 15 | -  | 8  | -  | 13 | - | 13 | -  | 11 | 0 0     |

| 2   | 2     | 19    | 14    | 24    | 1   | 15 | 19 | -  | 21 | -  | 2  | -  | 24 | - | 3  | -  | 2  | 1 0     |

| Table R.1—Matrix prototypes for codeword block length n=648 bits, |

|-------------------------------------------------------------------|

| subblock size is <b>Z</b> = 27 bits                               |

50. Each parity-check matrix includes a left-hand side that corresponds to information or message bits, and a right-hand side that corresponds to parity bits. In the parity-check matrix shown above, the left-hand side that corresponds to information or message bits includes columns 1-18, and the right-hand side that corresponds to the parity bits includes columns 19-24. The left-hand side is structured in a way that corresponds to the use of irregular repetition, scrambling and summing in the encoding process, while the right-hand side is structured in a way that corresponds to using accumulation in the encoding process. Further, the left-hand side is structured in a way that corresponds to the use of irregular operations of irregular repetition, scrambling and summing in the use of a low-density generator matrix for performing operations of irregular repetition, scrambling, and summing.

51. A Tanner graph can be constructed from any parity-check matrix. A unique and valuable characteristic of IRA codes is apparent in the Tanner graphs for IRA codes. For example, when constructing a Tanner graph from the 12 LDPC parity-check matrices in the 802.11 standard, message bits are repeated, different subsets of the information bits are repeated different numbers

Table R.1 defines the matrix prototypes of the parity-check matrices for a codeword block length n=648 bits, with a subblock size Z=27 bits.

<sup>&</sup>lt;sup>6</sup> See IEEE 802.11n-2009 at Annex R, Table R.1; see also IEEE 802.11-2012 at Annex F, Table F-1.

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 14 of 117

of times, check nodes are connected to information bits in a random but known pattern, and parity bits are connected to check nodes which enforce a constraint that facilitates the determination of parity bits. While this is not true for a generic LDPC code, it is true for the 12 LDPC codes in the 802.11 standard.

52. On information and belief, the LDPC encoders in the Accused Products are implemented in a manner that meets each and every limitation of claim 11 of the '032 patent. This is because implementations of the 802.11n, 802.11ac, and/or 802.11ax standards that infringe claim 11 of the '032 patent perform substantially fewer computations, have substantially more efficient circuitry, use less memory, consume less semiconductor die area, consume less power, and are otherwise more efficient and cost effective than implementations that do not infringe this claim. The Accused Products are devices that include LDPC encoders. The LDPC encoders receive a collection of message bits and encode the message bits to generate a collection of parity bits. The LDPC encoders in the Accused Products encode the collection of message bits in accordance with the Tanner graph depicted in claim 11. The Tanner graph depicted in claim 11 is a graph representing an IRA code as a set of parity-checks where every message bit is repeated, at least two different subsets of message bits are repeated a different number of times, and check nodes, randomly connected to the repeated message bits, enforce constraints that determine the parity bits.

53. Dell is not licensed or otherwise authorized to practice the claims of the '032 patent.

54. By reason of Dell's infringement, Caltech has suffered substantial damages.

55. Caltech is entitled to recover the damages sustained as a result of Dell's wrongful acts in an amount subject to proof at trial.

56. Caltech has complied with the requirements of 35 U.S.C. § 287(a) at least because neither Caltech nor any party that has held a license to the '032 patent have made, offered for sale, or sold any products in the United States subject to the marking requirements of 35 U.S.C. § 287(a).

57. Dell's infringement of the '032 patent is exceptional and entitles Caltech to attorneys' fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

## **COUNT III**

## Infringement of the '781 Patent

58. Caltech re-alleges and incorporates by reference the allegations of the preceding paragraphs of this Complaint as if fully set forth herein.

59. In violation of 35 U.S.C. § 271(a), Dell has infringed the '781 patent through its use and testing of the Dell Accused Products. Through its use and testing of the Dell Accused Products, Dell performs each and every limitation of at least claim 13 of the '781 patent. Dell has infringed literally and/or under the doctrine of equivalents.

60. Upon information and belief, the Accused Products comply with the 802.11n, 802.11ac, and/or 802.11ax standards and the 12 LDPC error correction codes defined in those standards. In addition, upon information and belief, the Accused Products are implemented in a manner that not only complies with the 802.11n, 802.11ac, and/or 802.11ax standards, but also infringes the '781 Patent. This is because implementations of the 802.11n, 802.11ac, and/or 802.11ax standards that infringe the '781 patent perform substantially fewer computations, have substantially more efficient circuitry, use less memory, consume less semiconductor die area, consume less power, and are otherwise more efficient and cost effective than implementations that do not infringe the '781 patent.

61. The 12 LDPC codes were originally defined in the 802.11n version of the standard and include three 1/2 rate, three 2/3 rate, three 3/4 rate, and three 5/6 rate LDPC codes as shown in Table 20-14 of the standard below.<sup>7</sup>

<sup>&</sup>lt;sup>7</sup> See IEEE 802.11n-2009 at § 20.3.11.6.2 (emphasis added); see also 802.11-2012 at § 20.3.11.7.2.

| Coding rate<br>(R) | LDPC information block length<br>(bits) | LDPC codeword block length<br>(bits) |

|--------------------|-----------------------------------------|--------------------------------------|

| 1/2                | 972                                     | 1944                                 |

| 1/2                | 648                                     | 1296                                 |

| 1/2                | 324                                     | 648                                  |

| 2/3                | 1296                                    | 1944                                 |

| 2/3                | 864                                     | 1296                                 |

| 2/3                | 432                                     | 648                                  |

| 3/4                | 1458                                    | 1944                                 |

| 3/4                | 972                                     | 1296                                 |

| 3/4                | 486                                     | 648                                  |

| 5/6                | 1620                                    | 1944                                 |

| 5/6                | 1080                                    | 1296                                 |

| 5/6                | 540                                     | 648                                  |

## Table 20-14—LDPC parameters

62. On information and belief, the Accused Products encode information or message bits using an LDPC encoder that supports the 12 LDPC codes defined in the standards. The LDPC encoder encodes the information or message bits to generate a codeword as described in Section 20.3.11.6.3 of the 802.11n standard shown below:<sup>8</sup>

## 20.3.11.6.3 LDPC encoder

For each of the three available codeword block lengths, the LDPC encoder supports rate 1/2, rate 2/3, rate 3/4, and rate 5/6 encoding. The LDPC encoder is systematic, i.e., it encodes an information block,  $\mathbf{c}=(i_0,i_1,...,i_{(k-1)})$ , of size *k*, into a codeword, **c**, of size *n*,  $\mathbf{c}=(i_0,i_1,...,i_{(k-1)}, p_0, p_1,..., p_{(n-k-1)})$ , by adding *n*-*k* parity bits obtained so that  $\mathbf{H} \times \mathbf{c}^T = \mathbf{0}$ , where **H** is an  $(n-k) \times n$  parity-check matrix. The selection of the codeword block length (*n*) is achieved via the LDPC PPDU encoding process described in 20.3.11.6.5.

63. On information and belief, the LDPC encoders in the Accused Products encode

information or message bits in accordance with the 12 parity-check matrices defined in the 802.11n

<sup>&</sup>lt;sup>8</sup> See IEEE 802.11n-2009 at § 20.3.11.6.3(emphasis added); see also IEEE 802.11-2012 at § 20.3.11.7.3.

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 17 of 117

standard. A parity-check matrix H for each of the 12 block sizes and code rates is defined in Tables R.1 to R.3 of the 802.11n. The parity-check matrix for one of the 12 LDPC codes is shown below.<sup>9</sup>

Table R.1 defines the matrix prototypes of the parity-check matrices for a codeword block length n=648 bits, with a subblock size Z=27 bits.

| _   |      |       |       |       |     |    |    |    |    | •  | •  |    |    |   |    |    |    |         |

|-----|------|-------|-------|-------|-----|----|----|----|----|----|----|----|----|---|----|----|----|---------|

| (c) | Codi | ing r | ate R | c = 3 | /4. |    |    |    |    |    |    |    |    |   |    |    |    |         |

| 16  | 17   | 22    | 24    | 9     | 3   | 14 | -  | 4  | 2  | 7  | -  | 26 | -  | 2 | -  | 21 | -  | 10      |

| 25  | 12   | 12    | 3     | 3     | 26  | 6  | 21 | -  | 15 | 22 | -  | 15 | -  | 4 | -  | -  | 16 | - 0 0   |

| 25  | 18   | 26    | 16    | 22    | 23  | 9  | -  | 0  | -  | 4  | -  | 4  | -  | 8 | 23 | 11 | -  | 0 0     |

| 9   | 7    | 0     | 1     | 17    | -   | -  | 7  | 3  | -  | 3  | 23 | -  | 16 | - | -  | 21 | -  | 0 0 0 - |

| 24  | 5    | 26    | 7     | 1     | -   | -  | 15 | 24 | 15 | -  | 8  | -  | 13 | - | 13 | -  | 11 | 0 0     |

| 2   | 2    | 19    | 14    | 24    | 1   | 15 | 19 | -  | 21 | -  | 2  | -  | 24 | - | 3  | -  | 2  | 1 0     |

|     |      |       |       |       |     |    |    |    |    |    |    |    |    |   |    |    |    | -       |

Table R.1—Matrix prototypes for codeword block length *n*=648 bits, subblock size is *Z* = 27 bits

64. Each parity-check matrix includes a left-hand side that corresponds to information or message bits, and a right-hand side that corresponds to parity bits. In the parity-check matrix shown above, the left-hand side that corresponds to information or message bits includes columns 1-18, and the right-hand side that corresponds to the parity bits includes columns 19-24. The lefthand side is structured in a way that corresponds to the use of irregular repetition, scrambling and summing in the encoding process, while the right-hand side is structured in a way that corresponds to using accumulation in the encoding process. Further, the left-hand side is structured in a way that corresponds to the use of a low-density generator matrix for performing operations of irregular repetition, scrambling and summing.

65. On information and belief, the LDPC encoders in the Accused Products are implemented in a manner that meets each and every limitation of claim 13 of the '781 patent. This is because implementations of the 802.11n, 802.11ac, and/or 802.11ax standards that infringe claim 13 of the '781 patent perform substantially fewer computations, have substantially more efficient circuitry, use less memory, consume less semiconductor die area, consume less power, and are otherwise more efficient and cost effective than implementations that do not infringe this claim.

<sup>&</sup>lt;sup>9</sup> See IEEE 802.11n-2009 at Annex R, Table R.1; see also IEEE 802.11-2012 at Annex F, Table F-1.

## Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 18 of 117

The LDPC encoders perform a method of encoding a signal. The LDPC encoders receive a block of data in the signal to be encoded. The block of data includes information bits. The LDPC encoders perform an encoding operation using the information bits as an input. The encoding operation includes an accumulation of mod-2 or exclusive-OR sums of bits in subsets of the information bits. The non-null values in each row in the left-hand side of the parity-check matrices correspond to the subsets of information bits that are summed.<sup>10</sup> The accumulation of the sums of bits in subsets of the information bits corresponds to the accumulation operations depicted in the left-hand side of the parity-check matrices.

66. Dell is not licensed or otherwise authorized to practice the claims of the '781 patent.

67. By reason of Dell's infringement, Caltech has suffered substantial damages.

68. Caltech is entitled to recover the damages sustained as a result of Dell's wrongful acts in an amount subject to proof at trial.

69. Caltech has complied with the requirements of 35 U.S.C. § 287(a) at least because neither Caltech nor any party that has held a license to the '781 patent have made, offered for sale, or sold any products in the United States subject to the marking requirements of 35 U.S.C. § 287(a).

70. Dell's infringement of the '781 patent is exceptional and entitles Caltech to attorneys' fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

## COUNT IV

#### **Infringement of the '833 Patent**

71. Caltech re-alleges and incorporates by reference the allegations of the preceding paragraphs of this Complaint as if fully set forth herein.

72. In violation of 35 U.S.C. § 271(a), Dell has infringed the '833 patent by making, using, selling, offering for sale, and/or importing into the United States, without authority, the Accused Products which practice each and every limitation of at least claim 1 of the '833 patent. Dell has infringed literally and/or under the doctrine of equivalents.

<sup>&</sup>lt;sup>10</sup> The null values are represented by "-" in the parity-check matrices. The non-null values are represented by numbers.

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 19 of 117

73. Upon information and belief, the Accused Products comply with the 802.11n, 802.11ac, and/or 802.11ax standards and the 12 LDPC error correction codes defined in those standards. In addition, upon information and belief, the Accused Products are implemented in a manner that not only complies with the 802.11n, 802.11ac, and/or 802.11ax standards, but also infringes the '833 patent. This is because implementations of the 802.11n, 802.11ac, and/or 802.11ax standards that infringe the '833 patent perform substantially fewer computations, have substantially more efficient circuitry, use less memory, consume less semiconductor die area, consume less power, and are otherwise more efficient and cost effective than implementations that do not infringe the '833 patent.

74. The 12 LDPC codes were originally defined in the 802.11n version of the standard and include three 1/2 rate, three 2/3 rate, three 3/4 rate, and three 5/6 rate LDPC codes as shown in Table 20-14 of the standard below.<sup>11</sup>

| Coding rate<br>(R) | LDPC information block length<br>(bits) | LDPC codeword block length<br>(bits) |

|--------------------|-----------------------------------------|--------------------------------------|

| 1/2                | 972                                     | 1944                                 |

| 1/2                | 648                                     | 1296                                 |

| 1/2                | 324                                     | 648                                  |

| 2/3                | 1296                                    | 1944                                 |

| 2/3                | 864                                     | 1296                                 |

| 2/3                | 432                                     | 648                                  |

| 3/4                | 1458                                    | 1944                                 |

| 3/4                | 972                                     | 1296                                 |

| 3/4                | 486                                     | 648                                  |

| 5/6                | 1620                                    | 1944                                 |

| 5/6                | 1080                                    | 1296                                 |

| 5/6                | 540                                     | 648                                  |

Table 20-14—LDPC parameters

<sup>&</sup>lt;sup>11</sup> See IEEE 802.11n-2009 at § 20.3.11.6.2 (emphasis added); see also 802.11-2012 at § 20.3.11.7.2.

75. On information and belief, the Accused Products encode information or message bits using an LDPC encoder that supports the 12 LDPC codes defined in the standards. The LDPC encoder encodes the information or message bits to generate a codeword as described in Section 20.3.11.6.3 of the 802.11n standard shown below:<sup>12</sup>

## 20.3.11.6.3 LDPC encoder

For each of the three available codeword block lengths, the LDPC encoder supports rate 1/2, rate 2/3, rate 3/4, and rate 5/6 encoding. The LDPC encoder is systematic, i.e., it encodes an information block,  $c=(i_0,i_1,...,i_{(k-1)})$ , of size *k*, into a codeword, **c**, of size *n*,  $c=(i_0,i_1,...,i_{(k-1)}, p_0, p_1,..., p_{(n-k-1)})$ , by adding *n*–*k* parity bits obtained so that  $\mathbf{H} \times \mathbf{c}^T = \mathbf{0}$ , where **H** is an  $(n-k) \times n$  parity-check matrix. The selection of the codeword block length (*n*) is achieved via the LDPC PPDU encoding process described in 20.3.11.6.5.

76. On information and belief, the LDPC encoders in the Accused Products encode information or message bits in accordance with the 12 parity-check matrices defined in the 802.11n standard. A parity-check matrix H for each of the 12 block sizes and code rates is defined in Tables R.1 to R.3 of the 802.11n. The parity-check matrix for one of the 12 LDPC codes is shown below.<sup>13</sup>

Table R.1 defines the matrix prototypes of the parity-check matrices for a codeword block length n=648 bits, with a subblock size Z=27 bits.

|     |      |       |       |        |     |    |    |    | *  | * * | *  |    |    |   |    |    |    |         |

|-----|------|-------|-------|--------|-----|----|----|----|----|-----|----|----|----|---|----|----|----|---------|

| (c) | Codi | ng ra | ate R | k = 3/ | /4. |    |    |    |    |     |    |    |    |   |    |    |    |         |

| 16  | 17   | 22    | 24    | 9      | 3   | 14 | -  | 4  | 2  | 7   | -  | 26 | -  | 2 | -  | 21 | -  | 10      |

| 25  | 12   | 12    | 3     | 3      | 26  | 6  | 21 | -  | 15 | 22  | -  | 15 | -  | 4 | -  | -  | 16 | - 0 0   |

| 25  | 18   | 26    | 16    | 22     | 23  | 9  | -  | 0  | -  | 4   | -  | 4  | -  | 8 | 23 | 11 | -  | 0 0     |

| 9   | 7    | 0     | 1     | 17     | -   | -  | 7  | 3  | -  | 3   | 23 | -  | 16 | - | -  | 21 | -  | 0 0 0 - |

| 24  | 5    | 26    | 7     | 1      | -   | -  | 15 | 24 | 15 | -   | 8  | -  | 13 | - | 13 | -  | 11 | 0 0     |

| 2   | 2    | 19    | 14    | 24     | 1   | 15 | 19 | -  | 21 | -   | 2  | -  | 24 | - | 3  | -  | 2  | 1 0     |

Table R.1—Matrix prototypes for codeword block length n=648 bits,subblock size is Z = 27 bits

77. Each parity-check matrix includes a left-hand side that corresponds to information or message bits, and a right-hand side that corresponds to parity bits. In the parity-check matrix shown above, the left-hand side that corresponds to information or message bits includes columns

<sup>&</sup>lt;sup>12</sup> See IEEE 802.11n-2009 at § 20.3.11.6.3(emphasis added); see also IEEE 802.11-2012 at § 20.3.11.7.3.

<sup>&</sup>lt;sup>13</sup> See IEEE 802.11n-2009 at Annex R, Table R.1; see also IEEE 802.11-2012 at Annex F, Table F-1.

#### Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 21 of 117

1-18, and the right-hand side that corresponds to the parity bits includes columns 19-24. The lefthand side is structured in a way that corresponds to the use of irregular repetition, scrambling and summing in the encoding process, while the right-hand side is structured in a way that corresponds to using accumulation in the encoding process. Further, the left-hand side is structured in a way that corresponds to the use of a low-density generator matrix for performing operations of irregular repetition, scrambling and summing.

78. On information and belief, the LDPC encoders in the Accused Products are implemented in a manner that meets each and every limitation of claim 1 of the '833 patent. This is because implementations of the 802.11n, 802.11ac, and/or 802.11ax standards that infringe claim 1 of the '833 patent perform substantially fewer computations, have substantially more efficient circuitry, use less memory, consume less semiconductor die area, consume less power, and are otherwise more efficient and cost effective than implementations that do not infringe this claim. The LDPC encoders in the Accused Products are an apparatus for performing encoding operations. The LDPC encoders in the Accused Products include a first a first set of memory locations to store information bits where two or more memory locations of the first set of memory locations are read by the permutation module different times from one another. The LDPC encoders in the Accused Products also include a second set of memory locations to store parity bits. The LDPC encoders in the Accused Products further include a permutation module to read a bit from the first set of memory locations and combine the read bit to a bit in the second set of memory locations based on a corresponding index of the first set of memory locations and a corresponding index of the second set of memory locations. The LDPC encoders in the Accused Products include an accumulator to perform accumulation operations on the bits stored in the second set of memory locations.

79. Dell is not licensed or otherwise authorized to practice the claims of the '833 patent.

80. By reason of Dell's infringement, Caltech has suffered substantial damages.

81. Caltech is entitled to recover the damages sustained as a result of Dell's wrongful acts in an amount subject to proof at trial.

## Case 6:20-cv-01042-ADA Document 77 Filed 01/22/24 Page 22 of 117

82. Caltech has complied with the requirements of 35 U.S.C. § 287(a) at least because neither Caltech nor any party that has held a license to the '833 patent have made, offered for sale, or sold any products in the United States subject to the marking requirements of 35 U.S.C. § 287(a).

83. Dell's infringement of the '833 patent is exceptional and entitles Caltech to attorneys' fees and costs incurred in prosecuting this action under 35 U.S.C. § 285.

#### DEMAND FOR JURY TRIAL

Pursuant to Rule 38 of the Federal Rules of Civil Procedure, Plaintiff hereby demands a trial by jury as to all issues so triable.

#### PRAYER FOR RELIEF

WHEREFORE, Plaintiff respectfully prays for the following relief:

(a) A judgment that Defendants have infringed each and every one of the Asserted Patents;

(b) Damages adequate to compensate Caltech for Defendants' infringement of the Asserted Patents pursuant to 35 U.S.C. § 284;

- (c) Pre-judgment interest;

- (d) Post-judgment interest;

(e) A declaration that this action is exceptional pursuant to 35 U.S.C. § 285, and an award to Caltech of its attorneys' fees, costs, and expenses incurred in connection with this action; and

(f) Such other relief as the Court deems just and equitable.

DATED: January 19, 2024

Respectfully submitted,

By /s/ J. Mark Mann

J. Mark Mann MANN TINDEL THOMPSON 300 West Main Street Henderson, Texas 75652 Telephone: (903) 657-8540 Facsimile: (903) 657-6003 Mark@themannfirm.com

James R. Asperger QUINN EMANUEL URQUHART & SULLIVAN, LLP 865 S. Figueroa Street, 10<sup>th</sup> Floor Los Angeles, CA 90017-2543 Telephone: (213) 443-3000 Facsimile: (213) 443 3100 jimasperger@quinnemanuel.com Kevin Johnson Todd Briggs QUINN EMANUEL URQUHART & SULLIVAN, LLP 555 Twin Dolphin Drive, 5<sup>th</sup> Floor Redwood Shores, California 94065-2139 Telephone: (650) 801 5000 Facsimile: (650) 801 5100 kevinjohnson@quinnemanuel.com toddbriggs@quinnemanuel.com

Brian Biddinger QUINN EMANUEL URQUHART & SULLIVAN, LLP 51 Madison Avenue, 22nd Floor New York, New York 10010-1601 Telephone: (212) 849 7000 Facsimile: (212) 849 7100 brianbiddinger@quinnemanuel.com

Attorneys for Plaintiff California Institute of Technology

# **EXHIBIT** A

US007116710B1

## (12) United States Patent

## Jin et al.

#### (54) SERIAL CONCATENATION OF INTERLEAVED CONVOLUTIONAL CODES FORMING TURBO-LIKE CODES

- (75) Inventors: Hui Jin, Glen Gardner, NJ (US); Aamod Khandekar, Pasadena, CA (US); Robert J. McEliece, Pasadena, CA (US)

- (73) Assignee: California Institute of Technology, Pasadena, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 735 days.

- (21) Appl. No.: 09/861,102

- (22) Filed: May 18, 2001

#### **Related U.S. Application Data**

- (60) Provisional application No. 60/205,095, filed on May 18, 2000.

- (51) Int. Cl. *H04B 1/66*

- 375/341; 341/51; 341/102; 714/752

See application file for complete search history.

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 5,392,299 | А |   | 2/1995 | Rhines et al.   |         |  |

|-----------|---|---|--------|-----------------|---------|--|

| 5,751,739 | А | * | 5/1998 | Seshadri et al. | 714/746 |  |

## (10) Patent No.: US 7,116,710 B1

## (45) **Date of Patent:** Oct. 3, 2006

| 5,881,093    | А | 3/1999 | Wang et al.         |

|--------------|---|--------|---------------------|

| 6.014.411    |   |        | Wang                |

| 6,023,783    |   |        | Divsalar et al.     |

| 6,031,874    |   | 2/2000 | Chennakeshu et al.  |

| 6.032.284    |   | 2/2000 |                     |

| 6.044.116    |   | 3/2000 | Wang                |

| 6,396,423    |   |        | Laumen et al 341/95 |

| 6,437,714    |   |        | Kim et al 341/81    |

| 2001/0025358 |   | 9/2001 | Eidson et al.       |

#### OTHER PUBLICATIONS

Wiberg et al., "Codes and Iteratic Decoding on General Graphs", 1995 Intl. Symposium on Information Theory, Sep. 1995, p. 506.\* Appendix A.1 "Structure of Parity Check Matrices of Standardized LDPC Codes," Digital Video Broadcasting (DVB) User guidelines for the second generation system for Broadcasting, Interactive Services, News Gathering and other broadband satellite applications (DVB-S2) ETSI TR 102 376 V1.1.1. (2005-02) Technical Report. pp. 64.

Benedetto et al., "Bandwidth efficient parallel concatenated coding schemes," Electronics Letters 31(24):2067-2069 (Nov. 23, 1995). Benedetto et al., "Soft-output decoding algorithms in iterative decoding of turbo codes," The Telecommunications and Data Acquisition (TDA) Progress Report 42-124 for NASA and California Institute of Technology Jet Propulsion Laboratory, Joseph H. Yuen, Ed., pp. 63-87 (Feb. 15, 1996).

#### (Continued)

Primary Examiner—Dac V. Ha

(74) Attorney, Agent, or Firm-Fish & Richardson P.C.

#### (57) ABSTRACT

A serial concatenated coder includes an outer coder and an inner coder. The outer coder irregularly repeats bits in a data block according to a degree profile and scrambles the repeated bits. The scrambled and repeated bits are input to an inner coder, which has a rate substantially close to one.

#### 33 Claims, 5 Drawing Sheets

#### OTHER PUBLICATIONS

Benedetto et al., "Serial Concatenation of Interleaved Codes: Performace Analysis, Design, and Iterative Decoding," The Telecommunications and Data Acquisition (TDA) Progress Report 42-126 for NASA and California Institute of Technology Jet Propulsion Laboratory, Jospeh H. Yuen, Ed., pp. 1-26 (Aug. 15, 1996). Benedetto et al., "A Soft-Input Soft-Output Maximum A Posteriori (MAP) Module to Decode Parallel and Serial Concatenated Codes," The Telecommunications and Data Acquisition (TDA) Progress Report 42-127 for NASA and California Institute of Technology Jet Propulsion Laboratory, Jospeh H. Yuen, Ed., pp. 1-20 (Nov. 15, 1996).

Benedetto et al., "Parallel Concatenated Trellis Coded Modulation," ICC '96, IEEE, pp. 974-978, (Jun. 1996).

Benedetto, S. et al., "A Soft-Input Soft-Output APP Module for Iterative Decoding of Concatenated Codes," IEEE Communications Letters 1(1):22-24 (Jan. 1997).

Benedetto et al., "Serial Concatenation of interleaved codes: performance analysis, design, and iterative decoding," Proceedings from the IEEE 1997 International Symposium on Information Theory (ISIT), Ulm, Germany, p. 106, Jun. 29-Jul. 4, 1997.

Benedetto et al., "Serial Concatenated Trellis Coded Modulation with Iterative Decoding," Proceedings from IEEE 1997 International Symposium on Information Theory (ISIT), Ulm, Germany, p. 8, Jun. 29-Jul. 4, 1997.

Benedetto et al., "Design of Serially Concatenated Interleaved Codes," ICC 97, Montreal, Canada, pp. 710-714, (Jun. 1997).

Berrou et al., "Near Shannon Limit Error-Correcting Coding and Decoding: Turbo Codes," ICC pp. 1064-1070 (1993).

Digital Video Broadcasting (DVB) User guidelines for the second generation system for Broadcasting, Interactive Services, News Gathering and other broadband satellite applications (DVB-S2) ETSI TR 102 376 V1.1.1. (Feb. 2005) Technical Report, pp. 1-104 (Feb. 15, 2005).

Divsalar et al., "Coding Theorems for 'Turbo-Like' Codes," Proceedings of the 36<sup>th</sup> Annual Allerton Conference on Communication, Control, and Computing, Sep. 23-25 1998, Allerton House, Monticello, Illinois, pp. 201-210 (1998).

Divsalar, D. et al., "Multiple Turbo Codes for Deep-Space Communications," The Telecommunications and Data Acquisition (TDA) Progress Report 42-121 for NASA and California Institute of Technology Jet Propulsion Laboratory, Jospeh H. Yuen, Ed., pp. 60-77 (May 15, 1995).

Divsalar, D. et al., "On the Design of Turbo Codes," The Telecommunications and Data Acquisition (TDA) Progress Report 42-123 for NASA and California Institute of Technology Jet Propulsion Laboratory, Jospeh H. Yuen, Ed., pp. 99-131 (Nov. 15, 1995).

Divsalar, D. et al., "Low-rate turbo codes for Deep Space Communications," Proceedings from the 1995 IEEE International Symposium on Information Theory, Sep. 17-22, 1995, Whistler, British Columbia, Canada, p. 35.

Divsalar, D. et al., "Turbo Codes for PCS Applications," ICC 95, IEEE, Seattle, WA, pp. 54-59 (Jun. 1995).

Divsalar, D. et al., "Multiple Turbo Codes," MILCOM 95, San Diego, CA pp. 279-285 (Nov. 5-6, 1995).

Divsalar et al., "Effective free distance of turbo codes," Electronics Letters 32(5): 445-446 (Feb. 29, 1996).

Divsalar, D. et al., "Hybrid concatenated codes and Iterative Decoding," Proceedings from the IEEE 1997 International Symposium on Information Theory (ISIT), Ulm, Germany, p. 10 (Jun. 29-Jul. 4, 1997).

Divsalar, D. et al., "Serial Turbo Trellis Coded Modulation with Rate-1 Inner Code," Proceedings from the IEEE 2000 International Symposium on Information Theory (ISIT), Italy, pp. 1-14 (Jun. 2000).

Jin et al., "Irregular Repeat - Accumulate Codes," 2nd International Symposium on Turbo Codes & Related Topics, Sep. 4-7, 2000, Brest, France, 25 slides, (presented on Sep. 4, 2000).

Jin et al., "Irregular Repeat-Accumulate Codes," 2<sup>nd</sup> International Symposium on Turbo Codes & Related Topics, Sep. 4-7, 2000, Brest, France, pp. 1-8 (2000).

Richardson, et al., "Design of capacity approaching irregular low density parity check codes," IEEE Trans, Inform. Theory 47: 619-637 (Feb. 2001).

Richardson, T. and R. Urbanke, "Efficient encoding of low-density parity check codes," IEEE Trans. Inform. Theory 47: 638-656 (Feb. 2001).

\* cited by examiner

Oct. 3, 2006

Sheet 1 of 5

US 7,116,710 B1

Oct. 3, 2006

## FIG. 3

U.S. Patent

Oct. 3, 2006

Sheet 4 of 5

US 7,116,710 B1

Oct. 3, 2006

Sheet 5 of 5

5

#### SERIAL CONCATENATION OF INTERLEAVED CONVOLUTIONAL CODES FORMING TURBO-LIKE CODES

#### CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims priority to U.S. Provisional Application Ser. No. 60/205,095, filed on May 18, 2000, and to U.S. application Ser. No. 09/922,852, filed on Aug. 18, 2000 10 and entitled Interleaved Serial Concatenation Forming Turbo-Like Codes.

#### GOVERNMENT LICENSE RIGHTS

The U.S. Government has a paid-up license in this invention and the right in limited circumstances to require the patent owner to license others on reasonable terms as provided for by the terms of Grant No. CCR-9804793 awarded by the National Science Foundation. 20

#### BACKGROUND

Properties of a channel affect the amount of data that can be handled by the channel. The so-called "Shannon limit" defines the theoretical limit of the amount of data that a <sup>25</sup> channel can carry.

Different techniques have been used to increase the data rate that can be handled by a channel. "Near Shannon Limit Error-Correcting Coding and Decoding: Turbo Codes," by Berrou et al. ICC, pp 1064–1070, (1993), described a new <sup>30</sup> "turbo code" technique that has revolutionized the field of error correcting codes. Turbo codes have sufficient randomness to allow reliable communication over the channel at a high data rate near capacity. However, they still retain sufficient structure to allow practical encoding and decoding algorithms. Still, the technique for encoding and decoding turbo codes can be relatively complex.

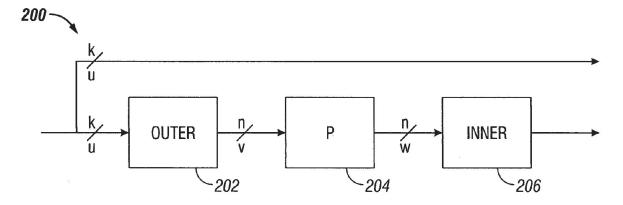

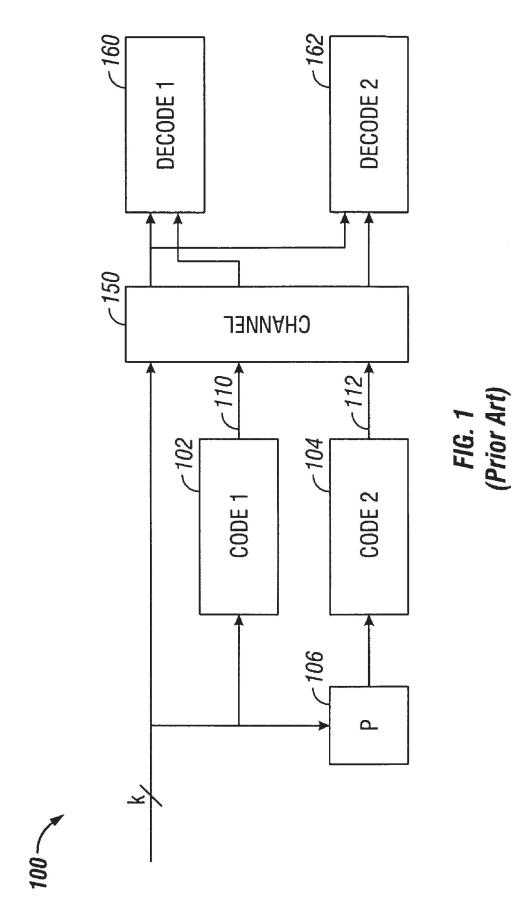

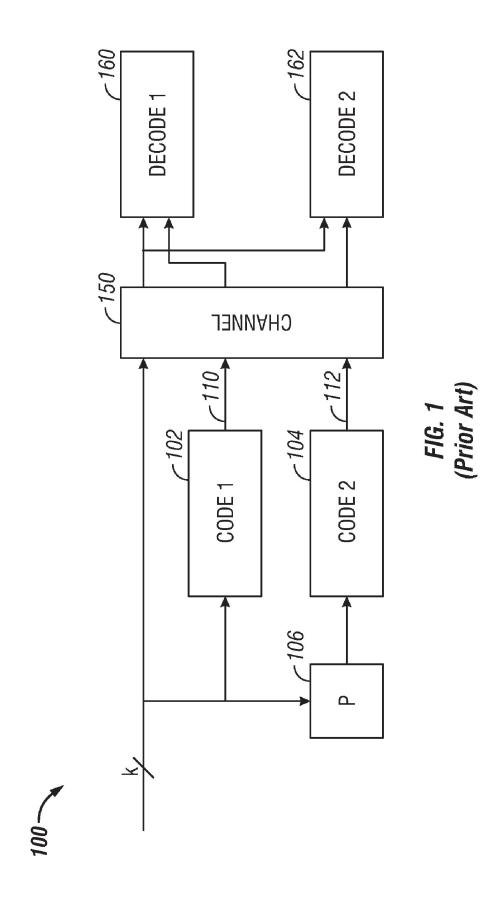

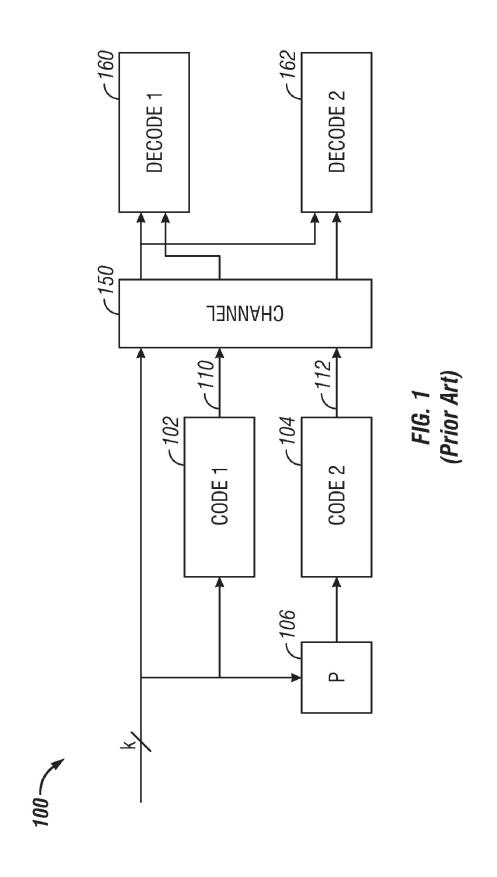

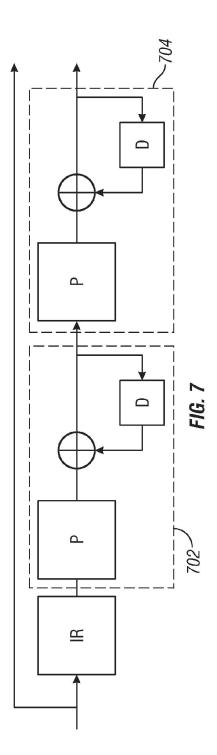

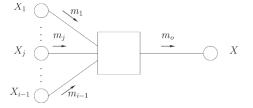

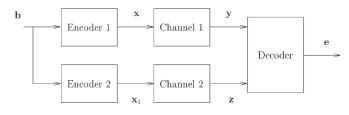

A standard turbo coder 100 is shown in FIG. 1. A block of k information bits is input directly to a first coder 102. A k bit interleaver 106 also receives the k bits and interleaves them prior to applying them to a second coder 104. The second coder produces an output that has more bits than its input, that is, it is a coder with rate that is less than 1. The coders 102, 104 are typically recursive convolutional coders.

Three different items are sent over the channel **150**: the original k bits, first encoded bits **110**, and second encoded bits **112**. At the decoding end, two decoders are used: a first constituent decoder **160** and a second constituent decoder **162**. Each receives both the original k bits, and one of the encoded portions **110**, **112**. Each decoder sends likelihood estimates of the decoded bits to the other decoders. The estimates are used to decode the uncoded information bits as corrupted by the noisy channel.

#### SUMMARY

A coding system according to an embodiment is configured to receive a portion of a signal to be encoded, for example, a data block including a fixed number of bits. The coding system includes an outer coder, which repeats and 60 scrambles bits in the data block. The data block is apportioned into two or more sub-blocks, and bits in different sub-blocks are repeated a different number of times according to a selected degree profile. The outer coder may include a repeater with a variable rate and an interleaver. Alterna-65 tively, the outer coder may be a low-density generator matrix (LDGM) coder. 2

The repeated and scrambled bits are input to an inner coder that has a rate substantially close to one. The inner coder may include one or more accumulators that perform recursive modulo two addition operations on the input bit stream.

The encoded data output from the inner coder may be transmitted on a channel and decoded in linear time at a destination using iterative decoding techniques. The decoding techniques may be based on a Tanner graph representation of the code.

#### BRIEF DESCRIPTION OF THE DRAWINGS

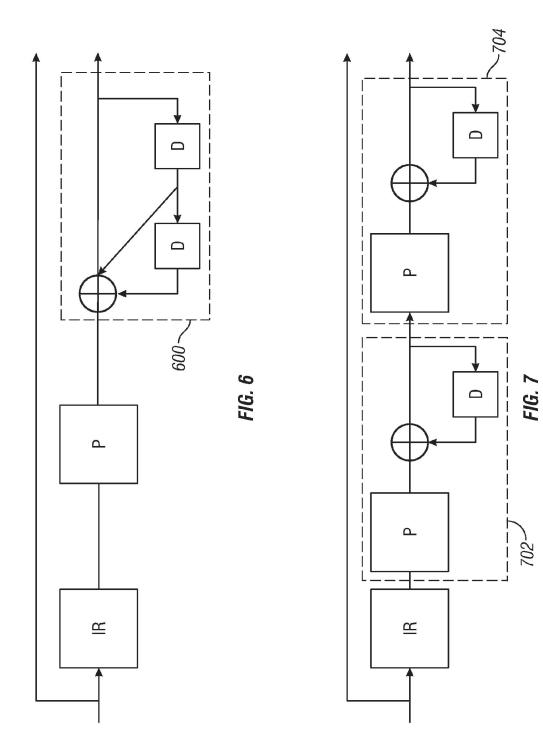

FIG. **1** is a schematic diagram of a prior "turbo code" 15 system.

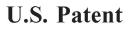

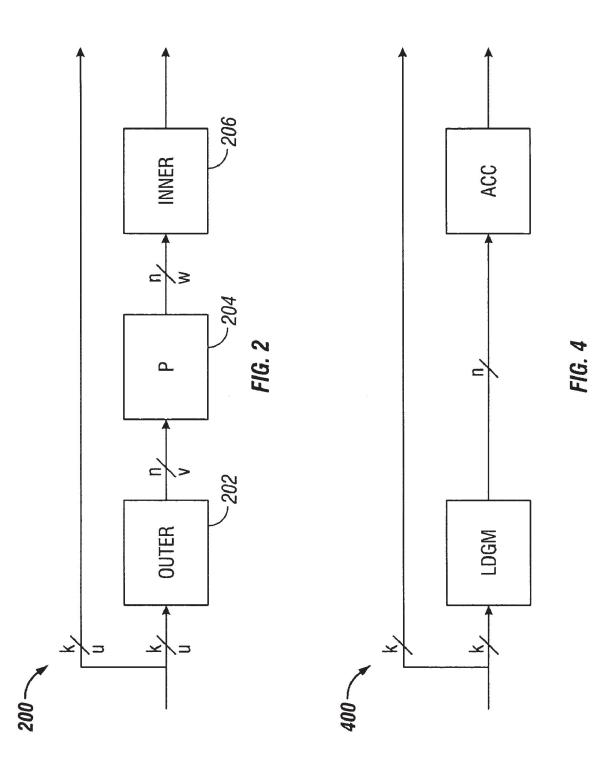

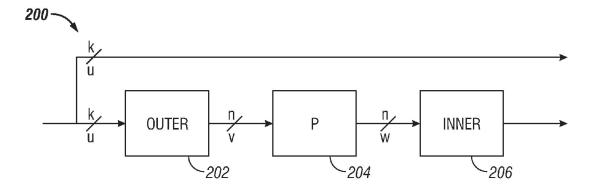

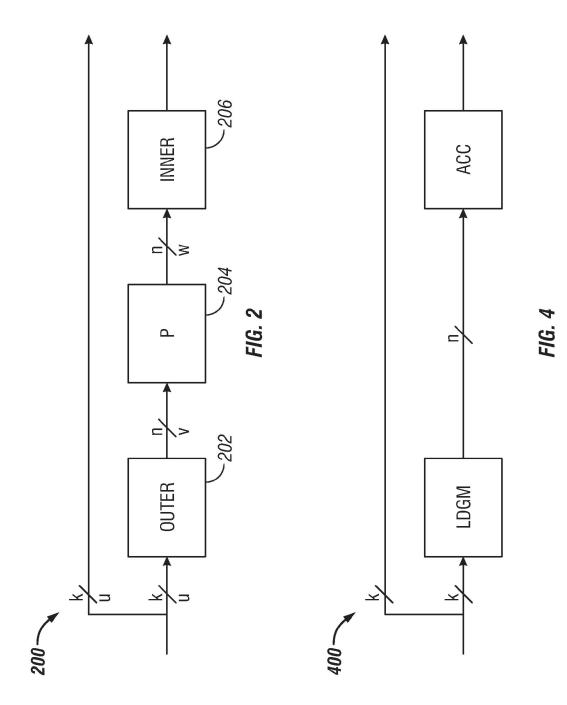

FIG. **2** is a schematic diagram of a coder according to an embodiment.

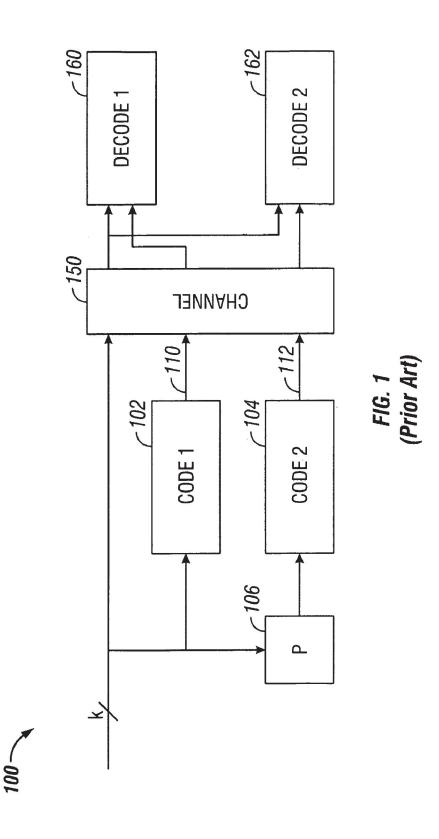

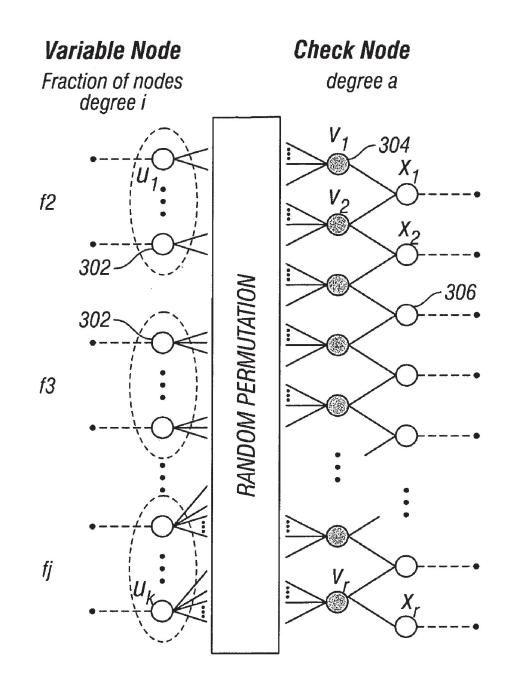

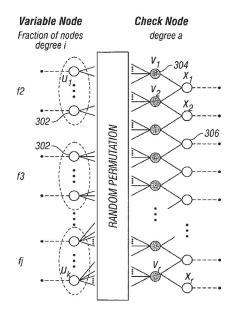

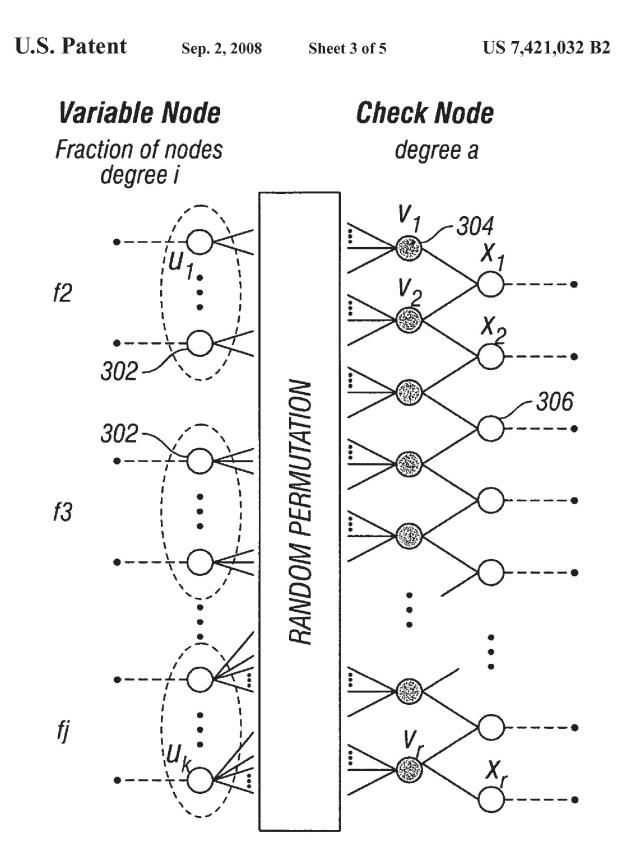

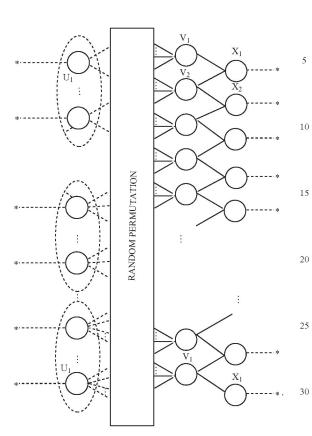

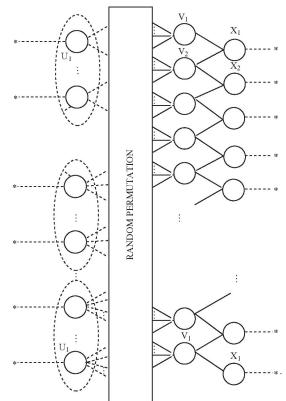

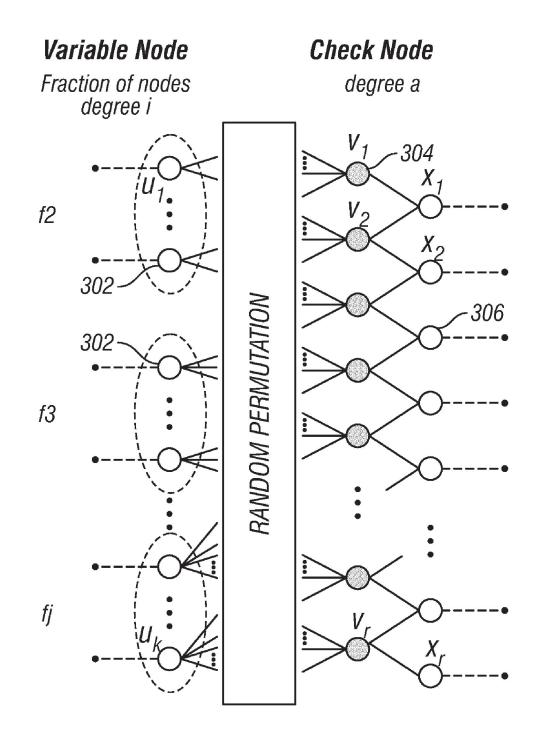

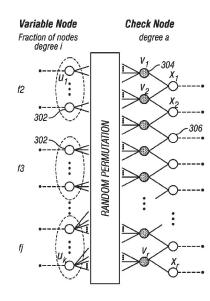

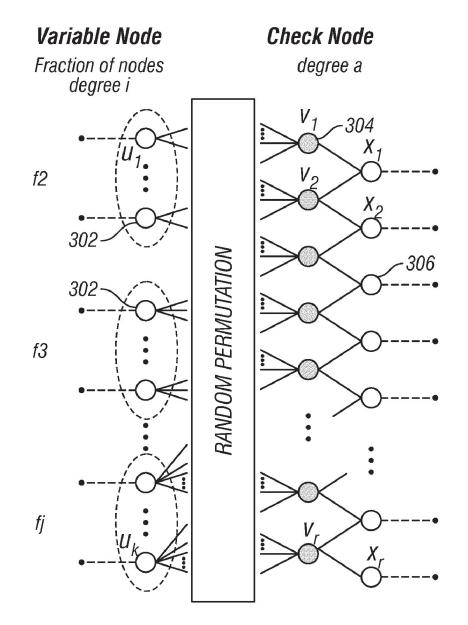

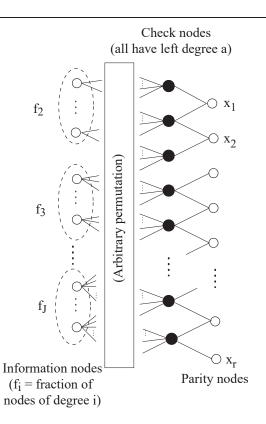

FIG. **3** is a Tanner graph for an irregular repeat and accumulate (IRA) coder.

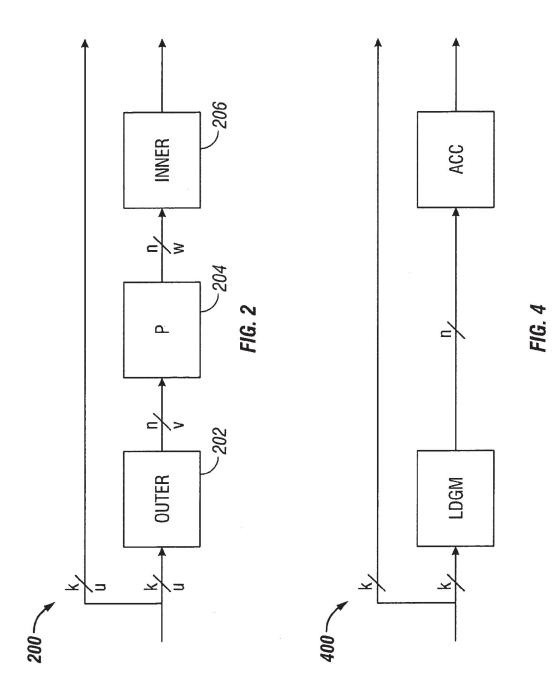

FIG. **4** is a schematic diagram of an IRA coder according to an embodiment.

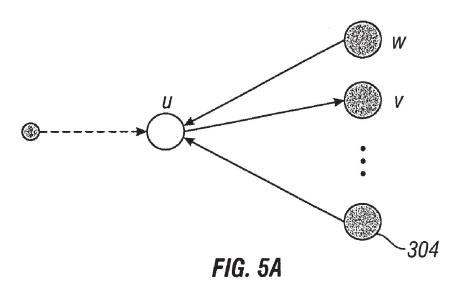

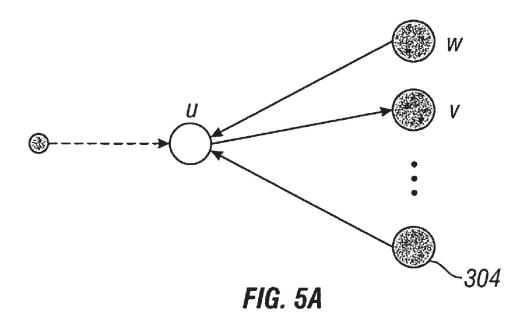

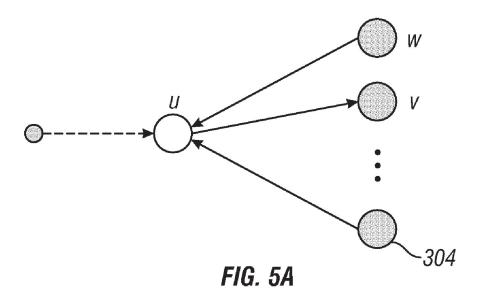

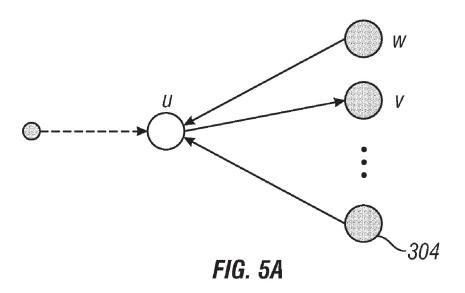

FIG. **5**A illustrates a message from a variable node to a check node on the Tanner graph of FIG. **3**.

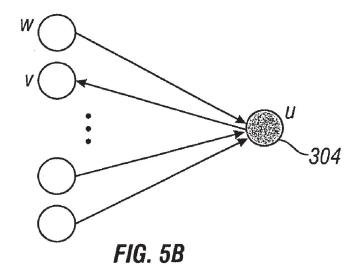

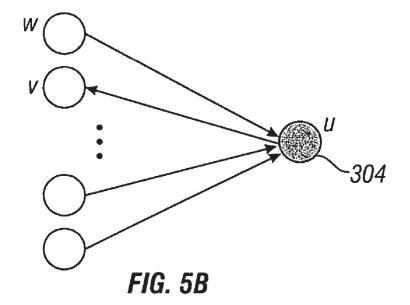

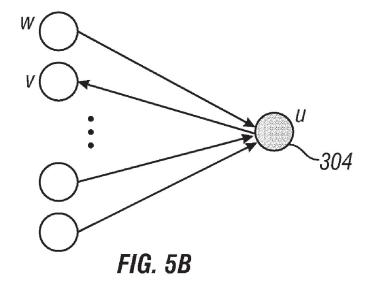

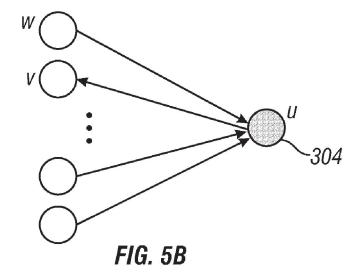

FIG. **5**B illustrates a message from a check node to a variable node on the Tanner graph of FIG. **3**.

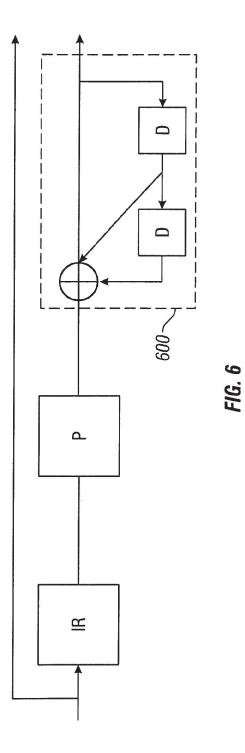

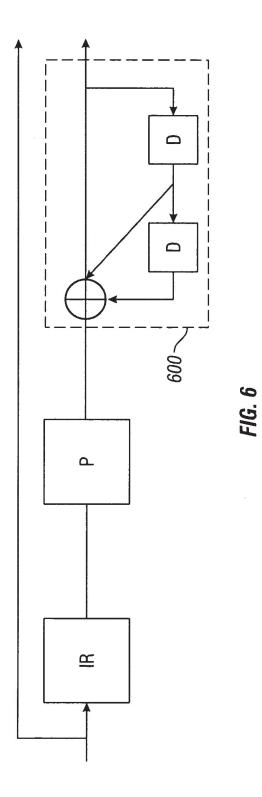

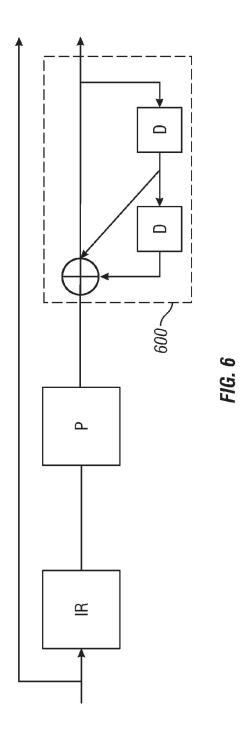

FIG. **6** is a schematic diagram of a coder according to an alternate embodiment.

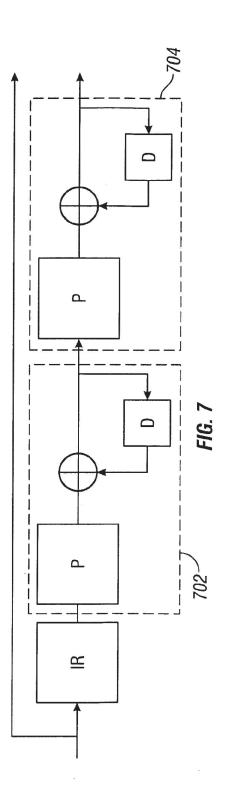

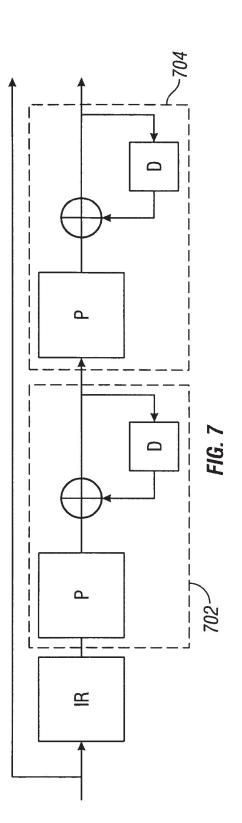

FIG. 7 is a schematic diagram of a coder according to another alternate embodiment.

#### DETAILED DESCRIPTION

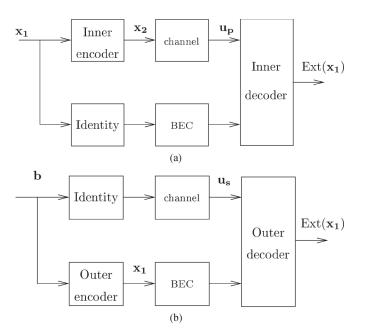

FIG. 2 illustrates a coder 200 according to an embodiment. The coder 200 may include an outer coder 202, an interleaver 204, and inner coder 206. The coder may be used to format blocks of data for transmission, introducing redundancy into the stream of data to protect the data from loss due to transmission errors. The encoded data may then be decoded at a destination in linear time at rates that may approach the channel capacity.

The outer coder **202** receives the uncoded data. The data may be partitioned into blocks of fixed size, say k bits. The outer coder may be an (n,k) binary linear block coder, where n>k. The coder accepts as input a block u of k data bits and produces an output block v of n data bits. The mathematical relationship between u and v is  $v=T_0u$ , where  $T_0$  is an n×k matrix, and the rate of the coder is k/n.

The rate of the coder may be irregular, that is, the value of  $T_0$  is not constant, and may differ for sub-blocks of bits 50 in the data block. In an embodiment, the outer coder **202** is a repeater that repeats the k bits in a block a number of times q to produce a block with n bits, where n=qk. Since the repeater has an irregular output, different bits in the block may be repeated a different number of times. For example, 55 a fraction of the bits in the block may be repeated two times, a fraction of bits may be repeated three times, and the remainder of bits may be repeated four times. These fractions define a degree sequence, or degree profile, of the code.

The inner coder **206** may be a linear rate-1 coder, which means that the n-bit output block x can be written as  $x=T_Iw$ , where  $T_I$  is a nonsingular n×n matrix. The inner coder **210** can have a rate that is close to 1, e.g., within 50%, more preferably 10% and perhaps even more preferably within 1% of 1.

In an embodiment, the inner coder **206** is an accumulator, which produces outputs that are the modulo two (mod-2) partial sums of its inputs. The accumulator may be a

5

10

truncated rate-1 recursive convolutional coder with the transfer function 1/(1+D). Such an accumulator may be considered a block coder whose input block  $[x_1, \ldots, x_n]$  and output block  $[y_1, \ldots, y_n]$  are related by the formula

$$y_1 = x_1$$

$$y_2 = x_1 \oplus x_2$$

$$y_3 = x_1 \oplus x_2 \oplus x_3$$

$y_n = x_1 \oplus x_2 \oplus x_3 \oplus \ldots \oplus x_n$

where "

"

denotes mod-2, or exclusive-OR (XOR), addition. An advantage of this system is that only mod-2 addition is necessary for the accumulator. The accumulator may be 15 embodied using only XOR gates, which may simplify the design.

The bits output from the outer coder 202 are scrambled before they are input to the inner coder 206. This scrambling may be performed by the interleaver 204, which performs a  $_{20}$ pseudo-random permutation of an input block v, yielding an output block w having the same length as v.

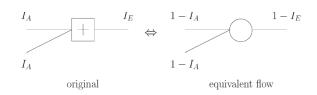

The serial concatenation of the interleaved irregular repeat code and the accumulate code produces an irregular repeat and accumulate (IRA) code. An IRA code is a linear 25 code, and as such, may be represented as a set of parity checks. The set of parity checks may be represented in a bipartite graph, called the Tanner graph, of the code. FIG. 3 shows a Tanner graph 300 of an IRA code with parameters  $(f_1, \ldots, f_i; a)$ , where  $f_i \ge 0$ ,  $\sum_i f_i = 1$  and "a" is a positive  $_{30}$ integer. The Tanner graph includes two kinds of nodes: variable nodes (open circles) and check nodes (filled circles). There are k variable nodes 302 on the left, called information nodes. There are r variable nodes 306 on the right, called parity nodes. There are  $r = (k \Sigma_i i f_i)/a$  check nodes  $_{35}$  exactly one  $f_i$  equal to 1, say  $f_{\alpha} = 1$ , and the rest zero, in which 304 connected between the information nodes and the parity nodes. Each information node 302 is connected to a number of check nodes 304. The fraction of information nodes connected to exactly i check nodes is  $f_i$ . For example, in the Tanner graph 300, each of the  $f_2$  information nodes are  $_{40}$ connected to two check nodes, corresponding to a repeat of q=2, and each of the  $f_3$  information nodes are connected to three check nodes, corresponding to q=3.

Each check node 304 is connected to exactly "a" information nodes 302. In FIG. 3, a=3. These connections can be 45 made in many ways, as indicated by the arbitrary permutation of the ra edges joining information nodes 302 and check nodes 304 in permutation block 310. These connections correspond to the scrambling performed by the interleaver 204. 50

In an alternate embodiment, the outer coder 202 may be a low-density generator matrix (LDGM) coder that performs an irregular repeat of the k bits in the block, as shown in FIG. 4. As the name implies, an LDGM code has a sparse (low-density) generator matrix. The IRA code produced by 55 the coder 400 is a serial concatenation of the LDGM code and the accumulator code. The interleaver 204 in FIG. 2 may be excluded due to the randomness already present in the structure of the LDGM code.

If the permutation performed in permutation block 310 is 60 fixed, the Tanner graph represents a binary linear block code with k information bits  $(u_1, \ldots, u_k)$  and r parity bits  $(x_1, \ldots, u_k)$  $x_r$ ), as follows. Each of the information bits is associated with one of the information nodes 302, and each of the parity bits is associated with one of the parity nodes 306. The value 65 of a parity bit is determined uniquely by the condition that the mod-2 sum of the values of the variable nodes connected

to each of the check nodes 304 is zero. To see this, set  $x_0=0$ . Then if the values of the bits on the ra edges coming out the permutation box are  $(v_1, \ldots, v_{ra})$ , then we have the recursive formula

$$x_j = x_{j-1} + \sum_{i=1}^{\lambda} v_{(j-1)\lambda+i}$$

for  $j=1, 2, \ldots, r$ . This is in effect the encoding algorithm.

Two types of IRA codes are represented in FIG. 3, a nonsystematic version and a systematic version. The nonsystematic version is an (r,k) code, in which the codeword corresponding to the information bits  $(u_1, \ldots, u_k)$  is  $(x_1, \ldots, u_k)$ x,.). The systematic version is a (k+r, k) code, in which the codeword is  $(u_1, ..., u_k; x_1, ..., x_r)$ .

The rate of the nonsystematic code is

$$R_{nsys} = \frac{a}{\sum_{i} if_i}$$

The rate of the systematic code is

$$R_{sys} = \frac{a}{a + \sum_{i} if_i}$$

For example, regular repeat and accumulate (RA) codes can be considered nonsystematic IRA codes with a=1 and case  $R_{nsvs}$  simplifies to  $R=1/\hat{q}$ .

The IRA code may be represented using an alternate notation. Let  $\lambda_i$  be the fraction of edges between the information nodes 302 and the check nodes 304 that are adjacent to an information node of degree i, and let  $\rho_i$  be the fraction of such edges that are adjacent to a check node of degree i+2 (i.e., one that is adjacent to i information nodes). These edge fractions may be used to represent the IRA code rather than the corresponding node fractions. Define  $\lambda(x)=\Sigma_i\lambda_ix^{i-1}$  and  $\rho(\mathbf{x}) = \sum_i \rho_i \mathbf{x}^{i-1}$  to be the generating functions of these sequences. The pair  $(\lambda, \rho)$  is called a degree distribution. For  $L(\mathbf{x}) = \sum_{i} f_i \mathbf{x}_i$

$$f_i = \frac{\lambda_i / i}{\sum\limits_i \lambda_j / j}$$

#### $L(x) = \int_0^x \lambda(t) dt / \int_0^1 \lambda(t) dt$

The rate of the systematic IRA code given by the degree distribution is given by

ate =

$$\left(1 + \frac{\sum_{j} \rho_j / j}{\sum_{j} \lambda_j / j}\right)^{-1}$$

Ra

"Belief propagation" on the Tanner Graph realization may be used to decode IRA codes. Roughly speaking, the belief

propagation decoding technique allows the messages passed on an edge to represent posterior densities on the bit associated with the variable node. A probability density on a bit is a pair of non-negative real numbers p(0), p(1) satisfying p(0)+p(1)=1, where p(0) denotes the probability of the bit being 0, p(1) the probability of it being 1. Such a pair can be represented by its log likelihood ratio, m=log(p(0)/p(1)). The outgoing message from a variable node u to a check node v represents information about u, and a message from 10 a check node u to a variable node v represents information about u, as shown in FIGS. **5**A and **5**B, respectively.

The outgoing message from a node u to a node v depends on the incoming messages from all neighbors w of u except v. If u is a variable message node, this outgoing message is

$$m(u \to v) = \sum_{w \neq v} m(w \to u) + m_0(u)$$

where  $m_0(u)$  is the log-likelihood message associated with u. If u is a check node, the corresponding formula is

$$\tan h \frac{m(u \to v)}{2} = \prod_{w \neq v} \tanh \frac{m(w \to u)}{2}$$

Before decoding, the messages  $m(w \rightarrow u)$  and  $m(u \rightarrow v)$  are initialized to be zero, and  $m_0(u)$  is initialized to be the log-likelihood ratio based on the channel received information. If the channel is memoryless, i.e., each channel output <sup>35</sup> only relies on its input, and y is the output of the channel code bit u, then  $m_0(i)=\log(p(u=0|y)/p(u=1|y))$ . After this initialization, the decoding process may run in a fully parallel and local manner. In each iteration, every variable/ check node receives messages from its neighbors, and sends back updated messages. Decoding is terminated after a fixed number of iterations or detecting that all the constraints are satisfied. Upon termination, the decoder outputs a decoded sequence based on the messages  $m(u)=\Sigma w_m(w\rightarrow u)$ .

Thus, on various channels, iterative decoding only differs in the initial messages  $m_0(u)$ . For example, consider three memoryless channel models: a binary erasure channel (BEC); a binary symmetric channel (BSC); and an additive <sub>50</sub> white Gaussian noise (AGWN) channel.

In the BEC, there are two inputs and three outputs. When 0 is transmitted, the receiver can receive either 0 or an erasure E. An erasure E output means that the receiver does not know how to demodulate the output. Similarly, when 1 is transmitted, the receiver can receive either 1 or E. Thus, for the BEC,  $y \in \{0, E, 1\}$ , and

$$m_0(u) = \begin{cases} +\infty & \text{if } y = 0\\ 0 & \text{if } y = E\\ -\infty & \text{if } y = 1 \end{cases}$$

In the BSC, there are two possible inputs (0,1) and two possible outputs (0, 1). The BSC is characterized by a set of 6

conditional probabilities relating all possible outputs to possible inputs. Thus, for the BSC  $y \in \{0, 1\}$ ,

$$n_0(u) = \begin{cases} \log \frac{1-p}{p} & \text{if } y = 0\\ -\log \frac{1-p}{p} & \text{if } y = 1 \end{cases}$$

and

20

55

In the AWGN, the discrete-time input symbols X take their values in a finite alphabet while channel output symbols Y can take any values along the real line. There is assumed to be no distortion or other effects other than the addition of white Gaussian noise. In an AWGN with a Binary Phase Shift Keying (BPSK) signaling which maps 0 to the symbol with amplitude  $\sqrt{Es}$  and 1 to the symbol with amplitude  $-\sqrt{Es}$ , output y $\in$ R, then

$m_0(u)=4y\sqrt{E_s}/N_0$

where  $N_0/2$  is the noise power spectral density.

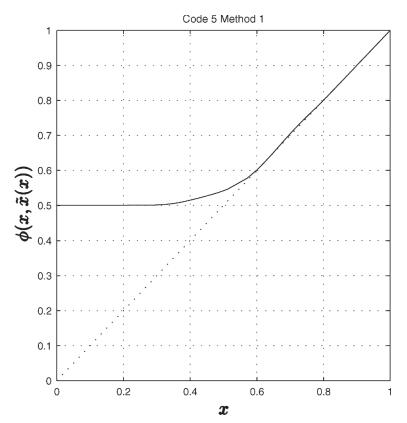

The selection of a degree profile for use in a particular transmission channel is a design parameter, which may be affected by various attributes of the channel. The criteria for selecting a particular degree profile may include, for example, the type of channel and the data rate on the channel. For example, Table 1 shows degree profiles that have been found to produce good results for an AWGN channel model.

TABLE 1

| a              | 2         | 3        | 4        |

|----------------|-----------|----------|----------|

| λ2             | 0.139025  | 0.078194 | 0.054485 |

| λ3             | 0.2221555 | 0.128085 | 0.104315 |