## IN THE UNITED STATES DISTRICT COURT FOR THE DISTRICT OF DELAWARE

**OPTIMORPHIX, INC.,**

Plaintiff,

v.

INTEL CORPORATION,

Defendant.

C.A. No. 24-1291-MN

**JURY TRIAL DEMANDED**

## FIRST AMENDED COMPLAINT FOR PATENT INFRINGEMENT

OptiMorphix, Inc. ("OptiMorphix" or "Plaintiff") brings this action and makes the following allegations of patent infringement relating to U.S. Patent Nos.: 7,099,273 (the "273 Patent"); 8,521,901 (the "901 Patent"); 10,412,388 (the "388 Patent"); 9,894,361 (the "273 Patent"); 10,123,015 (the "015 Patent"); 9,621,896 (the "896 Patent"); and 9,749,713 (the "713 Patent" and collectively, the "Patents-in-Suit"). Defendant Intel Corporation ("Intel" or "Defendant") infringes the Patents-in-Suit in violation of the patent laws of the United States of America, 35 U.S.C. § 1 *et seq.*

#### THE PARTIES

- 1. Plaintiff OptiMorphix, Inc. ("Plaintiff" or "OptiMorphix") is a Delaware corporation that holds a portfolio of over 250 patent assets that were developed at Citrix Systems, Inc. ("Citrix") and Bytemobile, Inc.

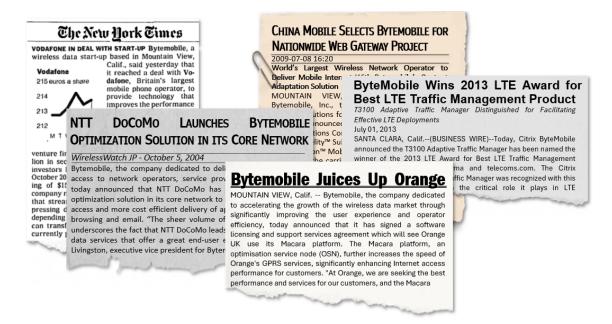

- 2. Bytemobile, Inc. ("Bytemobile") was a global leader in mobile internet solutions for network operators. The company was founded in 2000. Bytemobile's mission was to optimize video and web content services for mobile network operators to improve users' experiences while maximizing the efficiency of network infrastructure.

3. Bytemobile was established during a time when the mobile landscape was evolving rapidly. The advent of 3G technology, coupled with increasingly sophisticated smartphones, led to a surge in demand for data services. However, mobile networks at the time were not optimized to handle this influx, particularly for data-rich services like video streaming. Recognizing this opportunity, Bytemobile sought to create solutions that would enable network operators to deliver high-quality, consistent mobile data services. By 2011, Bytemobile was a "market leader in video and web optimization, with more than 125 cumulative operator deployments in 60 countries.<sup>1</sup>

Andrew Zipern, *Vodafone in Deal with Start-Up Bytemobile*, NYTimes at C4 (January 29, 2002) ("Bytemobile, a wireless data start-up . . . reached a deal with Vodafone, Britain's largest mobile phone operator"); *NTT DoCoMo Launches Bytemobile Optimization Solution in its Core Network*, WIRELESSWATCH IP (October 5, 2004) ("NTT DoCoMo has deployed Bytemobile's optimization solution in its core network"); *China Mobile Selects Bytemobile for Nationwide Web Gateway Project*, Business Wire (July 8, 2009) ("A Bytemobile customer since 2004, CMCC has deployed its web optimization solutions"); *Bytemobile Juices Up Orange*, Espicom Telecommunication News (October 10, 2002) ("Orange customers will experience faster application performance and Web page downloads"); *ByteMobile Wins 2013 LTE Award for Best LTE Traffic Management Product*, MarketScreener (July 1, 2013) ("ByteMobile technology has been deployed . . . in networks serving nearly two billion subscribers.").

-

<sup>&</sup>lt;sup>1</sup> Bytemobile: Importance of Video and Web Optimizations, Telecom Review at 58 (2011); see also Bytemobile Secures Its 36th Video Optimisation Win for MNO Deployment, Total Telecom & Total Telecom Magazine (March 21, 2011).

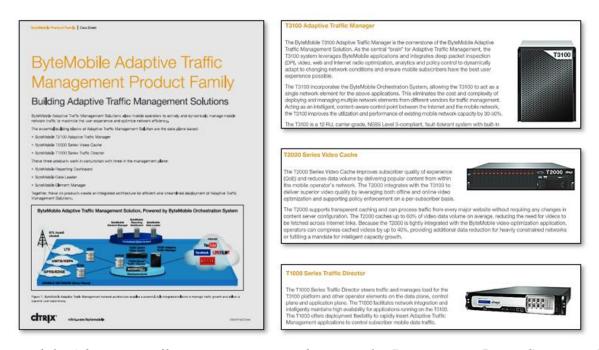

- 4. Bytemobile products, such as the Unison platform and the T3100 Adaptive Traffic Manager, were designed to optimize mobile data traffic in real-time, ensuring a high-quality mobile internet experience for end-users. This approach was groundbreaking at the time and set the stage for many of the mobile data optimization techniques used today.

- 5. Bytemobile's innovative technologies and customer-centric approach led to rapid growth and success. Bytemobile's innovative product portfolio included: the T3100 Adaptive Traffic Manager which was designed to handle high volumes of traffic efficiently and provide real-time optimization, compression, and management of mobile data; Bytemobile's T2000 Series Video Cache, which supported transparent caching of content; and Bytemobile's T1000 Series Traffic Director, which enabled traffic steering and load balancing for high availability of applications.

Bytemobile Adaptive Traffic Management Product Family, BYTEMOBILE DATA SHEET at 1-2 (2014).

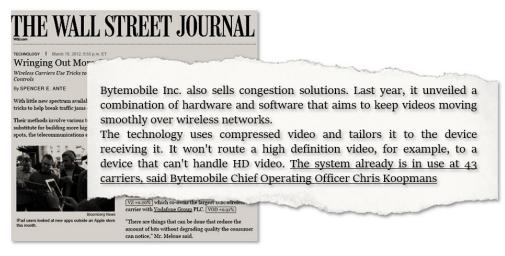

6. Bytemobile's groundbreaking technologies also included products for data optimization. Bytemobile's data optimization solutions were designed to compress and accelerate data transfer. By reducing the size of data packets without compromising quality, these technologies allowed faster data transmission and minimized network congestion. Bytemobile also offered solutions to analyze and manage network traffic, allowing network operators to identify patterns, allocate bandwidth intelligently, and prioritize different types of content.

Spencer E. Ante, *Wringing Out More Capacity*, WALL STREET JOURNAL at B3 (March 19, 2012) (emphasis added).

- 7. In July 2012, Bytemobile was acquired by Citrix Systems, Inc. ("Citrix") for \$435 million. Bytemobile "became part of [Citrix's] Enterprise division and extend[ed] [Citrix's] industry reach into the mobile and cloud markets."

- 8. OptiMorphix owns a portfolio of patents developed at Bytemobile and later Citrix. Highlighting the importance of the patents-in-suit is the fact that the OptiMorphix's patent portfolio has been cited by over 4,800 U.S. and international patents and patent applications

4

<sup>&</sup>lt;sup>2</sup> CITRIX SYSTEMS, INC. 2012 ANNUAL REPORT at 33 (2013).

assigned to a wide variety of the largest companies operating in the networking, content delivery, and cloud computing fields. OptiMorphix's patents have been cited by companies such as:

- Amazon.com, Inc. (263 citing patents and applications)<sup>3</sup>

- Oracle (59 citing patents and applications)<sup>4</sup>

- Alphabet, Inc. (103 citing patents and applications)<sup>5</sup>

- Broadcom Ltd. (93 citing patents and applications)<sup>6</sup>

- Cisco Systems, Inc. (277 citing patents and applications)<sup>7</sup>

- Lumen Technologies, Inc. (77 citing patents and applications)<sup>8</sup>

- *Intel Corporation* (49 citing patents and applications)<sup>9</sup>

- Microsoft Corporation (150 citing patents and applications)<sup>10</sup>

- AT&T, Inc. (93 citing patents and applications)<sup>11</sup>

- Verizon Communications, Inc. (31 citing patents and applications)<sup>12</sup>

- Juniper Networks, Inc. (29 citing patents and applications)<sup>13</sup>

- 9. Defendant Intel Corporation ("Intel"), is a Delaware corporation with its principal place of business at 2200 Mission College Blvd., Santa Clara, California 95054. Intel may be served through its registered agent The Corporation Trust Company, 1209 Orange Street, Wilmington, Delaware 19801.

### **JURISDICTION AND VENUE**

10. This action arises under the patent laws of the United States, Title 35 of the United States Code. Accordingly, this Court has exclusive subject matter jurisdiction over this action under 28 U.S.C. §§ 1331 and 1338(a).

<sup>&</sup>lt;sup>3</sup> See e.g., U.S. Patent Nos. 7,817,563; 9,384,204; 9,462,019; 11,343,551; and 11,394,620.

<sup>&</sup>lt;sup>4</sup> See e.g., U.S. Patent Nos. 7,475,402; 7,574,710; 8,589,610; 8,635,185; and 11,200,240.

<sup>&</sup>lt;sup>5</sup> See e.g., U.S. Patent Nos. 7,743,003; 8,458,327; 9,166,864; 9,665,617; and 10,733,376.

<sup>&</sup>lt;sup>6</sup> See e.g., U.S. Patent Nos. 7,636,323; 8,448,214; 9,083,986; 9,357,269; and 10,091,528.

<sup>&</sup>lt;sup>7</sup> See e.g., U.S. Patent Nos. 7,656,800; 7,930,734; 8,339,954; 9,350,822; and 10,284,484.

<sup>&</sup>lt;sup>8</sup> See e.g., U.S. Patent Nos. 7,519,353; 8,315,179; 8,989,002; 10,511,533; and 11,233,740.

<sup>&</sup>lt;sup>9</sup> See e.g., U.S. Patent Nos. 7,394,809; 7,408,932; 9,515,942; 9,923,821; and 10,644,961.

<sup>&</sup>lt;sup>10</sup> See e.g., U.S. Patent Nos. 8,248,944; 9,071,841; 9,852,118; 10,452,748; and 11,055,47.

<sup>&</sup>lt;sup>11</sup> See e.g., U.S. Patent Nos. 8,065,374; 8,429,302; 9,558,293; 9,800,638; and 10,491,645.

<sup>&</sup>lt;sup>12</sup> See e.g., U.S. Patent Nos. 8,149,706; 8,930,559; 9,253,231; 10,003,697; and 10,193,942.

<sup>&</sup>lt;sup>13</sup> See e.g., U.S. Patent Nos. 8,112,800; 8,509,071; 8,948,174; 9,407,726; and 11,228,631.

- 11. This Court has personal jurisdiction over Intel in this action because Intel has committed acts within the State of Delaware giving rise to this action and has established minimum contacts with this forum such that the exercise of jurisdiction over Defendant would not offend traditional notions of fair play and substantial justice. Intel, directly and/or through subsidiaries or intermediaries (including distributors, retailers, and others), has committed and continues to commit acts of infringement in this District by, among other things, offering to sell and selling products and/or services that infringe the patents-in-suit. Moreover, Intel actively directs its activities to customers located in the State of Delaware.

- 12. The Court further has personal jurisdiction over Intel because it is organized and existing under the laws of the State of Delaware and maintains a registered agent in Delaware.

- 13. Venue is proper in this District under 28 U.S.C. §§ 1391(b)-(d) and 1400(b). Defendant is organized and existing under the laws of the State of Delaware.

#### THE ASSERTED PATENTS

#### **U.S. PATENT No. 7,099,273**

- 14. U.S. Patent No. 7,099,273 entitled, *Data Transport Acceleration and Management Within a Network Communication System*, was filed on January 29, 2002. The '273 Patent is subject to a 35 U.S.C. § 154(b) term extension of 1,021 days. The '273 Patent claims priority to U.S. Provisional Patent Application No. 60/309,212 filed on July 31, 2001, and U.S. Provisional Patent Application No. 60/283,542 filed on April 12, 2001. A true and correct copy of the '273 Patent is attached hereto as Exhibit 1.

- 15. The '273 Patent has been in full force and effect since its issuance. OptiMorphix, Inc. owns by assignment the entire right, title, and interest in and to the '273 Patent.

- 16. The technologies disclosed in the '273 Patent improve the efficiency and speed of data transmission within network communication systems. The '273 Patent introduces methods and apparatuses that enhance data transport, especially in environments where network conditions are variable or unpredictable and "provide systems and method for data transport acceleration and management within a network communication system." ('273 Patent, col. 3:31-33.)

- 17. The '273 Patent is directed to solving the problem of inefficient data transport within network communication systems. This inefficiency can lead to poor utilization of network resources, increased latency, and reduced overall performance.

- 18. The '273 Patent identifies the shortcomings of the prior art. Specifically, the specification describes that traditional methods of data transport in network communication systems often fail to efficiently manage and accelerate data transport, especially in environments with variable or unpredictable network conditions. These methods may not adequately handle network congestion, leading to poor utilization of network resources, increased latency, and reduced overall performance. "This bursty nature of data transmission may under-utilize the available bandwidth on the downlink channel, and may cause some applications requiring a steady flow of data, such as audio or video, to experience unusually poor performance." ('273 Patent, col. 2:1-6.)

- 19. The '273 Patent identifies several shortcomings of the prior art, particularly in the context of the Transport Control Protocol (TCP) which is commonly used in modern data communication networks. The patent specification describes that:

Many of the problems associated with conventional TCP architectures stem from the flow control, congestion control and error recovery mechanisms used to control transmission of data over a communication network.

('273 Patent, col. 1:38-41.)

- 20. Conventional TCP architectures assume that the network employs symmetric communication channels that enable data packets and acknowledgements to be equally spaced in time. This assumption often does not hold true in networks that employ asymmetric uplink and downlink channels, such as wireless communication networks. Bursty data transmission might result in the inefficient use of the available bandwidth on the downlink channel, leading to suboptimal performance in applications that need a consistent data flow, such as those involving audio or video.

- 21. Another shortcoming identified is that conventional TCP architectures react to both random loss and network congestion by significantly and repeatedly reducing the congestion window, which can lead to significant and potentially unjustified deterioration in data throughput. This is particularly problematic in wireless and other bandwidth constrained networks where random packet loss due to fading, temporary degradation in signal quality, signal handoffs or large propagation delays occur with relatively high frequency.

- 22. The '273 Patent also points out that conventional TCP congestion control mechanisms tend to exhibit sub-optimal performance during initialization of data connections over reduced-bandwidth channels, such as wireless links. When a connection is initiated, the congestion control mechanism aggressively increases the size of the congestion window until it senses a data packet loss. This process may adversely impact other connections that share the same reduced-bandwidth channel as the connection being initialized attempts to maximize its data throughput without regard of the other pre-existing connections. This can lead to inefficient use of resources with decreased overall throughput.

- 23. The '273 Patent teaches the use of various techniques to accelerate and manage data transport in network communication systems. These techniques include the use of congestion

control mechanisms, timers, and other methods to optimize data transmission. By implementing these techniques, the patent aims to improve the efficiency of data transport, particularly in environments with variable or unpredictable network conditions. This can lead to better utilization of network resources, reduced latency, and improved overall performance. The inventions disclosed in the '273 Patent provide significant benefits and improvements to the function of the hardware in a computer network.

- 24. On March 8, 2024, Unified Patents, LLC filed a Request for *Ex Parte* Reexamination of the '273 Patent with the United States Patent and Trademark Office. The Patent Office entered an Order Granting *Ex Parte* Reexamination of the '273 Patent on April 29, 2024. On September 11, 2024, the Primary Examiner assigned to the Reexamination of the '273 Patent issued an Order confirming the patentability of all claims of the '273 patent. On November 14, 2024, the United States Patent and Trademark Office issued *Ex Parte* Reexamination Certificate No. 12770 confirming the patentability of Claims 1-15 of the '273 Patent. A true and correct copy of that Certificate is attached hereto as Exhibit 2.

- 25. The '273 Patent family has been cited by 1,466 United States and international patents and patent applications as relevant prior art. Specifically, patents issued to the following companies and research institutions have cited the '273 Patent family as relevant prior art:

- Cisco Technology, Inc.

- Qualcomm Incorporated

- International Business Machines Corporation

- Intel Corporation

- Microsoft Corporation

- Broadcom Corporation

- Google Inc.

- F5 Networks, Inc.

- Adobe Systems Incorporated

- Apple Inc.

- Lumen Technologies, Inc

- Oracle Corporation

Amazon.com, Inc.

#### **U.S. PATENT No. 8,521,901**

- 26. U.S. Patent No. 8,521,901 entitled, *TCP Burst Avoidance*, was filed on December 22, 2008. The '901 Patent claims priority to Provisional Patent Application No. 61/017,275, filed on December 28, 2007. The '901 Patent is subject to a 35 U.S.C. § 154(b) term extension of 525 days. A true and correct copy of the '901 Patent is attached hereto as Exhibit 3.

- 27. The '901 Patent has been in full force and effect since its issuance. OptiMorphix, Inc. owns by assignment the entire right, title, and interest in and to the '901 Patent.

- 28. The '901 Patent generally relates to methods and systems for minimizing packet bursts. The '901 Patent teaches implementing a packet scheduler layer between the network layer and the transport layer of a device, which smooths the delivery of TCP packets by delaying their delivery, thus addressing the challenges posed by the rapid and bursty transmission of data packets in network communications.

- 29. The '901 Patent is directed to solving the problem of TCP packet bursts in high-speed data networks, which can result from the buffering of TCP acknowledgment packets. These bursts can cause packet loss and inefficient use network bandwidth.

- 30. The '901 Patent identifies the shortcomings of the prior art. Specifically, the specification describes that the prior art does not adequately address the issues of packet loss and inefficient bandwidth utilization resulting from the bursty nature of TCP packet transmission in data networks. The prior technologies do not effectively manage the sudden bursts of TCP acknowledgment packets, which can be caused by buffering, leading to suboptimal utilization of available bandwidth and undesirable packet loss.

- 31. The '901 Patent teaches the use of a packet scheduler layer, which is positioned between the network and transport layers of a device. This layer receives, smoothens (by

delaying), and sends TCP packets to ensure that the delivery of these packets is managed in a manner that mitigates the issues of packet bursts. The packet scheduler layer manages both incoming and outgoing packets, ensuring that the transmission of these packets is smoothed out, thereby minimizing packet loss and ensuring more efficient use of available bandwidth. This approach provides benefits that differ from conventional methods by ensuring that TCP packet transmission is managed in a way that minimizes packet loss and ensures efficient bandwidth utilization, thereby addressing the specific challenges posed by TCP packet bursts in high-speed data networks.

- 32. The invention taught by the '901 Patent solves discrete, technological problems associated with computer systems; specifically, it addresses the issues of packet loss and inefficient bandwidth utilization in high-speed data networks by managing the transmission of TCP packets in a manner that smoothens their delivery, thereby ensuring that the available bandwidth is utilized efficiently, and that packet loss is minimized.

- 33. The '901 Patent family has been cited by 21 United States and international patents and patent applications as relevant prior art. Specifically, patents issued to the following companies have cited the '901 Patent family as relevant prior art:

- Lenovo Group Limited

- Telefonaktiebolaget Lm Ericsson

- Qualcomm, Inc.

- Nippon Telegraph & Telephone Corp.

- Hitachi, Ltd.

Case 1:24-cv-01291-MN

- Cisco Systems, Inc.

- Akamai Technologies, Inc.

- Huawei Technologies Co., Ltd.

#### U.S. PATENT No. 10,412,388

- 34. U.S. Patent No. 10,412,388 entitled, *Framework for Quality-Aware Video Optimization*, was filed on January 8, 2018. The '388 Patent claims priority to U.S. Patent Application No. 12/751,951, which was filed on March 31, 2010, and which claims priority to U.S. Provisional Patent Application No. 61/165,224, which was filed on March 31, 2009. A true and correct copy of the '388 Patent is attached hereto as Exhibit 4.

- 35. The '388 Patent has been in full force and effect since its issuance. OptiMorphix, Inc. owns by assignment the entire right, title, and interest in and to the '388 Patent.

- 36. The '388 Patent generally relates to a method and system for quality-aware video optimization. It teaches receiving an encoded video frame, decompressing it, extracting a first quantization parameter (QP), and acquiring a delta QP based on the first QP. The method also includes acquiring a second QP based on the delta QP and the first QP, compressing the decompressed video frame based on the second QP, and providing the compressed video frame. The process allows for fine control of quality degradation in byte-reduced content and can be applied to transcoding scenarios where the input and output compression formats are different.

- 37. The '388 Patent identifies the shortcomings of the prior art. Specifically, existing single-pass rate control techniques had a problem in that the relationship between the compressed byte size of a video frame and its quantization parameter were only known after the frame is encoded. This made it challenging to achieve byte reduction and controllable quality degradation in a single pass.

- 38. The '388 Patent teaches the use of a quality-aware video optimization technique that modifies a video frame sequence to reduce the byte size while limiting perceptual quality degradation to a controllable level.

- 39. The inventions disclosed in the '388 Patent provide significant benefits and improvements to the function of hardware in a computer network by enabling efficient video optimization. The method allows for single-pass, on-the-fly quality-aware optimization, making it well-suited for various environments, including live video feeds and storage arrays.

- 40. The '388 patent family has been cited by 30 United States and international patents and patent applications as relevant prior art. Specifically, patents issued to the following companies and research institutions have cited the '388 Patent family as relevant prior art:

- Interdigital, Inc.

- Tencent Holdings Ltd

- Microsoft Corporation

- Qualcomm, Inc.

- Lattice Semiconductor

- Openwave Mobility, Inc.

- Samsung Electronics Co., Ltd.

- Beijing Dajia Interconnection Information Technology Co., Ltd.

## **U.S. PATENT No. 9,894,361**

- 41. U.S. Patent No. 9,894,361 entitled, *Framework for Quality-Aware Video Optimization*, was filed on March 31, 2010. The '361 Patent claims priority to U.S. Provisional Application No. 61/165,224, which was filed on March 31, 2009. The '361 Patent is subject to a 35 U.S.C. § 154(b) term extension of 1,038 days. A true and correct copy of the '361 Patent is attached hereto as Exhibit 5.

- 42. The '361 Patent has been in full force and effect since its issuance. OptiMorphix, Inc. owns by assignment the entire right, title, and interest in and to the '361 Patent.

- 43. The '361 Patent relates to a method and system for quality-aware video optimization. Specifically, it teaches receiving an encoded video frame, decompressing it, extracting a first quantization parameter (QP), and acquiring a delta QP based on the first QP. The method further includes acquiring a second QP based on the delta QP and the first QP, compressing

the decompressed video frame based on the second QP, and providing the compressed video frame. The process is designed to reduce the byte size of the video stream as much as possible while limiting perceptual quality degradation to a controllable level.

- 44. The '361 Patent is directed to solving the problem of optimizing video quality in a way that balances the reduction of byte size with the preservation of perceptual quality. This involves a nuanced understanding of how quantization parameters (QPs) affect both the perceptual quality and the bitrate of a video frame, and how to manipulate these QPs to achieve the desired balance.

- 45. The '361 Patent identifies the shortcomings of the prior art. Specifically, existing single-pass rate control techniques had a problem in that the relationship between the compressed byte size of a video frame and its quantization parameter was only known after the frame was encoded. This made it challenging to achieve byte reduction and controllable quality degradation in a single pass.

- 46. The '361 Patent teaches the use of a quality-aware video optimization technique that requires only a single pass over the previously encoded video frame sequence to optimize the video frame sequence. It introduces a novel function that defines  $\Delta QP$  according to the value of QPInput, allowing fine control of quality degradation in the byte-reduced content. It also considers differences between input and output compression formats (codecs) and computes codec adjustment that accounts for these differences.

- 47. The inventions disclosed in the '361 Patent provide significant benefits and improvements to the function of hardware in a computer network by enabling efficient video optimization. By allowing for single-pass, on-the-fly, quality-aware optimization, the patent's methods can be applied in various environments, including optimizing live video feeds before they

traverse a low-capacity network segment, or optimizing surveillance video before archiving, thus saving storage space and network bandwidth.

- 48. The '361 Patent family has been cited by 30 United States and international patents and patent applications as relevant prior art. Specifically, patents issued to the following companies and research institutions have cited the '361 Patent family as relevant prior art:

- Interdigital, Inc.

- Tencent Holdings Ltd

- Microsoft Corporation

- Qualcomm, Inc.

- Lattice Semiconductor

- Openwave Mobility, Inc.

- Samsung Electronics Co., Ltd.

- Beijing Dajia Interconnection Information Technology Co., Ltd.

#### **U.S. PATENT NO. 10,123,015**

- 49. U.S. Patent No. 10,123,015 entitled, *Macroblock-Level Adaptive Quantization in Quality-Aware Video Optimization*, was filed on April 10, 2017. The '015 Patent claims priority to U.S. Application No. 13/492,619, which was filed on June 8, 2012, and which issued as U.S. Patent No. 9,621,896. The '015 Patent claims priority to U.S. Provisional Application No. 61/495,951, which was filed on June 10, 2011. A true and correct copy of the '015 Patent is attached hereto as Exhibit 6.

- 50. The '015 Patent has been in full force and effect since its issuance. OptiMorphix, Inc. owns by assignment the entire right, title, and interest in and to the '015 Patent.

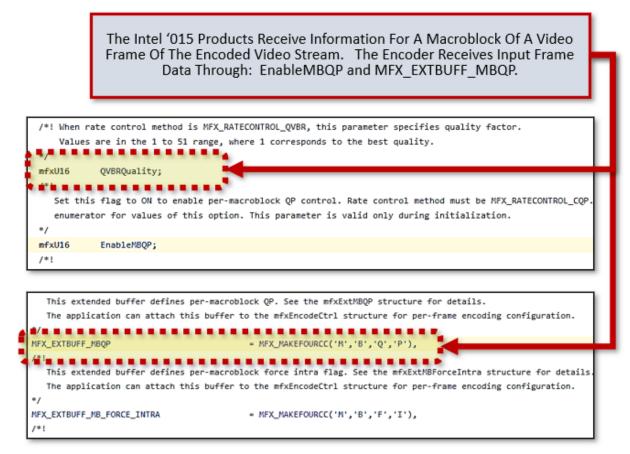

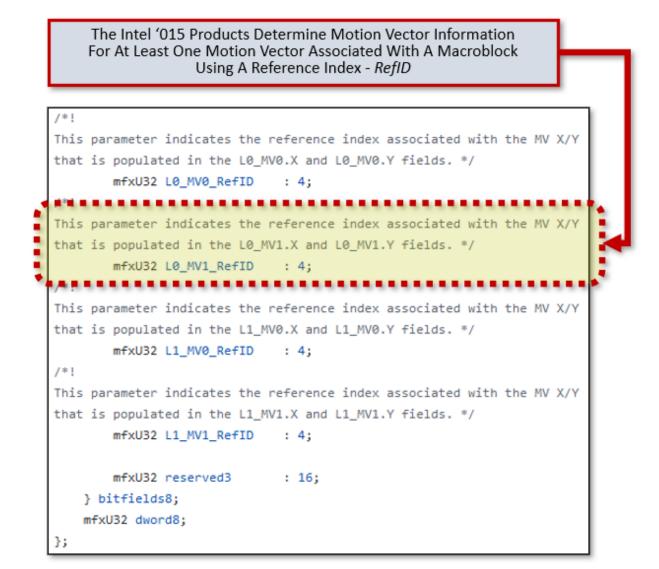

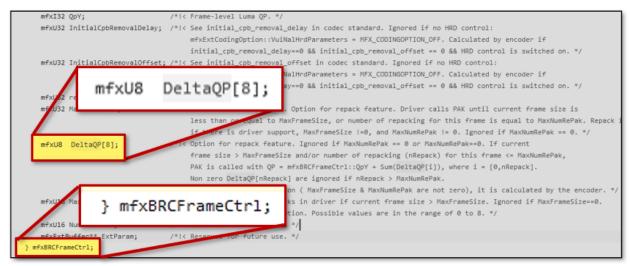

- 51. The '015 Patent teaches systems and methods for macroblock-level quality-aware video optimization. Unlike traditional methods that apply uniform compression settings across video frames, this approach focuses on adjusting compression at the macroblock level—small sections of a video frame. By analyzing each macroblock's visual and compression characteristics,

the system dynamically determines the appropriate quantization parameter (QP) to optimize the balance between file size and visual quality.

- 52. The technologies taught in the '015 Patent address the challenge of efficiently compressing video while preserving critical details, especially in regions with high visual complexity. Traditional methods fail to account for differences within a frame, leading to unnecessary quality degradation or inefficient compression. By tailoring QP settings to individual macroblocks, this system ensures better preservation of important visual elements, such as faces or text, while reducing the overall data size.

- 53. The '015 Patent provides significant benefits and improvements to the function of the hardware in a computer network by significantly reducing the necessary bitrate necessary to transmit video data with minimal perceptual quality loss. This is critical for computer networks to be able to deliver live-streamed video content and to deliver video content through low-bandwidth networks.

- 54. The '015 Patent has been cited by at least 29 United States and international patents and patent applications as relevant prior art. Specifically, patents issued to the following companies and research institutions have cited the '015 Patent family as relevant prior art:

- Microsoft Technology Licensing, LLC

- Google LLC

- Apple Inc.

- Samsung Electronics Co., Ltd.

- Qualcomm Incorporated

- Netflix, Inc.

- Sharp Corporation

- Tencent Technology (Shenzhen) Co., Ltd.

- Huawei Technologies Co., Ltd.

- Magnum Semiconductor, Inc.

- Integrated Device Technology, Inc.

#### U.S. PATENT No. 9,621,896

Case 1:24-cv-01291-MN

- 55. U.S. Patent No. 9,621,896 entitled, *Macroblock-Level Adaptive Quantization in Quality-Aware Video Optimization*, was filed on June 8, 2012. The '896 Patent claims priority to U.S. Provisional Application No. 61/495,951, which was filed on June 10, 2011. A true and correct copy of the '896 Patent is attached hereto as Exhibit 8.

- 56. The '896 Patent has been in full force and effect since its issuance. OptiMorphix, Inc. owns by assignment the entire right, title, and interest in and to the '896 Patent.

- 57. The '896 Patent relates to macroblock-level quality-aware video optimization, a method for improving video compression efficiency while maintaining perceptual quality. The '896 Patent discloses technologies for decoding video frames into small pixel blocks (macroblocks), analyzing visual and compression characteristics, and dynamically adjusting the quantization parameter (QP) for each block to optimize quality and file size.

- 58. The '896 Patent addresses the challenge of compressing video streams effectively without degrading user experience. Traditional methods apply uniform compression across entire frames, leading to unnecessary quality loss in detailed regions or excessive data usage in simpler regions. The technologies disclosed in the '896 Patent introduce precise control at the macroblock level, balancing file size reduction with quality retention.

- 59. One key benefit of the technologies disclosed in the '896 Patent that is important to the ubiquitousness of the distribution of video content over the internet and cellular networks is the ability to improve important visual details while minimizing the bandwidth necessary to transmit the video data.

- 60. The '896 Patent has been cited by at least 29 United States and international patents and patent applications as relevant prior art. Specifically, patents issued to the following companies and research institutions have cited the '896 Patent family as relevant prior art:

- Microsoft Technology Licensing, LLC

- Apple Inc.

- Qualcomm Incorporated

- Netflix, Inc.

- Google LLC

- Sharp Kabushiki Kaisha

- Huawei Technologies Co., Ltd.

- Magnum Semiconductor, Inc.

- Tencent Technology (Shenzhen) Co., Ltd.

- Integrated Device Technology, Inc.

#### **U.S. PATENT No. 9,749,713**

- 61. U.S. Patent No. 9,749,713 entitled, *Budget Encoding*, was filed on October 15, 2009. The '713 Patent claims priority to U.S. Patent Application No. 12/580,212, which was filed on October 15, 2009. The '713 Patent is subject to a 35 U.S.C. § 154(b) term extension of 1654 days. A true and correct copy of the '713 Patent is attached hereto as Exhibit 9.

- 62. The '713 Patent has been in full force and effect since its issuance. OptiMorphix, Inc. owns by assignment the entire right, title, and interest in and to the '713 Patent.

- 63. The '713 Patent is directed to solving the problem of inefficient allocation and management of network resources. Traditional methods often fail to prioritize applications effectively, leading to suboptimal performance for critical applications and inefficient utilization of network resources.

- 64. The '713 Patent identifies the shortcomings of the prior art. Specifically, existing systems lacked the ability to dynamically allocate resources based on real-time needs and priorities of applications. This leads to either over-provisioning, which wastes resources, or underprovisioning, which can cause critical applications to suffer or fail.

- 65. The '713 Patent teaches the use of a resource manager that dynamically allocates network resources to applications based on a set of defined policies and priority levels. It involves continuous monitoring of the network and applications, and the resource manager makes real-time

decisions to allocate or deallocate resources as needed. This ensures that critical applications always have the necessary resources, while other applications receive resources as available.

- 66. The inventions disclosed in the '713 Patent provide significant benefits and improvements to the function of the hardware in a computer network. By implementing a dynamic, policy-driven approach to resource allocation, the system ensures optimal performance for critical applications and efficient utilization of network resources. This leads to improved overall network performance, reduced waste, and the ability to adapt to changing conditions and demands.

- 67. The '713 Patent family has been cited by 41 United States and international patents and patent applications as relevant prior art. Specifically, patents issued to the following companies and research institutions have cited the '713 Patent family as relevant prior art:

- Samsung Electronics Co., Ltd.

- Openwave Mobility, Inc.

- Huawei Investment & Holding Co., Ltd.

- Cisco Systems, Inc.

- Flash Networks Ltd.

- ZTE Corporation

- Vizio, Inc.

- Wangsu Science & Technology Co., Ltd.

- Akamai Technologies, Inc.

- SK Telecom Co., Ltd.

- Sugon Information Industry(Beijing) Co., Ltd.

- Netscout Systems, Inc.

- Microsoft Corporation

- Telefonaktiebolaget Lm Ericsson

# COUNT I INFRINGEMENT OF U.S. PATENT No. 7,099,273

68. Plaintiff references and incorporates by reference the preceding paragraphs of this Complaint as if fully set forth herein.

- 69. Intel designs, makes, uses, sells, and/or offers for sale in the United States products comprising systems and methods for data transport acceleration and management within a network communication system.

- 70. Intel designs, makes, sells, offers to sell, imports, and/or uses software, including but not limited to versions of the Linux kernel (version 4.9 and later) incorporating TCP-BBR congestion control algorithms, Intel designs, makes, sells, offers to sell, imports, and/or uses processors, networking hardware, and other computing devices designed, marketed, or distributed for use with software employing TCP-BBR congestion control algorithms (this includes but is not limited to Intel's processors, chipsets, and other hardware components that are integrated with or otherwise configured to operate with the Linux kernel supporting TCP-BBR) (collectively, the "Intel '273 Product(s)").

- 71. One or more Intel subsidiaries and/or affiliates use the Intel '273 Products in regular business operations.

- 72. One or more of the Intel '273 Products include technology that performs the step of establishing a data connection between a sender and receiver using a handshake process. Specifically, the Intel '273 Products perform TCP-BBR congestion control.

```

/* BBR has the following modes for deciding how fast to send: */

enum bbr_mode {

BBR STARTUP,

/* ramp up sending rate rapidly to fill pipe */

81

BBR_DRAIN,

/* drain any queue created during startup */

82

BBR_PROBE_BW,

/* discover, share bw: pace around estimated bw

83

BBR_PROBE_RTT, /* cut inflight to min to probe min_rtt */

85

/* BBR congestion control block */

86

struct bbr {

87

88

u32

min_rtt_us;

/* min RTT in min_rtt_win_sec window */

89

min_rtt_stamp;

/* timestamp of min_rtt_us */

u32

probe_rtt_done_stamp;

/* end time for BBR_PROBE_RTT mode */

90

u32

91

struct minmax bw;

/* Max recent delivery rate in pkts/uS << 24 */

/* count of packet-timed rounds elapsed */

92

rtt_cnt;

u32

93

u32

next_rtt_delivered; /* scb->tx.delivered at end of round */

94

u64

cycle_mstamp;

/* time of this cycle phase start */

95

u32

mode:3,

/* current bbr mode in state machine */

```

*Intel Linux LTS – tcp\_bbr.c*, INTEL GITHUB REPOSITORY (November 2024), *available at:* https://github.com/intel/linux-intel-lts (emphasis added).

- 73. The Intel '273 Products send a TCP packet with the SYN (Synchronize) flag set to the server. This packet contains an initial sequence number (ISN), which helps the server and client synchronize their sequence numbers. The ISN used by the Intel '273 Products are represented as "x." Upon receiving the SYN packet, the Intel '273 Products sends a TCP packet back with both the SYN and ACK flags set. This packet contains two pieces of information: the responsive ISN, usually represented as 'y,' and an acknowledgment number, which is the ISN plus one (x+1). The acknowledgment number is used to confirm that the sender has received the SYN packet.

- 74. In establishing a connection between the sender and the receiver after receiving the SYN-ACK packet, the Intel '273 Products send another packet with the ACK flag set. This packet contains an acknowledgment number, which is the ISN plus one (y+1).

- 75. The Intel '273 Products measure round trip times (RTT) of data packets sent from the sender to the receiver. Specifically, the Intel '273 Products measure the round-trip propagation time (RTprop) using the minimum round-trip time (RTT) for the connection by keeping track of the lowest observed RTT in the recent past. This value represents the round-trip propagation time (RTprop) of the connection.

- 76. The Intel '273 Products perform timestamping. Specifically, when a Intel '273 Product transmits a data packet, it records the current time as a timestamp. The timestamp is stored in the transmission control block (TCB), which maintains the state of the TCP connection, including RTT measurements and other relevant information.

- 77. The Intel '273 Products perform acknowledgment processing. Specifically, the Intel '273 Products send an acknowledgment (ACK) for a specific packet, the sender processes the ACK and identifies the corresponding packet in the TCB. By matching the ACK with the original packet, the Intel '273 Products retrieve the original timestamp associated with that packet.

- 78. The Intel '273 Products perform a round-trip time (RTT) calculation. Specifically, the Intel '273 Products calculate the RTT for a specific packet by subtracting the original timestamp from the current time when the ACK is received. This gives an individual RTT sample for that packet as explained in the below excerpt.

$\textbf{Model} \ \text{network, update windowed} \ \textbf{max BW and min RTT estimates on each ACK}$

Control sending based on the model, to...

Probe both max BW and min RTT, to feed the model samples

Pace near estimated BW, to reduce queues and loss [move queue to sender]

Vary pacing rate to keep inflight near BDP (for full pipe but small queue)

That's BBR congestion control:

BBR = Bottleneck Bandwidth and Round-trip propagation time

BBR seeks high tput with small queue by probing BW and RTT sequentially

Neal Cardwell, Yunchung Cheng, et al., *BBR Congestion Control*, GOOGLE IETF 97: SEOUL PRESENTATION at 9 (November 2016) (emphasis added) (describing RTT\_sample = ACK\_receive\_time - original\_timestamp).

- 79. The Intel '273 Products perform the step of MinRTT estimation. Specifically, the Intel '273 Products maintain a running estimate of the minimum RTT observed (MinRTT) over a specified time window. The MinRTT is used by the Intel '273 Products to estimate the base round-trip propagation time without queuing delay. When a new RTT sample is calculated, the Intel '273 Products compare it with the current MinRTT value. If the new sample is lower than the existing MinRTT, the Intel '273 Products update MinRTT with a new value.

- 80. The Intel '273 Products perform round-trip time-based pacing. Specifically, the Intel products use the MinRTT estimate in performing pacing rate and congestion window calculations to ensure the sending rate is adapted based on the observed network conditions. BBR's pacing rate and congestion window calculations factor in the MinRTT value to maintain a balance between efficient data transfer and minimal congestion.

To match the packet-arrival rate to the bottleneck link's departure rate, BBR paces every data packet. BBR must match the bottleneck rate, which means pacing is integral to the design and fundamental to operation—pacing\_rate is BBR's primary control parameter. A secondary parameter, cwnd\_gain, bounds inflight to a small multiple of the BDP to handle common network and receiver pathologies (see the later section on Delayed and Stretched ACKs). Conceptually, the TCP send routine looks like the following code. (In Linux, sending uses the efficient FQ/pacing queuing discipline, which gives BBR line-rate single-connection performance on multigigabit links and handles thousands of lower-rate paced connections with negligible CPU overhead.)

Neal Cardwell, Yuchung Cheng, C. Stephen Gunn, Soheil Hassas Yeganeh, Van Jacobson, *BBR: Congestion-Based Congestion Control*, ACM Queue, Sep/Oct 2016 and CACM, Feb 2017 (emphasis added).

81. The Intel '273 Products determine a congestion window parameter that specifies a maximum number of unacknowledged data packets that may be sent to the receiver. The Intel '273 Products determine a congestion window parameter that limits unacknowledged data packets. In the Intel '273 Products, this parameter is called cwnd (congestion window) and is a key component of the Intel '273 Products' congestion control. The primary function responsible for determining the congestion window is bbr\_set\_cwnd(), which is called from the main control function bbr\_main().

*Intel LTS - tcp\_bbr.c*, INTEL GITHUB SOURCE CODE REPOSITORY, *available at:* https://github.com/intel/linux-intel-lts/net/ipv4/tcp\_bbr.c (last visited February 2025) (emphasis added).

- 82. The congestion window is calculated based on several factors by the Intel '273 Products. These factors include: (1) the bandwidth-delay product (BDP) via the bbr\_bdp() function, which multiplies the estimated bandwidth by the minimum RTT; (2) additional buffer for ACK aggregation via bbr\_ack\_aggregation\_cwnd(); and (3) quantization adjustments via bbr\_quantization\_budget() to handle packet boundaries and delayed ACKs. The Intel '273 Products determine a congestion window which controls the maximum number of unacknowledged packets allowed in flight.

- 83. The Intel '273 Products determine a congestion window parameter (cwnd) that limits the unacknowledged data packets in transit. This parameter is not determined by setting a specific parameter for the maximum number of unacknowledged packets. Instead, the Intel '273 Products calculate the congestion window based on network characteristics. The determination of the congestion control parameter based on network conditions is shown in the below excerpt from Intel's source code.

```

3

* BBR congestion control computes the sending rate based on the delivery

4

rate (throughput) estimated from ACKs. In a nutshell:

5

6

On each ACK, update our model of the network path:

7

bottleneck_bandwidth = windowed_max(delivered / elapsed, 10 round trips)

8

min_rtt = windowed_min(rtt, 10 seconds)

9

a pacing make as aparing again in both langch handwidth a a

cwnd = max(cwnd_gain * bottleneck_bandwidth * min_rtt, 4)

10

11

12

* The core algorithm does not react directly to packet losses or delays,

13

* although BBR may adjust the size of next send per ACK when loss is

* observed, or adjust the sending rate if it estimates there is a

14

15

* traffic policer, in order to keep the drop rate reasonable.

```

*Intel LTS - tcp\_bbr.c*, INTEL GITHUB SOURCE CODE REPOSITORY, *available at:* https://github.com/intel/linux-intel-lts/net/ipv4/tcp\_bbr.c (last visited February 2025) (emphasis added).

- 84. The Intel '273 Products determine a congestion window parameter using bbr\_set\_cwnd(). The Intel products determine this parameter using the: bandwidth-delay product (BDP): target\_cwnd = bbr\_bdp(sk, bw, gain); additional buffer for ACK aggregation: target\_cwnd += bbr\_ack\_aggregation\_cwnd(sk); and quantization adjustments: target\_cwnd = bbr\_quantization\_budget(sk, target\_cwnd, gain). Thus, the Intel '273 products determine the congestion window parameter based on estimated network conditions rather than being directly set as a fixed parameter.

- 85. The Intel '273 Products calculate a pacing rate based on these estimates to determine how quickly it should transmit data.

- 86. The Intel '273 Products transmit additional data packets to the receiver in response to expiration of a transmit timer, the period of the transmit timer based on the round trip time measurements and the congestion window parameter.

- 87. Intel has directly infringed and continues to directly infringe the '273 Patent by, among other things, making, using, offering for sale, and/or selling technology for transferring

data from a sender to a receiver in a communication network, including but not limited to the Intel '273 Products.

- 88. The Intel '273 Products are available to businesses and individuals throughout the United States.

- 89. The Intel '273 Products are provided to businesses and individuals located in this District.

- 90. By making, using, testing, offering for sale, and/or selling products and services for transferring data from a sender to a receiver in a communication network, including but not limited to the Intel '273 Products, Intel has injured Plaintiff and is liable to Plaintiff for directly infringing one or more claims of the '273 Patent, including at least claim 1 pursuant to 35 U.S.C. § 271(a).

- 91. Intel also indirectly infringes the '273 Patent by actively inducing infringement under 35 U.S.C. § 271(b).

- 92. Intel has had knowledge of the '273 Patent since at least March 23, 2010, when U.S. Patent No. 7,684,319, which is owned by Intel and cites the '273 Patent family as relevant prior art, was issued. Alternatively, Intel has had knowledge of the '273 Patent since at least December 5, 2013, when U.S. Patent Appl. No. 13/899,935, which is owned by Intel and cites the '273 Patent family as relevant prior art, was published. Alternatively, Intel has had knowledge of the '273 Patent since at least December 10, 2013, when U.S. Patent No. 8,606,956, which is owned by Intel and cites the '273 Patent family as relevant prior art, was issued. Alternatively, Intel has had knowledge of the '273 Patent since at least December 6, 2016, when U.S. Patent No. 9,515,942, which is owned by Intel and cites the '273 Patent family as relevant prior art, was issued. Alternatively, Intel has had knowledge of the '273 Patent since at least July 11, 2017,

when U.S. Patent No. 9,705,964, which is owned by Intel and cites the '273 Patent family as relevant prior art, was issued.

93. Intel intended to induce patent infringement by third-party customers and users of the Intel '273 Products and had knowledge that the inducing acts would cause infringement or was willfully blind to the possibility that its inducing acts would cause infringement. Intel specifically intended and was aware that the normal and customary use of the accused products would infringe the '273 Patent. Intel performed the acts that constitute induced infringement, and would induce actual infringement, with knowledge of the '273 Patent and with the knowledge that the induced acts would constitute infringement. For example, Intel provides the Intel '273 Products that have the capability of operating in a manner that infringe one or more of the claims of the '273 Patent, including at least claim 1, and Intel further provides documentation and training materials that cause customers and end users of the Intel '273 Products to utilize the products in a manner that directly infringe one or more claims of the '273 Patent.<sup>14</sup> By providing instruction and training to

<sup>&</sup>lt;sup>14</sup> See, e.g., Intel Wireless Wi-Fi Drivers for Linux, Intel Drivers & Software Website (July 29, 2024), available at: https://www.intel.com/content/www/us/en/download/824804/intel-wirelesswi-fi-drivers-for-linux.html; Release Notes - Intel Wireless Wi-Fi Driver Package Cor87 for Linux, INTEL DOCUMENTATION (July 2024); Linux Drivers Support for Intel Killer Wireless Products, INTEL **PRODUCT** SUPPORT WEBSITE (September 16. 2022). at: https://www.intel.com/content/www/us/en/support/articles/000088040/wireless.html; Intel/LT S/net/ipv4/tcp bbr.c, INTEL GITHUB REPOSITORY (last visited November 2024), available at: https://github.com/intel/linux-intel-lts/blob/20bd5cdc7663c3b902be4c39650 ad8cdb80ac2fb/net/ipv4/tcp bbr.c; Intel/Mainline-Tracking/net/ipv4/tcp bbr.c, INTEL REPOSITORY (last visited November 2024), available at: https://github.com/intel/mainlinetracking/blob/e0582fea0d501d507dffe716dae8d99c2f8b3f2e/net/ipv4/tcp bbr.c; Intel/xdp-bpfacceleration/net/ipv4/tcp\_bbr.c, INTEL GITHUB REPOSITORY (last visited November 2024), available at: https://github.com/intel/xdp-bpfacceleration/blob/52f1250b1f735cae7daa15e38469c436c6c4f7eb/net/ipv4/tcp\_bbr.c; Pat Gelsinger and Linus Torvalds talk Linux, open source, technology and more, INTEL NEWSROOM CHANNEL (November 2022). at: https://www.youtube.com/watch?v=0m4hlWx7oRk; Linux Xeon Scalable Processors – Minimum OS Support Matrix, Intel Documentation (April 25, 2024); Intel Virtual RAID on CPU (Intel VROC) for Linux -Release Notes for Intel VROC 9.0, and Intel Documentation (June 2024); SR-IOV Configuration Guide - Intel Ethernet 800 Series on Red Hat Enterprise Linux 8 *Technical Brief Revision 1.2*, Intel Documentation (June 2021).

customers and end-users on how to use the Intel '273 Products in a manner that directly infringes one or more claims of the '273 Patent, including at least claim 1, Intel specifically intended to induce infringement of the '273 Patent. Intel engaged in such inducement to promote the sales of the Intel '273 Products, e.g., through Intel user manuals, product support, marketing materials, and training materials to actively induce the users of the accused products to infringe the '273 Patent. Accordingly, Intel has induced and continues to induce users of the accused products to use the accused products in their ordinary and customary way to infringe the '273 Patent, knowing that such use constitutes infringement of the '273 Patent.

- 94. The '273 Patent is well-known within the industry as demonstrated by multiple citations to the '273 Patent in published patents and patent applications assigned to technology companies and academic institutions. Intel is utilizing the technology claimed in the '273 Patent without paying a reasonable royalty. Intel is infringing the '273 Patent in a manner best described as willful, wanton, malicious, in bad faith, deliberate, consciously wrongful, flagrant, or characteristic of a pirate.

- 95. To the extent applicable, the requirements of 35 U.S.C. § 287(a) have been met with respect to the '273 Patent.

- 96. As a result of Intel's infringement of the '273 Patent, Plaintiff has suffered monetary damages, and seeks recovery in an amount adequate to compensate for Intel's infringement, but in no event less than a reasonable royalty for the use made of the invention by Intel together with interest and costs as fixed by the Court.

## <u>COUNT II</u> <u>INFRINGEMENT OF U.S. PATENT NO. 8,521,901</u>

97. Plaintiff references and incorporates by reference the preceding paragraphs of this Complaint as if fully set forth herein.

- 98. Intel designs, makes, uses, sells, and/or offers for sale in the United States products comprising technology for a data packet scheduler that reduces packet bursts.

- 99. Intel designs, makes, sells, offers to sell, imports, and/or uses the following products: Intel Ethernet 800 Series Network Adapters (including models: E810-2CQDA2, E810-CQDA1, E810-CQDA1 for OCP 3.0, E810-CQDA2, E810-CQDA2 for OCP 3.0, E810-CQDA2T, E810-XXVDA2, E810-XXVDA2 for OCP 3.0, E810-XXVDA4, E810-XXVDA4 for OCP 3.0, E810-XXVDA4T) and Intel Ethernet 800 Series Controllers (including models: E810-CAM1; E810-CAM2; E810-XXVAM2) (collectively, the "Intel '901 Product(s)").

- 100. One or more Intel subsidiaries and/or affiliates use the Intel '901 Products in regular business operations.

- 101. The Intel '901 Products contain a packet scheduler layer identified in Intel documentation as the "Tx-Scheduler layer." Specifically, according to Intel documentation "[t]ransmitted packets pass through different hierarchies in the network . . . reflected in the Tx-Scheduler Layers structure."

- Transmitted packets pass through different hierarchies in the network. The network hierarchies are reflected in the Tx-Scheduler layers structure. The capacity of each network unit is reflected in the rate limit and bandwidth allocation configuration of the nodes.

- Each unit in the network branch can deal with different portions of the packets.

- Typically, for the network hop, the whole packet including the IPG and the L1 header needs to be taken into account in the bandwidth calculation. Next hops, bridges, or the target station can consider a portion of the packet. For example, in tunneled environment, the target station does not see the whole packet, but only inner L4 part.

- The Tx-Scheduler is required to calculate up to four different adjustments of packets lengths for different Tx-Scheduler layers or nodes.

- The Tx-Scheduler is also required to calculate different adjustments of packets lengths for different types of packets.

INTEL ETHERNET CONTROLLER E810 DATASHEET REVISION 2.8 at § 8.3.2.4.1(September 2024) (emphasis added).

102. The Intel '901 Products implement the packet scheduler layer functionality as claimed in the '901 Patent. This packet scheduler layer operates within a first device, positioned

between the network interface layer and transport layer of the first device's networking stack. The Intel '901 Products contain the packet scheduler layer. The Intel '901 Products both receive the TCP packets and store the requisite connection data - operating as a first device.

Case 1:24-cv-01291-MN

103. The Intel '901 Products implement a packet scheduler layer on a first device. As detailed in Intel's documentation, the Intel '901 Products contain a packet scheduler layer residing between network interface and transport layers of the networking stack within the first device. The packet scheduler layer contained in the Intel '901 Products is a component within the first device that receives packets from another layer (either the network interface layer or transport layer) on that same device. As evidenced by the Intel documentation the Intel '901 Products implement packet processing pipelines that receive TCP packets from one layer and deliver them to another layer within the same computing system, functioning as the packet scheduler layer.

Once the Tx-Scheduler selects a transmit queue (either from LAN or from RDMA), it services some amount of transmit data (called a "quanta"). Packet data is read from host memory and any packet processing or packet manipulation takes place. These can include partial parsing of the packet, performing Transmit Segmentation Offload (TSO), calculating relevant checksums and CRCs, L2 header manipulations UP enforcement, and inner protocol TTL decrement.

The packet is then passed to the Packet Processing Pipeline, where it queries the on-die switch to identify its destinations. A packet can be forwarded locally to a Host destination (for example VM-VM communication) or to an on-board BMC. The packet also goes through the ACL block, where permissions are checked, and might alter the forwarding decisions made in the switch.

The LAN Controller then forwards the packet to one of the LAN ports and/or to the Receive path. If the destination port is busy, the packet is stored in a local Transmit Buffer. Transmission to a LAN port is done via a 802.3 MAC that interfaces an On-Chip Network Packet Interface (ONPI).

INTEL ETHERNET CONTROLLER E810 DATASHEET REVISION 2.8 at § 1.3.1 (September 2024) (emphasis added).

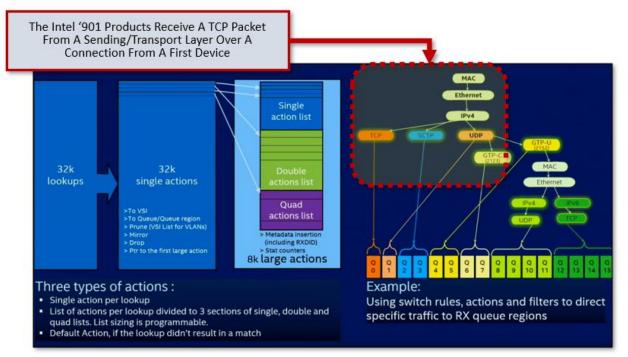

104. The Intel '901 Products receive a transmission control protocol (TCP) packet from a sending layer on the first device. The sending layer is one of the network interface layer or the transport layer and the TCP packet is sent over a connection between the first device and a second device. The receipt of TCP packets is shown in the following excerpt from an Intel presentation.

Brian Johnson and Jesse Brandeburg, *Intel Ethernet 800 Series Technical Feature Discussion*, TECH FIELD DAY YOUTUBE CHANNEL at 4:38 (October 2, 2019), *available at*: https://www.youtube.com/watch?v=T38CWUWaeto (annotation added).

- 105. Intel '901 Products contain functionality for receiving and sending TCP packets and comprise functionality for optimizing the flow of data between devices over various network paths.

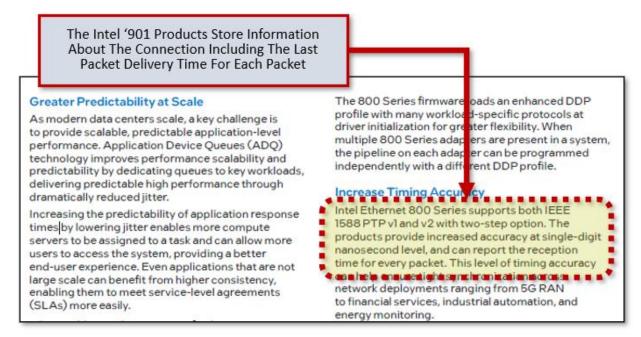

- 106. Intel '901 Products store information about the connection between a first device and the second device. The information stored by the Intel '901 Products include a last packet delivery time for the connection as shown in the below excerpt from Intel documentation of the Intel '901 Products.

*Intel Ethernet Network Adapter E810-XXVDA4T Data Sheet*, INTEL DOCUMENTATION at 5 (2023) (annotation added).

107. Intel '901 Products determine if a TCP packet is part of a bursty transmission on the connection by looking at whether a burst count for the connection is greater than a burst-count threshold. The Intel '901 Products determine if a TCP packet is part of a bursty transmission by ascertaining that a burst count of the connection is greater than a burst-count threshold as shown in the following excerpt from Intel documentation.

|      | Name               | Byte.Bit | Value                                                                                                                | Remarks                                                                                                                 |

|------|--------------------|----------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 4114 | Tx-Scheduler Layer | 0        | Valid values = 1-9                                                                                                   | Note: In case of RLs aimed to Queues, the layer is the max logical layer independently of where the queue was attached. |

|      | Flags              | 1        | Bits 1.0-1.1: Profile Type<br>00b = CIR<br>01b = EIR<br>10b = Shared<br>11b = Reserved<br>Bits 1.2-1.7: Reserved (0) | Type of RL profile to be added.                                                                                         |

|      | Profile ID         | 2-3      |                                                                                                                      | Command: Reserved as part of command (0). Response: The profile index value returned by firmware.                       |

|      | Max Burst Size     | 4-5      | Max valid value is 0xFFF (12 bits in hardware).                                                                      | Max burst size.                                                                                                         |

|      | RL Multiply        | 6-7      | Max valid value is 0x7FF (11 bits in hardware).                                                                      | Reserved when adding shared RL.                                                                                         |

Intel Ethernet Controller E810 Version 2.7, INTEL DOCUMENTATION NEX CLOUD NETWORKING GROUP at 1341 (March 2024) (emphasis added).

108. Intel '901 Products calculate a delay time for a connection using the last packet delivery time after determining that the TCP packet is part of a bursty transmission. This measurement is then used to determine the burstiness of a TCP packet transmission.

Each LAN Tx-Queue and RDMA QSet is associated with a single TC inside the port space and mapped into a single CGD. To handle sudden PFC XOFF notifications received from the link, the transmit data path is provided with buffers in its different stages. To reduce impact on-die size, provision is made for only two types of traffic: High-Priority (also called Low-Latency (LL) in this Document) and Bulk (B).

Each CGD in Tx is configured with four main behavioral parameters:

Case 1:24-cv-01291-MN

- Advanced Mode Host Interface The Advanced Transmit mode enables software to control

tightly the burstiness of the traffic from this queue, to interleave transmissions between multiple

data sources while limiting the burst size from any one given queue. When a CGS is recognized as

Burst Sensitive, all the Tx-Queues associated with this CGD must be configured to operate in

Advanced Transmit Mode.

- **Bulk vs. Low Latency** Each CGD is configured as LL (Low Latency) or B (Bulk) CGD. High-priority CGDs are selected first in the Tx arbiters, allowing them running faster through the Tx-Pipe.

- Congested vs. Not Congested CGD This defines if the specific CGD is declared as Droppable in the network, and therefore no Priority Flow Control (PFC) is expected for the CGD or PFC support for it is required.

Intel Ethernet Controller E810 Version 2.7, INTEL DOCUMENTATION NEX CLOUD NETWORKING GROUP at 1265 (March 2024) (emphasis added).

- 109. The Intel '901 Products contain functionality for delivering the TCP packet to a receiving layer based on the calculated delay time, wherein the receiving layer is either the network interface layer or the transport layer that is not the sending layer. Specifically, the Intel '901 Products manage packet transmission times and delays as part of the Intel '901 Products' traffic optimization and prioritization functionality.

- 110. The Intel '901 Products enable sending the TCP packet to the receiving layer.

- 111. The Intel '901 Products perform the steps at a packet scheduler layer located between a network interface layer and a transport layer. Specifically, the Intel '901 Products use a Transmit Scheduler that operates at the packet scheduling layer. The packet scheduling layer in the Intel '901 Products sits between the network layer (the Ethernet MAC/PHY) and the transport interface layer (which includes protocols such as TCP). The Transmit Scheduler manages transmission requests across multiple Tx-Queues. Intel's documentation for the Intel '901 Products confirm the Transmit Scheduler supports up to 16K Tx-Queues. The Intel '901 Products Transmit Scheduler manages the "transmission of all Tx-Queues" and "decides which [] Tx-Queue is allowed to transmit and how many bytes."

usage type called a user priority. The Tx-Scheduler is responsible for controlling the transmission of all Tx-Queues. It executes a scheduling algorithm and decides which the Tx-Queue is allowed to transmit and how many bytes. To meet all QoS agreements while considering the network capacity, and to reduce packet drop or flow control events, the Tx-Scheduler takes into account the following configuration parameters:

- · Priority.

- Bandwidth allocation, bandwidth limit, minimum guaranteed bandwidth.

- Network topology, the network infrastructure fed by device ports, its capacity, and the deployment of the Rx units (switches, routers, target NICs, and so on) in the network.

- Those Rx units might be buffer-limited or limited by packet processing power. To address both types, the E810 can configure each topology node to arbitrate and shape for bytes per second (BPS) or packets per second (PPS).

- Quality of Service (QoS) and service level agreement (SLA).

INTEL ETHERNET CONTROLLER E810 DATASHEET REVISION 2.8 at § 8.3.1 (September 2024) (emphasis added).

- 112. Intel has directly infringed and continues to directly infringe the '901 Patent by, among other things, making, using, offering for sale, and/or selling technology for a data packet scheduler that reduces packet bursts, including but not limited to the Intel '901 Products.

- 113. The Intel '901 Products are available to businesses and individuals throughout the United States.

- 114. The Intel '901 Products are provided to businesses and individuals located in this District.

- 115. By making, using, testing, offering for sale, and/or selling products and services comprising technology for a data packet scheduler that reduced packet bursts, including but not limited to the Intel '901 Products, Intel has injured Plaintiff and is liable to Plaintiff for directly infringing one or more claims of the '901 Patent, including at least claim 1 pursuant to 35 U.S.C. § 271(a).

- 116. Intel has had knowledge of the '901 Patent and its infringement of the '901 Patent since at least service of the Original Complaint in this action or shortly thereafter. Moreover, the '901 Patent is well-known within the industry as demonstrated by multiple citations to the '901 Patent in published patents and patent applications assigned to technology companies and academic institutions. Intel has continued to infringe the '901 Patent despite knowing of the '901 Patent and its infringement thereof. Intel is infringing the '901 Patent in a manner best described as willful, wanton, malicious, in bad faith, deliberate, consciously wrongful, flagrant, or characteristic of a pirate.

- 117. To the extent applicable, the requirements of 35 U.S.C. § 287(a) have been met with respect to the '901 Patent.

118. As a result of Intel's infringement of the '901 Patent, Plaintiff has suffered monetary damages, and seeks recovery in an amount adequate to compensate for Intel's infringement, but in no event less than a reasonable royalty for the use made of the invention by Intel together with interest and costs as fixed by the Court.

# COUNT III INFRINGEMENT OF U.S. PATENT No. 10,412,388

- 119. Plaintiff references and incorporates by reference the preceding paragraphs of this Complaint as if fully set forth herein.

- 120. Intel designs, makes, uses, sells, and/or offers for sale in the United States products comprising technology for video compression using adaptive re-quantization using extracted and derived quantization parameters.

- 121. Intel designs, makes, sells, offers to sell, imports, and/or uses Intel products that perform encoding of media data in compliance with the H.265 High Efficiency Video Coding (HEVC) compression standard, including but not limited to the products identified in the list attached hereto as Exhibit 7 (collectively, the "Intel '388 Product(s)").

- 122. Intel designs, makes, sells, offers to sell, imports, and/or uses Intel '388 products that comply with the H.265 video encoding standard.

- 123. The Intel '388 Products perform video processing compliant with the High Efficiency Video Coding (HEVC) standard, which is also often referred to as the H.265 standard. Specifically, the Intel '388 Products perform HEVC encoding.

Intel® Quick Sync Video uses the dedicated media processing capabilities of Intel® Graphics

Technology to decode and encode fast. This enables the processor to complete other tasks at

the same time and improves system responsiveness.

The High Efficiency Video Coding (HEVC), also known as H.265 and MPEG-H Part 2, is a video

compression standard designed as part of the MPEG-H project as a successor to the widely

used Advanced Video Coding (AVC, H.264, or MPEG-4 Part 10).

Resolution

Hardware accelerated support for the H.265/HEVC codec starts with 6th generation Intel®

Core™ processors.

This site contains some more detailed information about the encoding/decoding capabilities of

7th generation and newer Intel® Core™ processors.

*H.265/HEVC Hardware Encoding and Decoding Support*, INTEL PRODUCT SUPPORT WEBSITE (last visited November 2024), *available at:* https://www.intel.com/content/www/us/en/support/articles/000037112/graphics.html (emphasis added).

- 124. One or more Intel subsidiaries and/or affiliates use the Intel '388 Products in regular business operations.

- 125. The Intel '388 Products identify an initial quantization parameter employed to compress a previously decoded frame.

- 126. The Intel '388 Products, as part of the encoding process use an initial quantization parameter (QP) for encoding each frame or coding unit (CU). In conforming to the HEVC standard, the Intel '388 Products must set an initial QP value that serves as the baseline for encoding the decoded frame.

- 127. The Intel '388 Products calculate a delta quantization parameter as influenced by the initial quantization parameter, where the function is designed to yield this delta parameter at least in part to achieve a bitrate reduction while sustaining a given quality threshold.

- 128. The Intel '388 Products calculate a delta QP based on the initial quantization parameter. This function aims to minimize bitrate while retaining the required video quality.

- 129. The Intel '388 Products ascertain a subsequent quantization parameter for the purpose of compressing the decoded frame, based on both the initial and delta quantization parameters.

- 130. The Intel '388 Products determine a second quantization parameter using the initial QP and the delta QP. The Intel '388 Products calculate the second quantization parameter as QP1 + Delta QP. This second quantization parameter is the one used for encoding either the entire frame or specific coding units within the frame.

- 131. The Intel '388 Products compress the decoded frame utilizing the second quantization parameter.

- 132. The Intel '388 Products encode the video frames using the newly derived second quantization parameter.

- 133. By complying with the HEVC standard, the Intel '388 Products necessarily infringe the '388 Patent. Mandatory sections of the HEVC standard require the elements required by certain claims of the '388 Patent, including but not limited to claim 1. High Efficiency Video Coding, Series H: Audiovisual And Multimedia Systems: Infrastructure Of Audiovisual Services Coding Of Moving Video Rec. ITU-T H.265 (August 2021). The following sections of the HEVC Standard are relevant to Intel's infringement of the '388 Patent: "7.3.2.2.3 Sequence parameter set screen content coding extension syntax;" "7.3.8.4 Coding quadtree syntax;" "7.3.8.14 Delta QP syntax;" "7.4.3.3.1 General picture parameter set RBSP semantics;" "7.4.7.1 General slice segment header semantics;" "7.4.9.14 Delta QP semantics;" "8.6.1 Derivation process for quantization parameters;" and "9.3.3.10 Binarization process for cu\_qp\_delta\_abs."

- 134. All implementations of the HEVC standard necessarily infringe the '388 Patent as every implementation of the standard requires compliant devices to carry out the following: Each

frame or coding unit (CU) is encoded using a pre-defined initial Quantization Parameter (QP) which serves as a baseline for various optimizations. The standard mandates that a first QP (QP1) be identified before any encoding can occur. The Intel '388 Products are, therefore, required to have mechanisms to set this initial QP1 for the to-be-encoded (or re-encoded) frame. Further, the HEVC standard sets out a structured way to adjust this initial QP based on a delta value. The objective of introducing a delta QP is generally to adapt to the complexity variations within a video sequence and to optimize rate-distortion performance. The HEVC encoding standard sets forth calculating a new QP (QP2) after determining the delta QP. This is done by adding the initial QP (QP1) and the delta QP. This step is essential for maintaining granular control over the rate-distortion tradeoff during encoding. Finally, the final encoding of the frame or CU takes place using QP2. The HEVC standard specifies that this is a requisite step for the encoding process to be considered compliant. The Intel '388 Products must, therefore, encode frames using this newly computed QP2 to meet the standard's rate and quality stipulations.

- 135. Intel has directly infringed and continues to directly infringe the '388 Patent by, among other things, making, using, offering for sale, and/or selling technology for video compression using adaptive re-quantization using extracted and derived quantization parameters, including but not limited to the Intel '388 Products.

- 136. The Intel '388 Products are available to businesses and individuals throughout the United States.

- 137. The Intel '388 Products are provided to businesses and individuals located in this District.

- 138. By making, using, testing, offering for sale, and/or selling products and services comprising technology for video compression using adaptive re-quantization using extracted and

derived quantization parameters, including but not limited to the Intel '388 Products, Intel has injured Plaintiff and is liable to Plaintiff for directly infringing one or more claims of the '388 Patent, including at least claim 1 pursuant to 35 U.S.C. § 271(a).

- 139. Intel has had knowledge of the '388 Patent and its infringement of the '388 Patent since at least service of the Original Complaint in this action or shortly thereafter. Moreover, the '388 Patent is well-known within the industry as demonstrated by multiple citations to the '388 Patent in published patents and patent applications assigned to technology companies and academic institutions. Intel has continued to infringe the '388 Patent despite knowing of the '388 Patent and its infringement thereof. Intel is infringing the '388 Patent in a manner best described as willful, wanton, malicious, in bad faith, deliberate, consciously wrongful, flagrant, or characteristic of a pirate.

- 140. To the extent applicable, the requirements of 35 U.S.C. § 287(a) have been met with respect to the '388 Patent.

- 141. As a result of Intel's infringement of the '388 Patent, Plaintiff has suffered monetary damages, and seeks recovery in an amount adequate to compensate for Intel's infringement, but in no event less than a reasonable royalty for the use made of the invention by Intel together with interest and costs as fixed by the Court.

### COUNT IV INFRINGEMENT OF U.S. PATENT No. 9,894,361

- 142. Plaintiff references and incorporates by reference the preceding paragraphs of this Complaint as if fully set forth herein.

- 143. Intel designs, makes, uses, sells, and/or offers for sale in the United States products containing technology for quality-aware video optimization.

- 144. Intel designs, makes, sells, offers to sell, imports, and/or uses the following products: Intel designs, makes, sells, offers to sell, imports, and/or uses Intel products that perform encoding of media data in compliance with the H.265 High Efficiency Video Coding (HEVC) compression standard, including but not limited to the products identified in the list attached hereto as Exhibit 7 (collectively, the "Intel '361 Product(s)").

- 145. Intel designs, makes, sells, offers to sell, imports, and/or uses Intel '361 Products that comply with the H.265 video encoding standard.

- 146. The Intel '361 Products perform video processing compliant with the High Efficiency Video Coding (HEVC) standard, which is also often referred to as the H.265 standard. Specifically, the Intel '361 products perform HEVC encoding.

Intel® Quick Sync Video uses the dedicated media processing capabilities of Intel® Graphics Technology to decode and encode fast. This enables the processor to complete other tasks at the same time and improves system responsiveness.

The High Efficiency Video Coding (HEVC), also known as H.265 and MPEG-H Part 2, is a video compression standard designed as part of the MPEG-H project as a successor to the widely used Advanced Video Coding (AVC, H.264, or MPEG-4 Part 10).

#### Resolution

Hardware accelerated support for the H.265/HEVC codec starts with 6th generation Intel® Core™ processors.

This site contains some more detailed information about the encoding/decoding capabilities of 7th generation and newer Intel® Core™ processors.

*H.265/HEVC Hardware Encoding and Decoding Support*, INTEL PRODUCT SUPPORT WEBSITE (last visited November 2024), *available at:* https://www.intel.com/content/www/us/en/support/articles/000037112/graphics.html (emphasis added).

- 147. One or more Intel subsidiaries and/or affiliates use the Intel '361 Products in regular business operations.

- 148. The Intel '361 Products unpack a compressed video frame from a series containing multiple video frames.

- 149. The Intel '361 Products take an encoded video frame as input. This frame is one in a series that consists of multiple frames. The encoded frame is then passed through a decoding pipeline by the Intel '361 Products. The Intel '361 Products use inverse quantization and inverse DCT (Discrete Cosine Transform) functions, to revert the video data to a decompressed state suitable for further manipulation.

- 150. The Intel '361 Products obtain an initial Quantization Parameter (QP) from the unpacked video frame, where this initial QP is indicative of the quantization configurations initially applied to compress the video frame.

- 151. The Intel '361 Products extract a first Quantization Parameter (QP) from the video frame metadata or from the bitstream itself. This first QP reflects the quantization settings initially applied during the original encoding. This first QP is read from the slice header or similar control structures and used to modulate the quantization matrices in the decoding process.