# IN THE UNITED STATES DISTRICT COURT FOR THE DISTRICT OF DELAWARE

MYW SEMITECH, LLC,

Plaintiff,

Case No.

v.

JURY TRIAL DEMANDED

APPLE INC.,

Defendant.

# **COMPLAINT FOR PATENT INFRINGEMENT**

Plaintiff MYW Semitech, LLC ("MYW Semitech"), by and through its undersigned counsel, files this Complaint against Defendant Apple Inc. ("Apple" or "Defendant") for patent infringement of United States Patent Nos. 11,107,768; 11,538,763; and 11,894,306 (the "Patents-In-Suit") and alleges as follows:

# **NATURE OF THE ACTION**

1. This is an action for patent infringement arising under the patent laws of the United States, 35 U.S.C. §§ 1 *et seq*.

## **PARTIES**

- 2. Plaintiff MYW Semitech is a Delaware corporation with a place of business at 8 The Green, Suite A, Dover, Delaware 19901.

- 3. On information and belief, Apple, Inc. is a publicly traded company organized and existing under the laws of the state of California. Apple may be served with process through its registered agent, CT Corporation System at 818 W. Seventh St., Los Angeles, CA 90017.

## JURISDICTION AND VENUE

- 4. This Court has jurisdiction over the subject matter of this action pursuant to 28 U.S.C. §§ 1331 and 1338(a) because the action arises under the patent laws of the United States, 35 U.S.C. §§ 1 et seq.

- 5. On information and belief, Apple is subject to this Court's personal jurisdiction in accordance with due process and/or the Delaware Long-Arm Statute.

- 6. This Court has personal jurisdiction over Apple because Apple has sufficient minimum contacts with this forum as a result of business conducted within the State of Delaware and this judicial district. In particular, this Court has personal jurisdiction over Apple because, inter alia, Apple has substantial, continuous, and systematic business contacts in this judicial district, and derives substantial revenue from goods provided to individuals including in this judicial district.

- 7. Apple has purposefully availed itself of the laws of, and of the privileges of conducting business within, this judicial district, has established sufficient minimum contacts with this judicial district such that it should reasonably and fairly anticipate being hauled into court in this judicial district, has purposefully directed activities at residents of this judicial district, and at least a portion of the patent infringement claims alleged in this Complaint arise out of or are related to one or more of the foregoing activities.

- 8. On information and belief, Apple has litigated cases before this Court in which it admitted that venue was proper, did not contest personal jurisdiction and/or venue, and/or filed a complaint or counterclaims, including Openwave Systems, Inc. v. Apple Inc., et al., 1:11-cv-00765-RGA (D.Del.); Apple Inc. v. Masimo Corporation and Sound United, LLC 1:22-cv-01377-JLH (D.Del.); Memory Integrity, LLC v. Apple, Inc., 1:13-cv-01796-GMS (D.Del.).

- 9. This Court has personal jurisdiction over Apple because Apple (directly and/or through its subsidiaries, affiliates, or intermediaries) has committed and continues to commit acts of infringement in this judicial district in violation of at least 35 U.S.C. § 271(a). In particular, on information and belief, Apple manufacturers, uses, sells, offers for sale, imports, advertises, and/or otherwise promotes infringing products in the United States, the State of Delaware, and this judicial district.

- 10. On information and belief, Apple has a regular and established place of business within the District of Delaware, including 125 Christiana Mall, Newark, Delaware 19702. On information and belief, Apple has physical stores and employees in this judicial district.

- 11. Venue is proper in this judicial district under 28 U.S.C. §§ 1391(b)-(d) and/or 1400(b) at least because Apple has committed acts of infringement within this judicial district giving rise to this action.

## THE ASSERTED PATENTS

#### **United States Patent No. 11,107,768**

- 12. On August 31, 2021, the United States Patent and Trademark Office duly and legally issued United States Patent No. 11,107,768 ("the '768 patent") entitled "Chip Package" to inventor Ping-Jung Yang. A true and correct copy of the patent is attached as Exhibit A.

- 13. The '768 patent is presumed valid under 35 U.S.C. § 282.

- 14. MYW Semitech owns all rights, title, and interest in the '768 patent.

#### United States Patent No. 11,538,763

- 15. On December 27, 2022, the United States Patent and Trademark Office duly and legally issued United States Patent No. 11,538,763 ("the '763 patent") entitled "Chip Package" to inventor Ping-Jung Yang. A true and correct copy of the patent is attached as Exhibit B.

- 16. The '763 patent is presumed valid under 35 U.S.C. § 282.

17. MYW Semitech owns all rights, title, and interest in the '763 patent.

# United States Patent No. 11,894,306

- 18. On February 6, 2024, the United States Patent and Trademark Office duly and legally issued United States Patent No. 11,894,306 ("the '306 patent") entitled "Chip Package" to inventor Ping-Jung Yang. A true and correct copy of the patent is attached as Exhibit C.

- 19. The '306 patent is presumed valid under 35 U.S.C. § 282.

- 20. MYW Semitech owns all rights, title, and interest in the '306 patent.

# THE ACCUSED APPLE PRODUCTS

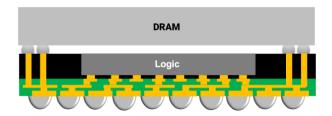

21. Apple uses an integrated fanout package-on-package (InFO PoP) technology in its chips, which exemplified in the infographic below:

InFO-PoP, the industry's first 3D wafer-level fan-out package, features a high density RDL and TIVs to integrate mobile application processors with dynamic random access memory (DRAM). InFO-PoP has better electrical and thermal performance, and a thinner profile than flip chip package-on-package, because it has no organic substrate or C4 bump.

Source: https://3dfabric.tsmc.com/english/dedicatedFoundry/technology/InFO.htm

22. Apple has extensively adopted the InFO PoP technology for its iPhone and iPad products. Specifically, Apple is currently utilizing the InFO PoP technology in at least the following chips: Apple A10 Fusion, A10X Fusion, A11 Bionic, A12 Bionic, A12X Bionic, A12X Bionic, A12X Bionic, A13 Bionic, A14 Bionic, A15 Bionic, A16 Bionic, A17 Pro, as well as the Apple S4, S5, S6, S7, S8, and S9. See, e.g. <a href="https://medias.yolegroup.com/">https://medias.yolegroup.com/</a> uploads/2019/03/Yole\_TSMC\_Fan-out\_inFO\_Apple\_A10\_iPhone7Plus\_Sample.pdf

- 23. Exemplary images of these chips are seen below:

- Apple A10

$Source: https://medias.yolegroup.com/uploads/2019/03/Yole\_TSMC\_Fanout\_inFO\_Apple\_A10\_iPhone7Plus\_Sample.pdf$

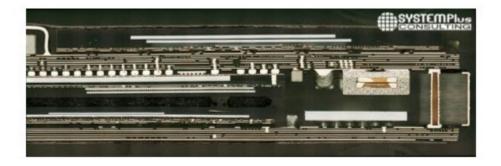

# • Apple A11

Source: <a href="https://www.yolegroup.com/product/report/second-generation-of-tsmcs-integrated-fan-out-info-packaging-for-the-apple-a11-found-in-the-iphone-x/">https://www.yolegroup.com/product/report/second-generation-of-tsmcs-integrated-fan-out-info-packaging-for-the-apple-a11-found-in-the-iphone-x/</a>

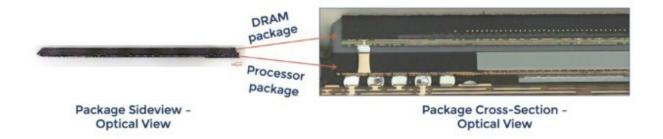

# • Apple A14

Source: <a href="https://www.yolegroup.com/press-release/apples-a14-and-a15-bionic-the-game-changing-soc-solutions-from-apple/">https://www.yolegroup.com/press-release/apples-a14-and-a15-bionic-the-game-changing-soc-solutions-from-apple/</a>

## Apple A17

Source: https://www.yolegroup.com/technology-outlook/unveiling-the-iphone-15-pro-max-and-a17-pro-processor-the-chronicles-by-yole-systemplus/

- Apple, including but not limited to, the iPhone 7, iPhone 7 Plus, iPad 6<sup>th</sup> generation, iPad 7<sup>th</sup> generation, iPad Pro 2<sup>nd</sup> generation, Apple TV 4K 1<sup>st</sup> generation, iPhone 8, iPhone 8 Plus, iPhone X, iPhone XR, iPhone XS, iPhone XS Max, iPad Air 3<sup>rd</sup> generation, iPad mini 5<sup>th</sup> generation, Apple TV 4K 2<sup>nd</sup> generation, iPad Pro third generation, iPad Pro 4<sup>th</sup> generation, 2020 Mac minibased Developer Transition Kit, iPhone 11, iPhone 11 Pro, iPhone 11 Pro Max, iPhone SE 2<sup>nd</sup> generation, iPad Air, iPhone 12, iPhone 12 Mini, iPhone 12 Pro, iPhone 12 Pro Max, iPhone 13, iPhone 13 Mini, iPhone 13 Pro, iPhone 13 Pro Max, iPad mini 6<sup>th</sup> generation, iPhone SE 3<sup>rd</sup> generation, iPhone 14 Pro, iPhone 14 Pro Max, iPhone 15, iPhone 15 Plus, iPhone 15 Pro, iPhone 15 Pro Max, Apple Watch Series 4, Apple Watch Series 5, Apple Watch SE, HomePod mini, Apple Watch Series 6, Apple Watch Series 7, HomePod 2<sup>nd</sup> generation, Apple Watch Series 9, and Apple Watch Ultra 2 ("the Accused Apple Products).

- 25. On information and belief, these Accused Apple Products infringe the patents-insuit.

# **CLAIMS FOR RELIEF**

# **COUNT I – Infringement of United States Patent No. 11,107,768**

- 26. The allegations set forth above are re-alleged and incorporated by reference as if they were set forth fully here.

- 27. On information and belief, Defendant has infringed (literally and/or under the doctrine of equivalents) and continues to infringe the '768 patent in the State of Delaware, in this judicial district, and elsewhere in the United States, by and among other things, making, using, importing, offering for sale, and/or selling the Accused Apple Products, which are covered by at least claims 1-5, 7-8, 10-11, 14-15, 16-17, 19-20, 22-23, 25-28 of the '768 patent.

- 28. On information and belief, and by way of example, the Accused Apple Products infringe at least Claim 1 because each product contains a chip package (*e.g.*, Apple A10 Fusion, A10X Fusion, A11 Bionic, A12 Bionic, A12X Bionic, A12Z Bionic, A13 Bionic, A14 Bionic, A15 Bionic, A16 Bionic, A17 Pro, as well as the Apple S4, S5, S6, S7, S8, and S9). Examples of those chip packages are seen above in paragraph 22.

- 29. On information and belief, each chip package, contains a first polymer layer having a first surface and a second surface opposite to said first surface, wherein said first surface is substantially parallel to said second surface, wherein said first polymer layer has a thickness between 100 and 300 micrometers and has a coefficient of expansion between 3 and  $10 \text{ppm}/^{\text{oC}}$ .

- 30. On information and belief, each chip package contains a first metal plug vertically in a first through via in said first polymer layer, wherein said first metal plug comprises a first copper layer, wherein the first copper layer contacts with a sidewall of said first through via.

- 31. On information and belief, each chip package contains a second metal plug vertically in a second through via in said first polymer layer, wherein said second metal plug

comprises a second copper layer, wherein a top surface of said second metal plug and a top surface of said first metal plug are in the same horizontal plane.

- 32. On information and belief, each chip package contains a first interconnection scheme comprises a first metal interconnect over said first surface, a second metal interconnect over said first surface and a second polymer layer over said first, second, and third metal interconnects, wherein said first metal interconnect is connected to said first metal plug, wherein said second metal interconnect is connected to said second metal plug, wherein said first metal interconnect comprises a first metal layer, a third copper layer on said first metal, and a fourth copper layer on said third copper layer.

- 33. On information and belief, each chip package contains a first metal bump over said first interconnection scheme and said second metal plug, wherein said first metal bump comprises a tin-containing layer.

- 34. On information and belief, each chip package contains a first semiconductor chip under said first interconnection scheme, wherein said first semiconductor chip comprises a fourth metal interconnect on a first metal pad of said first semiconductor chip, wherein said fourth metal interconnect comprises a second metal layer on said first metal pad and a fifth copper layer over said second metal layer, wherein said fifth copper layer has a thickness between 5 and 30 micrometers, wherein said fourth metal interconnect is connected to said third metal interconnect.

- 35. On information and belief, the Accused Apple Products infringe each of the claims 2-5, 7-8, 10-11, 14-15, 16-17, 19-20, 22-23, 25-28 for the reasons similar to those stated above.

36. By making, using, importing, offering for sale and/or selling such products that are covered by one or more claims of the '768 patent, MYW Semitech has been damaged by the direct infringement of Apple and is suffering and will continue to suffer irreparable harm and damages as a result of this infringement.

# **COUNT II - Infringement of United States Patent No. 11,538,763**

- 37. The allegations set forth above are re-alleged and incorporated by reference as if they were set forth fully here.

- 38. On information and belief, Defendant has infringed (literally and/or under the doctrine of equivalents) and continues to infringe the '763 patent in the State of Delaware, in this judicial district, and elsewhere in the United States, by and among other things, making, using, importing, offering for sale, and/or selling the Accused Apple Products, which are covered by at least claims 1-5, 7, 9-15, 17 of the '763 patent.

- 39. On information and belief, , and by way of example, the Accused Apple Products infringe at least Claim 1 because each product contains a chip package (*e.g.*, Apple A10 Fusion, A10X Fusion, A11 Bionic, A12 Bionic, A12X Bionic, A12Z Bionic, A13 Bionic, A14 Bionic, A15 Bionic, A16 Bionic, A17 Pro, as well as the Apple S4, S5, S6, S7, S8, and S9). Examples of those chip packages are seen above in paragraph 22.

- 40. On information and belief, each chip package contains a solid layer having a first surface and a second surface opposite to said first surface, wherein said first surface is substantially parallel to said second surface, wherein said solid layer comprises a compound of silicon and oxygen, wherein said solid layer has a thickness between 100 and 300 micrometers, wherein said solid layer comprises a first region and a second region between said first region and an edge of said solid layer.

- 41. On information and belief, each chip package contains a plurality of copper plugs in a plurality of through vias in said second region of said solid layer respectively, wherein one of said plurality of copper plugs comprises a first copper layer contacting a sidewall of one of said plurality of through vias, wherein said first region has a width in a direction greater than a shortest distance between said sidewall of one of said plurality of through vias and said edge of said solid layer in said direction and greater than a pitch between two neighboring copper plugs of said plurality of copper plugs.

- 42. On information and belief, each chip package contains a first interconnection scheme over said first surface, wherein said first interconnection scheme comprises a first metal interconnect over said first surface, a second metal interconnect over said first surface and a first polymer layer over said first and second metal interconnects, wherein said first metal interconnect is connected to a first copper plug of said plurality of copper plugs, wherein said second metal interconnect is connected to a second copper plug of said plurality of copper plugs, wherein said first metal interconnect comprises a first metal layer and a second copper layer over said first metal layer, wherein a top surface of said second copper plug and a top surface of said first copper plug are substantially in the same horizontal plane.

- 43. On information and belief, each chip package contains a first metal bump over said first interconnection scheme, wherein said first metal bump comprises a second metal layer and a tin-containing layer over said second metal layer.

- 44. On information and belief, each chip package contains a first semiconductor chip under said first interconnection scheme, wherein said first semiconductor chip comprises a third metal interconnect on a first metal pad of said first semiconductor chip, wherein said third metal interconnect comprises a third metal layer on said first metal pad and a third copper layer over

said third metal layer, wherein said third copper layer has a thickness between 5 and 30 micrometers.

- 45. On information and belief, the Accused Apple Products infringe each of the claims 2-5, 7, 9-15, 17 for the reasons similar to those stated above.

- 46. By making, using, importing, offering for sale and/or selling such products that are covered by one or more claims of the '763 patent, MYW Semitech has been damaged by the direct infringement of Apple and is suffering and will continue to suffer irreparable harm and damages as a result of this infringement.

# **COUNT III - Infringement of United States Patent No. 11,894,306**

- 47. The allegations set forth above are re-alleged and incorporated by reference as if they were set forth fully here.

- 48. On information and belief, Defendant has infringed (literally and/or under the doctrine of equivalents) and continues to infringe the '306 patent in the State of Delaware, in this judicial district, and elsewhere in the United States, by and among other things, making, using, importing, offering for sale, and/or selling the Accused Apple Products, which are covered by at least claims 10-17 of the '306 patent.

- 49. On information and belief, , and by way of example, the Accused Apple Products infringe at least Claim 10 because each product contains a chip package (*e.g.*, Apple A10 Fusion, A10X Fusion, A11 Bionic, A12 Bionic, A12X Bionic, A12Z Bionic, A13 Bionic, A14 Bionic, A15 Bionic, A16 Bionic, A17 Pro, as well as the Apple S4, S5, S6, S7, S8, and S9). Examples of those chip packages are seen above in paragraph 22.

- 50. On information and belief, each chip package contains a solid layer having a first surface and a second surface opposite to said first surface, wherein said solid layer comprises a compound of silicon and oxygen, wherein said solid layer has a thickness between 100 and 300

micrometers, wherein said solid layer comprises a first region and a second region between said first region and a first edge of said solid layer.

- 51. On information and belief, each chip package contains a plurality of copper posts in a plurality of through holes in said second region respectively, wherein said first region has a width in a direction greater than a shortest distance between a sidewall of one of said plurality of through holes and said first edge in said direction and greater than a pitch between two neighboring copper posts of said plurality of copper posts.

- 52. On information and belief, each chip package contains a first interconnection scheme over said first surface, wherein said first interconnection scheme comprises a first metal interconnect over said first surface, and a polymer layer over said first metal interconnect, wherein said first metal interconnect is connected to one of said plurality of copper posts, wherein said first metal interconnect comprises a first metal layer and a first copper layer over said first metal layer.

- 53. On information and belief, each chip package contains a first metal bump over said first interconnection scheme, wherein said first metal bump comprises a first in-containing layer.

- 54. On information and belief, each chip package contains a second metal bump over said first interconnection scheme.

- 55. On information and belief, each chip package contains a first semiconductor chip over said first interconnection scheme and between said first and second metal bumps, wherein said first semiconductor chip has a height between a backside surface of said first semiconductor chip and a top surface of said polymer layer is smaller than a thickness of said first metal bump,

wherein said first semiconductor chip comprises a third metal bump on a first metal pad of said first semiconductor chip, wherein said third metal bump comprises a second tin-containing layer.

- 56. On information and belief, each chip package contains a second semiconductor chip over said first interconnection scheme, wherein said second semiconductor chip comprises a fourth metal bump on a second metal pad of said semiconductor chip, wherein said fourth metal bump comprises a third tin-containing layer.

- 57. On information and belief, the Accused Apple Products infringe each of the claims 11-17 for the reasons similar to those stated above.

- 58. By making, using, importing, offering for sale and/or selling such products that are covered by one or more claims of the '306 patent, MYW Semitech has been damaged by the direct infringement of Apple and is suffering and will continue to suffer irreparable harm and damages as a result of this infringement.

## **JURY DEMANDED**

Pursuant to Rule 38(b) of the Federal Rules of Civil Procedure, MYW Semitech hereby requests a trial by jury on all issues so triable.

#### PRAYER FOR RELIEF

WHEREFORE, MYW Semitech respectfully requests that the Court enter judgment in its favor and against Apple as follows:

- a. finding that Apple directly infringes one or more claims of each of the patents-insuit;

- b. awarding MYW Semitech damages under 35 U.S.C. § 284, or otherwise permitted by law, including supplemental damages for any continued post-verdict infringement;

- c. awarding MYW Semitech pre-judgment and post-judgment interest on the damages award and costs;

- d. awarding cost of this action (including all disbursements) and attorney fees pursuant to 35 U.S.C. § 285, or as otherwise permitted by the law; and

- e. awarding such other costs and further relief that the Court determines to be just and equitable.

Dated: April 24, 2025 STAMOULIS & WEINBLATT LLC

/s/ Richard C. Weinblatt

Stamatios Stamoulis (#4606)

Richard C. Weinblatt (#5080)

800 N. West Street, Third Floor

Wilmington, DE 19801

(302) 999-1540

stamoulis@swdelaw.com

weinblatt@swdelaw.com

Ronald M. Daignault\* (pro hac vice to be filed)

Chandran Iyer (pro hac vice to be filed)

Ray Mort\* (pro hac vice to be filed)

Erin Hadi (pro hac vice to be filed)

Taylor Lepore\* (pro hac vice to be filed)

Richard Juang\* (pro hac vice to be filed)

DAIGNAULT IYER LLP

8229 Boone Boulevard – Suite 450

Vienna, VA 22182

\*Not admitted in Virginia

Attorneys for Plaintiff MYW Semitech, LLC