# UNITED STATES DISTRICT COURTS, DISTRICT COURT EASTERN DISTRICT OF TEXAS LUFKIN DIVISION 202 JAN 15 PM 1: 01

TX EASTERN -LUFKIN

MOTOROLA, INC.,

v.

Plaintiff,

WINBOND ELECTRONICS CORPORATION, and WINBOND ELECTRONICS CORPORATION AMERICA,

Defendants.

CIVIL ACTION NO.

GOOCVIO

JURY TRIAL DEMANDED

Judge Hanneh

## COMPLAINT FOR DAMAGES AND INJUNCTIVE RELIEF DEMAND FOR JURY TRIAL

Plaintiff Motorola, Inc., by its attorneys, complains against Winbond Electronics Corporation and Winbond Electronics Corporation America, and alleges as follows:

#### **Parties**

- 1. Plaintiff Motorola, Inc. ("Motorola"), is a corporation organized under the laws of the State of Delaware with its principal place of business at 1303 East Algonquin Road, Schaumburg, Illinois 60196. Motorola markets and sells semiconductor products throughout the United States, including within this District.

- 2. On information and belief, Defendant Winbond Electronics Corporation ("Winbond") is a corporation organized under the laws of Taiwan, the Republic of China, with its principal place of business at No. 4, Creation Road 3, Science-Based Industrial Park, Hsinchu, 300, Taiwan, R.O.C. Winbond manufactures semiconductor products in

Taiwan, imports its products into the United States and sells and/or offers for sale its products for importation into the United States. In addition, Winbond's semiconductor products are marketed, sold, and/or offered for sale throughout the United States, including within this District.

3. On information and belief, Defendant Winbond Electronics Corporation America ("Winbond America") is a corporation organized under the laws of the State of Delaware with its principal place of business at 2727 North First Street, San Jose, CA 95134. Winbond America imports, sells and/or offers for sale its products in the United States. In addition, Winbond America's semiconductor products are marketed, sold, and/or offered for sale throughout the United States, including within this District.

## Jurisdiction and Venue

- 4. This is an action arising under the patent laws of the United States, 35 U.S.C. § 101 et seq. This Court has subject matter jurisdiction under 28 U.S.C. §§ 1331 and 1338(a).

- 5. Venue is proper in this judicial district under 28 U.S.C. §§ 1391(b), (c) and (d) and 1400(b).

#### The Patents

- 6. United States Patent No. 4,758,945, invented by James J. Remedi, entitled "Method for Reducing Power Consumed by a Static Microprocessor" (the "945 Remedi Patent"), was duly and legally issued by the United States Patent and Trademark Office on July 19, 1988. A copy of the '945 Remedi Patent is attached hereto as Exhibit A.

- 7. United States Patent No. 4,468,411, invented by James W. Sloan, Truoc T. Tran, and Frank T. Jones, III, entitled "Method for Providing Alpha Particle Protection for an Integrated Circuit Die" (the "Sloan Patent"), was duly and legally issued by the United States Patent and Trademark Office on August 28, 1984. A copy of the Sloan Patent is attached hereto as Exhibit B.

- 8. United States Patent No. 4,446,194, invented by Jon Candelaria and Kurt S. Heidinger, entitled "Dual Layer Passivation" (the "Candelaria Patent"), was duly and legally issued by the United States Patent and Trademark Office on May 1, 1984. A copy of the Candelaria Patent is attached hereto as Exhibit C.

- 9. United States Patent No. 4,279,947, invented by Jon C. Goldman, Larry D. McMillan, and James B. Price, entitled "Deposition of Silicon Nitride" (the "Goldman Patent"), was duly and legally issued by the United States Patent and Trademark Office on July 21, 1981. A copy of the Goldman Patent is attached hereto as Exhibit D.

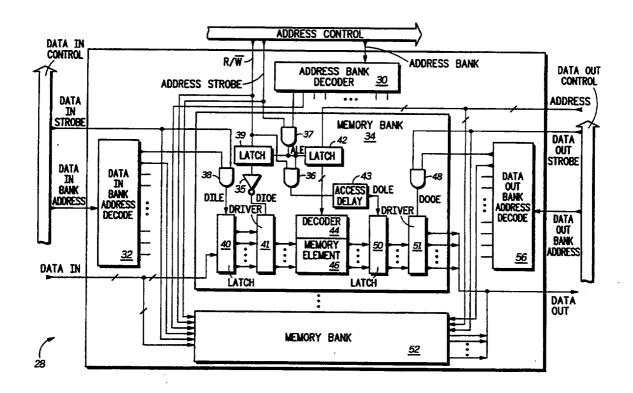

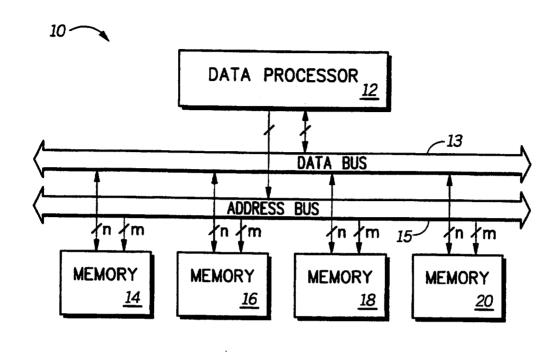

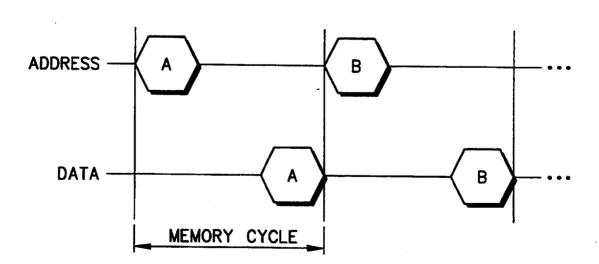

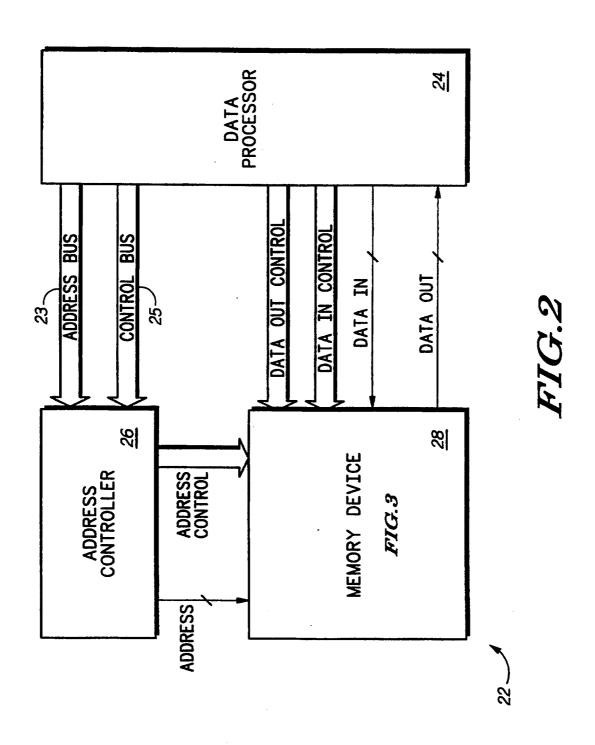

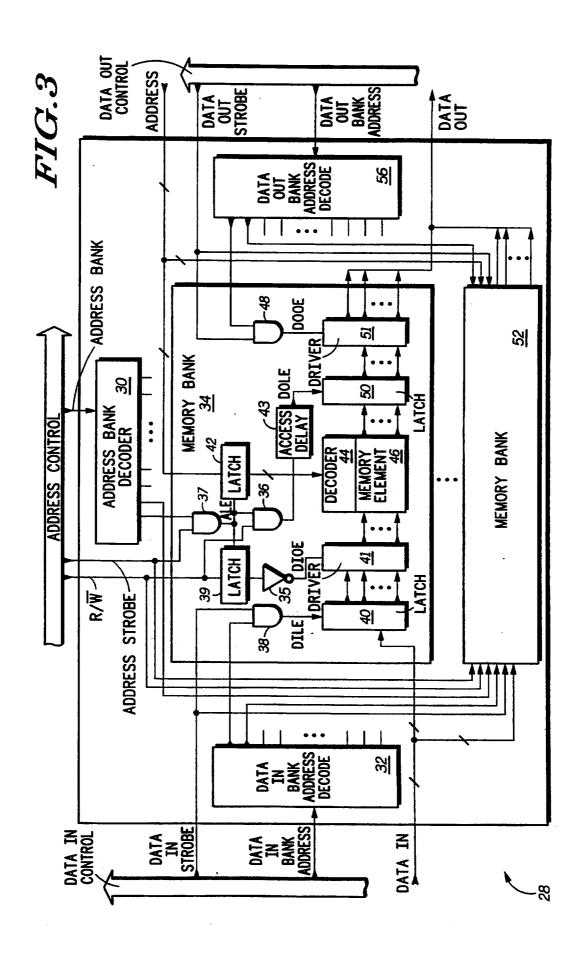

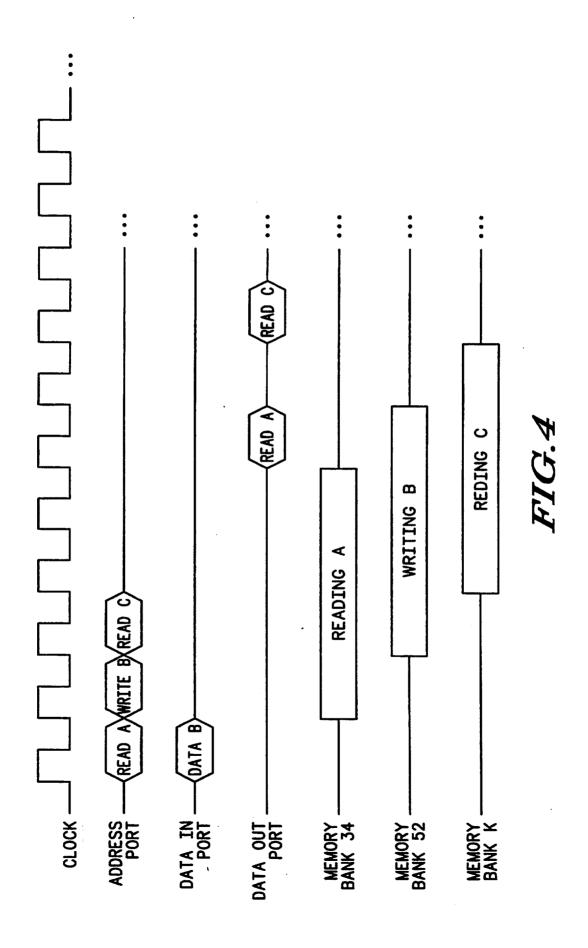

- 10. United States Patent No. 5,367,494, invented by Michael C. Shebanow, Mitchell K. Alsup, Hunter L. Scales, and George P. Hoekstra, entitled "Randomly Accessible Memory Having Time Overlapping Memory Accesses" (the "Shebanow Patent"), was duly and legally issued by the United States Patent and Trademark Office on November 22, 1994. A copy of the Shebanow Patent is attached hereto as Exhibit E.

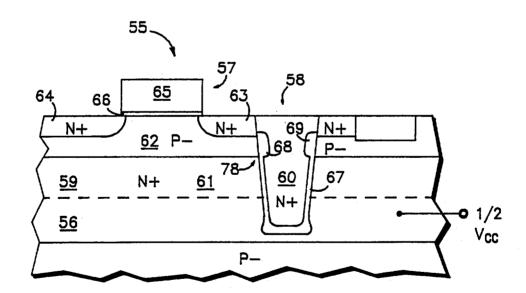

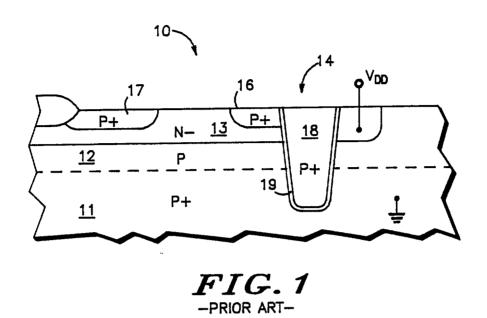

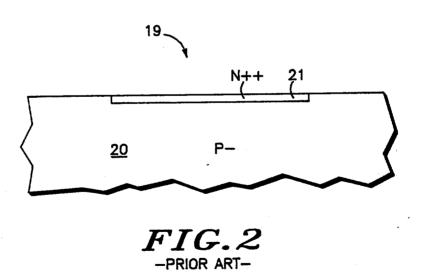

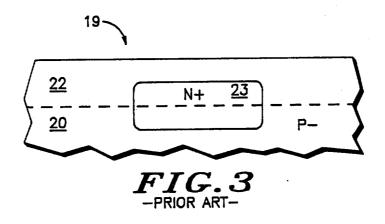

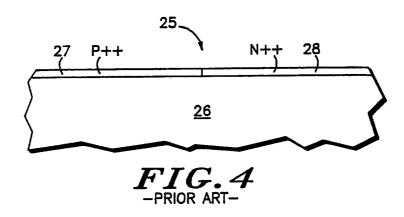

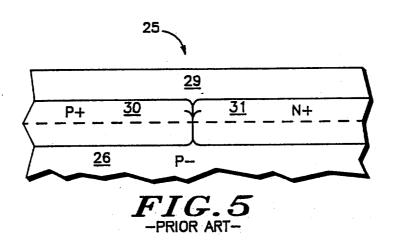

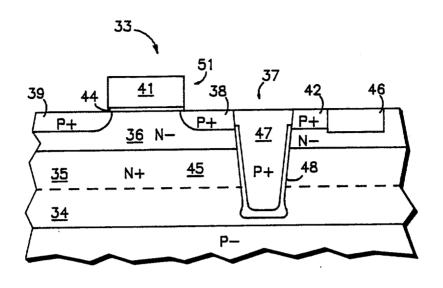

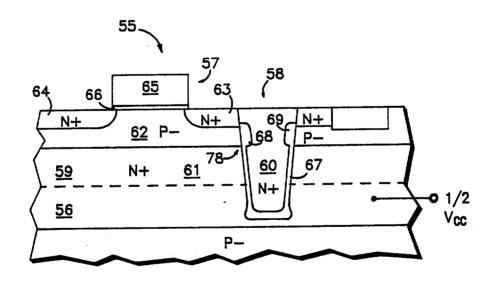

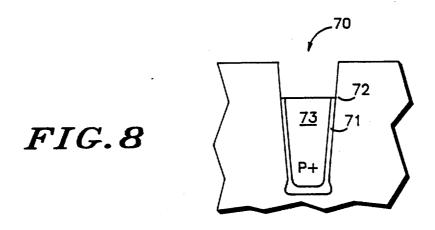

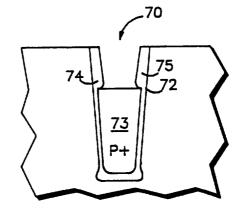

- United States Patent No. 4,794,434, invented by Perry H. Pelley, III, entitled "Trench Cell for a DRAM" (the "Pelley Patent"), was duly and legally issued by the United States Patent and Trademark Office on December 27, 1988. A copy of the Pelley Patent is attached hereto as Exhibit F.

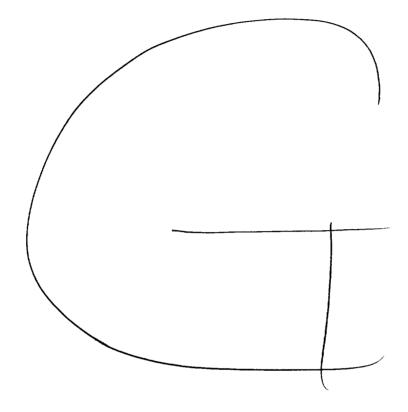

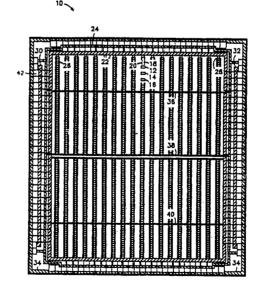

- 12. United States Patent No. 4,511,914, invented by James J. Remedi, Don G. Reid, and Lynette Ure, entitled "Power Bus Routing for Providing Noise Isolation in Gate Arrays" (the "'914 Remedi Patent"), was duly and legally issued by the United States Patent and Trademark Office on April 16, 1985. A copy of the '914 Remedi Patent is attached hereto as Exhibit G.

- 13. Motorola is the owner of all rights, title and interest in and to the '945 Remedi Patent, the Sloan Patent, the Candelaria Patent, the Goldman Patent, the Shebanow Patent, the Pelley Patent, and the '914 Remedi Patent (collectively, the "Motorola Patents") and is entitled to sue for past and future infringement.

## Background

- 14. The Motorola Patents cover inventions relating to semiconductor processing and semiconductor chip design.

- 15. The Defendants have imported into the United States, marketed, sold and/or offered for sale in the United States, products covered by the Motorola Patents.

- 16. The Defendants have had actual and/or constructive notice and knowledge of the Motorola Patents. The filing of this Complaint also constitutes notice in accordance with 35 U.S.C. § 287. Despite such notice, the Defendants continue to import into and sell in the United States products covered by the Motorola Patents.

#### Count I

- 17. Motorola repeats and realleges the allegations in paragraphs 1-16.

- 18. On information and belief, the Defendants have infringed, and/or induced infringement of, the '945 Remedi Patent by importing into, offering for sale, or selling in the United States, or by intending that others import into, offer for sale, or sell in the United States, products that incorporate the invention of, and/or were made using the methods claimed in, the '945 Remedi Patent.

- 19. On information and belief, the Defendants' infringement of the '945 Remedi Patent has been willful. Defendants' continued infringement of the '945 Remedi Patent has damaged and will continue to damage Motorola.

- 20. On information and belief, the Defendants' infringement of the '945 Remedi Patent has caused and will continue to cause Motorola irreparable harm unless enjoined by the Court. Motorola has no adequate remedy at law.

## Count II

- 21. Motorola repeats and realleges the allegations in paragraphs 1-16.

- 22. On information and belief, the Defendants have infringed, and/or induced infringement of, the Sloan Patent by importing into, offering for sale, or selling in the United States, or by intending that others import into, offer for sale, or sell in the United

States, products that incorporate the invention of, and/or were made using the methods claimed in, the Sloan Patent.

- On information and belief, the Defendants' infringement of the Sloan Patent has been willful. The Defendants' continued infringement of the Sloan Patent has damaged and will continue to damage Motorola.

- 24. On information and belief, the Defendants' infringement of the Sloan Patent has caused and will continue to cause Motorola irreparable harm unless enjoined by the Court. Motorola has no adequate remedy at law.

## Count III

- 25. Motorola repeats and realleges the allegations in paragraphs 1-16.

- 26. On information and belief, the Defendants have infringed, and/or induced infringement of, the Candelaria Patent by importing into, offering for sale, or selling in the United States, or by intending that others import into, offer for sale, or sell in the United States, products that incorporate the invention of, and/or were made using the methods claimed in, the Candelaria Patent.

- On information and belief, the Defendants' infringement of the Candelaria Patent has been willful. The Defendants' continued infringement of the Candelaria Patent has damaged and will continue to damage Motorola.

- 28. On information and belief, the Defendants' infringement of the Candelaria Patent has caused and will continue to cause Motorola irreparable harm unless enjoined by the Court. Motorola has no adequate remedy at law.

#### **Count IV**

- 29. Motorola repeats and realleges the allegations in paragraphs 1-16.

- 30. On information and belief, the Defendants have infringed, and/or induced infringement of, the Goldman Patent by importing into, offering for sale, or selling in the United States, or by intending that others import into, offer for sale, or sell in the United

States, products that incorporate the invention of, and/or were made using the methods claimed in, the Goldman Patent.

- 31. On information and belief, the Defendants' infringement of the Goldman Patent has been willful. The Defendants' continued infringement of the Goldman Patent has damaged and will continue to damage Motorola.

- 32. On information and belief, the Defendants' infringement of the Goldman Patent has caused and will continue to cause Motorola irreparable harm unless enjoined by the Court. Motorola has no adequate remedy at law.

#### Count V

- 33. Motorola repeats and realleges the allegations in paragraphs 1-16.

- 34. On information and belief, the Defendants have infringed, and/or induced infringement of, the Shebanow Patent by importing into, offering for sale, or selling in the United States, or by intending that others import into, offer for sale, or sell in the United States, products that incorporate the invention of, and/or were made using the methods claimed in, the Shebanow Patent.

- 35. On information and belief, the Defendants' infringement of the Shebanow Patent has been willful. The Defendants' continued infringement of the Shebanow Patent has damaged and will continue to damage Motorola.

- 36. On information and belief, the Defendants' infringement of the Shebanow Patent has caused and will continue to cause Motorola irreparable harm unless enjoined by the Court. Motorola has no adequate remedy at law.

## Count VI

- 37. Motorola repeats and realleges the allegations in paragraphs 1-16.

- 38. On information and belief, the Defendants have infringed, and/or induced infringement of, the Pelley Patent by importing into, offering for sale, or selling in the United States, or by intending that others import into, offer for sale, or sell in the United

States, products that incorporate the invention of, and/or were made using the methods claimed in, the Pelley Patent.

- 39. On information and belief, the Defendants' infringement of the Pelley Patent has been willful. The Defendants' continued infringement of the Pelley Patent has damaged and will continue to damage Motorola.

- 40. On information and belief, the Defendants' infringement of the Pelley

Patent has caused and will continue to cause Motorola irreparable harm unless enjoined by

the Court. Motorola has no adequate remedy at law.

## Count VII

- 41. Motorola repeats and realleges the allegations in paragraphs 1-16.

- 42. On information and belief, the Defendants have infringed, and/or induced infringement of, the '914 Remedi Patent by importing into, offering for sale, or selling in the United States, or by intending that others import into, offer for sale, or sell in the United States, products that incorporate the invention of, and/or were made using the methods claimed in, the '914 Remedi Patent.

- 43. On information and belief, the Defendants' infringement of the '914 Remedi Patent has been willful. The Defendants' continued infringement of the '914 Remedi Patent has damaged and will continue to damage Motorola.

- 44. On information and belief, the Defendants' infringement of the '914 Remedi Patent has caused and will continue to cause Motorola irreparable harm unless enjoined by the Court. Motorola has no adequate remedy at law.

## **Prayer for Relief**

WHEREFORE, Motorola, Inc., respectfully requests that this Court enter judgment in its favor and grant the following relief:

- A. Adjudge that the Defendants are infringing the Motorola Patents,

- B. Adjudge that the Defendants' infringement of the Motorola Patents was willful, and that Defendants' continued infringement of the Motorola Patents is willful;

C. Enter an order preliminarily and permanently enjoining the Defendants from any further acts of infringement of the Motorola Patents;

D. Award Motorola damages in an amount adequate to compensate Motorola for the Defendants' infringement of the Motorola Patents, but in no event less than a reasonable royalty under 35 U.S.C. § 284;

E. Enter an order trebling any and all damages awarded to Motorola by reason of the Defendants' willful infringement of the Motorola Patents, pursuant to 35 U.S.C. § 284;

F. Enter an order awarding Motorola interest on the damages awarded and its costs pursuant to 35 U.S.C. § 284;

G. Enter an order finding that this is an exceptional case and award Motorola its reasonable attorneys' fees pursuant to 35 U.S.C. § 285; and

H. Award such other relief as the Court may deem appropriate and just under the circumstances.

DATED: January 15, 2002

**HEARTFIELD & McGINNIS LLP**

Bv

THAD HEARTFIELD Attorney-in-Charge

for Plaintiff MOTOROLA, INC.

State Bar No. 09346800 2196 Dowlen Road

Beaumont, TX 77706

Telephone: 409-866-3318 Facsimile: 409-866-5789

111

## OF COUNSEL:

Fay E. Morisseau (Texas State Bar No. 14460750) Michael R. O'Neill McDERMOTT, WILL & EMERY 18191 Von Karman Avenue, Suite 500 Irvine, CA 92612-0187 Telephone: (949) 851-0633 Facsimile: (949) 851-9348

Terrence P. McMahon David L. Larson McDERMOTT, WILL & EMERY 2700 Sand Hill Road Menlo Park, CA 94025 Telephone: (650) 233-5500 Facsimile: (650) 233-5599

| <b>United States</b> | Patent | [19] |

|----------------------|--------|------|

|----------------------|--------|------|

## Remedi

[11] Patent Number:

4,758,945

[45] Date of Patent:

Jul. 19, 1988

| [54] | METHOD FOR REDUCING POWER |

|------|---------------------------|

|      | CONSUMED BY A STATIC      |

|      | MICROPROCESSOR            |

| [75] Invent | or: James | I. Remedi, | Austin, | Tex. |

|-------------|-----------|------------|---------|------|

|-------------|-----------|------------|---------|------|

[73] Assignee: Motorola, Inc., Schaumburg, Ill.

[21] Appl. No.: 65,292

[22] Filed: Aug. 9, 1979

| [51] | Int. Cl.4 | *************************************** | G06F 1/04 |

|------|-----------|-----------------------------------------|-----------|

| FEAT | ** C C    | •                                       | 2/4/200   |

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

|           |         | Packard          |         |

|-----------|---------|------------------|---------|

|           |         | Bouricius et al  |         |

| 3,855,577 | 12/1974 | Vandierendonck   | 364/200 |

| 3,941,989 | 3/1976  | McLaughlin et al | 235/156 |

| 4 | ,030,079 | 6/1977 | Bennett et al   | 364/200 |

|---|----------|--------|-----------------|---------|

| 4 | ,151,611 | 4/1979 | Sugawara et al  | 365/227 |

| 4 | ,158,230 | 6/1979 | Washizuka et al | 364/708 |

| 4 | ,191,998 | 3/1980 | Carmody         | 364/200 |

Primary Examiner—David Y. Eng Attorney, Agent, or Firm—John A. Fisher; Jeffrey Van Myers

## [57] ABSTRACT

In response to a software instruction, a static microprocessor is placed in a low current mode by disabling clock pulse generation. Means are provided for disabling a master oscillator when a STOP instruction is decoded. Additional means are provided for inhibiting clock pulses when a WAIT instruction is decoded without disabling the master oscillator. Clock pulse generation is again enabled upon receipt of a reset or interrupt signal.

6 Claims, 3 Drawing Sheets

Jul. 19, 1988

Sheet 1 of 3

4,758,945

Jul. 19, 1988

Sheet 2 of 3

4,758,945

Jul. 19, 1988

Sheet 3 of 3

4,758,945

#### METHOD FOR REDUCING POWER CONSUMED BY A STATIC MICROPROCESSOR

#### CROSS REFERENCE TO RELATED **APPLICATIONS**

(1) U.S. patent application Ser. No. 065,293 filed of even date herewith entitled "Apparatus for Reducing Power Consumed by a Static Microprocessor" and 10 assigned to the assignee of the present invention.

(2) U.S. patent application Ser. No. 065,294 filed of even date herewith entitled "CMOS Microprocessor Architecture" and assigned to the assignee of the present invention.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

This invention relates generally to microcomputers and, more particularly, to a method for reducing the 20 microprocessor. power consumed by static microprocessors.

#### 2. Description of the Prior Art

Microcomputers are sophisticated, general purpose logic devices which can be programmed to perform a wide variety of useful control functions in industrial and 25 communications equipment, large scale and medium scale computer peripheral and terminal hardware, automobiles and other transportation media, amusement and educational devices, household appliances and other consumer goods, and the like. Generally, an entire spec- 30 trum of microcomputers is presently available in the commercial marketplace. As the speed of operation increases, the more valuable and more versatile the microcomputer becomes since it is capable of controlling the given operation more efficiently and more ac-  $^{35}$ curately, of controlling a greater number of operations simultaneously, and of controlling operations requiring relatively fast response times.

The throughput of any given microcomputer is a function of, among other things, the number of machine cycles required to execute a given set of instructions. In the course of designing any computer system, and in particular a microcomputer, a set of instructions is selected which will provide the anticipated program requirements for the projected market in which the computer system is to be used. The microprocessor, or processor component of a single chip microcomputer, executes each instruction as a sequence of machine cycles, with the more complex instructions consuming a 50 greater number of machine cycles.

The operation of the internal circuitry of the microprocessor is synchronized by means of a master clock signal applied to the microprocessor. The master clock signal may actually comprise two or even four clock 55 consumption in the processor. components; i.e., the microprocessor clock may be two phase or four phase. During the basic clock cycle known as the machine cycle, a number of internal processor related operations may take place simultaneously including the transfer of digital information from a bus 60 of a microprocessor of a type which may embody the to a register or vice versa, between certain registers, from an address or data buffer to a bus or vice versa, and so forth. Additionally, the individual conductors of a bus may each be set to a predetermined logic level, or the contents of a register may be set to a predetermined 65 logic level.

It is also desirable, particularly with respect to microcomputers intended for marketing in the middle to

low end of the price scale, to minimize the computer chip size as much as possible.

Static microprocessors implemented with complementary MOS technology (CMOS) exhibits low DC 5 current drain. Such systems are thus considered to consume less power and little power when operating. To further reduce power consumption, one known system utilizes a HALT instruction which inhibits processor execution. However, all clock signals utilized by the processor continue to be generated. Since a static microprocessor will maintain its state even in the absence of clock signals, it would be desirable to provide a method for disabling clock signals in an intelligent manner until further processor operations become neces-15 sary.

#### SUMMARY OF THE INVENTION

It is an object of the present invention to provide a method for reducing the power consumed by a static

It is a further object of the present invention to reduce power consumed by static microprocessor by utilizing software instructions which place the microprocessor in a very low current state.

It is yet another object of the present invention to provide a method for reducing power consumed by a CMOS static microprocessor by inhibiting the clock pulses generated until processor operation is required as indicated by some external stimulus.

According to a broad aspect of the invention there is provided a method for reducing, in response to at least one software instruction, energy consumed by a digital system of the type which includes a master oscillator having at least one signal output for producing a clock signal, said method comprising the steps of: decoding said at least one software instruction; and inhibiting said clock signal in response to said software instruction.

The above and other objects, features and advantages of the present invention will be more clearly understood from the following detailed description taken in conjunction with the accompany drawings; in which:

## BRIEF DESCRIPTION OF THE DRAWINGS

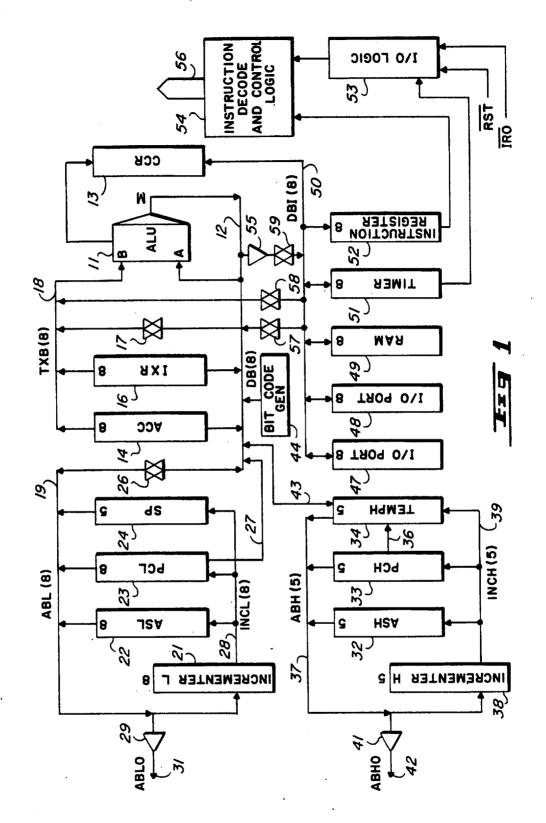

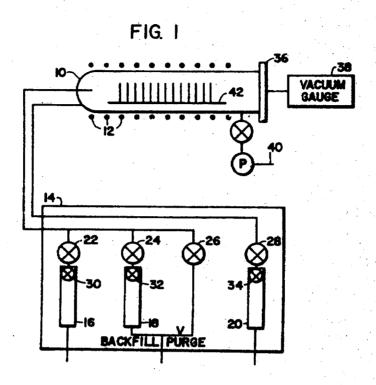

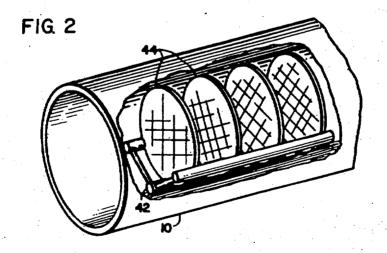

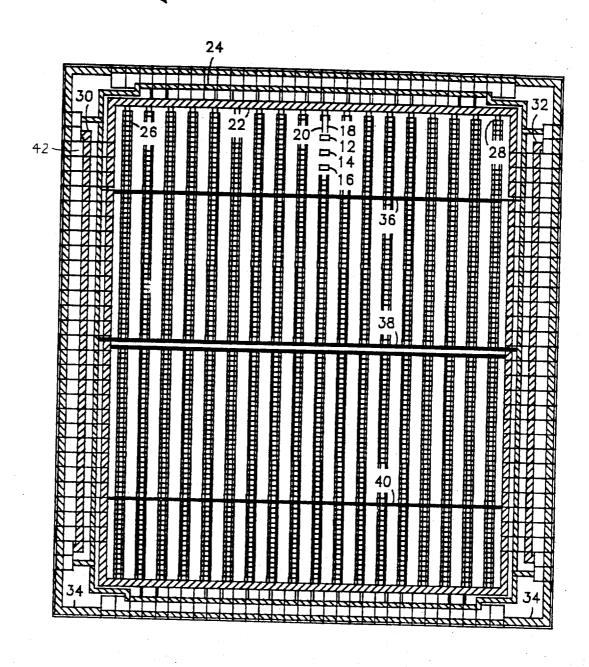

FIG. 1 is a block diagram of a microprocessor in 45 which the present invention may be embodied;

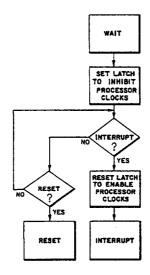

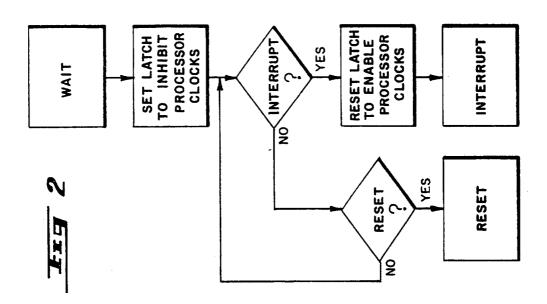

FIG.-2 is a flow diagram illustrating the sequence of operation produced by a WAIT instruction in accordance with the present invention;

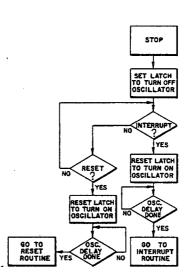

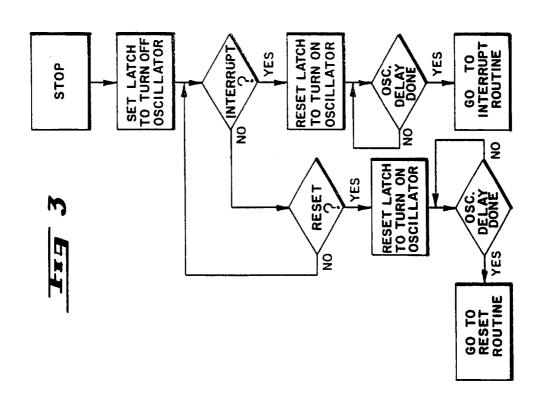

FIG. 3 is a flow diagram illustrating the sequence of operation produced by a STOP instruction in accordance with the present invention; and

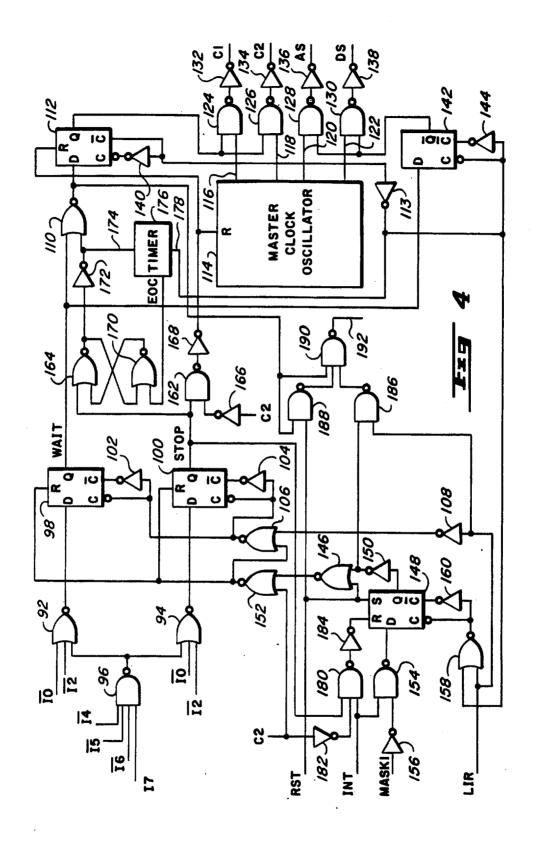

FIG. 4 is a logic diagram illustrating an apparatus for inhibiting clock signal in response to the WAIT or STOP instructions of FIGS. 2 and 3 to reduce power

#### DESCRIPTION OF THE PREFERRED **EMBODIMENT**

Referring to FIG. 1, there is shown a block diagram present invention. The microprocessor includes a RAM, timer, and input/output (I/0). The microprocessor has an ALU 11 having an input A, an input B, and a summation output. The summation output is coupled to an 8 bit data bus 12. Data bus 12 couples information to input A. Information is carried to input B by an 8 bit transfer bus 18. An accumulator 14 is coupled to both transfer bus 18 and data bus 12. Accumulator 14 is an 8

bit general purpose register used for arithmetic calculations and data manipulations. An 8 bit index register 16 is coupled between transfer bus 18 and data bus 12. Index register 16 is used during an index mode of addressing and provides an 8 bit address which may be 5 added as an offset to create a new effective address. Index register 16 is also used for calculations and data manipulation during read/modify/write instructions, and as a temporary storage register when not in use for addressing purposes. A transmission gate 17 is used to 10 couple data bus 12 to transfer bus 18. A condition code register 13 is coupled to internal data bus 50 and receives an input from ALU 11. Condition code register 13 is a 5 bit register and contains flags which reflects the results of ALU 11 operations. A first bit contained in 15 condition code register 13 is a carry bit and is set when a carry or a borrow out of ALU 11 occurs during an arithmetic operation. The carry bit can also be modified by certain branch instructions. A second bit in condition code register 13 is a zero bit and is set whenever the 20 result of the last arithmetic, logical, or data manipulation is zero. A third bit is a negative bit which indicates that the result of the last arithmetic, logical, or data manipulation is negative. A fourth bit is a mask interrupt bit and when set, disables both external and timer 25 interrupts. Clearing the interrupt mask bit enables both of the interrupts. Both the timer and external interrupts are latched so that no interrupts are lost because of the interrupt mask bit being set. A fifth bit is a half carry bit, and is set if a carry occurs between bits 3 and 4 of the 30 ALU during an add or an add with carry instruction.

An 8 bit address bus 19 is coupled to data bus 12 by transmission gate 26. Address bus 19 carries the lower 8 bits of an address. The microprocessor of FIG. 1 is capable of addressing up to 8K bytes of external mem- 35 ory with a multiplexed address/data bus. Address bus 19 is coupled to an output buffer 29 and to an incrementer 21. Buffer 29 provides buffered outputs on line 31 which is the 8 bit lower order output address bus. Incrementer 21 is an 8 bit incrementer which can decre- 40 ment as well as increment. Incrementer 21 is coupled to three registers by line 28. The three registers are an address store register 22, a program counter register 23, and a stack pointer 24. Address store 22 is an 8 bit register which is used to store a lower order effective ad- 45 dress such as generated from a branch instruction. Program counter 23 is an 8 bit register which contains the lower 8 bits of a thirteen bit word which is used to point to the next instruction to be executed by the microprocessor. Stack pointer 24 is a 6 bit stack pointer which 50 contains the address of the next free location on a push down/pop up stack. The stack pointer 24 decrements during pushs and increments during pulls. Stack pointer 24 is used to store the location of the return address on subroutine calls and to store the location of the machine 55 state during interrupts. In a preferred embodiment stack pointer 24 is an 8 bit register with the two most significant bits permanently set to a predetermined state.

The outputs of registers 22, 23, and 24 are connected to address bus 19. Program counter 23 also provides an 60 output to data bus 12 via line 27. When one of register 22, 23, or 24 is desired to be modified its contents are transferred by address bus 19 to incrementer 21, where incrementer 21 can increment or decrement the contents, and the contents are then carried by line 28 back 65 to any desired register. This arrangement of incrementer 21 with registers 22, 23 and 24 permit one common incrementer/decrementer for three registers with

one of the registers, the program counter 23, also being directly coupled to data bus 12. As mentioned hereinbefore, address bus 19 is coupled to data bus 12 by transmission gate 26.

It should be noted that although the buses are illustrated by one line that they are multiple lines with each different line carrying a different data bit.

The higher five bits of the address word is provided on line 42 by output buffer 41. Output buffer 41 is coupled to a 5 bit address bus 37. It should be noted that in a preferred embodiment, the lower eight bits of the address are multiplexed to external devices while the upper five bits are directly provided on interface pins. Address bus 37 is also coupled to an incrementer/decrementer 38 which is similar to incrementer 21 but only handles five bits. An address store register 32 is coupled from the output of incrementer 38 to address bus 37. Address store 32 contains the high bits of the address while address store 22 contains the lower eight bits of the address. A 5 bit program counter 33 is coupled between the output of incrementer 38 and address bus 37. A 5 bit temporary register 34 is coupled from the output of incrementer 38 to address bus 37. Program counter 33 also provides an output 36 to temporary register 34, which allows the contents of program counter 33 to be directly transferred into temporary register 34. This transfer between registers of course results in faster operation. The output of incrementer 38 is carried by a 5 bit bus or line 39 to registers 32, 33, and 34. Temporary register 34 is directly coupled to data bus 12 by interconnect bus 43. A bit code generator 44 is also connected to data bus 12 which allows any one of the bit lines of data bus 12 to be set or reset under instruction control.

An 8 bit internal data bus 50 is coupled by transmission gate 57 to data bus 12, by a transmission gate 58 to transfer bus 18, and receives information from data bus 12 by buffer/driver 55 and transmission gate 59. Buffer/driver 55 and transmission gate 59 are connected in series. As will be seen hereinafter, the registers are compact, fully static, and are not required to provide static current drive since the drive is provided by buffer 55. By having buffers/drivers 29, 41, and 55 the registers do not require large current drivers and therefore the entire microprocessor can be made smaller in size. An 8 bit I/O port 47 and an 8 bit I/O port 48 are coupled to internal data bus 50. I/O ports 47 and 48 contain data direction registers which control whether the individual interface pins associated with the I/O ports are serving as an input or an output for the microprocessor. Also coupled to internal data bus 50 is a random access memory (RAM) 49 which stores 8 bit words. In a preferred embodiment, RAM 49 stores 112 bytes. RAM 49 could be used for, among other things, a stack to store the contents of the registers during an interrupt.

Timer 51 is coupled to internal data bus 50 and has a single 8 bit counter with a 7 bit prescaler as its timer. The 8 bit counter is preset under program control and then decrements towards zero. When a zero crossing is detected the timer interrupt request bit of timer 51 is set, then, if a timer interrupt mask and the interrupt mask bit of condition code register 13 are both cleared the microprocessor receives an interrupt. The microprocessor now stores the appropriate registers on the stack, which is located in RAM 49, and then fetches the interrupt address vectors and begins servicing the interrupt. The prescaler of timer 51 is a 7 bit counter used to extend the maximum length of the timer. Timer 51 also provides an

output to input/output logic 53. Input/output logic 53 provides an output to instruction decode and control logic 54. Input/output logic 53 receives and processes a reset and an interrupt request input. An 8 bit instruction register 52 is coupled from internal data bus 50 to instruction decode and control logic 54. Control logic 54 provides decoded instruction outputs and the necessary controls on output lines 56. The outputs on line 56 are used throughout the microprocessor to control the functioning and operation of the microprocessor, a few 10 of such being transmission gates 17, 57, 58, and 59 and bit code generator 44. It is possible for the microprocessor to be a microcomputer simply by the addition of a read only memory (ROM) coupled to internal data bus 50.

A detailed description of the microprocessor shown in FIG. 1 can be found in U.S. patent application Ser. No. 065,294 filed of even date herewith entitled "CMOS Microprocessor Architecture" and assigned to the assignee of the present invention.

As stated previously, a static CMOS microprocessor will maintain its state even in the absence of clock signals. Therefore, to reduce the amount of power consumed, it is desirable to inhibit clock pulses when the processor need not be functioning. This, according to 25 the present invention, is accomplished in two ways. First, a WAIT instruction is added to the instruction repertoire. When executed, the master clock oscillator continues to function as does the timer 51 shown in FIG. 1. However, all other internal processor clocks 30 are inhibited. Thus, the WAIT instruction places the processor in a low power state. The processor may be again rendered operational by (1) activating an external reset, or (2) the presence of an interrupt signal.

A second approach to inhibiting the clocks when the 35 processor need not function is to provide a STOP instruction to the instruction repertoire. When a STOP instruction is executed, both the master clock oscillator and the internal clocks are inhibited. The processor is now in a very low current state; i.e., only leakage current is present. The processor is then restarted as a result of an external reset or interrupt signal; however, it is necessary to provide some period of delay to allow the oscillator to become stable.

FIG. 2 is a flow diagram which illustrates the execution of a WAIT instruction. After a WAIT instruction has been decoded, a latch is set which inhibits the processor clocks. Thus, the processor is placed in a low current mode and awaits either a reset signal or an interrupt signal. If a reset signal is received, the processor will execute a reset routine. If, on the other hand, an interrupt is received, the above referred to latch is reset to enable the processor clocks to commence and an interrupt routine to be executed.

FIG. 3 is a flow diagram illustrating the use of the 55 STOP instruction. After the STOP instruction has been decoded, a second latch is set which turns off the master oscillator. This places the processor in a very low current mode until either a reset or an interrupt signal is received. If an interrupt or a reset signal is received, the 60 second latch is reset to enable the master oscillator. In order to assure that the oscillator is functioning with sufficient logic swing and has settled with respect to frequency, a predetermined amount of delay is provided before the processor executes an interrupt or reset rou-65 tine.

FIG. 4 is a logic diagram illustrating the apparatus for inhibiting the clocks or master clock oscillator in re-

sponse to a WAIT or STOP instruction respectively. The instruction is decoded in decode and control logic 54 (FIG. 1), and the individual decoded instruction bits or the complements thereof are applied to gates 92, 94 and 96. The output of NOR gate 92 will be high when signals I0, I2, I4, I5, I6 and I7 are at a logical "1" level. The output of NOR gate 94 will be high when signals 10, 12, 14, 15, 16 and 17 are at a logical "1" level. A logical "1" at the output of NOR gate 92 will occur when a WAIT instruction has been decoded, and a logical "1" will appear at the output of NOR gate 94 when a STOP instruction has been decoded. D- type flip-flops 98 and 100 are employed to latch the WAIT and STOP commands respectively. Both flip-flops 98 and 100 are clocked by the output of NOR gate 106 which is applied to the C inputs of flip-flops 98 and 100 directly and which is applied to the C inputs of flip-flops 98 and 100 via inverters 102 and 104 respectively. The clocking of these flip-flops occurs at the trailing edge of a load instruction register (LIR) signal which is applied to inverter 108 the output of which is applied to a first input of NOR gate 106. As will be discussed below, the second input of NOR gate 106 is normally low thus permitting flip-flops 98 and 100 to be clocked at the trailing edge of the LIR signal.

The operation of the circuit shown in FIG. 4 will first be described with reference to a WAIT instruction; i.e. a logical "1" appearing at the D input of flip-flop 98. At the trailing edge of the load instruction register signal, flip-flop 98 will be clocked thus latching the WAIT instruction and producing a logical "1" at the Q output of flip-flop 98. This output is coupled to a first input of NOR gate 110 and, as a result thereof, a logical "0" appears at the output of NOR gate 110 and the D input of flip-flop 112.

The master clock oscillator 114 produces outputs 116. 118, 120 and 122 which after propagation through NAND gates 124, 126, 128 and 130 respectively and through inverters 132, 134, 136 and 138 respectively form first and second clock signals (C1 and C2), an address strobe (AS) and a data strobe (DS). Output 116 from master clock 114 is applied directly to the C input of flip-flop 112 and to the C input of flip-flop 112 via inverter 140. Therefore, after a logical "0" has been placed at the D input of flip-flop 112 in response to the latching of a WAIT instruction, the Q output of flipflop 112 will become a logical "0" at the leading edge of the next clock pulse appearing at output 116. The O output of flip-flop 112 is applied to inputs of NAND gates 124 and 126. Thus, when flip-flop 112 is in the zero state, NAND gates 124 and 126 do not permit passage of the signals appearing on master clock oscillator outputs 116 and 118. As a result, the outputs of inverters 132 and 134 remain a logical "0", and the processor clock pulses C1 and C2 are disabled.

The output of WAIT flip-flop 98 is also applied directly to the D input of flip-flop 142 which is clocked by the output of inverter 113. Thus, when a WAIT instruction is latched, flip-flop 142 is set at the next leading edge of the signal appearing on output 116. The  $\overline{\mathbb{Q}}$  output of flip-flop 142 is applied to inputs of NAND gates 128 and 130. Since the flip-flop 142 is now set, the  $\overline{\mathbb{Q}}$  output is a logical "0" thus inhibiting the passage of signals appearing on outputs 120 and 122 of the master clock oscillator. This produces a logical "0" at the output of inverters 136 and 138 thus disabling both the address strobe (AS) and the data strobe (DS) signals.

This is done to prevent the AS and DS lines from charging and discharging unnecessarily during the wait state.

The clock signals and address and data strobe signals will remain inhibited until either a reset signal (RST) or an interrupt signal (INT) is received. The reset signal RST is applied to a first input of NOR gate 146. The output of flip-flop 148 after inversion in inverter 150 is applied to the second input of NOR gate 146. Since flip-flop 148 is normally on, the output of inverter 150 will be a logical "0". Thus, when the reset signal (RST) 10 goes high, a logical "0" will appear at the output of NOR gate 146. This is applied to a first input of NOR gate 152. Clock pulse C2 is applied to a second input of NOR gate 152, and since this clock signal has been disabled as a result of the WAIT instruction, a logical 15 "0" is applied to the second input of NOR gate 152. This results in the production of a logical "1" at the output of NOR gate 152 and at the reset input of WAIT flip-flop 98. With flip-flop 98 now reset, a logical "0" is applied to the D input of flip-flop 142 and a logical "1" is ap- 20 plied to the D input of flip-flop 112. The next clock signal appearing on output 116 of master clock oscillator 114 will cause flip-flop 112 to set and flip-flop 142 to reset. This will enable NAND gates 124, 126, 128 and 130 resulting in the renewed production of clock signals 25 C1 and C2, and address and data strobe signals AS and DS.

If, instead, an interrupt signal (INT), is applied to a first input of NAND gate 154. A mask interrupt signal (MASKI) is applied to inverter 156 the output of which 30 is coupled to a second input of NAND gate 154. Thus, in the presence of an interrupt signal and in the absence of a mask interrupt signal, a logical "0" is applied to the D input of flip-flop 148. Flip-flop 148 is clocked by the output of NOR gate 158 which is applied directly to the 35 C input of flip-flop 148 and to the C input of flip-flop 148 via inverter 160. The load instruction register signal (LIR) is applied to a first input of NOR gate 158 and the output of inverter 113 is applied to the second input. Thus, with a zero appearing at the D input of flip-flop 40 148, the flip-flop is clocked by the next trailing edge of clock 116 resulting in a logical "0" at its Q output. This produces a logical "1" at the output of inverter 150 and a logical "0" at the output of NOR gate 146 since no reset signal is present. With logical "0's" at both inputs 45 of NOR gate 152, a logical "1" is applied to the reset input of WAIT flip-flop 98. Clock signals C1 and C2 and address and data strobe signals AS and DS are again enabled as was described above in the case of a reset signal. It should be apparent that the primary purpose of 50 flip-flop 148 is to synchronize the interrupt signal with the signal appearing on output 116 of the master clock oscillator 114.

When a STOP instruction is decoded, a logical one is placed at the D input of STOP flip-flop 100. This condition is latched by flip-flop 100 at the trailing edge of the load instruction register (LIR) signal as was described previously. The Q output of the STOP flip-flop 100 is applied to a first input of NAND gate 162 and a first input of NOR gate 164. Clock signal C2 is inverted in 60 inverter 166 and applied to a second input of NAND gate 162. This synchronizes the output of NAND gate 162 with processor clock C2. When both of the Q output of STOP flip-flop 100 and the inverted processor clock C2 (i.e. C2) are high, a logical "1" appears at the 65 output of inverter 168. This output is applied to a reset input of master clock oscillator 114 and to the reset input of flip-flop 112. By resetting the master clock

8

oscillator in this manner, outputs 116, 118, 120 and 122

are totally disabled.

The logical "1" at the output of STOP flip-flop 100 is also applied to one input of cross-coupled NOR gates 164 and 170. A logical "0" will be produced at the output of NOR gate 164, and a logical "1" will be produced at the output of inverter 172. This produces a logical "0" at the D input of flip-flop 112.

If a reset signal (RST) is received, a logical "1" will appear at the output of NOR gate 152 as was described previously. This output is coupled to the reset input of STOP flip-flop 100. When flip-flop 100 becomes reset, a logical "0" will be applied to the reset input of master clock oscillator 114 thus enabling outputs 116, 118, 120 and 122. However, flip-flop 112 has not yet been set and therefore clock signals C1 and C2 remain disabled. Since output 116 has been enabled, flip-flop 142 is clocked to a reset state thus enabling AS and DS.

Flip-flop 112 becomes set as follows. When the STOP flip-flop 100 was set, a logical "1" appeared at the output of inverter 172 which was applied via line 174 to timer 176. This signal applied to timer 176 enables the timer to count clock pulses received from output 116 of master clock oscillator 114 over line 178. Thus, when the STOP flip-flop 100 is reset, timer 176 begins counting pulses received over line 178. When the counter in the timer reaches a predetermined state, an end of count (EOC) signal is applied to the input of NOR gate 170. The EOC signal is a logical "1" which causes a logical "0" to appear at the output of gate 170 which is in turn applied to an input of NOR gate 164. The output of STOP flip-flop 100 is likewise applied to an input of NOR gate 164. Since the inputs to NOR gate 164 are both zero, the output of NOR gate 164 will be a logical "1" thus producing a logical "0" at the output of inverter 172. With the zeros at both inputs of NOR gate 110, a logical "1" is applied to the D input of flipflop 112. When the next pulse occurs on output 116 of master clock oscillator 114, flip-flop 112 is clocked producing a logical "1" at its Q output. This now enables gates 124 and 126 to pass the signals appearing on outputs 116 and 118 to produce clock pulses C1 and C2.

Timer 176 may be employed to provide a delay of for example 2 milliseconds. Such timers are well known and a further discussion at this time is not deemed necessary. For example, the timer of U.S. Pat. No. 4,222,103 entitled "Real Time Capture Registers For Data Processor" and assigned to the assignee of the present invention would be suitable.

If instead of a reset signal, an interrupt signal should occur, it is still necessary to reset flip-flop 148. However, since the master clock oscillator 114 has been disabled, no clock pulses can be applied to the C and C inputs of flip-flop 148. Therefore, flip-flop 148 must be reset asynchronously. This is accomplished as follows, a logical "1" on the interrupt input is applied to a first input of NAND gate 180. Since clock signal C2 is at a logical "0", a logical "1" is applied to a second input of NAND gate 180 via inverter 182. Finally, a third input of NAND gate 182 is coupled to the output of STOP flip-flop 100 which, after execution of the STOP instruction, is at a logical "1" level. Therefore, the output of NAND gate 180 is at a logical "0" level. This output is inverted by inverter 184 and applied to the R input of flip-flop 148. After flip-flop 148 is reset, the process is the same as above described resulting in the resetting of STOP flip-flop 100.

One additional group of logic comprises NAND gates 186, 188 and 190. The first input of NAND gate 186 is coupled to the load instruction register (LIR) signal, and a second input is coupled to the output of inverter 150. A first input of NAND gate 188 is coupled 5 to the reset signal (RST) and a second input is coupled to the output of NOR gate 110 which is a logical "0" during a WAIT or STOP condition. The outputs of NAND gates 186 and 188 are respectively coupled to input of NAND gate 190 is coupled to the output of NOR gate 110. The purpose of the output 192 of NAND gate 190 is to load the instruction register with a hardware interrupt thus making the system ready to 15 receive an interrupt.

What is claimed is:

1. In a digital computing system which executes software instructions in synchronization with clock signals generated by a master clock oscillator in an enabled 20 condition thereof, a method for reducing the energy consumed by the digital system, comprising the steps of: decoding a predetermined software instruction selected for execution by said digital computing sys-

inhibiting passage of said clock signals from said master clock oscillator to said digital computing system in response to the decoding of said predetermined software instruction, and continuing to inhibit passage of said clock signals for a predeter- 30 mined length of time after said master clock oscillator has been enabled;

disabling the generation of said clock signals by said master clock oscillator in response to the decoding of said predetermined software instruction; and

10

enabling the generation of said clock signals by said master clock oscillator in response to a control

2. A method according to claim 1 wherein said control signal comprises an externally produced reset sig-

3. A method according to claim 1 wherein said control signal comprises an interrupt signal.

4. In a digital computing system which executes softfirst and second inputs of NAND gate 190. A third 10 ware instructions in synchronization with clock signals generated by a master clock oscillator in an enabled condition thereof, a method for reducing the energy consumed by the digital system, comprising the steps of: executing a predetermined software instruction se-

lected for execution by said digital computing system:

inhibiting passage of said clock signals from said master clock oscillator to said digital computing system in response to the execution of said predetermined software instruction, and continuing to inhibit passage of said clock signals for a predetermined length of time after said master clock oscillator has been enabled;

disabling the generation of said clock signals by said master clock oscillator in response to the decoding of said predetermined software instruction; and

enabling the generation of said clock signals by said master clock oscillator in response to a control

5. A method according to claim 1 wherein said control signal comprises an externally produced reset signal.

6. A method according to claim 1 wherein said control signal comprises an interrupt signal.

45

50

55

60

## United States Patent [19]

Sloan et al.

[11] Patent Number:

4,468,411

[45] Date of Patent:

Aug. 28, 1984

#### [54] METHOD FOR PROVIDING ALPHA PARTICLE PROTECTION FOR AN INTEGRATED CIRCUIT DIE

[75] Inventors: James W. Sloan; Truoc T. Tran; Frank T. Jones, III, all of Austin,

Tex.

[73] Assignee: Motorola, Inc., Schaumburg, Ill.

[21] Appl. No.: 365,724

[22] Filed: Apr. 5, 1982

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 3,615,913 | 10/1971 | Shaw   | 427/82 |

|-----------|---------|--------|--------|

| 3,682,698 | 8/1972  | Palmer | 427/82 |

| 4,323,405 | 4/1982  | Uno    | 427/5  |

## FOREIGN PATENT DOCUMENTS

55-128851 10/1980 Japan .

#### OTHER PUBLICATIONS

Mukai, et al., "Planar Multilevel Interconnection Technology Employing a Polyimide", IEEE Journal of Solid State Circuits, vol. SC-13, No. 4, Aug. 1978. Ward, "Alpha Particle Shield", IBM TDB, vol. 22, No. 4, p. 1398, Sep. 1979.

Primary Examiner—John D. Smith Attorney, Agent, or Firm—Jeffrey Van Myers

#### [7] ABSTRACT

A controlled quantity of a liquid polyimide precursor compound is deposited on the active surface of an integrated circuit die which has been prepared for packaging, and thereafter cured using a two step curing process to develop a polyimide coating of sufficient thickness to provide alpha particle protection for the die once packaged.

#### 12 Claims, 1 Drawing Figure

Aug. 28, 1984

4,468,411

#### METHOD FOR PROVIDING ALPHA PARTICLE PROTECTION FOR AN INTEGRATED CIRCUIT DIE

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The subject invention relates generally to methods for providing alpha particle protection for integrated circuit die, and, in particular, to a method for providing alpha particle protection for an integrated circuit die prior to the plastic encapsulation thereof.

#### 2. Description of the Prior Art

The phenomenon of charge carrier generation as a result of the passage of an alpha particle through the 15 active surface of an integrated circuit die has been known for many years. However, the effects were generally considered to be laboratory curiosities prior to the advent of high density, dynamic MOS memories wherein the stored data is represented by the presence 20 or absence of quantities of charge stored on capacitor portions of the storage cells. As improvements in fabrication processes allowed the shrinkage of the storage cells, the quantity of charge distinguishing a "zero" from a "one" shrank relative to the number of charge 25 carriers generated by a typical alpha particle impact. In April of 1978, T. C. Mays and M. H. Woods with the physical analysis laboratory of Intel Corporation first reported the protection of "soft" errors induced by alpha particles in such dynamic memories. (Proceedings 30 of the 1978 International Reliability Physics Symposium; see also "Alpha-Particle-Induced Soft Errors in Dynamic Memories," I.E.E.E. Transactions on Electron Devices, Vol. EE-26, January 1979).

Since 1978, efforts to prevent alpha particle induced 35 errors in integrated circuits have focused on three approaches: (1) to design the circuitry, particularly charge storage cells, with sufficiently high operating margins to ensure that the quantity of charge carriers generated by even very energetic alpha particles will be insuffi- 40 cient to effect the logic state; (2) packaging the integrated circuit using materials having very low levels of radioactive impurities such as uranium and thorium; and (3) protecting the active surface of the integrated circuit with a material which absorbs the alpha particles before 45 frame, comprising the steps of: depositing a selected they reach the surface. A fourth alternative, not available to the integrated circuit manufacturer, is to provide an error detection and correction in the system in which the sensitive circuit is used. Since alternative 1 typically requires an increased charge storage capability, the 50 resulting increase in die size will often be prohibitive. Alternative 2, while appearing to be the most advantageous, is very difficult to achieve and, with respect to plastic encapsulation, is presently unavailable due to the lack of any suitable filler material with sufficiently low 55 levels of contaminants. As a result of these and other limitations, attention has been focused upon alternative 3 in an effort to identify one or more techniques for shielding the surface of the integrated circuit from the alpha particles generated within the package material 60 itself.

In general, surface shielding has taken one of two forms: (1) a preformed tape of a suitably dense flexible material, such as polyimide, which can be adhered to the active surface of the integrated circuit prior to pack- 65 aging; and (2) a liquid material, such as a liquid polyimide precursor compound, which is dispensed upon the active surface of the die and allowed to spread over

the critical area and then cured prior to packaging. Development of the tape process has been severely impacted by the difficulty in physically attaching the tape to the integrated circuit die without damaging 5 either the die, the tape or the wire bonds connecting the circuit to the adjacent portions of the lead frame, and by difficulty in achieving consistant adhesion between the tape and the die so as to preclude separation during and after packaging. With respect to the liquid coating process, problems include poor coating to die surface adhesion as a result of improper formulation or contaminated die surfaces, insufficiently thick coating after curing to intercept alpha particles, and excessively thick coatings after curing resulted in shrink-induced separation or damage to the wire bonds or to die itself. However, at least one manufacturer, Hitachi Semiconductor Division of Japan, is currently marketing 64 K memory devices having a polyimide coating applied by a proprietary process using a liquid polyimide precursor compound currently marketed by the Hitachi Chemical Company of Japan. However, the Hitachi Chemical Company polyimide compound, while generally suitable for use in side braze packages, is generally unsuitable for use in hermetic cerdip packaging due to the intolerance of the required seal temperatures and the tendency to generate intolerable levels of internal cavity moisture. In addition, Hitachi Chemical Company offers no polyimide compound suitable for use of an integrated circuit die to be plastic encapsulated.

#### SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to provide a method for providing alpha particle protection for an integrated circuit die to be encapsulated in side braze, cerdip or plastic, as desired.

Another object of the present invention is to provide a method for dispensing a selected quantity of a liquid polyimide compound to provide alpha particle protection for an integrated circuit die.

These and other objects of the present invention are achieved in a method for providing alpha particle protection for an integrated circuit die which has been mounted on and electrically connected to a suitable lead quantity of a liquid polyimide precursor compound having a predetermined solids content and viscosity on the active surface of the die to form a liquid polyimide precursor coating thereon; curing the coating for a first time period at a temperature selected to reduce the volatile content thereof below a predetermined level, and then for a second time period at a temperature selected to substantially complete the imidization thereof and the removal of the remaining volatile content thereof; and, substantially immediately prior to encapsulating the coated die and selected adjacent portions of the lead frame, dehydrating the coating for a third time period at a temperature selected to remove moisture absorbed by the coating since the curing thereof if a significant period of time has elapsed since the curing of the coating.

To achieve a coating of consistent thickness, a method is provided for dispensing a selected quantity of the liquid coating material onto the active surface of the integrated circuit die, comprising the steps of: subjecting to a substantially constant, predetermined pressure a quantity of a liquid polyimide precursor compound having a predetermined solids content and viscosity;

and then directing for a predetermined length of time a portion of said compound through a conduit of predetermined cross-sectional area onto said surface.

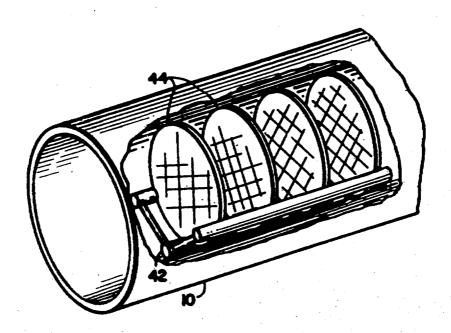

#### DESCRIPTION OF THE DRAWING

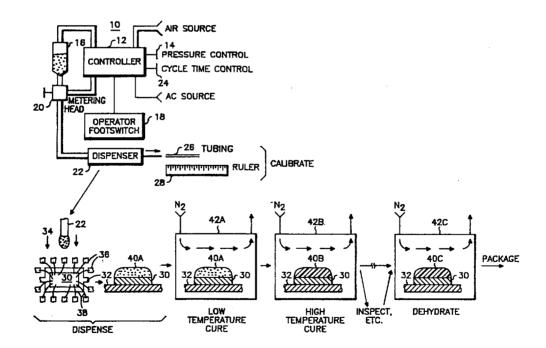

The single FIGURE illustrates the several steps comprising the method of the subject invention.

## DESCRIPTION OF THE PREFERRED METHOD

In the development of the preferred method of the 10 subject invention, considerable testing was done in order to determine the minimum thickness below which protection against the alpha particle radiation is insufficient to ensure that alpha particle induced soft errors during operation of the protected integrated circuit 15 remained below a specified limit. In general, this minimum thickness is a function of the sensitivity of the integrated circuit to be protected, the selected soft error tolerance limit, the flux density and energy distribution of the alpha particle radiation emanating from the pack- 20 aging materials, and the resistivity of the selected coating material after curing to the passage of alpha particles therethrough. For example, using the 64 K dynamic RAM integrated circuit commercially available from Motorola in a plastic package as part no. 25 MCM6665AP, the Dupont polyimide precursor commercially available as Pyralin PI2562 satisfies a soft error tolerance limit of 1 failure in 10,000 hours with a minimum thickness of 1 mil. However, testing of cured coatings of other polyimide precursor compounds have 30 been shown to exhibit similar alpha radiation shielding properties. While in general, coatings thicker than the minimum thickness provide extra insurance against alpha particle induced soft errors, shrinkage of the coating during the curing process may exert sufficient stress 35 upon the die to cause wire bond separation or, under extreme circumstances, die shear or coating separation. Tests have shown that a maximum thickness of the cured coating of the order of about 10 mils should preclude such damage.

Having established a minimum and a maximum thickness goal for the cured coating appropriate for providing the desired level of alpha particle protection for a particular integrated circuit die, the viscosity and solids contents of an appropriate liquid polyimide precursor 45 compound must be selected, since each affects the volume of compound necessary to produce the desired coating. In general, the viscosity of the selected liquid polyimide precursor compound must be low enough so that, when dispersed on the active surface of the inte- 50 grated circuit die, it will flow outward to the die edges and completely cover the active surface. On the other hand, the viscosity must not be so high that the polyimide precursor compound will flow over the edges of the die, possibly contaminating other portions of the die 55 assembly. Within these broad guidelines, a viscosity of the order of between about 75 and 200 centipoise has been found to be acceptable, although viscosities outside of this range may be acceptable from a functional standpoint in particular circumstances. While viscosity 60 affects the surface coverage characteristic of the liquid polyimide precursor compound, the solids content or percent of solids in the compound tends to affect the cross sectional configuration of the final cured coating. For example, liquid polyimide precursor compounds 65 containing less than about 15 percent solids have been found to produce a cured coating having a concave profile, thus undesirably thinning the cured coating

over the central portions of the integrated circuit die. On the other hand, a liquid polyimide precursor compound having a solids content above about 30 to 37 percent tends to a viscosity higher than desired, thus requiring such a large amount of liquid material to completely cover the die that the resulting coating is excessively thick. As a result, the mismatch of the coefficients of thermal expansion between the die and the coating often generates shear stress between the die and the coating sufficient to cause delamination or die fracture. Thus, a suitable liquid polyimide precursor compound will have a percents solids between about 20 and 30 percent and, preferably, between about 24 and 27 percent.

An initial estimate of the volume of the selected liquid polyimide precursor compound required to provide the desired cured coating thickness may be computed in a conventional manner using the solids/solvents ratio of the selected compound and the active surface area of the integrated circuit die to be protected. Using this estimate as the starting point, more accurate determinations of the required volume can be empirically determined using the actual die and curing process. Recalibration for the particular die should thereafter be necessary only if the composition of the selected compound varies or if the curing process is modified.

In the preferred process for practicing the present integrated circuit protection method shown in the FIG-URE, a precision fluid dispensing system 10 of the pneumatic type is employed. In the system 10, a controller 12 is coupled in a conventional manner to a compressed air source (not shown) and to an alternating current source (not shown). In operation, the controller 12 applies a substantially constant pressure selected via a pressure control knob 14 to a reservoir 16 containing a quantity of the selected liquid polyimide precursor compound. In response to the actuation of an operator footswitch 18, the controller 12 enables a metering head 20 to pass the pressurized polyimide precursor compound from the reservoir 16 to a hand-held dispenser 22 for a period of time determined by a cycle time control knob 24. One such precision fluid dispensing system 10 suitable for practicing the present method is the model 280J commercially available from the Tridak Division of Indicon Inc., Secor Road, Brookfield Center, Conn.

To calibrate the selected dispensing system 10, the pressure control knob 14 is set within the operating range of the controller 12 to suit the viscosity of the selected liquid polyimide precursor compound. The cycle time control knob 24 is then varied until the required volume is dispensed via the metering head 20. Periodically, the accuracy of the volume dispensed by the dispensing system 10 can be quickly verified by inserting the dispensing needle portion of the dispenser 22 into a short section of tubing 26 having substantially the same inner diameter as the outer diameter of the dispensing needle. The resulting length of the column of liquid polyimide precursor injected into the tubing 26 will then be equal to the polyimide precursor actually dispensed divided by the cross-sectional area of the tubing 26. This "gauge" length can be quickly verified using a ruler 28 or the like.

The present method is preferably performed after a given integrated circuit die 30 has been mounted for packaging, such as on the flag 32 of a conventional lead frame 34, and electrically connected to the appropriate conductor leads 36 via bonding wires 38. The dispens-

ing system 10 can then be selectively actuated via the operator footswitch 18 to deposit the selected quantity of the liquid polyimide precursor compound on the active surface of the die 30 to form a liquid polyimide precursor coating 40a thereon. The die assembly is then 5 placed in an oven 42a and heated to a temperature selected to reduce the solvent content of the coating 40a sufficiently slowly to preclude the formation of significant gas bubbles therein. For example, an upper temperature limit for this "low temperature cure" suitable for 10 the PI2562 polyimide precursor has been found to be between about 100° C. and 150° C. However, it is deemed preferable to operate the oven 42a somewhat below the particular upper temperature limit to minimize the likelihood of bubble generation, even though 15 to do so may extend slightly the low temperature curing time. This low temperature cure should be continued until at least about 95% of the solvent content of the coating 40a has been driven off, typically between about 1 and 4 hours. It has been discovered that the 20 temperature of the oven 42a should be ramped from about ambient up to the selected low cure temperature, in order to minimize the likelihood of delamination of the coating 40a during the subsequent high temperature cure thereof. This can be accomplished directly by 25 using a suitably equipped oven 42a or indirectly by simply overloading an oven 42a capable of bringing the overload up to the desired temperature within about 15 to 30 minutes of loading. One oven found particularly well suited for performing the low temperature cure 30 using the latter indirect ramping technique is the Model 5851 commercially available from the National Appliance Company of Portland, Oreg.

After the low temperature cure, the partially cured coating 40b is then raised to a temperature selected to 35 substantially complete the imidization thereof and the removal of the remaining solvent content thereof and the water molecules released during the imidization process. The lower temperature limit for this "high temperature cure" should be sufficient to sustain the 40 imidization process, while the upper temperature limit is generally dictated by the tolerance of the die assembly. A suitable temperature for performing this high temperature cure for the PI2562 polyimide precursor is between about 250° C. and 450° C., and preferably be- 45 of: tween about 300° C. and 350° C. A curing time between about 1 and 4 hours has been found suitable when using the latter preferred temperature range. Although the oven 42b used to perform the high temperature cure may be the same as the oven 42a used to perform the 50 low temperature cure, the time consumed in temperature ramping may be saved by using different ovens. An oven found suitable for performing the high temperature cure is the model POM256-B.1 commercially available from the Blue M Electric Company of Blue Island, 55

To facilitate the removal of all of the solvents from the coating 40a-40b, each of the ovens 42a and 42b should be plumbed with nitrogen (N<sub>2</sub>) so that a flow of dry nitrogen can be maintained therethrough during 60 both the low temperature cure and the high temperature cure. However, if the die assembly is of the ceramic type and the selected high cure temperature exceeds the melting point of the glass material in the package, dry filtered air is preferred rather than nitrogen in order to 65 minimize migration of the lead plating material.

After the high temperature cure, the die 30 and particularly the coating 40c thereon, should be inspected to

identify any significant mechanical defects in the die 30 or the coating 40c. Those die assemblies which exhibit die sheer or fracture, wire bond separation or shorting, or similar defects should be eliminated from further processing to minimize expense. Such an inspection should preferably be conducted under a laminar flow hood using a suitable microscope (not shown).

Although it is known that the cured polyimide coating 40c is hygroscopic, it has been discovered that the rate of moisture absorption following the high temperature cure proceeds surprisingly rapidly. Tests have shown that after only 2 hours following the high temperature cure, the coating 40c may absorb a sufficient amount of moisture from the ambient atmosphere to adversely affect the environment around the integrated circuit die 30 once packaged. Accordingly, in the preferred method, the coating 40c is dehydrated in an oven 42c at a temperature selected to remove any moisture absorbed by the coating 40c since the curing thereof, substantially immediately prior to the packaging of the coated integrated circuit die 30 whether in plastic as shown in the FIGURE, or in ceramic. For the PI2562 polyimide precursor, a dehydration temperature between about 280° C. and 450° C. has been found suitable, so long as the drying time is at least about 10 minutes. The oven model POM256-B.1 commercially available from the Blue M Electric Company has been found suitable for performing the pre-packaging dehydration of this coating 40c. As in the low temperature cure and the high temperature cure, it is preferred to provide a continuous flow of dry nitrogen, or air in the case of a ceramic package, through the oven 42c during the dehydration to insure rapid removal of the moisture driven out of the coating 40c.

Since many changes and modifications may be made to the several steps of the methods disclosed herein without departing from the spirit and scope of the present invention, it is therefore intended that the following claims cover all such changes and modifications.

I claim:

1. A method for providing alpha particle protection for an integrated circuit die which has been mounted for packaging and electrically connected to conductor leads integral with such packaging, comprising the steps of:

depositing a selected quantity of a liquid polyimide precursor compound having a predetermined solids content and viscosity on the active surface of the die to form a liquid polyimide precursor coating thereon:

curing the coating for a first time period at a first temperature selected to reduce the volatile content thereof below a predetermined level, and for a second time period at a second temperature selected to substantially complete the imidization thereof and the removal of the remaining volatile content thereof; and

substantially immediately prior to packaging the coated die, dehydrating the coating for a third time period at a third temperature selected to remove moisture absorbed by the coating since the curing thereof.

2. The method of claim 1 wherein the step of curing the coating for a first time period is performed at a first temperature selected to reduce the volatile content thereof below said predetermined level sufficiently slowly to preclude the formation of significant gas bubbles therein.

3. The method of claim 2 wherein said first time period comprises until at least about 95% of the solvent content of said coating has been driven off.

4. The method of claim 1 or 2 further including the

inspecting the die and the coating thereon after the curing thereof to identify any significant mechanical defects in the die and coating; and

formed after the inspection of the die and the coating

5. The method of claim 1 or 2 wherein the step of depositing said selected quantity of said liquid polyimide precursor compound comprises the steps of:

subjecting to a substantially constant, predetermined pressure a quantity of said liquid polyimide precursor compound; and

directing for a fourth predetermined length of time a 20 portion of said compound through a conduit of predetermined cross-sectional area onto said sur-

6. The method of claim 5 including the further step of:

periodically dispensing one of said portions of said compound into a length of tubing of predetermined cross-sectional area and verifying that the resulting length of the column of said compound in said tubing is substantially equal to a predetermined gauge length.

7. The method of claim 1 or 2 wherein said first temperature is selected between about 100° C. and 150° C.

8. The method of claim 1 or 2 wherein said second wherein the step of dehydrating the coating is per- 10 temperature is selected between about 250° C. and 450° C., and preferably, between about 300° C. and 350° C.

9. The method of claim 1 or 2 wherein the step of curing the coating is performed in a flow of dry nitro-

10. The method of claim 1 or 2 wherein the step of dehydrating the coating is performed in a flow of dry nitrogen.

11. The method of claim 1 or 2 wherein the liquid polyimide precursor compound has a solids content between about 20 and 30 percent, and preferably between about 24 and 27 percent.

12. The method of claim 1 or 2 wherein the liquid polyimide precursor compound has a viscosity of the order of between about 75 and 200 centipoise.

30

35

40

45

50

60

55

| United | <b>States</b> | Patent | [19] |

|--------|---------------|--------|------|

|--------|---------------|--------|------|

[11]

Candelaria et al.

| [45] | May 1, 1984 |

|------|-------------|

|      |             |

4,446,194

| [54]         | DUAL LA                    | YER                 | PASSIVATION                                                  |

|--------------|----------------------------|---------------------|--------------------------------------------------------------|

| [75]         | Inventors:                 | Jon<br>Hei          | Candelaria, Mesa, Ariz.; Kurt S. dinger, Santa Clara, Calif. |

| [73]         | Assignee:                  | Mo                  | torola, Inc., Schaumburg, Ill.                               |

| [21]         | Appl. No.                  | : 391               | ,047                                                         |

| [22]         | Filed:                     | Jun                 | . 21, 1982                                                   |

| [51]<br>[52] | U.S. Cl                    | ••••••              | B05D 3/14<br>428/428; 357/54;<br>427/39; 427/93; 428/432     |

| [58]         | Field of S                 | <b>earch</b><br>427 |                                                              |

| [56]         |                            | Re                  | ferences Cited                                               |

|              | U.S.                       | PAT                 | ENT DOCUMENTS                                                |

|              | 3,560,810 2<br>4,076,575 2 | /1971<br>/1978      | Balk et al                                                   |

| 4,086,614 | 4/19/8 | Scheidel       | 44//93 |

|-----------|--------|----------------|--------|

| 4,091,406 | 5/1978 | Lewis          | 427/94 |

| 4,091,407 | 5/1978 | Williams et al | 427/94 |

|           |        |                |        |

Primary Examiner-John H. Newsome Attorney, Agent, or Firm-Robert M. Handy

## **ABSTRACT**

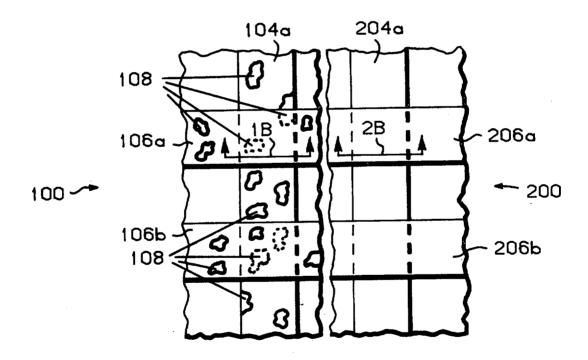

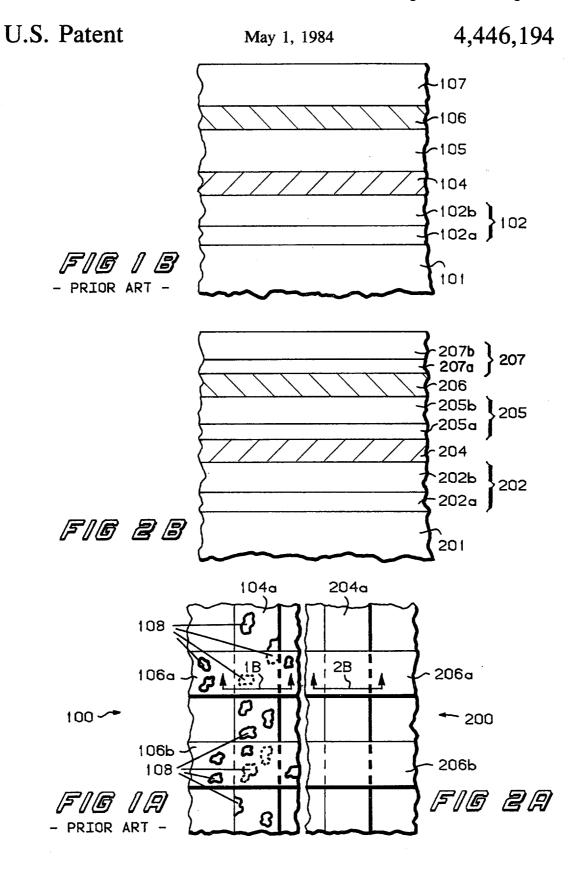

When multilayer-metal electronic devices are heated, voids can form in the metal layers. Void formation is avoided by using a double dielectric layer as the interlayer dielectric. The double layer has a first oxide layer portion in contact with the first metal which is formed by plasma assisted chemical vapor deposition, and a second oxide layer portion formed by other means. The plasma formed oxide layer portion is believed to be in compressive stress relative to the substrate.

12 Claims, 4 Drawing Figures

#### **DUAL LAYER PASSIVATION**

#### **BACKGROUND OF THE INVENTION**

#### 1. Field of the Invention

This invention relates, in general, to means and methods for improved electronic devices, especially semiconductor devices and integrated circuits, and more particularly, to an improved manufacturing process for structures involving passivated metal layers or multiple passivated metal layers on nitride passivated substrates, and to structures, devices, and circuits made thereby.

#### 2. Background Art

It is common practice in the manufacture of semiconductor devices and integrated circuits, and other electronic devices as well, to protect the semiconductor surface and the metal surface layers with a covering dielectric. This dielectric is referred to as the passivation layer or the metal passivation layer, and is often the outermost layer of the device. Openings are provided in the passivation layer through which external connections to the device may be made. As used herein, the word "device" is intended to include both individual devices, portions of devices, and collections of devices, as for example in integrated circuits and the like.

Frequently, a device will require multiple metal layers, one crossing over the other and separated by an interlayer dielectric. In this case the interlayer dielectric serves to passivate the first metal layer as well as insulate and separate it from the overlying second metal layer. Interlayer connection points are provided through openings formed for that purpose in the passivation layer serving as the interlayer dielectric.

With semiconductor and other devices having con- 35 ductive substrates, a primary dielectric layer is also required between the substrate and any metal layers. This dielectric serves to passivate the substrate surface as well as insulate it from the metal layer or layers. Again, openings may be provided for connection 40 points. When structures involving one or more metal layers superimposed on a dielectric layer and covered by a passivation layer are heated during subsequent manufacturing stages, as for example during assembly die bonding, it is found that voids frequently form in the 45 metal layer or layers. These voids can be of appreciable size relative to the thickness and width of the metal conductor paths. The voids create weaknesses in the conductor paths which lead to reduced manufacturing yield and poorer reliability. This phenomenon is partic- 50 ularly severe when an aluminum alloy is used for the metal layer or layers and one of the several dielectric layers includes a nitride material. Thus, a need exists for a system of materials and manufacturing methods which reduces or eliminate the formation of voids in layered 55 structures wherein one or more metal layers are sandwiched between dielectric layers. Because of their widespread use, there is a particular need for reducing or eliminating void formation in silicon oxide-nitride—aluminum alloy—doped oxide layer structures. 60

Accordingly, it is an object of this invention to provide an improved manufacturing method for the formation of metal—passivation layer structures wherein void formation in the metal layer is reduced or eliminated.

It is a further object of this invention to provide an 65 improved manufacturing method for the formation of dielectric—first metal—first passivation—second metal—second passivation layer structures wherein

void formation in one or both metal layers is reduced or eliminated.

It is an additional object of this invention to provide an improved process for the manufacture of dielectric—metal—passivation layer structures and/or dielectric—first metal—first passivation layer—second metal—second passivation layer structure, wherein the passivation layer or layers comprise a double layer.