US1DOCS 7696897v2

## COMPLAINT FOR DECLARATORY JUDGMENT

Plaintiff Broadcom Corporation ("Broadcom"), brings this action against CSR plc, SiRF Technology Holdings, Inc., and SiRF Technology, Inc. (collectively "Defendants") to obtain a declaratory judgment that United States Patent Nos. 6,526,322 ("the '322 patent"), 6,775,319 ("the '319 patent"), 6,930,634 ("the '634 patent") and 5,897,605 ("the '605 patent") (collectively, the patents-in-suit) are not infringed by Plaintiff and are invalid. A true and correct copy of the patents-in-suit are attached hereto as Exhibits A-D. Plaintiff alleges as follows:

## **THE PARTIES**

- 1. Plaintiff Broadcom is a corporation organized under the laws of California with its principal place of business at 5300 California Ave., Irvine, California 92617.

- 2. Upon information and belief, Defendant CSR plc is a corporation registered in the United Kingdom with its principal place of business at Churchill House, Cambridge Business Park, Cowley Road, Cambridge, CB4 0WZ United Kingdom, and with its U.S. headquarters in California.

- 3. Upon information and belief, Defendant SiRF Technology Holdings, Inc., a wholly-owned subsidiary of CSR plc, is a Delaware corporation with its principal place of business at 217 Devcon Drive, San Jose, California 95112.

- 4. Upon information and belief, Defendant SiRF Technology, Inc. a wholly-owned subsidiary of Defendant SiRF Technology Holdings, Inc., is a Delaware corporation with its principal place of business at 217 Devcon Drive, San Jose, California 95112.

# **FACTUAL BACKGROUND**

5. Since 2006, Broadcom and CSR have litigated at least three related patent infringement suits in the United States District Court for the Central District

-1-

COMPLAINT FOR DECLARATORY JUDGMENT OF NON-INFRINGEMENT AND INVALIDITY

of California. These actions all involve substantially the same or similar products,

Selna has presided over these three cases for nearly four years, and all involve

6. On December 15, 2006, Defendant SiRF Technology, Inc. filed a patent infringement action against Global Locate, Inc. in the United States District Court for the Central District of California. SiRF Technology, Inc. v. Global Locate, Inc., 06-cv-01216-JVS-MLG (C.D. Cal.). SiRF Technology, Inc. alleged

that Global Locate, Inc. infringed patents related to GPS and wireless technology. Broadcom acquired Global Locate, Inc. on or about June 12, 2007. A true and

correct copy of the Complaint is attached hereto as Exhibit E.

- 7. On May 14, 2008, Broadcom filed a patent infringement action against Defendant SiRF Technology Inc. in the United States District Court for the Central District of California. *Broadcom Corp. v. SiRF Technology, Inc.*, 08-cv-00546-JVS-MLG (C.D. Cal.). Broadcom alleged that SiRF's GPS receivers and multimedia processors for GPS devices infringed patents owned by Broadcom. A true and correct copy of the Complaint is attached hereto as Exhibit F.

- 8. On August 20, 2010, CSR filed a complaint against Broadcom in the United States District Court for the Central District of California, alleging that Broadcom infringed nine of its patents relating to GPS and wireless technology. *CSR plc v. Broadcom Corp.*, No. 10-cv-01281-JVS-MLG (C.D. Cal.). A true and correct copy of the Complaint is attached hereto as Exhibit G.

- 9. On October 13, 2010, CSR filed another related action against Broadcom, this time in the United States District Court for the District of Delaware. *CSR plc v. Broadcom Corp.*, No. 10-cv-876-SLR (D. Del). CSR now alleges that Broadcom infringed the '322, '319, '634 and '605 patents, all

1 2 3

5

4

6 7

8

9

10 11

12

13

14

15 16

17

18 19

20

21 22

23 24

25

26

27

28

previously unasserted against Broadcom or its subsidiaries, which all relate generally to the GPS and wireless technology at issue in the actions pending before Judge Selna in this District. A true and correct copy of the Complaint is attached hereto as Exhibit H.

# JURISDICTION AND VENUE

- This is a declaratory judgment action seeking a declaration of non-10. infringement and/or invalidity of the claims of the '322, '319, '634 and '605 patents. This Court has subject matter jurisdiction over this action pursuant to 28 U.S.C. §§ 1331, 1338(a), 2201, and 2202. As CSR has asserted the '322, '319, '634 and '605 patents against Broadcom in an action brought in the United States District Court for the District of Delaware, an actual case or controversy exists between the parties. With the filing of this Complaint, Broadcom expects to concurrently move that the Delaware court transfer venue of the action to this District.

- Venue is proper in the Central District of California pursuant to 28 11. U.S.C. §§ 1391.

# **COUNT I**

# (Non-Infringement)

- Broadcom repeats and realleges the allegations of paragraphs 1-11 as 12. if fully set forth herein.

- Broadcom does not infringe or willfully infringe any valid and 13. enforceable claims of the '322, '319, '634 and/or '605 patents.

- To resolve the legal and factual questions raised by CSR and to afford 14. relief from the uncertainty and controversy which CSR's accusations have precipitated, Broadcom is entitled to a declaratory judgment that it does not

1 2

2

3

4 5

6 7

8

11 12

10

13

1415

16

17 18

19

2021

2223

24

2526

27

28

infringe or willfully infringe any valid and enforceable claim of the '322, '319, '634 and/or '605 patents.

## **COUNT II**

## (Invalidity)

- 15. Broadcom repeats and realleges the allegations of paragraphs 1-11 as if fully set forth herein.

- 16. One or more claims of the '322, '319, '634 and/or '605 patents are invalid under one or more provisions of Title 35 of the United States Code, including but not limited to 35 U.S.C. §§ 102, 103, and 112.

- 17. To resolve the legal and factual questions raised by CSR and to afford relief from the uncertainty and controversy which CSR's accusations have precipitated, Broadcom is entitled to a declaratory judgment that one or more of the claims of the '322, '319, '634, and/or '605 patents are invalid.

## PRAYER FOR RELIEF

WHEREFORE, Broadcom requests entry of judgment in its favor and against CSR as follows:

- A. Declaring that Broadcom does not infringe or willfully infringe the '322 patent and/or that one or more of the claims of the '322 patent are invalid.

- B. Declaring that Broadcom does not infringe or willfully infringe the '319 patent and/or that one or more of the claims of the '319 patent are invalid.

- C. Declaring that Broadcom does not infringe or willfully infringe the '634 patent and/or that one or more the claims of the '634 patent are invalid.

- D. Declaring that Broadcom does not infringe or willfully infringe the '605 patent and/or that one or more of the claims of the '605 patent are invalid.

- E. Finding that this is an exceptional case under 35 U.S.C. § 285 and awarding Broadcom the costs and expenses of this litigation, including reasonable attorneys' fees and disbursements; and

Awarding Broadcom other such relief as is just and proper. F. 1 **DEMAND FOR JURY TRIAL** 2 Broadcom demands a trial by jury on all issues so triable. 3 4 5 Dated: October 28, 2010 6 Respectfully submitted, 7 Of Counsel: William F. Lee Wilmer Cutler Pickering Hale and Dorr 9 60 State Street Boston, Massachusetts 02109 (617) 526-6000 (617) 526-5000 10 James Dowd Michael Jay 11 David B. Bassett 12 David A. Manspeizer 350 South Grand Avenue, Suite 2100 Los Angeles, CA 90071 (213) 443-5300 (213) 443-5400 Nicole E. Feit 13 Brian Sutherland Wilmer Cutler Pickering Hale and Dorr 14 399 Park Avenue New York, NY 10022 15 (212) 295-6358 16 '212) 230-8888 **ATTÓRNEYS FOR PLAINTIFFS** 17 BROADCOM CORPORATION 18 19 20 21 22 23 24 25 26 27

Wilmer Cutler Pickering Hale and Dorr

28

# **EXHIBIT A**

# (12) United States Patent

Peng et al.

#### (10) Patent No.: US 6,526,322 B1

(45) Date of Patent: Feb. 25, 2003

### (54) SHARED MEMORY ARCHITECTURE IN **GPS SIGNAL PROCESSING**

(75) Inventors: Leon Kuo-Liang Peng, Mountain

View, CA (US); Henry D. Falk, Long

Beach, CA (US)

(73) Assignee: SiRF Technology, Inc., San Jose, CA

Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/465,985

(22) Filed: Dec. 16, 1999

(51) Int. Cl.<sup>7</sup> ...... G05B 19/42; G01C 21/02

**U.S. Cl.** ...... 700/5; 701/213; 711/148

342/357.05, 357.06, 357.07, 357.12; 711/147, 148; 701/213-215

#### (56)References Cited

### U.S. PATENT DOCUMENTS

| 4,426,712 | Α | 1/1984  | Gorski-Popiel 375/343      |

|-----------|---|---------|----------------------------|

| 4,445,118 | Α | 4/1984  | Taylor et al 342/357.09    |

| 4,463,357 | Α | 7/1984  | MacDoran 342/460           |

| 4,578,678 | Α | 3/1986  | Hurd 342/357.12            |

| 4,667,203 | Α | 5/1987  | Counselman, III 342/357.06 |

| 4,701,934 | Α | 10/1987 | Jasper 375/147             |

| 4,754,465 | Α | 6/1988  | Trimble 375/376            |

| 4,785,463 | Α | 11/1988 | Jane et al 375/147         |

| 4,809,005 | Α | 2/1989  | Counselman, III 342/352    |

| 4,821,294 | Α | 4/1989  | Thomas, Jr 375/343         |

| 4,884,041 | Α | 11/1989 | Walker 331/57              |

| 4,890,233 | Α | 12/1989 | Ando et al 701/224         |

| 4,894,662 | Α | 1/1990  | Counselman 342/357.15      |

| 4,998,111 | Α | 3/1991  | Ma et al 342/352           |

| 5,014,066 | Α | 5/1991  | Counselman, III 342/352    |

| 5,036,329 | Α | 7/1991  | Ando 342/357.12            |

| 5,043,736 | Α | 8/1991  | Darnell et al 342/357.1    |

| 5,108,334 | Α | 4/1992  | Eschenbach et al 455/314   |

| 5,172,076 | Α | 12/1992 | Brown 331/57               |

| 5,202,829 | Α | 4/1993  | Geier 701/215              |

|           |   |         |                            |

| 5,225,842 A | 7/1993 | Brown et al 342/357.09   |

|-------------|--------|--------------------------|

| 5,293,170 A | 3/1994 | Lorenz et al 342/352     |

| 5,311,195 A | 5/1994 | Mathis et al 342/357.14  |

| 5,323,164 A | 6/1994 | Endo 342/357.15          |

| 5,343,209 A | 8/1994 | Sennott et al 342/357.02 |

| 5,345,244 A | 9/1994 | Gildea et al 342/357.12  |

| 5,347,536 A | 9/1994 | Meehan 375/148           |

(List continued on next page.)

### FOREIGN PATENT DOCUMENTS

| EP | WO 90/11652 | 10/1990 |

|----|-------------|---------|

| EP | 0511741     | 11/1993 |

| GB | 2115195     | 1/1983  |

| JP | 58-105632   | 6/1983  |

| JP | 7-36035     | 5/1986  |

| JP | 4-326079    | 11/1992 |

### OTHER PUBLICATIONS

Mark Moeglein et al., document, "An Introduction to Snap Track™ Server-Aided GPS Technology", 11pp, (undated). Mark Markoff, As Seen in The New York Times: Deals to Move Global Postitioning Technology Toward Everyday Use, Article, The New York Times, © 1998, 1pp.

Primary Examiner—Paul P. Gordon (74) Attorney, Agent, or Firm-Thomas, Kayden, Horstemeyer & Risley, LLP

#### (57)**ABSTRACT**

A shared memory architecture for a GPS receiver, wherein a processing memory is shared among the different processing functions, such as the correlator signal processing, tracking processing, and other applications processing. The shared memory architecture within the GPS receiver provides the memory necessary for signal processing operations, such as the massively parallel processing, while conserving memory cost by re-using that same memory for other GPS and non-GPS applications. The shared memory architecture for a GPS receiver provided in accordance with the principles of this invention thereby significantly minimize the costly memory requirement often required of extremely fast signal acquisition of a GPS receiver.

### 10 Claims, 8 Drawing Sheets

# US 6,526,322 B1 Page 2

| U.S. PATENT         | DOCUMENTS              |                                  | Tso et al.                   |

|---------------------|------------------------|----------------------------------|------------------------------|

| 5 370 224 A 1/1005  | Brown et al. 701/215   | -, -,,                           | Loomis et al.                |

|                     | Brown et al 701/215    | 5,920,283 A 7/1999               |                              |

|                     | McBurney et al 701/213 |                                  | Pon et al.                   |

|                     | Washizu et al 375/208  |                                  | Sakumoto et al.              |

|                     | Geier et al.           |                                  | Loomis et al.                |

| 5,418,538 A 5/1995  |                        |                                  | Hanson et al.                |

|                     | Johnson                |                                  | Krasner                      |

| 5,420,593 A 5/1995  |                        |                                  | Stansell, Jr.                |

|                     | Osterdock et al.       |                                  | Harrison et al.              |

|                     | Woo et al.             | 5,982,324 A 11/1999              | Watters et al.               |

|                     | Gilbert                | 5,983,109 A 11/1999              | Montoya                      |

|                     | Lau et al.             | 5,987,016 A 11/1999              | He                           |

|                     | Cooper et al.          | 5,999,124 A 12/1999              | Sheynblat                    |

|                     | Lau et al.             | 5,999,125 A 12/1999              | Kurby                        |

|                     | Misra                  | 6,002,362 A 12/1999              | Gudat                        |

|                     | Loomis et al.          | 6,002,363 A 12/1999              | Krasner                      |

|                     | Sutardja et al.        | 6,009,551 A 12/1999              | Sheyblat                     |

|                     | Krasner                | 6,011,509 A 1/2000               | Dutka                        |

| 5,663,735 A 9/1997  | Eshenbach              | 6,014,101 A 1/2000               | Loomis                       |

| 5,764,184 A 6/1998  | Hatch et al.           |                                  | Krasner                      |

|                     | Krasner                |                                  | Horton et al.                |

| 5,786,789 A 7/1998  | Janky                  |                                  | Cahn et al.                  |

| 5,796,662 A 8/1998  | Kalter at al.          |                                  | Krasner                      |

| 5,812,087 A 9/1998  | Krasner                |                                  | Sheyblat                     |

| 5,825,327 A 10/1998 | Krasner                |                                  | Krasner                      |

| 5,828,694 A 10/1998 | Schipper               | * *                              | Krasner                      |

| 5,831,574 A 11/1998 | Krasner                |                                  | Krasner                      |

| 5,841,396 A 11/1998 | Krasner                |                                  | Krasner                      |

| 5,845,203 A 12/1998 | LaDue                  |                                  | Krasner                      |

| 5,854,605 A 12/1998 | Gildea                 |                                  | Girerd et al.                |

| 5,874,914 A 2/1999  | Krasner                | 6,133,871 A 10/2000              |                              |

| 5,877,724 A 3/1999  | Davis                  | 6,133,873 A 10/2000              |                              |

| 5,877,725 A 3/1999  | Kalfaus                | 6,133,874 A 10/2000              |                              |

| 5,883,594 A 3/1999  | Lau                    | 6,150,980 A 11/2000              |                              |

|                     | Krasner                |                                  | Lin                          |

|                     | LaDue                  |                                  | Dougherty et al 342/357.12   |

|                     | Kohli et al.           |                                  | Niles                        |

|                     | Kohli et al.           |                                  | Kovach, Jr. et al 455/456    |

|                     | Milton et al.          | 0,517,00 <del>4</del> B1 11/2001 | 150 vacii, 31. ct ai 455/450 |

|                     | Molnar et al.          | * cited by examiner              |                              |

| -, -, 0/2000        |                        | · - J                            |                              |

U.S. Patent

Feb. 25, 2003

Sheet 1 of 8

US 6,526,322 B1

U.S. Patent

Feb. 25, 2003

Sheet 2 of 8

US 6,526,322 B1

FIG.2

U.S. Patent Feb. 25, 2003 Sheet 3 of 8 US 6,526,322 B1

U.S. Patent

Feb. 25, 2003

Sheet 4 of 8

US 6,526,322 B1

U.S. Patent Feb. 25, 2003 Sheet 5 of 8 US 6,526,322 B1

U.S. Patent US 6,526,322 B1 Feb. 25, 2003 Sheet 6 of 8 OR CAN BE USED AS FAST SAMPLE 0 Q ACCUM LOCAL RAM STORAGE) DATA STORAGE AREA REACQUISITION MODES SAMPLES STORAGE CPU CACHE TAG & IN TRACK MODE MULTIPATH/E-L MEMORY USAGE TRACK AND DURING SAMPLE 0 IACCUM 0x17f 0x180 0x078 0x07f 0x178 0x1f8 0x1ff 0x0f7 0x0f8 0x0ff 0x0800x1f7 0x077 NOT USED NOT USED SAMPLE 0 NOT USED NOT USED SAMPLE 3 SAMPLE 2 Q ACCUM Q ACCUM Q ACCUM SAMPLE 1 Q ACCUM **ACQUISITION MODES** MEMORY USAGE DURING NOT USED NOT USED NOT USED NOT USED SAMPLE 0 SAMPLE 2 SAMPLE 3 I ACCUM I ACCUM SAMPLE 1 I ACCUM I ACCUM

**TAP 238**

**TAP 239**

TAP 0

TAP

TAP

FIG.6

U.S. Patent

Feb. 25, 2003

Sheet 7 of 8

859

US 6,526,322 B1

| 759 | ACQUISITION MODE FOR IQSQRAM MEMORY MAP | DESCRIPTIONS  | IQSQ NON-COHERENT ACCUMULATION DATA | G1/G2 LOOKUP TABLE | TRACKING PROCESSING FOR CHANNEL 0 PARAMETERS | NOT USED      |

|-----|-----------------------------------------|---------------|-------------------------------------|--------------------|----------------------------------------------|---------------|

|     | DE FOR I                                | # OF<br>WORDS | 1920                                | 128                | 128                                          | 128           |

|     | <b>QUISITION MC</b>                     | FUNCTION      | IQSQ ACCUM                          | G1/G2              | TRACK CHO                                    | SPARE         |

|     | AC                                      | 12 BITS ADDR  | 0x000 - 0x77f                       | 0x780 - 0x7ff      | 0x800 - 0x87f                                | 0x880 - 0x8ff |

TRACKING PROCESSING PARAMETERS AND DATA IQSQ NON-COHERENT ACCUMULATION DATA CONVOLUTION DECODER PARAMETERS TRACK/REACQUISITION MODE FOR IQSQRAM MEMORY MAP DESCRIPTIONS CONVOLUTION DECODER DATA TRACKING PROCESSING DATA NOT USED #OF WORDS 1664 240 256 16 2 2 IQSQ/IQ ACCUM CONVOLUTION CONVOLUTION FUNCTION TRACKING TRACKING SPARE 12 BITS ADDR 0x000 - 0x0ef 0x200 - 0x23f 0x240 - 0x27f 0x100 - 0x1ff 0x280 - 0x8ff 0x0f0 - 0x0ff

FIG.7

U.S. Patent

Feb. 25, 2003

Sheet 8 of 8

US 6,526,322 B1

FIG. 9

### US 6,526,322 B1

### 1

# SHARED MEMORY ARCHITECTURE IN GPS SIGNAL PROCESSING

### FIELD OF INVENTION

This invention relates to the field of GPS receivers.

### BACKGROUND OF INVENTION

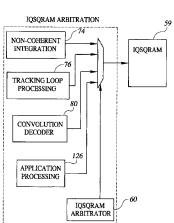

FIG. 1 illustrates a typical GPS radio receiver 10, while FIG. 2 provides a general flow chart illustrating the general operations of GPS receiver 10 such as a satellite signal acquisition, tracking, or re-acquisition, and navigational processing. As illustrated in the simplified block diagram of a typical GPS receiver 10 shown in FIG. 1, a signal processing block 20 is provided to perform satellite signal acquisition and processing on a digitized IF signal 19 received via receiver antenna 12. Signal processing block 20 typically performs a two-dimensional search for a satellite signal, in time (code phase) and frequency. To decrease the 20 amount of time needed for GPS signal acquisition in time, and frequency domains, a massively parallel architecture is usually required for searching in parallel a large number of code positions and frequency uncertainties. In the code phase search, the required number of code positions is 25 directly related to initial time uncertainty. A large number of corellators allows a quick, parallel search of many code positions. In the frequency search, a large number of frequency bins architecture speeds up searching multiple fretime for search.

As illustrated in FIG. 1, signal processing 20 consists of three functional stages: a first stage consists of channel correlation signal processing 22 that compares (or correlates) digitized signal 19 with a locally generated code 35 that attempts to replicate the P or C/A code generated by a satellite. The replica code searches a "space" that consists of the unique codes generated by the different satellites, the temporal position of the code being sent at any given time, and the Doppler frequency offset caused by the relative 40 motion of the satellite and user. Generally, correlator signal processing unit 22 can perform parallel correlations with multiple code/position/doppler combinations simultaneously in a multiple channel fashion, usually up to 12. The next functional stage of signal processing 20 comprises 45 tracking processing unit 24, typically provided by a tracking processing CPU. The tracking processing CPU uses correlator information from correlator signal processing unit 22 to ascertain the probability of correctness of a code/position/ doppler combination and to "follow", or track, that signal 50 once it is found. Tracking processing unit 24 includes having the tracking CPU program the correlator signal processing unit 22 where to search for a GPS satellite signal. Once a signal is found and locked onto, the tracking CPU also extracts the 50 Hz modulated data that contains navigation 55 information transmitted by the GPS satellite. Finally, a navigation processing unit 26, comprising a navigation processing CPU, uses data collected by the correlator signal processing unit 22 and tracking processing unit 24 to perform the calculations to determine the user's position, 60 velocity, and time.

In the typical GPS signal processing **20**, an associated and dedicated memory unit is coupled to each functional unit stage. Thus, correlator signal processing unit **22** is typically coupled to an associated dedicated correlation processing 65 memory unit **28** shown in FIG. 1. Coherent and noncoherent I & Q samples are stored in correlation processing

### 2

memory 28 received from correlator signal processing unit 22. Tracking processing unit 24 is coupled to a tracking unit memory 30 to store the code, data, and parameters utilized by the tracking processor CPU for acquisition and tracking processing such as, for example, carrier loops, code loops, code lock detect, costas lock detect, bit synchronization, data demodulation. Navigation processing unit 26 is coupled to a navigation processing memory 32 for storing the code and data for the navigation processing CPU, such as calculation of position and time.

Thus, in operation, typical GPS receiver 10 requires significant hardware and memory to search, utilizing a large number of correlators and multiple frequency bins to implement. For example, an 8 frequency bin search should reduce the search time by a factor of 8 but it will require 4 times the memory to store the coherent integration samples and 8 times the memory to store the non-coherent integration samples. In order to achieve low cost, commercial GPS receiver architectures are deterred from using massively parallel architectures to avoid the cost of massively parallel implementation. There is therefore a need for a GPS signal processing architecture that minimizes the costly memory requirement and still achieves extremely fast signal acquisition.

### SUMMARY OF INVENTION

A shared memory architecture for a GPS receiver is provided, wherein a processing memory is shared among the different processing functions, such as the correlator signal processing. The shared memory architecture within the GPS receiver provided, wherein a processing functions, such as the correlator signal processing. The shared memory architecture within the GPS receiver provided, wherein a processing functions, such as the correlator signal processing. The shared memory architecture within the GPS receiver provided, wherein a processing functions, such as the correlator signal processing. The shared memory architecture within the GPS receiver provides the memory architecture within the GPS receiver provided, wherein a processing functions, such as the correlator signal processing. The shared memory architecture within the GPS receiver provides the memory architecture within the GPS receiver provides the memory architecture within the GPS receiver provided, wherein a processing functions, such as the correlator signal processing. The shared memory architecture within the GPS receiver provides the memory architecture for a GPS receiver is provided, wherein a processing functions, such as the correlator signal processing. The shared memory architecture within the GPS receiver provides the memory architecture within the GPS and non-GPS applications. The shared memory architecture within the GPS receiver provides the memory architecture within the GPS architecture for a GPS receiver provides the memory architecture within the GPS receiver provides the memory architecture within the GPS and non-GPS applications. The shared memory architecture within the GPS receiver provides the memory architecture within the GPS architecture within the G

### BRIEF DESCRIPTION OF DRAWINGS

FIG. 1 is a block diagram describing a prior art GPS receiver.

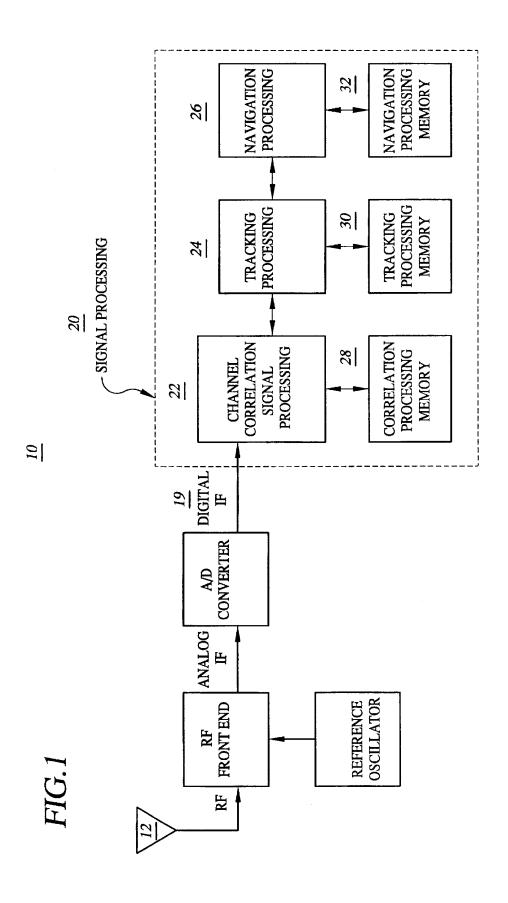

FIG. 2 is a flowchart describing the operation of a GPS receiver.

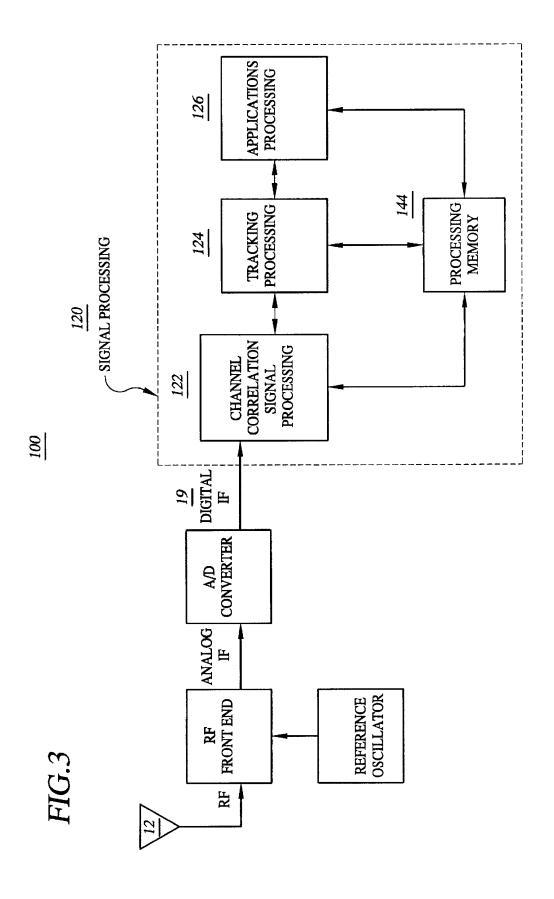

FIG. 3 is a block diagram describing the shared memory architecture of the invention.

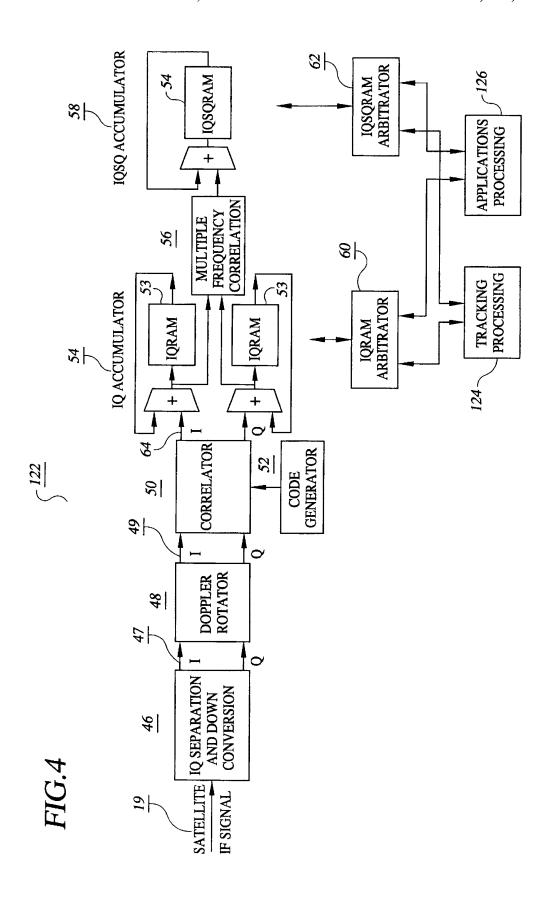

FIG. 4 is a block diagram describing the channel correlator signal processing.

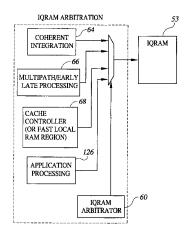

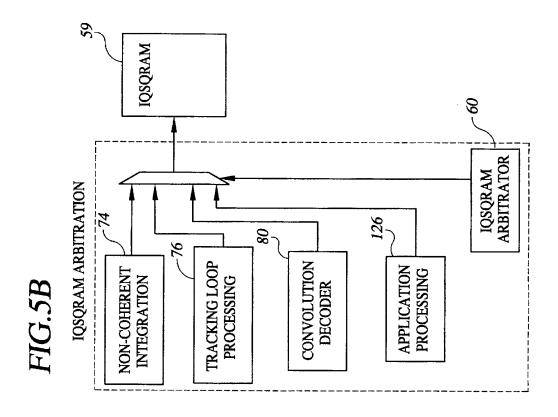

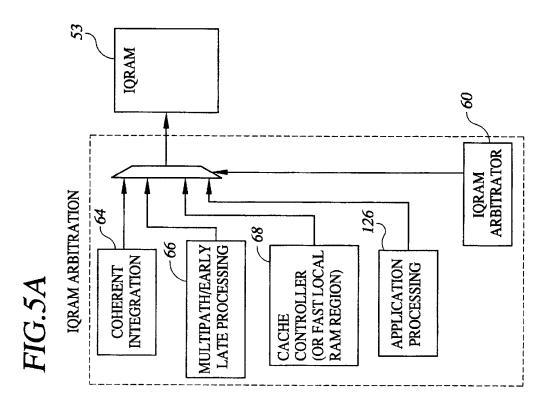

FIGS. 5A and 5B are block diagrams describing IQRAM and IQSQRAM arbitration in channel correlator signal processing.

FIG. 6 is a block diagram describing a memory map for IQRAM for the channel correlator signal processing.

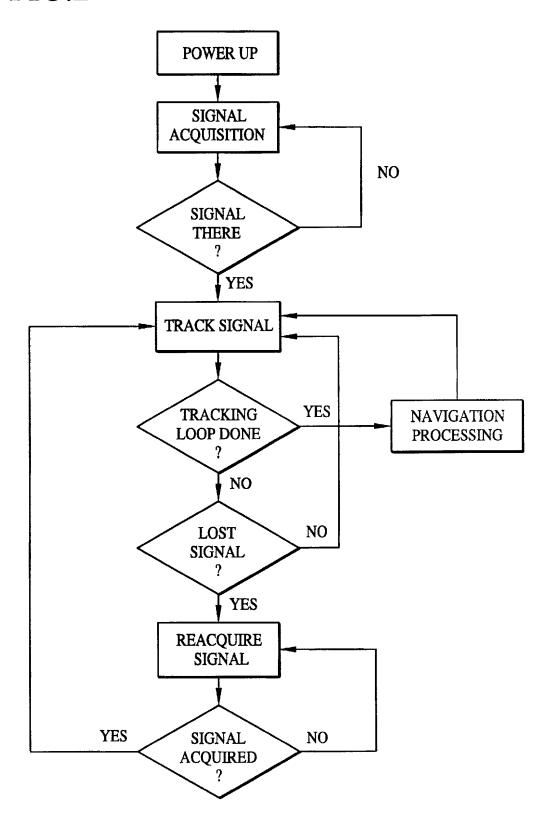

FIG. 7 is a block diagram describing a memory map for IQSQRAM in acquisition for the channel correlator signal processing.

FIG. 8 is a block diagram describing a memory map for IQSQRAM in tracking/reacquisition mode.

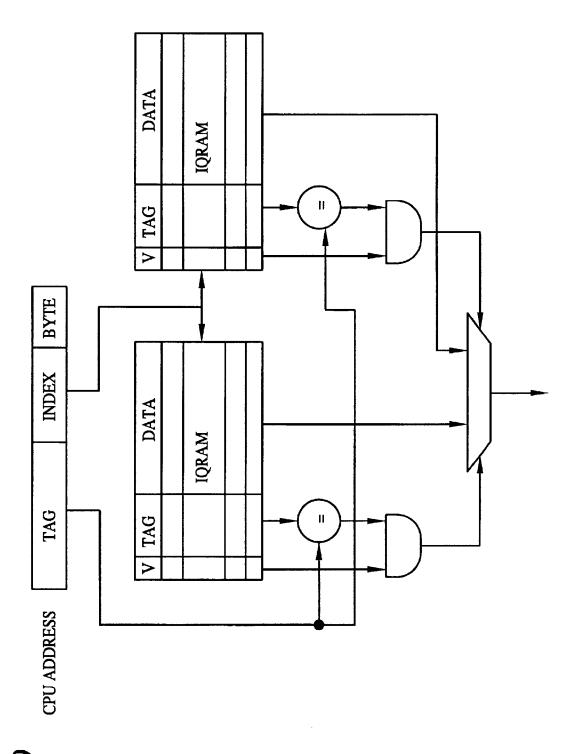

FIG. 9 is a block diagram describing an example of a two way set associative cache memory map for both tracking and navigation processing.

# DETAILED DESCRIPTION OF PREFERRED EMBODIMENT(S)

FIG. 3 shows a shared memory architecture for a GPS receiver 100, wherein a signal processing memory 144 is

### US 6,526,322 B1

3

shared among different signal processing functional units, such as a correlator signal processing unit 122, tracking processing unit 124 and applications processing unit 126. FIG. 4 shows a more detailed functional block diagram of processing memory 144 comprising an IQRAM 53 and an IQSQRAM 59. FIG. 4 further illustrates shared memory architecture in operation, as an illustration, such as during operations of channel correlator signal processing unit 122.

In operation, an IQ separator and down converter 46 samples a satellite IF signal 19 and separates signal 19 into 10 navigation processing is stored in the range from 0×100 to a pair of I and Q signals 47. I and Q signal pair 47 is down converted to a baseband frequency before being provided to a Doppler rotator 48, which provides Doppler rotation of I and Q signal pair 47. Both carrier phase and carrier frequency are programmed in the Doppler rotator 48 by a tracking processing CPU of tracking processing unit 124 of FIG. 3. As shown in FIG. 4, correlator 50 receives the Doppler rotated I and Q signal pair 49 and correlates signal pair 49 with a replica I and Q code produced by a code generator 52. An IQ accumulator 54 receives both I and Q 20 processing, wireless networking protocol processing, and samples 64 from correlator 50 and accumulates the samples over a coherent integration period. The accumulated results are stored separately in an IQRAM 53. The multiple frequency bin correlator 56 then receives I and Q data provided from IQ accumulator 54 and performs an accumulation at IQSQ accumulator 58 on the results of the square root of the sum of I-squared plus Q-squared for a period of time specified as non-coherent integration. The accumulation results are then stored in an IQSQRAM memory 59 of processing memory 144.

FIGS. 5A and 5B further illustrate a more detailed block diagram of an IORAM arbitration (FIG. 5A) and an IQSQRAM arbitration (FIG. 5B) provided to arbitrate use of IQRAM 53 and IQSQRAM 59. FIGS. 5A-5B illustrate the IQRAM and IQSQRAM arbitrator 60 and 62 that control 35 parameters and data. access to shared memory IQRAM 53 and IQSQRAM 59, i.e., such as arbitrating memory use between channel correlator signal processing unit 122 and the other functions seeking access to memory 144. For the IQRAM arbitrator **60**, the multiple memory access sources comprise the coher-40 ent integration of I and Q data from the output of coherent integration function 64 of correlator signal processing unit 122, the multipath/early-late processing 66 (i.e., for sampling data used for multipath mitigation by the tracking 68 (i.e., used to speed, up memory accesses for all the signal processing, including tracking processing and navigation processing), and any application processing 126. In this example, during tracking, the IQRAM arbitrator 60 arbitrates the multiple sources seeking access to IQRAM 53. The IQSQRAM arbitrator 62 shown in FIG. 5B includes controlling access from the non-coherent integration of I and Q signals 74, access to parameters stored for the tracking loops 76, multiple frequency bin correlation 56 (FIG. 4), the convolution decoder 80 (used for a special differential GPS 55 function), and any application processing functions 126. The arbitrator, such as the IQSQRAM arbitrator 62, arbitrates the multiple sources seeking access to the IQSQRAM 59.

FIG. 6 shows an example of the memory map 653 of the IQRAM 53 during our tracking operation example. There 60 are three different address ranges for three types of memory sources: the coherent integration of I and Q data from the correlator outputs (multiple samples in acquisition mode, single sample in track/re-acquisition mode), the multipath/ early-late sample data, and the cache tag/data. For this 65 above teachings, and it is thus intended that the scope of example, in satellite acquisition mode the whole address space of 0×000 though 0×1f7 is used to store the multiple

sample (in this case four) coherent integrations needed to search multiple frequency bins simultaneously. In track, or reacquisition modes, however, only a single sample needs to be collected instead of four. Thus, in track/reacquisition modes, the coherent integration I and Q data is stored only in the address range from  $0\times000$  to  $0\times077$ . This frees up the remaining space to be used for other functions. The multipath/early-late sampling data is stored in the address rage from 0×080 to 0×0ff. The cache tag/data for tracking or 0×1ff. FIG. 9 shows a structure for a 2 way set associative cache implementation of processing memory 144. The cache can be used as the instruction and data cache for the tracking and navigation processing functions to speed them up. The memory region used as cache can alternatively be used as fast local RAM for data storage by the tracking processor or applications processor. Thus, same areas of the address map are shared by multiple functions, including other non-GPS applications, such as navigation processing, GPS location other application processing that would be desirable to

FIG. 7 and FIG. 8 show the memory maps 759 and 859 for IQSQRAM 59 for other GPS functions, such as acqui-25 sition (or re-acquisition). The memory requirements once again are different for acquisition mode and track/ reacquisition modes. In acquisition mode, 1920 words in address range of 0×000 to 0×77f are used to store noncoherent accumulations. In track/reacquisition modes, how-30 ever only 240 words stored in address range 0×000 to 0×0ef are needed to store the noncoherent accumulations. This frees up the remaining space for other functions. In this example the other functions include convolutional decoder parameters and data, and expanded tracking processor

incorporate into GPS receiver 100.

FIGS. 7–8 illustrate sample memory mapping for memory IQSQRAM 59 during different modes. The memory mapping of IQRAM 53 and IQSQRAM 59 of processing memory 144 as illustrated in FIGS. 6-8 is a sample implementation. It is understood that this shared memory mapping in GPS receiver 100 can be extended to process other applications performed by the GPS receiver, such as navigation processing, GPS location processing, processing wireless networking protocols, to just name a few. It should processor), the cache tag and data from the cache controller 45 be understood that the shared memory architecture, such as illustrated with reference to FIGS. 3–9 can be applied to other GPS receiver applications contemplated as being within a GPS receiver. The shared memory architecture within the GPS receiver provides the memory necessary for signal processing operations, such as the massively parallel processing, while conserving memory cost by re-using that same memory for other GPS and non-GPS applications. The shared memory architecture for a GPS receiver provided in accordance with the principles of this invention thereby minimize the costly memory requirement often required of extremely fast signal acquisition of a GPS receiver.

Foregoing described embodiments of the invention are provided as illustrations and descriptions. They are not intended to limit the invention to precise form described. In particular, Applicant(s) contemplate that functional implementation of invention described herein may be implemented equivalently in hardware, software, firmware, and/or other available functional components or building blocks. Other variations and embodiments are possible in light of invention not be limited by this Detailed Description, but rather by Claims following.

### US 6,526,322 B1

What is claimed is:

1. A shared memory architecture for a receiver system, comprising a memory space shared commonly by two or more receiver functions comprising correlator signal processing, tracking processing and application processing

5

to minimize the memory space, wherein the commonly shared memory space functions as a coherent and a noncoherent integration memory for the correlation processing during signal correlation mode while the commonly shared memory space is also used for one or more other receiver 10 processing functions during one or more other receiver operation modes.

- 2. The shared memory architecture of claim 1, wherein the commonly shared memory space comprises a first memory section used as the system memory for a fast local memory 15 or system cache during tracking or application processing.

- 3. The shared memory architecture of claim 1, wherein the application processing comprises navigation processing.

- 4. The shared memory architecture of claim 1, wherein the application processing comprises GPS location processing. 20 application processing comprises GPS location processing.

- 5. The shared memory architecture of claim 1, wherein the application processing comprises wireless networking protocol processing.

- 6. A shared memory architecture for a receiver system comprising a memory space shared commonly by two or

6

more receiver functions comprising correlator signal processing, tracking processing and application processing to minimize the memory space, wherein the commonly shared memory space comprises a first memory section and a second memory section, wherein the first memory section functions as a coherent and the second memory section as a noncoherent integration memory for a correlation processing during signal correlation mode while the shared memory space is also used for one or more other receiver processing functions during one or more other receiver operation modes.

- 7. The shared memory architecture of claim 6, wherein the commonly shared memory space comprises a first memory section used as the system memory for a fast local memory or system cache during tracking or application processing.

- 8. The shared memory architecture of claim 6, wherein the application processing comprises navigation processing.

- 9. The shared memory architecture of claim 6, wherein the

- 10. The shared memory architecture of claim 6, wherein the application processing comprises wireless networking protocol processing.

# **EXHIBIT B**

US006775319B2

# (12) United States Patent

King et al.

(10) Patent No.: US 6,775,319 B2

(45) **Date of Patent:** \*Aug. 10, 2004

### (54) SPREAD SPECTRUM RECEIVER ARCHITECTURES AND METHODS THEREFOR

(75) Inventors: Thomas Michael King, Tempe, AZ

(US); Denise C. Riemer, Gurnee, IL

(US); Robert B. Harbour, Gilbert, AZ

(US); Andrew P. Hoover, Austin, TX

(US)

(73) Assignee: Motorola, Inc., Schaumburg, IL (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 181 days.

This patent is subject to a terminal disclaimer.

(21) Appl. No.: 09/931,121

(22) Filed: Aug. 16, 2001

(65) Prior Publication Data

US 2003/0081660 A1 May 1, 2003

(51) Int. Cl.<sup>7</sup> ...... H04B 1/69

275/120 150

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 4,114,155 | A | 9/1978 | Raab          |

|-----------|---|--------|---------------|

| 4,164,036 | A | 8/1979 | Wax           |

| 4,291,409 | A | 9/1981 | Weinberg      |

| 4,426,712 | A | 1/1984 | Gorski-Popiel |

|           |   |        | -             |

| 4,870,422 A | 9/1989   | Counselman        |

|-------------|----------|-------------------|

| 5,043,736 A | 8/1991   | Darnell           |

| 5,194,871 A | 3/1993   | Counselman        |

| 5,343,209 A | 8/1994   | Sennott           |

| 5,365,450 A | 11/1994  | Schuchman         |

| 5,384,574 A | 1/1995   | Counselman        |

| 5,420,593 A | 5/1995   | Niles             |

| 5,506,861 A | * 4/1996 | Bottomley 375/147 |

|             |          |                   |

(List continued on next page.)

### OTHER PUBLICATIONS

Lawrence L. Wells, "Real-Time Missile Tracking with GPS", 7 pages.

(List continued on next page.)

Primary Examiner—Temesghen Ghebretinsae (74) Attorney, Agent, or Firm—Roland K. Bowler, II

### (57) ABSTRACT

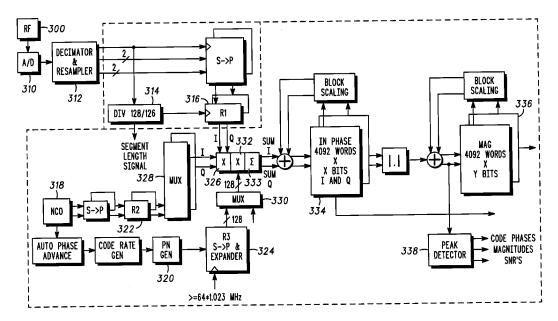

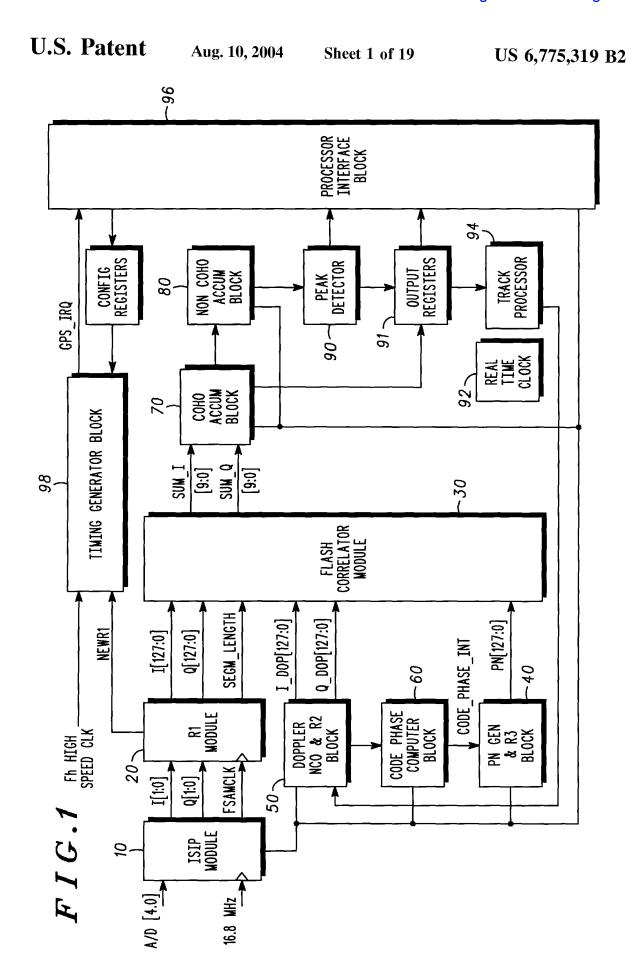

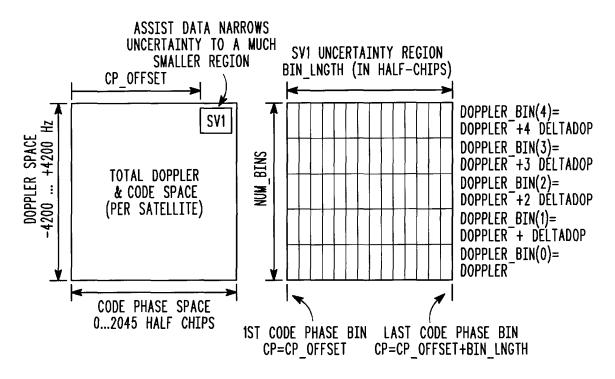

Methods and architectures for code phase searching spread spectrum signals having a repeating sequence of bits. The signals are searched virtually in parallel by segmenting with a divider (314) received signals by sequentially, partially correlating signal segments with a corresponding replica signal segments for a predetermined number of phase delays during a time interval not greater than that required to form the next signal segment. Multiplexors (322) and (330) provide Doppler and replica signal segments data from Doppler signal and replica signal generators (318) and (320) to corresponding multipliers (326) and (332), respectively, for multiplication with corresponding signal segments in a segment register (316). The partial correlation results for each phase delay and at each Doppler frequency are stored in corresponding memory locations in a coherent accumulation RAM (334). The signals may be searched over one or more phase delays and at one or more Doppler frequencies.

### 50 Claims, 19 Drawing Sheets

### US 6,775,319 B2

Page 2

### U.S. PATENT DOCUMENTS

| 5,600,670 A 2/1997    | Turney              |

|-----------------------|---------------------|

| 5,663,734 A 9/1997    | Krasner             |

| 5,663,735 A 9/1997    | Eshenbach           |

| 5,757,859 A 5/1998    | Retzer et al.       |

| 5,841,396 A 11/1998   | Krasner             |

| 5,893,044 A 4/1999    | King et al.         |

| 5,901,171 A * 5/1999  | Kohli et al 375/130 |

| 5,917,444 A 6/1999    | Loomis              |

| 5,945,944 A 8/1999    | Krasner             |

| 5,960,048 A * 9/1999  | Haartsen 375/366    |

| 5,982,324 A 11/1999   | Watters             |

| 5,982,811 A 11/1999   | Harrison et al.     |

| 6,002,363 A 12/1999   | Krasner             |

| 6,009,118 A 12/1999   | Tiemann et al.      |

| 6,041,222 A 3/2000    | Horton              |

| 6,061,018 A 5/2000    | Sheynblat           |

| 6,064,336 A 5/2000    | Krasner             |

| 6,088,348 A 7/2000    | Bell                |

| 6,097,974 A 8/2000    | Camp                |

| 6,107,960 A 8/2000    | Krasner             |

| 6,111,540 A 8/2000    | Krasner             |

| 6,121,923 A 9/2000    | King                |

| 6,122,506 A 9/2000    | Lau                 |

| 6,133,871 A 10/2000   | Krasner             |

| 6,133,873 A 10/2000   | Krasner             |

| 6,133,874 A 10/2000   | Krasner             |

| 6,181,911 B1 1/2001   | Sih et al.          |

| 6,191,731 B1 2/2001   | McBurney et al.     |

| 6,208,290 B1 3/2001   | Krasner             |

| 6,208,291 B1 3/2001   | Krasner             |

| 6,208,292 B1 3/2001   | Sih                 |

| 6,236,354 B1 5/2001   | Krasner             |

| 6,289,041 B1 9/2001   | Krasner             |

| 6,389,291 B1 5/2002   | Pande et al.        |

| 6,421,002 B2 7/2002   | Krasner             |

| 6,427,120 B1 7/2002   | Garin et al.        |

| 6,429,809 B1 8/2002   | Vayanos et al.      |

| 6,532,251 B1 * 3/2003 | King et al 375/142  |

| 6,580,746 B2 6/2003   | Challa et al.       |

### OTHER PUBLICATIONS

E.D. Holm and E.E. Westerfield, "A GPS Fast Acquisition Receiver", IEEE 1983 National Telesystems Conference, Feb. 1983.

Robert P. Denaro, Navstar GPS Test Results and Eric J. Hoffman, et al.; GPSPAC: A Spaceborne GPS Navigation Set; IEEE Plans 1978 Position Location and Navigation Symposium; Nov. 6–9, 1978; which includes the title page, Table of Contents, pp. 1–6 and pp. 13–20.

M. J. Bordel, et al., Texas Instruments Phase I GPS User Equipment; The Institute of Navigation, Global Positioning System; vol. 1, pp. 87–102.

Larry L. Horowitz, Analysis Of A Single-Bit Digital Receiver For Carrier And Code Tracking; The Johns Hopkins University—Applied Physics Laboratory; Jul. 1976, Copy No. 59, pp. 5–138.

B. G. Glazer, GPS Receiver Operation; Navigation Journal of the Institute of Navigation; vol. 25, No. 2, Spring 1978; pp. 173–178.

Charles C. Counselman III et al., Miniature Interferometer Terminals For Earth Surveying; Massachusetts Institute of Technology; pp. 139–163.

Charles C. Counselman III et al., Miniature Interferometer Terminals For Earth Surveying; Massachusetts Institute of Technology; pp. 65–85.

Charles C. Counselman III et al., Miniature Interferometer Terminals For Earth Surveying: Ambiguity and Multipath with Global Positioning System; IEEE Transactions on Geoscience and Remote Sensing; vol. GE–19, No. 4, Oct. 1981; pp. 244–252.

Charles C. Counselman III et al., The Macrometer: A Compact Radio Interferometry Terminal For Geodesy With GPS; Macrometrics, Inc.; pp. 1165–1172.

T. Thompson, Performance Of The Satrack/Global Positioning System Trident I Missile Tracking System; The Johns Hopkins University, Applied Physics Laboratory; 1980 IEEE; pp. 455–449.

Mikko Kokkonen, et al., A New Bit Synchronization Method for a GPS Receiver; 2002 IEEE; pp. 85–90.

Charles C. Counselman III et al., Accuracy of Baseline Determinations By Mites Assessed By Comparison With Tape, Theodolite and Geodimeter Measurements; EOS; vol. 62, No. 17; Apr. 28, 1981; p. 260.

<sup>\*</sup> cited by examiner

U.S. Patent

Aug. 10, 2004

Sheet 2 of 19

US 6,775,319 B2

FIG.2

| MODE | NUMBER OF SATELLITES SEARCHED               | NUMBER OF<br>DOPPLER BINS                          | CODE PHASE SEARCH<br>SPACE PER DOPPLER BIN       |

|------|---------------------------------------------|----------------------------------------------------|--------------------------------------------------|

| 1    | 2                                           | 1                                                  | 2046                                             |

| 2    | 1                                           | 2                                                  | 2046                                             |

| 3    | 2                                           | 4                                                  | 511                                              |

| 4    | 2                                           | 8                                                  | 255                                              |

| 5    | 1                                           | 32                                                 | 127                                              |

| 6    | 16                                          | 1                                                  | 255                                              |

|      |                                             |                                                    |                                                  |

| Х    | 1 SATELLITE<br>3 SATELLITES<br>7 SATELLITES | 5 DOPPLER BINS<br>3 DOPPLER BINS<br>4 DOPPLER BINS | 73 HALF-CHIPS<br>143 HALF-CHIPS<br>87 HALF-CHIPS |

FIG.3