# Case 3:05-cv-01958-B-BLM Document 1 Filed 10/14/05 Page 1 of 55 USDC SCAN INDEX SHEET

APB 10/17/05 11:03

3:05-CV-01958 QUALCOMM INC V. BROADCOM CORPORATION

\*1\*

\*CMP.\*

Case 3:05-cv-01958-B-BLM Document 1 Filed 10/14/05 Page 2 of 55

David E. Kleinfeld (Bar No. 110734) 1 C3 CCT 14 PH 4: 012 Barry J. Tucker (Bar No. 164163 HELLER EHRMAN LLP 2 4350 La Jolla Village Drive, 7th Floor San Diego, CA 92122 3 Telephone: (585) 450-8400 4 Facsimile: (585) 450-8499 5 Robert T. Haslam (Bar No. 71134) Nitin Subhedar (Bar No. 171802) HELLER EHRMAN LLP 6 275 Middlefield Road Menlo Park, CA 94025 7 Telephone: (650) 324-7000 8 Facsimile: (650) 324-0638 9 James R. Batchelder (Bar No. 136347) DAY CASEBEER MADRID & BATCHELDER LLP 20300 Stevens Creek Blvd., Suite 400 10 Cupertino, CA 95014 Telephone: (408) 873-0110 11 Facsimile: (408) 873-0220 12 Louis M. Lupin (Bar No. 120846) Alexander H. Rogers (Bar No. 131879) 13 Roger Martin (Bar No. 195003) **QUALCOMM INCORPORATED** 14 5775 Morehouse Drive San Diego, CA 92121 15 (858) 658-1121 16 Attorneys for Plaintiff 17 QUALCOMM INCORPORATED 18 UNITED STATES DISTRICT COURT 19 SOUTHERN DISTRICT OF CALIFORNIA 20 (NL\$ CASE NO. 115 CV 1958 1EG QUALCOMM INCORPORATED, 21 Plaintiff, 22 COMPLAINT FOR PATENT INFRINGEMENT 23 ٧. DEMAND FOR JURY TRIAL **BROADCOM CORPORATION,** 24 25 Defendant. 26 27 28

COMPLAINT FOR PATENT INFRINGEMENT DEMAND FOR JURY TRIAL

8

13

11

14

16

15

17

19

18

20 21

22 23

24 25

26 27

28

Plaintiff QUALCOMM Incorporated ("QUALCOMM") for its complaint herein states:

#### **PARTIES**

- Plaintiff QUALCOMM is a corporation organized and existing under the laws of the 1. state of Delaware, with its principal place of business in San Diego, California.

- Defendant Broadcom Corporation ("Broadcom") is a corporation organized and 2. existing under the laws of the state of California, with its principal place of business in Irvine, California.

- 3. OUALCOMM is informed and believes and thereon alleges that Broadcom is doing business in California and in this district.

#### JURISDICTION AND VENUE

- 4. This is an action for patent infringement. The claims arise under the patent laws of the United States, Title 35 U.S.C. §§ 1 et seq. This Court has subject matter jurisdiction over these claims pursuant to 28 U.S.C. §§ 1331 and 1338(a).

- Venue is proper in this district under 28 U.S.C. §§ 1391(b) and (c), and 1400(b), as 5. Broadcom resides and/or conducts substantial business in this district and has committed, and is continuing to commit, acts of infringement in this district.

#### **GENERAL ALLEGATIONS**

6. This action arises out of Broadcom's infringement of two (2) patents assigned to QUALCOMM.

#### **QUALCOMM's Patents**

- 7. On September 17, 1995, United States Patent No. 5,452,104 (the "'104 Patent"), entitled "Adaptive Block Size Image Compression Method and System," was duly and legally issued to QUALCOMM as assignee of the inventor, Chong U. Lee. A true and correct copy of the '104 Patent is attached hereto as Exhibit 1.

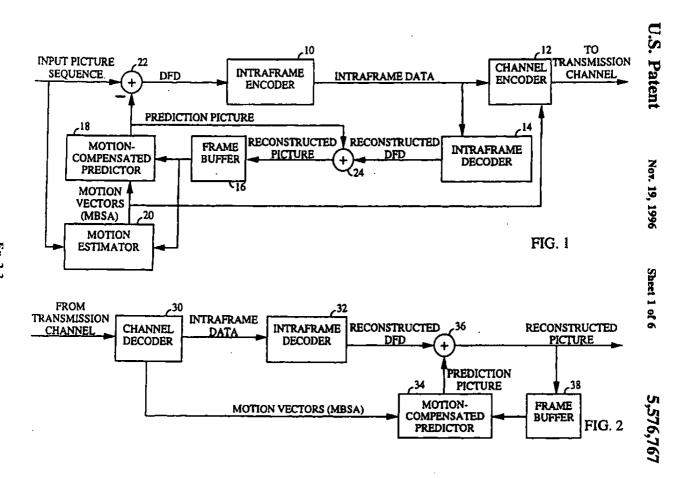

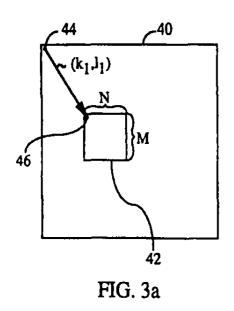

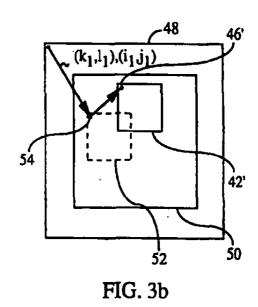

- 8. On November, 19, 1996. United States Patent No. 5,576,767 (the "'767 Patent"), entitled "Interframe Video Encoding and Decoding System," was duly and legally issued to QUALCOMM as assignee of the inventors, Chong U. Lee and Donald Pian. A true and correct copy of the '767 Patent is attached hereto as Exhibit 2.

- 9. The patents described in paragraphs 7 through 8 above, copies of which are attached hereto as Exhibits I through 2, are referred to collectively herein as the "patents-in-suit." The patents-in-suit relate generally to the processing of digital video signals.

- 10. On information and belief, Broadcom manufactures, sells and offers for sale in the United States products that comply with the H.264 standards and technical specifications adopted by the International Telecommunication Union ("ITU-T"), which standards are also known as ISO/IEC MPEG-4 Part 10, and/or manufactures, sells and offers for sale in the United States products intended to be used with or incorporated into products or systems that comply with said standards.

- 11. QUALCOMM is informed and believes and thereon alleges that Broadcom has been and is infringing, literally and/or under the doctrine of equivalents, one or more claims of each of the patents-in-suit directly and/or indirectly pursuant to 35 U.S.C. § 271(a), (b), (c) and/or (f).

# FIRST CAUSE OF ACTION Patent Infringement (35 U.S.C. §§ 271 et seq.)

- 12. QUALCOMM refers to and incorporates paragraphs 1 through 11 inclusive, as though fully set forth herein.

- 13. QUALCOMM is informed and believes and thereon alleges that Broadcom has been and is infringing, literally and/or under the doctrine of equivalents, one or more claims of each of the patents-in-suit directly and/or indirectly pursuant to 35 U.S.C. § 271(a), (b), (c) and/or (f).

- 14. Broadcom threatens to continue to do the acts complained of herein, and unless restrained and enjoined will continue to do so, all to QUALCOMM's irreparable damage.

- 15. By reason of Broadcom's acts alleged herein, QUALCOMM has suffered, is suffering, and unless such acts are enjoined by the Court will continue to suffer injury to its business and property rights, for which it is entitled to damages pursuant to 35 U.S.C. § 284 in an amount to be proved at trial.

- 16. By reason of Broadcom's acts alleged herein, QUALCOMM has suffered, is suffering, and unless such acts are enjoined by the Court will continue to suffer irreparable harm for which there is no adequate remedy at law, and for which QUALCOMM is entitled to permanent injunctive relief pursuant to 35 U.S.C. § 283.

suit;

COMPLAINT FOR PATENT INFRINGEMENT DEMAND FOR JURY TRIAL

#### **PRAYER**

WHEREFORE, QUALCOMM prays for judgment against Broadcom as follows:

- (a) For judgment that Broadcom has infringed, directly and/or indirectly, the patents-in-

- (b) For a preliminary and permanent injunction prohibiting Broadcom, and all persons or entities acting in concert with Broadcom, from infringing, directly and/or indirectly, the patents insuit;

- (c) For an award to QUALCOMM of all compensatory damages resulting from the direct and/or indirect infringement by Broadcom of the patents-in-suit, including pre-judgment and post-judgment interest;

- (d) For judgment and an order directing Broadcom to pay QUALCOMM's reasonable attorneys' fees, expenses and costs due to this being an "exceptional" case within the meaning of 35 U.S.C. § 285;

- (e) For judgment directing Broadcom to pay costs of suit; and

- (f) For an award to QUALCOMM of such other and further relief as the court deems equitable, just and proper.

Dated: October 14, 2005

DAY CASEBEER

MADRID & BATCHELDER LLP

James R. Batchelder

Attorneys for Plaintiff

QUALCOMM Incorporated

**DEMAND FOR JURY TRIAL**

Pursuant to Rule 38 of the Federal Rules of Civil Procedure, QUALCOMM demands a trial by jury on all issues triable of right by a jury.

Dated: October 14, 2005

**DAY CASEBEER** MADRID & BATCHELDER LLP

Attorneys for Plaintiff QUALCOMM Incorporated

COMPLAINT FOR PATENT INFRINGEMENT 28663\_1.doc DEMAND FOR JURY TRIAL

Case No. 05 cv 1392 B (BLM)

US005452104A

## United States Patent [19]

Lee

[11] Patent Number:

5,452,104

[45] Date of Patent:

Sep. 19, 1995

#### [54] ADAPTIVE BLOCK SIZE IMAGE COMPRESSION METHOD AND SYSTEM

[75] Inventor: Cheng U. Lee, San Diego, Calif.

[73] Assignee: Qualcomm Incorporated, San Diego,

Calif

[21] Appl. No.: 102,124

[22] Filed: Aug. 4, 1993

# Related U.S. Application Data

[63] Continuation of Ser. No. 4,213, Jan. 13, 1993, abandoned, which is a continuation of Ser. No. 710,216, Jun. 4, 1991, abandoned, which is a continuation-ispart of Ser. No. 487,012, Feb. 27, 1990, Pat. No. 3,021,891.

[51] Int. Cl.<sup>4</sup> H04N 1/415 [52] U.S. Cl. 358/433; 358/261.2; 348/404

[56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,774,574 | 9/1988  | Daly et al     | 358/133 |

|-----------|---------|----------------|---------|

| 4,776,030 | 10/1988 | Tzou           | 358/432 |

| 4,922,341 | 5/1990  | Strobach       | 358/136 |

| 4,924,309 | 5/1990  | Hartnack et al | 358/133 |

| 4,984,076 | 1/1991  | Watanabe et al | 358/133 |

| 5,021,891 | 6/1991  | Lœ             | 358/432 |

| 5.045,938 | 9/1991  | Sogiyama       | 358/133 |

| 5,073,820 | 12/1991 | Nakagawa et al | 358/209 |

| 5,073,821 | 12/1991 | Juri .         |         |

| 5,107,345 | 4/1992  | Lee            | 358/136 |

| 5,126,157 | 6/1992  | Watenabe et al | 358/432 |

| 5,142,380 | 1/1992  | Sakagami et al | 358/432 |

| 5,227,878 | 7/1993  | Puri et al     |         |

| 5,272,528 | 12/1993 | Juri et al     |         |

| 5,335,016 | 1/1994  | Nakagawa .     |         |

|           |         |                |         |

#### OTHER PUBLICATIONS

"Discrete Cosine Transform" by N. Ahmed et al., IEEE Transactions on Computers, Jan. 1974, pp. 90-93. "Adaptive Coding of Monochrome and Color Images" by Wen-Hsiung Chen et al., IEEE Transactions on Communications, vol. Com-25 No. 11, Nov. 1977 pp. 1285-1292.

"Interframe Cosine Transform Image Coding" by John

A. Roese et al., IEEE Transactions on Communications, vol. Com-25, No. 11, Nov. 1977, pp. 1329-1339. "Distributions of the Two-Dimensional DCT Coefficients for Images" by Randall C. Raininger et al., IEEE Transactions on Communications, vol. Com-31, No. 6, Jun. 1983, pp. 835-839.

"Scene Adaptive Coder": by Wen-Hsiung Chen et al., IEEE Transactions on Communications, vol. Com-32, No. 3, Mar. 1984, pp. 225-232.

"Hamming Coding of DCT-Compressed Images over Noisy Chamaels" by David R. Comstock et al., IEEE Transactions on Communications, vol. Com-32, No. 7, Jul. 1984, pp. 856-861.

"Variable Block-Size Transform Image Coder" by Its' Hak Dinstein et al., IEEE Transactions on Communications, vol. 38, No. 11, Nov. 1990, pp. 2073-2078.

"Quadtree-Structured Recursive Plane Decomposition Coding of Images" by Peter Strobach, IEEE Transactions on Signal Processing, vol. 39, No. 6, Jun. 1991.

Primary Examiner—Edward L. Coles, Sr.

Assistant Examiner—Kim Yen Vu

Attorney, Agent, or Firm—Russell B. Miller; Sean

English

#### [57] ABSTRACT

In an adaptive block size image compression method and system for compressing image data, a respective method and system for further compressing the image data for transmission. Each block and corresponding sub-blocks of pixel data is subjected to a discrete cosine transform (DCT) operation. Varying levels of subblocks of resulting corresponding transform coefficients are selected for construction into a composite transform coefficient block corresponding to each input block of pixel data. The selection of transform coefficient block size for the composite block is determined by a comparison process between transform block and sub-block coding efficiency. The composite block is variable length coded to further reduce bit count in the compressed data. A discrete quadtree transform (DQT) operation is in supplement of the adaptive block size block selection with coefficient replacement to optimize image data compression.

### 61 Claims, 10 Drawing Sheets

U.S. Patent

19, 1995

Sheet 1 of

U.S. Patent Sep. 19, 1995 Sheet 3 of 10 5,452,104

FIG. 3A

FIG. 3B

FIG. 4A

Ex. 1-4

5,452,104

Ex. 1-5

U.S. Patent

Ş

19, 1995

Sheet 5 of 10

Ex. 1-

U.S. Patent Scp. 19, 1995

Sheet 6 of 10

5,452,10

19, 1995

Short 7 of

ಕ

Sep. 19, 1995

U.S. Patent

SHEET O OF TO

5,452,10

Ex. 1-9

U.S. Patent Sep. 19, 1995 Sheet 9 of 10

5,452,104

**FIG. 10**

U.S. Patent Sep. 19, 1995

Sheet 10 of 10

5,452,104

FIG. 11

#### ADAPTIVE BLOCK SIZE IMAGE COMPRESSION METHOD AND SYSTEM

This application is a continuation of application Ser. 5 No. 08/004,213, filed Jan. 13, 1993, abandoned, which is a continuation of application Ser. No. 07/710,216, filed Jun. 4, 1991, now abandoned, which is a continuationin-part application of U.S. patent application Ser. No. issued Jun. 4, 1991, and as such relates to image process-

#### BACKGROUND OF THE INVENTION

#### I. Field of the Invention

More particularly, the present invention relates to a novel and improved method and system for data compression in an image signal compression scheme utilizing adaptively sized blocks and sub-blocks of encoded discrete cosine transform (DCT) coefficient data.

II. Description of the Related Art

In the field of transmission and reception of television signals, various improvements are being made to the NTSC (National Television Systems Committee) System. Developments in the field of television are com- 25 monly directed towards a high definition television (HDTV) System. In the development of HDTV, system developers have merely applied the Nyquist sampling theorem and low pass filtering design with varying degrees of success. Modulation in these systems 30 amounts to nothing more than a simple mapping of an analog quantity to a value of signal amplitude or fre-

It has most recently been recognized that it is possible to achieve further improvements in HDTV systems by 35 using digital techniques. Many of the proposed HDTV transmission formats share common factors. These systems all involve digital processing of the video signal, which necessitates analog-to-digital (A/D) conversion of the video signal. An analog transmission format is 40 then used thereby necessitating conversion of the digitally processed picture back to analog form for trans-

The receiver/processor must then reverse the process in order to provide image display. The received 45 analog signal is therefor digitized, stored, processed and reconstructed into a signal according to the interface format med between the receiver/processor and the HDTV display. Furthermore the signal is most likely is noted however that the proposed HDTV formats utilize digital transmission for transmission of control, audio and authorization signals.

Many of the conversion operations mentioned above, however, may be avoided using a digital transmission 55 format which transmits the processed picture, along with control, audio and authorization signals, using digital modulation techniques. The receiver may then be configured as a digital modern with digital outputs to the video processor function. Of course, the modem 60 requires an A/D function as part of operation, but this implementation may only require a 4-bit resolution device rather than the 8-bit resolution device required by analog format receivers.

Digital transmission is superior to analog transmission 65 in many ways. Digital transmissions provide efficient use of power which is particularly important to satellite transmission and in military applications. Digital trans-

missions also provide a robustness of the communications link to impairments such as multipath and jamming. Furthermore digital transmission facilitates ease in signal encryption, necessary for military and many broadcast applications.

Digital transmission formats have been avoided in previous HDTV system proposals primarily because of the incorrect belief that they inherently require excessive bandwidth. Therefore in order to realize the bene-487.012 filed Feb. 27, 1990, now U.S. Pat. No. 5,021,891 10 fits of digital transmission, it is necessary to substantially compress the HDTV signal, HDTV signal compression must therefor be achieved to a level that enables transmission at bandwidths comparable to that required by analog transmission formats. Such levels of signal compression coupled with digital transmission of the signal will enable a HDTV system to operate on less power with greater immunity to channel impairments.

It is therefore an object of the present invention to provide a novel and improved method and system for 20 enhancing the compression of HDTV signals so as to enable digital transmission at bandwidths comparable to that of analog transmissions of conventional TV signals.

#### SUMMARY OF THE INVENTION

The present invention is a novel and improved method and system for further compressing image data for transmission and for reconstruction of the image data upon reception. The image compression system includes a subsystem for generating from a block of input pixel data a corresponding composite block of discrete cosine transform (DCT) data optimized for encoding for a minimized transmission data rate. An additional subsystem is utilized to replace certain DCT coefficients with Discrete Quadtree Transform (DQT) coefficients in order to further reduce the data rate.

In the present invention a transform means receives an input block of pixel data and performs a discrete cosine transform (DCT) operation on the block of pixel data and on at least one predetermined level of constituent sub-blocks thereof. The transform means provides an output of corresponding block and sub-blocks of DC and AC DCT coefficient values.

An additional transform means also receives the input block of pixel data and performs a discrete quadtree transform (DQT) operation thereupon so as to generate a block of DQT coefficient values.

A block size assignment means receives, for the block and each sub-block, AC DCT coefficient values and a DQT value which in replacement of the DC DCT coefconverted back to analog form once more for display. It 50 ficient value. The block size assignment means determines, for the block and each corresponding group of constituent sub-blocks of DQT/DCT coefficient values, a bit count value corresponding to a number of bits required to respectively encode the block and each corresponding group of constituent sub-blocks of DQT/DCT coefficient values according to a predetermined coding format. The block assignment means further determines, from the bit count values, ones of the block and group of constituent sub-blocks of DQT/DCT coefficient values requiring a lesser number of bits to encode according to the predetermined coding format, and providing an output of a corresponding selection value.

A DCT selection means receives the selection value and the block and sub-blocks of DCT coefficient values and selects the block of DCT coefficient values or ones of the DCT coefficient values sub-blocks in accordance with the selection value. The DCT selection means

provides an output of a corresponding composite block of DCT coefficient values formed from the selected block or sub-blocks of DCT coefficient values. A DQT selection means also receives the selection value and the block of DQT coefficient values and selects ones of the 5 DQT coefficient values in accordance with the selection value. The each selected DQT coefficient values corresponds to a DC DCT coefficient values of the selected block or sub-block.

A DCT ordering means receives and orders the composite block of DCT coefficient values according to a

predetermined ordering format. The ordering means

provides an output of the ordered DCT coefficient

values to an encoder means that codes the ordered DCT

coefficient values according to a predetermined coding 15

format. The encoder means provides an output of the

coded ordered DCT coefficient values.

A DQT ordering means receives selected DQT coefficient and orders the selected DQT coefficients in a format such that each maintains corresponds with a 20 respective one of the DC DCT coefficients in the coded ordered coefficient values. The DQT ordering means provides an output of the ordered DQT coefficient values.

An assembler means receives the coded ordered 25 DCT coefficient values, the ordered DQT values and the selection value. The assembler means generates an coded image value by removing the DC coefficient values in the ordered coded DCT coefficient values while combining the selection value with the remaining 30 AC DCT coefficients in the ordered coded DCT coefficient values and the ordered DQT coefficient values. The coded image value is representative of the input block of pixel data and is of a reduced bit count with respect to a bit count of the input block of pixel data. 35 The assembler means provides an output of the coded image value for transmission.

The present invention also provides for a novel and improved method for reconstructing from each received coded image value a corresponding block pixel 40 of pixel data. The present invention further envisions a novel and improved method for compressing an image signal as represented by a block of pixel data and for reconstructing the image signal from the compressed image signal.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The features, objects, and advantages of the present invention will become more apparent from the detailed description set forth below when taken in conjunction 50 with the drawings in which like reference characters identify correspondingly throughout and wherein:

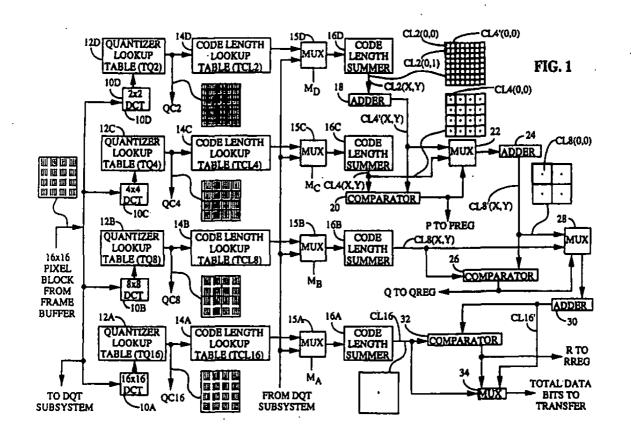

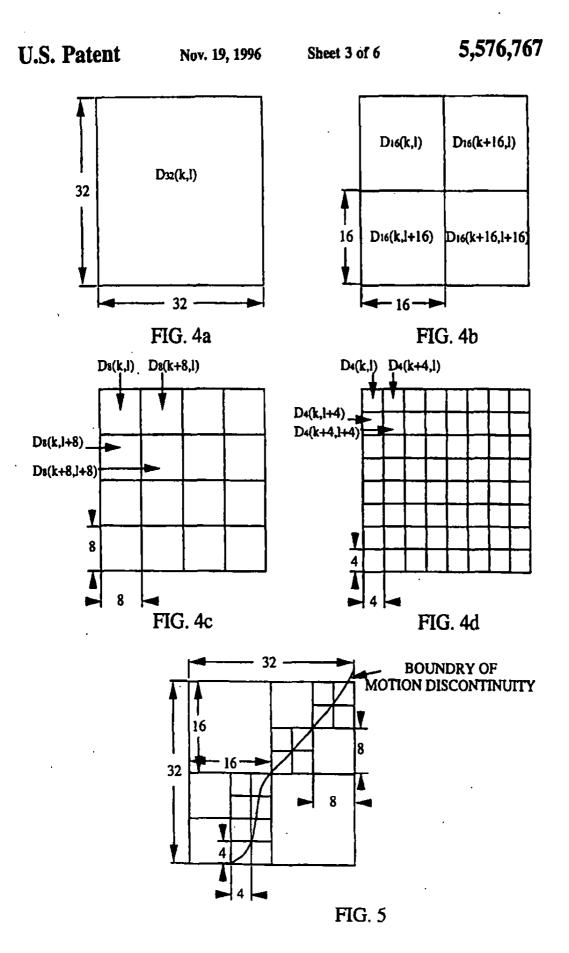

FIG. 1 is a block diagram illustrating the processing elements of the adaptive block size image compression system for providing DCT coefficient data and block 55 size determination:

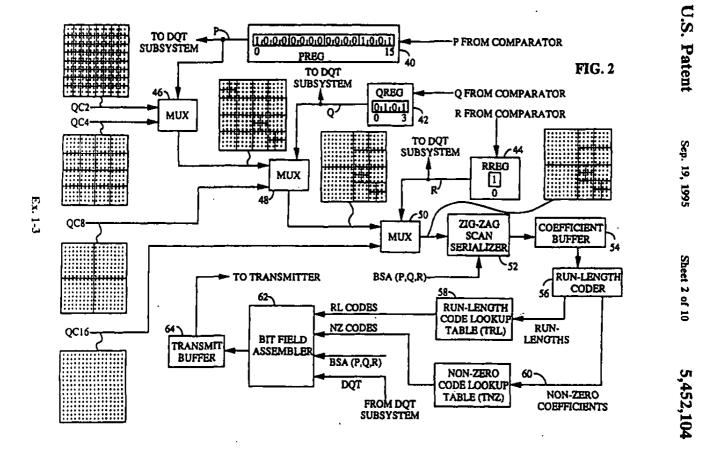

FIG. 2 is a block diagram illustrating the further processing elements for the adaptive block size image compression system for selecting block sizes of DCT coefficient data so as to generate a composite block of 60 DCT coefficient data and the encoding of the composite block for transmission;

FIGS. 3a and 3b respectively illustrate exemplarily register block size assignment data and the block selection tree corresponding thereto;

FIGS. 4s and 4b are graphs respectively illustrating in graphical form the selected block zig-zag scan serialization ordering sequence within the sub-blocks and

between sub-blocks for an exemplary composite block of DCT coefficient data whose block size selection was made according to the block size assignment data of FIG. 3a;

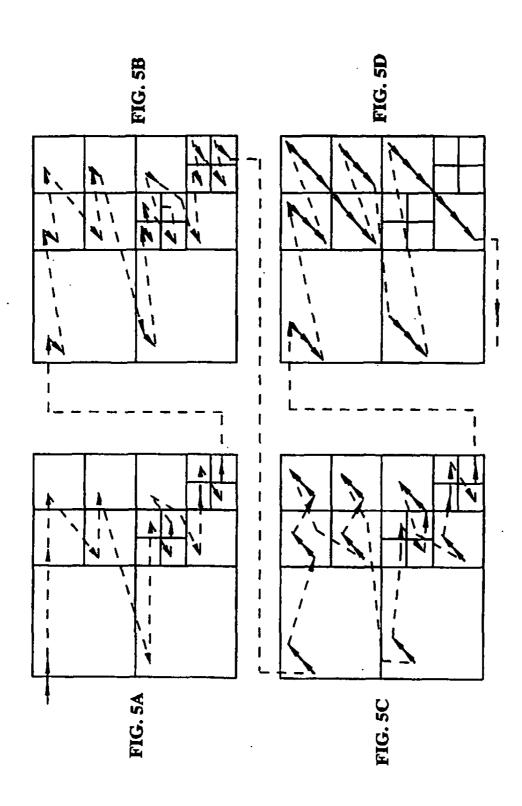

FIGS. 50-5d respectively illustrate in graphical form an alternate zig-zag scan serialization format;

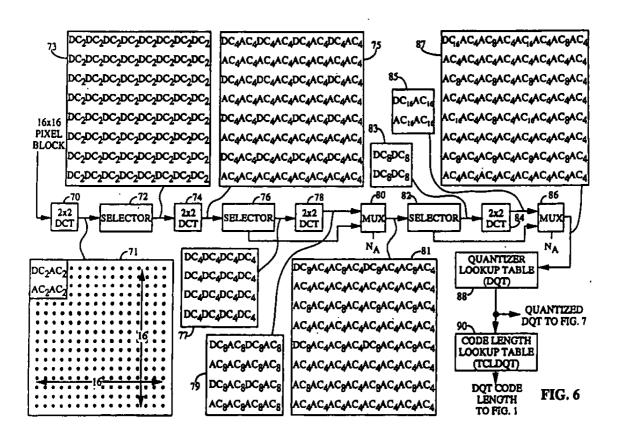

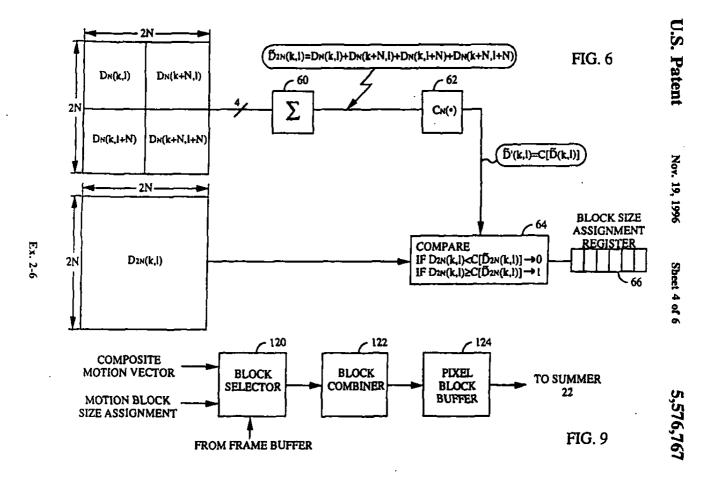

FIG. 6 is a block diagram illustrating the DQT coefficient processing elements of the DQT subsystem of the present invention used in accompaniment with the image compression system of FIGS. 1 and 2;

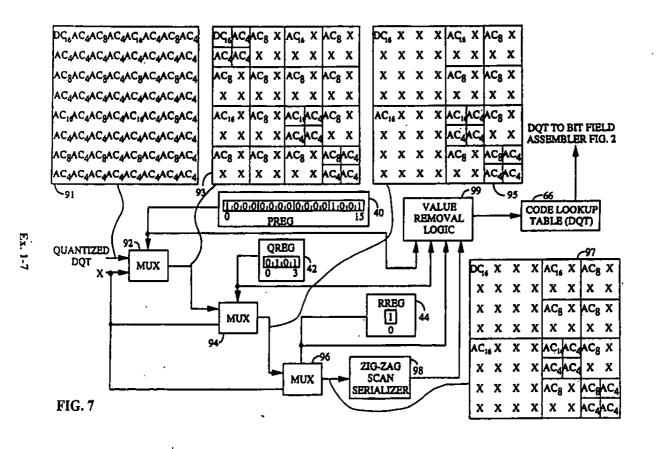

FIG. 7 is a block diagram further illustrating the DQT coefficient block replacement processing elements of the DQT subsystem of the present invention used in accompaniment with the image compression system of FIGS. 1, 2 and 6

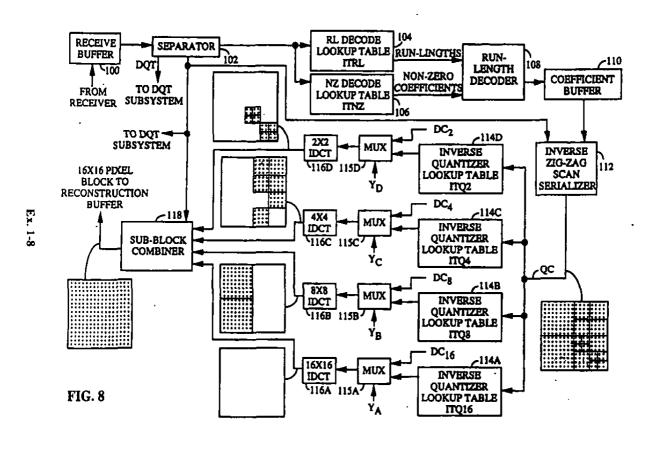

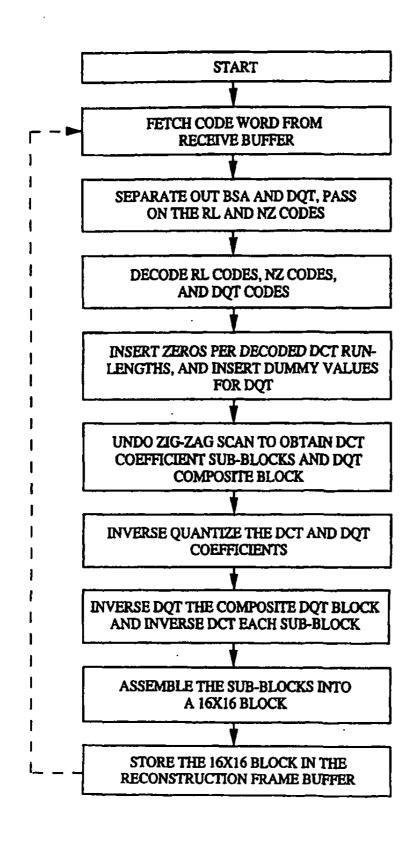

FIG. 8 is a block diagram illustrating a decoder for reconstructing an image from a received signal generated by the processing elements of FIGS. 1 and 2;

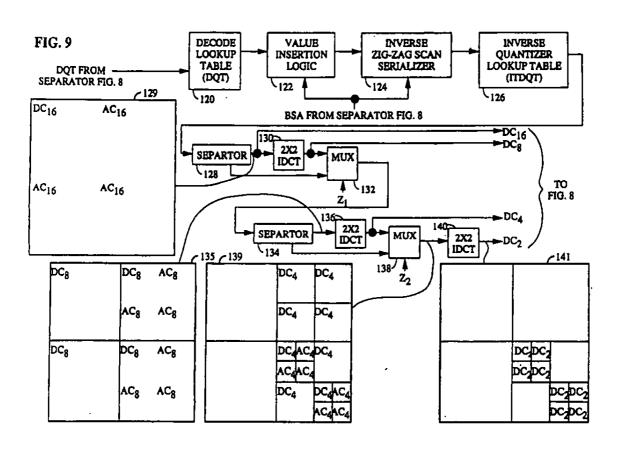

FIG. 9 is block diagram illustrating the DQT subsystem of the present invention used in accompaniment with the decoder of FIG. 7;

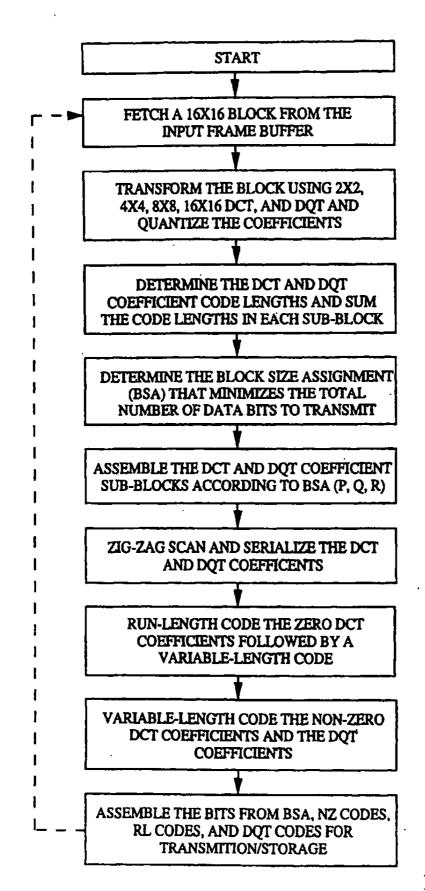

FIG. 10 is a flow chart illustrating the processing steps involved in compressing and coding image data as performed by the processing elements of FIGS. 1 and 2; and

FIG. 11 is a flow chart illustrating the processing steps involved in decoding and decompressing the compressed signal so as to generate pixel data.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

In order to facilitate digital transmission of HDTV signals and enjoy the benefits thereof, it is necessary to employ some form of signal compression. In order to achieve such high definition in the resulting image, it is also important that high quality of the image also be maintained. The discrete cosine transform (DCT) techniques have been shown to achieve a very high compression. One such article which illustrates the compression factor is that entitled "Scene Adaptive Coder" by Wen-Hsiung Chen et al., IEEE Transactions on Communications, Vol. Com-32, No. 3, March, 1984. However, the quality of reconstructed pictures is marginal even for video conferencing applications.

With respect to the DCT coding techniques, the image is composed of pixel data which is divided into an array of non-overlapping blocks, N×N in size. Strictly for black and white television images each pixel is represented by an 8-bit word whereas for color television each pixel may be represented by a word comprised of up to 24-bits. The blocks in which the image is divided up to is typically a 16×16 pixel block, i.e. N=16. A two-dimensional N×N DCT is performed in each block. Since DCT is a separable unitary transformation, a two-dimensional DCT is performed typically by two successive one-dimensional DCT operations which can result in computational savings. The one-dimensional DCT is defined by the following equation:

$$I(k) = \frac{2C(k)}{N} \prod_{n=0}^{N-1} I(n) \cos \frac{\pi(2n+1)k}{2N}$$

(1)

where

$$C(0) = \frac{1}{\sqrt{2}}$$

(2)

Ex. 1-13

5,452,104

5 -continued

C(k) = 1 for k = 1,2,3,...N - 1.

For television images, the pixel values are real so that 5 the computation does not involve complex arithmetic. Purthermore, pixel values are non-negative so that the DCT component X(0) is always positive and usually has the most energy. In fact, for typical images, most of the transform energy is concentrated around DC. This 10 energy compaction property makes the DCT such an attractive coding method.

It has been shown in the literature that the DCT approaches the performance of the optimum Karhunen-Loeve Transform (KLT), as evidenced by the article 15 entitled "Discrete Cosine Transform" by N. Ahmed et al., IERE Transactions on Computers, Japanary 1974, pages 90-93. Basically, the DCT coding performs a spatial redundancy reduction on each block by discarding frequency components that have little energy, and 20 by assigning variable numbers of bits to the remaining DCT coefficients depending upon the energy content. A number of techniques exist that quantize and allocate bits to minimize some error criterion such as MSE over mapped into a one-dimensional string by ordering from low frequency to high frequency. The mapping is done according to diagonal zig-zag mapping over the block of DCT coefficients. The locations of the zero (or discoding technique.

In order to optimally quantize the DCT coefficient. one needs to know the statistics of the transform coefficients. Optimum or sub-optimal quantizers can be designed based on the theoretical or measured statistics 35 that minimize the over-all quantization error. While there is not complete agreement on what the correct statistics are, various quantization schemes may be utilized, such as that disclosed in "Distribution of the Two-Dimensional DCT Coefficients for Images" by 40 Randall C. Reininger et al., IEEE Transactions on Communications, Vol. 31, No. 6, June 1983, Pages 835-839. However, even a simple linear quantizer has been uti-

lized which has provided good results.

Aside from deciding on a quantization scheme, there 45 are two other methods to consider in order to produce the desired bit rate. One method is to threshold the DCT coefficient so that the small values are discarded and set to zero. The other technique is to linearly scale (or normalize) the coefficients to reduce the dynamic 50 range of the coefficients after floating point to integer conversion for coding. Scaling is believed to be superior to thresholding in retaining both the subjective as well as objective signal to noise ratio quality. Therefore the main variable in the quantization process will be the 55 code the coefficient locations and Huffman code the coefficient scale factor which can be varied to obtain

the desired bit rate.

The quantized coefficients usually are coded by Hulfman codes designed from the theoretical statistics or from the measured histogram distribution. Most of the 60 coefficients are concentrated around the low values so that Huffman coding gives good results. It is believed that Huffman codes generated from a measured histogram performs very close to theoretical limits set by the entropy measure. The location of the zero coefficients 65 are coded by run-length codes. Because the coefficients are ordered from low to high frequencies, the runs tend to be long such that there is a small number of runs.

6

However, if the number of runs in terms of length were counted, the short runs dominate so that Huffman coding the run-lengths reduces the bit rate even more.

An important issue that concerns all low bit-rate compression schemes is the effect of channel bit error on the reconstruction quality. For DCT coding, the lower frequency coefficients are more vulnerable especially the DC term. The effect of the bit error rate (BER) on the reconstruction quality at various compression rates has been presented in the literature. Such issues are discussed in the article entitled "Intraframe Cosine Transfer Image Coding" by John A. Rosse et al., IEEE Transactions on Communications, Vol. Com-25, No. 11, November 1977, Pages 1329-1339. The effect of BER becomes noticeable around 10-3 and it becomes significant at 10-2. A BER of 10-5 for the transmission subsystem would be very conservative. If necessary, a scheme can be devised to provide additional protection for lower frequency coefficients, such as illustrated in the article "Hamming Coding of DCT-Compressed Images over Noisy Channels" by David R. Comstock et al., IERE Transactions on Communications, Vol. Com-32, No. 7, July 1984, Pages 856-861.

It has been observed that most natural images are the block. Typically the quantized DCT coefficients are 25 made up of blank or relatively slow varying areas, and busy areas such as object boundaries and high-contrast texture. Scene adaptive coding schemes take advantage of this factor by assigning more bits to the busy area and less bits to the blank area. For DCT coding this adaptacarded) coefficients are then coded by a run-length 30 tion can be made by measuring the busyness in each transform block and then adjusting the quantization and bit allocation from block to block. The article entitled "Adaptive Coding of Monochrome and Color images" by Wen-Haining Chen et al., IERR Transactions on Communications, Vol. Com-25, No. 11, November 1977, Pages 1285-1292, discloses a method where block energy is measured with each block classified into one of four classes. The bit allocation matrix is computed iteratively for each class by examining the variance of the transform samples. Each coefficient is scaled so the desired number of bits result after quantization. The overhead information that must be sent are the classification code, the normalization for each block, and four bit allocation matrices. Utilization of this method has produced acceptable results at I and 0.5 bits per pixel.

Further bit rate reduction was achieved by Chen et al in the previously mentioned article "Scene Adaptive Coder" where a channel buffer is utilized to adaptively scale and quantize the coefficients. When the buffer becomes more than half full, a feedback parameter normalizes and quantizes the coefficients coarsely to reduce the bits entering the buffer. The converse happens when the buffer becomes less than half full. Instead of transmitting the bit allocation matrices, they run-length coefficients as well as the run-lengths. Such an implomentation has shown good color image reconstructions at 0.4 bits per pixel. Although these results look very good when printed, the simulation of the system shows many deficiencies. When images are viewed under normal to moderate magnification smoothing and blocking effects are visible.

In the image compression method and system disclosed herein, intraframe coding (two-dimensional processing) is utilized over interframe coding (three-dimensional processing). One reason for the adoption of intraframe coding is the complexity of the receiver required to process interframe coding signals. Interframe coding

inherently require multiple frame buffers in addition to more complex processing circuits. While in commercialized systems there may only be a small number of transmitters which contain very complicated hardware, the receivers must be kept as simple as possible for mass 5 production purposes.

The second most important reason for using intraframe coding is that a situation, or program material, may exist that can make a three-dimensional coding scheme break down and perform poorly, or at least no better than the intraframe coding scheme. For example, 24 frame per second movies can easily fall into this category since the integration time, due to the mechanical abutter, is relatively short. This short integration time allows a higher degree of temporal aliasing than in TV cameras for rapid motion. The assumption of frame to frame correlation breaks down for rapid motion as it becomes jurky. Practical consideration of frame to frame registration error, which is already noticeable on home videos become worse at higher resolution.

An additional reason for using intraframe coding is that a three-dimensional coding scheme is more difficult to standardize when both 50 Hz and 60 Hz power line frequencies are involved. The use of an intraframe scheme, being a digital approach, can adapt to both 50 25 Hz and 60 Hz operation, or even to 24 frame per second movies by trading off frame rate versus spatial resolution without inducing problems of standards conversion.

Although the present invention is described primarily 30 with respect to black and white, the overhead for coding color information is surprisingly small, on the order of 10 to 15% of the bits needed for the huminance. Because of the low spatial sensitivity of the eye to color, most researchers have converted a color picture from 35 RGB space to YIQ space, sub-sample the I and Q components by a factor of four in horizontal and vertical direction. The resulting I and Q components are coded similarly as Y (luminance). This technique requires 6.25% overhead each for the I and Q components. In 40 practice, the coded Q component requires even less data than the I component. It is envisioned that no significant loss in color fidelity will result when utilizing this class of color coding techniques.

In the implementation of DCT coding techniques, the 45 blocking effect is the single most important impairment to image quality. However, it has been realized that the blocking effect is reduced when a smaller sized DCT is used. The blocking effect becomes virtually invisible when a 2×2 DCT is used.

However, when using the small-sized DCT, the bit per pixel performance suffers somewhat. However, a small-sized DCT helps the most around sharp edges that separate relatively blank areas. A sharp edge is equivalent to a step signal which has significant compo- 55 nents at all frequencies. When quantized, some of the low energy coefficients are truncated to zero. This quantization error spreads over the block. This effect is similar to a two-dimensional equivalent of the Gibbs phenomenon, i.e. the ringing present around a step pulse 60 signal when part of the high frequency components are removed in the reconstruction process. When adjacent blocks do not exhibit similar quantization error, the block with this form of error stands out and creates the blocking effect. Therefore by using smaller DCT block 65 picture. sizes the quantization error becomes confined to the area near the edge since the error cannot propagate outside the block. Thereby, by using the smaller DCT

8

block sizes in the busy areas, such as at edges, the error is confined to the area along the edge. Furthermore, the use of the small DCT block sizes is further enhanced with respect to subjective quality of the image due to the spatial masking phenomena in the eye that hides noise near busy areas.

The adaptive block size DCT technique implemented in the present invention may be simply described as a compare-and-replace scheme. A b 16×16 pixel data array or block of the image is coded as in the fixed block size DCT techniques, however, block and sub-block sizes of  $16 \times 16$ ,  $8 \times 8$ ,  $4 \times 4$  and  $2 \times 2$  are used. For each 4×4 block, the number of bits to code the block by using four  $2\times2$  sub-blocks inside the  $4\times4$  block is examined. If the sum of the four 2×2 sub-blocks is smaller than the bits needed to code it as a  $4\times4$  block, the  $4\times4$ block is replaced by four 2×2 sub-blocks. Next, each of the  $8 \times 8$  blocks are examined to determine if they can in turn be replaced by four 4×4 sub-blocks which were optimized in the previous stage. Similarly, the 16×16 block is examined to determine if it can be replaced by four 8×8 sub-blocks that were optimized in the previous stage. At each stage the optimum block/sub-block size is chosen so that the resulting block size assignment is optimized for the 16×16 block.

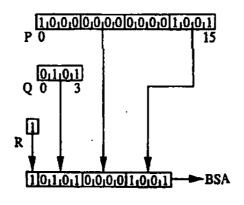

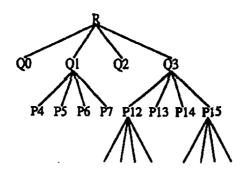

Since 8-bits are used to code the DC coefficients regardless of the block size, utilization of small blocks results in a larger bit count. For this reason, 2×2 blocks are used only when their use can lower the bit count. The resulting sub-block structure can be conveniently represented by an inverted quadtree (as opposed to a binary tree), where the root corresponding to the 16×16 block in each node has four possible branches corresponding to four sub-blocks. An example of a possible inverted quadtree structure is illustrated in FIG. 3b.

Each decision to replace a block with smaller subblocks requires one bit of information as overhead. This overhead ranges from one bit for a 16×16 block up to 21 bits (1+4+16) when 4×4 and 2×2 smb-blocks are used everywhere within in the 16×16 block. This overhead is also incorporated into the decision making process to ensure that the adaptive block size DCT scheme always uses the least number of bits to code each 16×16 block.

Although block sizes discussed herein as being N×N in size, it is envisioned that various block sizes may be used. For example an N×M block size may be utilized where both N and M are integers with M being either greater than or lesser than N. Another important aspect is that the block is divisible into at least one level of sub-blocks, such as N/i×N/, N/i×N/j, N/i×M/j, and etc. where i and j are integers. Furthermore, the exemplary block size as discussed herein is a 16×16 pixel block with corresponding block and sub-blocks of DCT coefficients. It is further envisioned that various other integer such as both even or odd integer values may be used, e.g. 9×9.

Due to the importance of these overhead bits for the quadtree, these bits need to be protected particularly well against channel errors. One can either provide an extra error correction coding for these important bits or provide and error recovery mechanism so that the effect of channel errors is confined to a small area of the picture.

The adaptive block size DCT compression scheme of the present invention can be classified as an intraframe coding technique, where each frame of the image se-

quence is encoded independently. Accordingly, a single frame still picture can be encoded just as easily without modification. The input image frame is divided into a number of 16×16 pixel data blocks with encoding performed for each block. The main distinction of the 5 compression scheme of the present invention resides in the fact that the 16×16 block is adaptively divided into sub-blocks with the resulting sub-blocks at different sizes also encoded using a DCT process. By properly choosing the block sizes based on the local image characteristics, much of the quantization error can be confined to small sub-blocks. Accordingly small sub-blocks naturally line up along the busy area of the image where the perceptual visibility of the noise is lower than in blank areas.

In review, a conventional or fixed block size DCT coding assigns a fixed number of bits to each block such that any quantization noise is confined and distributed within the block. When the severity or the characteristics of the noise between adjacent blocks are different, 20 the boundary between the blocks become visible with the effect commonly known as a blocking artifact. Scene adaptive DCT coding assigns a variable number of bits to each block thereby shifting the noise between fixed sized blocks. However, the block size is still large 25 enough, usually 16×16, such that some blocks contain both blank and busy parts of the image. Hence the blocking artifact is still visible along image detail such as lines and edges. Using smaller block sizes such as 8×8 or 4×4 can greatly reduce the blocking artifact, 30 however, at the expense of a higher data rate. As a result, the coding efficiency of DCT drops as the block size gets smaller.

In the embodiment is which the present invention is described an adaptive block size DCT trechnique is used 35 in which optimal block size is chosen such that smaller blocks are used only when they are needed. As a result, the blocking artifact is greatly reduced without increasing the data rate. Although a number of different methods can be devised that determine block size assignment, an exemplary illustration of an embodiment is provided which assigns block sizes such that the total number of bits produced for each block is minimized. Using the DQT transform of the present invention in combination with the adaptive block size technique a 45 further reduction in the data rate, on the order of 5% or greater, can be achieved.

FIGS. 1 and 2 illustrate an exemplary implementation of the adaptive block size DCT transform image signal compression scheme for converting N×N pixel data 50 spective code length values. The number of bits required for purposes of illustration N=16. FIG. 1 illustrates the implementation of the DCT transform and block size determination elements. FIG. 2 illustrates the DCT coefficient data block selection according to the block 55 code lengths for the DC are size determination along with composite DCT coefficient data block bit coding.

In FIG. 1, an image signal as represented by a 16×16 block of digitized pixel data is received from the frame buffer (not shown). The pixel data may be either 8 bit 60 black and white image data or 24 bit color image data. The 16×16 pixel block is input to a 16×16 two-dimensional discrete cosine transform (DCT) element 10a. The 16×16 pixel block is also input as four 8×8 pixel blocks to 8×8 DCT element 10b, as eight 4×4 pixel 65 blocks to 4×4 DCT element 10c, and as sixty-four 2×2 pixel blocks to 2×2 DCT element 10d. DCT elements 10a-10d may be constructed in integrated circuit form

as is well known in the art. The 16×16 pixel block is also input is also provided in parallel to a DQT subsystem as discussed later herein with reference to FIG. 9.

DCT elements 10a-10d perform two-dimensional DCT operations on each respectively sized input block of pixel data. For example, DCT element 10a performs a single 16×16 transform operation, DCT element 10b performs four 8×8 DCT operations, DCT element 10c performs sixteen 4×4 DCT operations, while DCT element 10d performs sixty-four 2×2 DCT operations. Transform coefficients are output from each DCT element 10a-10d to a respective quantizer look up table 12a-12d.

Quantizer lookup tables 12a-12d may be implemented in conventional read only memory (ROM) form with memory locations containing quantization values. The value of each transform coefficient is used to address a corresponding memory location to provide an output data signal indicative of a corresponding quantized transform coefficient value. The output of quantizer lookup table 12a, indicated by the reference signal QC16, is a 16×16block of quantized DCT coefficient values. The output of quantizer lookup table 12h, indicated by the reference signal QCS, is comprised of a data block of four \$X8sub-blocks of quantized DCT coefficient values. The output of quantizer lookup table 12c, indicated by the reference signal QCA, is comprised of a data block of sixteen 4×4 sub-blocks of quantized DCT coefficient values. And finally, the output of quantizer lookup table 12d, indicated by the reference signal QC2, is comprised of a data block of sixty-four 2×2 sub-blocks of quantized DCT coefficient. Although not illustrated, the DC (lowest frequency) coefficients of each transform may be optionally treated separately rather than through the corresponding quantizer lookup table.

The outputs of quantizer lookup tables 120-12d are respectively input to code length lookup tables 14a-14d. The quantized DCT coefficient values are each coded using variable length code, such as a Huffman code, in order to minimize the data rate. Code words and corresponding code lengths are found in the form of code length look up tables 14a-14d. Each of the quantized DCT coefficients QC2, QC4, QC8, and QC16 are used to look up in the code length tables the corresponding number of bits required to code each coefficient. Code length lookup tables 14a-14d may be implemented in read only memory form with the DCT coefficients addressing memory locations which contain respective code length values.

The number of bits required to code each block or sub-block is then determined by summing the code lengths in each block and sub-block. In the basic implementation of the adaptive block size coding scheme the code lengths for the DC and AC coefficients of each block and sub-block is used in determining the number of bits to code the respective block or sub-block. However in the case where the DQT subsystem is utilized, the value corresponding to the DC DCT coefficients output from code length lookup tables 14a-14d is replaced with a similar value from the DQT subsystem. Multiplexers 15a-15d are used to permit the DQT coefficient code length values output from the DQT subsystem to be provided to the respective code length summer 160-16d. Multiplexers 150-15d also permit the AC DCT coefficient code length values output from code length lookup tables 14a-14d to be provided to the respective code length summer 160~16d.

The 256 code length values from code length lookup table 14a, comprised of 1 DC coefficient code length values and 255 AC coefficient code length values, are provided to multiplexer 15a. A DQT coefficient code length value is also provided to multiplexer 15a from 5 the DQT subsystem. Multiplexer 15a is responsive to a control signal Ma so as to provide the DQT coefficient code length value from the DQT subsystem to code length summer 16s in place of the DC DCT coefficient code length value from code length lookup table 14a. 10 However, the 255 AC coefficient code length values are provided via multiplexer 15s to code length summer 16a. In code length summer 16a the number of bits required to code the 16×16block DQT/DCT coefficient block is determined by summing the code lengths 15 for the block. Therefore for the 16×16block, code length summer 16a sums the 255 AC coefficient code length values along with the 1 DQT coefficient code length value. The output from code length summer 16a is the signal CL16, a single value indicative of the num- 20 ber of bits required to code the 16×16 block of quantized DOT/DCT coefficients.

The 256 code length values from code length lookup table 14b, comprised of a total of 4 DC coefficient code length values and 252 AC coefficient code length val- 25 ues, are provided to multiplexer 156. Each of the four 8x8 blocks is comprised of 1 DC coefficient code length value and 63 AC coefficient code length values. For each DC DCT coefficient code length value provided to multiplexer 15b, a corresponding DQT coeffi- 30 cient code length value is provided to multiplexer 156 from the DOT subsystem. Multiplexer 15b is responsive to a control signal Maso as to provide the DQT coefficient code length value from the DQT subsystem to code length summer 166 in place of each of the 4 DC coeffici- 35 ent code length values from code length lookup table 145. However, the 252 AC coefficient code length values from code length lookup table 146 are provided via multiplexer 150 to code length summer 166. For each of the four 8×8 blocks, code length summer 160 sums the 40 63 AC coefficient code length values along with the DQT coefficient code length value so as to determine the number of bits required to code each 8×8 DQT/DCT coefficient sub-block. The output of code length summer 16b is four values indicated by the refer- 45 ence signal CL8 with each value corresponding to the sum of the code lengths in each of the four \$x8 DQT/DCT blocks.

Similarly, the 256 code length values from code length lookup table 14c, comprised of a total of 16 DC 50 coefficient code length values and 240 AC coefficient code length values, are provided to multiplexer 15c. Each of the sixteen 4×4 blocks is comprised of 1 DC coefficient code length value and 15 AC coefficient code length values. For each DC DCT coefficient code 55 leagth value provided to multiplexer 15c, a corresponding DQT coefficient code length value is provided to multiplexer 15c from the DQT subsystem. Multiplexer 15c is responsive to a control signal Meso as to provide the DC coefficient code length value from the DQT 60 subsystem to code length summer 16c in place of each of the 16 DC coefficient code length values from code length lookup table 14c. However, the 240 AC coefficient code length values from code length lookup table 14c are provided via multiplexer 15c to code length 65 summer 16b. For each of the sixteen 4×4 blocks, code length summer 16c sums the 15 AC coefficient code length values along with the DQT subsystem DC coef12

ficient code length value so as to determine the number of bits required to code each 4×4 DQT/DCT coefficient sub-block. The output of code length summer 16c is sixteen values indicated by the reference signal CLA with each value corresponding to the sum of the code lengths in each of the sixteen 4×4 DQT/DCT blocks.

Finally, the 256 code length values from code length lookup table 14d, comprised of a total of 64 DC coefficient code length values and 192 AC coefficient code length values, are provided to multiplexer 15d. Each of the sixty-four 2×2 blocks is comprised of 1 DC coefficient code length value and 3 AC coefficient code length values. For each DC DCT coefficient code length value provided to multiplexer 15d, a corresponding DQT coefficient code length value is provided to multiplexer 15d from the DQT subsystem. Multiplexer 15d is responsive to a control signal Maso as to provide the DC coefficient code length value from the DQT subsystem to code length summer 16d in place of each of the 64 DC coefficient code length values from code length lookup table 14d. However, the 192 AC coefficient code length values from code length lookup table 14d are provided via multiplexer 15d to code length summer 16d. For each of the sixty-four 2×2 blocks, code length summer 16d sums the 3 AC coefficient code length values along with the DQT subsystem DC coefficient code length value so as to determine the number of bits required to code each 2×2 DQT/DCT coefficient subblock. The output of code length summer 16d is sixtyfour values indicated by the reference signal CL2 with each value being the sum of the code lengths in each of the sixty-four 2×2 DQT/DCT blocks.

The values CL8, CLA, and CL2 are also identified with block position orientation indicia for discussion later herein. The position indicia is a simple x-y coordinate system with the position indicated by the subscript (x,y) associated with the values CL8, CLA, and CL2.

The block size assignment (BSA) is determined by examining values of CL2, CLA, CLA and CL16. Four neighboring entries of CL2(x,s) are added and the sum is compared with the corresponding entry in CLA(LL) The output of CL2(x,) from code length summer 16d is input to adder 18 which adds the four neighboring entries and provides a sum value CLA'(12). For example, the values representative of blocks CL2(0,0), CL2(0,1), CL2(1,0), and CL2(1,1) are added to provide the value CLA (0.0). The value output from adder 18 is the value CLA'(x,) which is compared with the value CLA(x,) output from code length summer 16c. The value CLA'(x,y) is input to comparator 20 along with the value CLA(x,y). Comparator 20 compares the corresponding input values from adder 18 and code length summer 16c so as to provides a bit value, P, that is output to a P register (FIG. 2) and as a select input to multiplexer 22.

In the example as illustrated in FIG. 1, the value CLA'(n,0) is compared with the value CLA(n,0). If the value CLA'(n,0) is greater than the summed values of CLA'(n,0) comparator 28 generates a logical one bit, "1", that is entered into the P register. The "1" bit indicates that a corresponding 4×4 block of DCT coefficients can be coded more efficiently using four 2×2 subblocks. If not, a logical zero bit, "0", is entered into the P register, indicating that the 4×4 block is coded more efficiently using the corresponding 4×4 block.

The output of code length summer 16c and adder 18 are also provided as data inputs to multiplexer 22. In response to the "1" bit value output from comparator 20, multiplexer 22 enables the CLA'(x,y) value to be out-

put therefrom to adder 24. However should the comparison result in a "0" bit value being generated by comparator 20, muliplexer 22 enables the output CLA(x,r) from code length summer 16c to be input to adder 24. Adder 24 is used to sum the data input therefrom, as selected from the comparisons of the values of CLA(xx) and CLA'(xx). The result of the sixteen comparisons of the CLA(x,y) and the CLA'(x,y) data is added in adder 24 to generate a corresponding CLA (x, ) seles. For CLA'(x,r) mbon the comparison result bit is sent to the P

The next stage in the determination of block size assignment is similar to that discussed with respect to the generation and comparison of the values CLA and 15 CLA'. The output of CLB'(x,p) is provided as an input to comparator 26 along with the output CL8(x,r) from code length summer 166. If the corresponding entry in CLE(x,) is greater than the summed value CLE(x,) comparator 26 generates a "1" bit which is output to the 20 Q register (FIG. 2). The output of comparator 26 is also provided as a selected input to multiplexer 28 which also receives the values CLa(xx) and CLa(xx) respectively from code length summer 160 and adder 24. Should the value output from comparator 26b be a "1" 25 bit, the CLS (x,r) value is output from multiplexer 28 to adder 30. However, should the value CLE(xx) be greater than the value CLE(ap) comparator 26 generates a "O" bit that is sent to the Q register and also to the select input of multiplexer 28. Accordingly, the value 30 CLB(xx) is then input to adder 30 via multiplexer 28. Comparison results of comparator 26 are the Q values sent to the Q register. Again a "1" bit indicates that the corresponding 8×8 block of DCT coefficients may be more efficiently coded by smaller blocks such as all 35 4×4 blocks, all 2×2 blocks or a combination thereof as optimally determined by the smaller block comparisons. A "0" bit indicates that the corresponding 8×8block of DCT coefficients can be more efficiently coded than any combination of smaller blocks.

The values input to adder 30 are summed and provided as an output value CL16' input to comparator 32. A second input is provided to comparator 32 as the value CL16 output from by code length summer 16a. Comparator 32 preforms a single comparison of the 45 value CL16 and CL16'. Should the value CL16 be greater than the value CL16' a "1" bit is extered into the R register (FIG. 3). A "1" bit input to the R register is indicative that the block may be coded more efficiently using sub-blocks rather than a single 16×16block. 50 However should the value CL16 be greater than the value CL16, comparator 32 outputs a "0" bit to the R register. The "O" bit in the R register is indicative that the block of DCT coefficients may be coded more efficiently as a 16×16 block.

Comparator 32 is also provides the output R bit as a select input to multiplexer 34. Multiplexer 34 also has inputs for receiving the CL16 and CL16' values respectively provided from code length summer 16s and adder 30. The output from multiplexer 34 is the value 60 CL16 should the R output bit be a "O" while the value CL16' is output should the R output bit be a "1". The output of multiplexer 34 is a value indicative of the total bits to be transmitted.

It should be noted that the overhead bits vary from 65 one bit to up to twenty-one bits (1+4+16) when  $4\times4$ and  $2\times2$  blocks are used everywhere within the  $16\times16$ block.

In FIG. 2, the P value output from comparator 20 (FIG. 1) is input serially to a sixteen-bit register, P register 40. Similarly, the output from comparator 26 is input serially to a four-bit register, Q register 42. Finally, the output from comparator 32 is input serially to a one-bit register, R register 44. The output from P register 40 is provided as a P output to the select input of multiplexer 46. Multiplexer 46 also has inputs as the QC2 and QC4 values respectively output from Quantizer lookup tables each of the sixteen comparisons of the CLA(x,t) and 10 12d and 12c. The output of multiplexer 46 is provided as an input to multiplexer 48, which also has as a second input for the QCS values as output from quantizer lookup table 12b. A select input to multiplexer 48 is provided from the output of Q register 42. The output of multiplexer 48 is coupled as one input to multiplexer 50. The other input of multiplexer 50 is coupled to the output of quantizer lookup table 12a for receiving the values QC16. The select input of multiplexer 50 is conpled to the output of R register 44 so as to receive the output bit R.

As illustrated in FIG. 2, P register 40 includes a sequence of bit positions, 0-15, with corresponding bit values as determined by the comparison process as discussed with reference to FIG. 1. Similarly Q register 42 and R register 44 respectively have bit position 0-3 and 0 with corresponding data as determined with reference to PIG. 1. The data in the P, Q and R registers as illustrated in FIG. 2 is merely for the purpose of illustration.

As illustrated in FIG. 2, the value of P register 40 bit is used to select via multiplexer 46, QC2 data (four 2×2 blocks of quantized transform coefficients) or the corresponding QC4 data (a 4×4 block of quantized transform coefficients). Multiplexer 48, in response to the value of the bit output from Q register 42 selects between the output of multiplexer 46 and the value QCS data. When the Q register bit value is a "1" bit, the output of multiplexer 46 as input to multiplexer 48 is selected for output of multiplexer 48. When the Q register bit value is a "0" bit, the output of multiplexer 48 is the QC\$ value. Therefore, the output bit value of O register 42 is used to select between four QC4 blocks or sub-blocks of QC2 values as output from multiplexer 46 or a corresponding single 8×8 block. As illustrated in FIG. 2, the four upper left hand blocks as output from multiplexer 46 include four 2×2 blocks with three neighboring 4×4 blocks. However with the bit of the Q register being a "0" bit, multiplexer 48 selects the \$x8 block as an output. This example illustrates the conditional replacement scheme.

The output of multiplexer 48 is coupled as an input to multiplexer 50. The other input of multiplexer 50 is provided with the Q16 data, the  $16 \times 16$  block of quantized DCT coefficients as provided from quantizer lookup table 12a. The select input to multiplexer 50 is the output bit of the R register. In the example illustrated in FIG. 2, the bit output from R register 44 is a "1" bit thus selecting data as output from multiplexer 50 that which was provided from multiplexer 48. Should the R register 44 output bit value be a "0" bit, multiplexer 50 would output the QC16 data.

The multiplexing scheme as illustrated in FIG. 2 utilizes the block assignments to multiplex coefficient sub-blocks QC2, QC4, QC1, QC16 values into a composite block of DCT coefficients QC. In essence this step is accomplished by three stages. The first stage conditionally replaces a 4×4 block of QC4 with four 2×2 sub-blocks according to the content of the P register. The second stage conditionally replaces an \$x8

block of QC8 by four 4×4 sub-blocks as resulting from the previous stage according to the content of the Q register. The third stage conditionally replaces the 16×16 block of QC16 with the result of the previous stages if the R register contains a "1" bit.

FIGS. 3a and 3b respectively illustrate the exemplary P, Q and R register data and corresponding and BSA bit pattern, and the corresponding inverted quadtree corresponding thereto. The level of hierarchy involved is that should the bit stored in the R register be a "1", a 10 condition exists which is indicative that the image block may be more efficiently coded using smaller blocks. Similarly, should the Q register contain any "1" bits it further indicates that the corresponding 8 x 8 block may be more efficiently coded by smaller blocks. Similarly, 15 should the P register contain any "1" bits it further indicates that the corresponding 4×4 block may be more efficiently coded using four 2×2 blocks. Should any of the registers contain a "O" bit, this indicates that the block or sub-block may be coded more efficiently 20 by using the size block related thereto.

For example, the value of the bit in the P register bit 0 position, a "1" bit, indicates that this 4×4 block may be more efficiently coded using four 2×2 blocks, while the "O" bits in the P register bit positions indicate that 25 the three 4×4 are more efficiently coded using corresponding 2×2 blocks. However, the bit value "0" in the O register indicates that the four 4×4 blocks, comprised of one group of four 2×2 blocks and three 4×4 blocks. may be more efficiently coded by a single 8×8 block. 30 Therefore, the Q register data would override the P register data. Once the P register data was overridden by the Q register 0 position bit, data in the P register bit positions 0-3, need not be transmitted as part of the block size assignment (BSA) data. However, should a 35 bit position in a higher register be a "I" bit, such as bit position 1 of the Q register, the corresponding P register bits are provided as part of the BSA data. As illustrated in FIG. 3a, the Q register bit position 1 is a "1" bit and therefore the corresponding P register bits 4-7 are pro- 40 vided in the BSA data. On a higher level, since the R register bit is a "1" bit each of the Q register bits are provided in the BSA data.

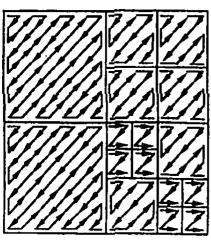

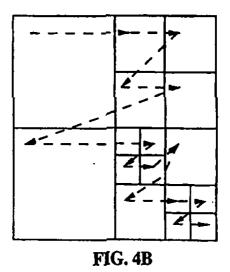

Returning to FIG. 2, the composite block QC conefficiently coded by run-length codes. The number of consecutive zeros or runs are sent instead of the code words for each zero. In order to maximize the efficiency of the run-length coding, the coefficients are ordered in a predetermined manner such that the occur- 50 reace of short runs is minimized. Minimization is done by encoding the coefficients which are likely to be non-zeros first, and then encoding the coefficients that are more likely to be zeros last, Because of the energy compaction property of DCT towards low frequency, 55 and because diagonal details occur less often than horizontal or vertical details, diagonal scan or zig-zag scan of the coefficients is preferred. However, because of the variable block sizes used, the zig-zag scan has to be modified to pick out the low frequency components 60 from each sub-block first, but at the same time follow the diagonal acanning for coefficients of similar frequency, technically when the sum of the two frequency indices are the same.

Accordingly, the output composite block QC from 65 multiplexer 50 is input to zig-zag scan serializer 52 along with the BSA data (P, Q and R). FIG. 4c illustrates the zig-zag ordering of the block data within blocks and

corresponding sub-blocks. FIG. 46 illustrates the ordering in the serialization between blocks and sub-blocks as determined by the BSA data.

The output of zig-zag scan serializer 52, comprised of the ordered 256 quantized DCT coefficients of the composite block QC, is input to coefficient buffer 54 where they are stored for run-length coding. The serialized coefficients are output from coefficient buffer 54 to run-length coder 56 where run-length coding is preformed to separate out the zeros from the non-zero coefficients. Run-length as well as the non-zero coefficient values are separately provided to corresponding lookup tables. The run-length values are output from run-length coder 56 as an input of run-length code lookup table 58 where the values are Huffman coded. Similarly, the non-zero coefficient values are output from run-length coder 56 as an input to non-zero code lookup table 60 where the values are also Huffman coded. Although not illustrated it is further envisioned that run-length and non-zero code look up tables may be provided for each block size.

The Huffman run-length coded values along with the Huffman non-zero coded values are respectively output from run-length lookup code table 58 and non-zero code lookup table 60 as inputs to bit field assembler 62. An additional input to bit field assembler 62 is the BSA data from the P, Q and R registers. Bit field assembler 62 disregards the unnecessary bits provided from the P, O and R registers. Bit field assembler 62 assembles the input data with BSA data followed by the combined RL codes and NZ codes. The combined data is output from bit field assembler 62 to a transmit buffer 64 which temporarily stores the data for transfer to the transmitter (not shown).

When the DQT subsystem is employed the coded DC DCT coefficients are omitted from transfer to transmit buffer 64. Instead the DQT coefficients provided by the DQT subsystem, as an input to bit field assembler 62, are transmitted. The formatting of data in this embodiment is typically a data packet comprised in sequence of sync, BSA, DQT and DCT data bits. Furthermore, the packet may also include end of block code bits following the DCT bits.

FIGS. 50-5d illustrates an alternate scan and serialtains many zero coefficient values which can be more 45 ization format for the zig-zag scan serializer 52. In FIGS. 50-5d, the quantized DCT coefficients are mapped into a one-dimensional string by ordering from low frequency to high frequency. However in the scheme illustrated in FIGS. 5a-5d the lower order frequencies are taken from each block prior to taking the next higher frequencies in the block. Should all coefficients in a block be ordered, during the previous scan, the block is skipped with priority given to the next block in the scan pattern. Block to block scanning, as was done with the scanning of FIGS. 4a-4c is a left-to-right, up to down scan priority.

As previously mentioned the present invention implements a new and previously undisclosed transform identified herein as the differential quadtree transform (DQT). The basis for this transform is the recursive application of the 2×2 DCT on a quadtree representation of the sub-blocks. At the bottom of the inverted quadtree, for example the quadtree illustrated in FIG. 3b, the  $2\times2$  DCT operation is performed and the node is assigned the DC value of the 2x2 DCT transform. The nearest nodes are gathered and another 2×2 DCT is performed. The process is repeated until a DC value is assigned to the root. Only the DC value at the root is signal N<sub>d</sub> for providing the DC DCT coefficient (DC<sub>4</sub>) and the AC coefficients (AC<sub>4</sub>) from DCT element 78. Multiplexer 80 creates a composite 8×8 block of DC and AC DCT coefficients, block 81. Block 81 is identical in arrangement with respect to the AC DCT coefficients (AC<sub>4</sub>) as output from DCT element 74 in block 75. However in block 81 the DC DCT coefficients (DC<sub>4</sub>) and AC DCT coefficients (AC<sub>4</sub>) replace the DC DCT coefficients (DC<sub>4</sub>) in block 75 as it was output from DCT element 74. As illustrated in FIG. 6, the circled DC DCT coefficients (DC<sub>4</sub>) and AC DCT coefficients (AC<sub>4</sub>) in block 81 replace a corresponding DC DCT coefficients (DC<sub>4</sub>) in the 8×8 block arrangement of block 75. In block 81 since there is only one DC coefficient for every fifteen AC coefficients, the com-

coded at a fixed number of bits, typically 8-bits, while the rest are Huffman coded. Because each 2×2 DCT operation is nothing more than a sum and a difference of numbers, no multiplications are required, and all coefficients in the quadtree, except DC, represent the differences of two sums, hence the name DQT. Theoretically this type of transform cannot exceed the performance of 16×16 DCT coding. However the implementation of the DQT transform has the advantage of requiring seemingly simple hardware in addition to naturally 10 implementing the adaptive block size coding. Purthermore the quadtree structure allows the coding of the zero coefficients by simply indicating the absence of a subtree when all sub-blocks under the subtree contain only zeros.

posite block is considered as four 4×4 blocks.

The four 4×4 blocks of DCT coefficients output from Multiplexer \$0 is provided to selector \$2. Selector \$2 provides the AC DCT coefficients (AC<sub>4</sub>) and (AC<sub>4</sub>) from the input block of DCT coefficients as an input to multiplexer \$6 while providing the DC DCT coefficients (DC<sub>4</sub>) as 2×2 block of DC DCT coefficients (DC<sub>4</sub>), block \$3, to 2×2 DCT element \$4.

FIG. 6 illustrates an exemplary implementation of a DQT subsystem. In FIG. 6, the same 16×16 block of pixel data is received as that of the subsystem of FIGS. 1 and 2 such that the DQT processing is accomplished in parallel to the adaptive block size data processing. 20 The input block of pixel data is provided to 2×2 DCT element 70 which performs sixty-four 2×2 two-dimensional DCT operations on data. The output of DCT element 70 is comprised of a 16×16 block of DCT coefficients, block 71. For each 2×2 block of pixel data 25 processed by DCT element 70, the corresponding output is comprised of one DC DCT coefficient (DC2) and three AC coefficients (AC2).

DCT element \$4 performs a 2×2 two-dimensional DCT operations on the input block of DC DCT coefficients (DC<sub>4</sub>). The output of DCT element 78 is comprised of a 2×2 block of DCT coefficients, block \$5. For the 2×2 block of DC DCT coefficients (DC<sub>4</sub>) processed by DCT element \$4, the output is comprised of one DC DCT coefficient (DC<sub>16</sub>) and three AC DCT coefficients (AC<sub>16</sub>). The output DC DCT coefficient (DC<sub>16</sub>) and AC DCT coefficients (AC<sub>16</sub>) are provided as another input to multiplexer \$6.

The 16×16 block of DCT coefficients output from DCT element 70 is provided to selector 72. Selector 72 30 removes the AC DCT coefficients from the input block of DCT coefficients and provides an output \$×8 block of comprised of DC DCT coefficients (DC<sub>2</sub>) only. The \$×8 block of DC DCT coefficients (DC<sub>2</sub>), block 73, is provided to 2×2 DCT element 74.

Multiplexer 86 normally provides an output of the AC DCT coefficients (AC4) and (AC4) from multiplexer 80 (via separator \$2). Multiplexer 86 is responsive to a control signal Na for providing the DC DCT coefficient (DC16) and the AC coefficients (AC16) from DCT element \$4. Multiplexer \$6 creates a composite 8×8 block of DC and AC DCT coefficients, block 87. Block \$7 is identical in arrangement with respect to the AC DCT coefficients (AC4) and (AC4) as output from multiplexer 80 in block \$1. However in the block \$7 the DC DCT coefficient (DC14) and AC DCT coefficients (AC14) replace the DC DCT coefficients (DC4) in block 81 as output from multiplexer 80. As illustrated in FIG. 6, the circled DC DCT coefficient (DC14) and AC DCT coefficients (ACid) in block \$7 replace a corresponding DC DCT coefficients (DC<sub>2</sub>) in the \$x\$ block arrangement of block \$1. In block \$7 since there is only one DC coefficient for every fifteen AC coefficients, the composite block is considered as one 8×8 block.

DCT element 74 performs sixteen 2×2 two-dimensional DCT operations on the input block of DC DCT coefficients (DC<sub>2</sub>). The output of DCT element 74 is comprised of an 8×8 block of DCT coefficients. For each 2×2 block of DC DCT coefficients (DC<sub>2</sub>) processed by DCT element 74, the corresponding output is comprised of one DC DCT coefficient (DC<sub>4</sub>) and three AC DCT coefficients (AC<sub>4</sub>). As illustrated in FIG. 6, the circled DC DCT coefficients (DC<sub>4</sub>) and AC DCT coefficients (AC<sub>4</sub>) in block 75 replace a corresponding 45 DC DCT coefficients (DC<sub>2</sub>) in the 8×8 block, block 73, arrangement as output from selector 72.

C(4) as four 2×2 blocks of DC DCT coefficients

C(4), block 77, to 2×2 DCT element 78.

The 8×8 block, block 87, output from multiplexer 86

is comprised of what are considered Discrete Quadtree

DCT element 78 performs four 2×2 two-dimensional

CT operations on the input block of DC DCT coefficients

CT operations on the input block of DC DCT coefficients

CT operations on the input block of DC DCT coefficients

CT operations on the input block of DC DCT coefficients

CT operations on the input block of DC DCT coefficients

are then quantized by providing the coefficient values

to quantizer look table 88.

The 8×8 block of DCT coefficients output from DCT element 74 is provided to selector 76. Selector 76 provides the AC DCT coefficients (AC4) from the 50 input block of DCT coefficients as an input to multiplexer 80 while providing the DC DCT coefficients (DC4) as four 2×2 blocks of DC DCT coefficients (DC4), block 77, to 2×2 DCT element 78.

Quantizer lookup table 88 may also be implemented in conventional read only memory (ROM) form with 60 memory locations containing quantization values. The value of each transform coefficient is used to address a corresponding memory location to provide an output data signal indicative of a corresponding quantized transform coefficient value. The output of quantizer lookup table 88, indicated by the reference signal QC16, is an 8×8 block of quantized DQT coefficient values. Although not illustrated, again the DC coefficient (DC16) of the DQT transform operation may be option-

DCT element 78 performs four 2×2 two-dimensional 55 DCT operations on the input block of DC DCT coefficients (DC4). The output of DCT element 78 is comprised of an 4×4 block of DCT coefficients, block 79. For each of the four 2×2 blocks of DC DCT coefficients (DC4) processed by DCT element 78, the corresponding output is comprised of one DC DCT coefficient (DC4) and three AC DCT coefficients (AC4). The output DC DCT coefficient (DC4) and AC DCT coefficients (AC4) are provided as another input to multiplexer 80.

Multiplexer 80 normally provides an output of the AC DCT coefficients (AC4) from DCT element 74 (via separator 76). Multiplexer 80 is responsive to a control

B

ally treated separately rather than through the corresponding quantizer lookup table.

The DOT coefficients are provided as an output of quantizer lookup table 88 to code length lookup table 90. The quantized DQT coefficient values are each 5 coded using variable length code, such as a Huffman code, in order to minimize the data rate. Code words and corresponding code lengths are found in the form of code length look up table 90. Each of the quantized DQT coefficients DC16, AC16, AC2 and AC4, are used 10 to look up in the code length table the corresponding number of bits required to code each coefficient. Code length lookup table 90 may also be implemented in read only memory form with the DQT coefficients address ing memory locations which contain respective code 15 length values. The DQT coefficient code length values are provided to multiplexers 150-15d of FIG. 1 for replacing the corresponding DC DCT coefficient code length value for each block and sub-block in the block FIGS. 1 and 2.

In FIG. 7 the 64 quantized DQT coefficient values of block 91 are selected for replacement of the DC DCT coefficient values for the block sizes as determined by the block size determination made in accordance as 25 discussed with reference to FIGS. 1 and 2. The values stored in P, Q and R registers 40, 42 and 44 are used in selecting the DQT coefficient values for replacement in the block and sub-blocks of the DC DCT coefficient

The DQT coefficient values are provided from quantizer lookup table 53 (FIG. 6) to one input to multiplexer 92. At the other input of multiplexer 92 a dummy value x is provided. Multiplexer 92 is responsive to the bits of P register 40 for providing an output of the DQT 35 coefficient values for the entire 2×2 sub-block when a "I" is in the P register 40 bit position. When the value in P register 40 bit position is a "0", only the DQT coefficient value which corresponds to the DC coefficient value of the sub-block is output with the remaining 40 values output being the dummy values x. The value x is used merely to maintain the arrangement within the sub-block with these values eventually discarded. Using the data in the sixteen bit position of P register 40 as provided in the example as given with reference to 45 FIGS. 1 and 2, composite block 93 is formed.

The sub-blocks of DQT coefficients and dummy values x output from multiplexer 92 are provided as one input to multiplexer 94. At the other input of multiplexer 94 the dummy value x is again provided. Multi- 50 plexer 94 is responsive to the bits of Q register 42 for providing an output of the DQT coefficient values and dummy values x for an entire 4×4 sub-block as provided from multiplexer 92 when a "1" is in the Q register 42 bit position. When the value in Q register 42 bit 55 position is a "0", only the DQT coefficient value which corresponds to the DC coefficient value of the subblock is output with the remaining values output being the dummy values x. The value x is again used merely to maintain the arrangement within the sub-block with 60 these values eventually discarded. Using the data in the four bit positions of Q register 42 as provided in the example as given with reference to FIGS. 1 and 2, composite block 95 is formed.

The sub-blocks of DQT coefficients and dummy valus x output from multiplexer 94 are provided as one

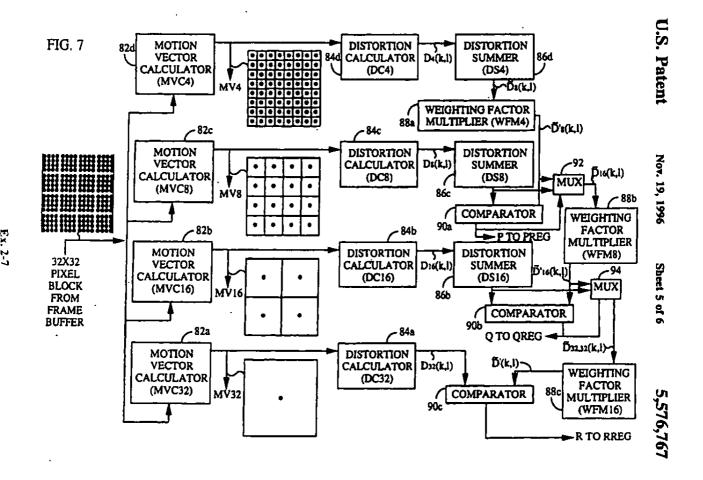

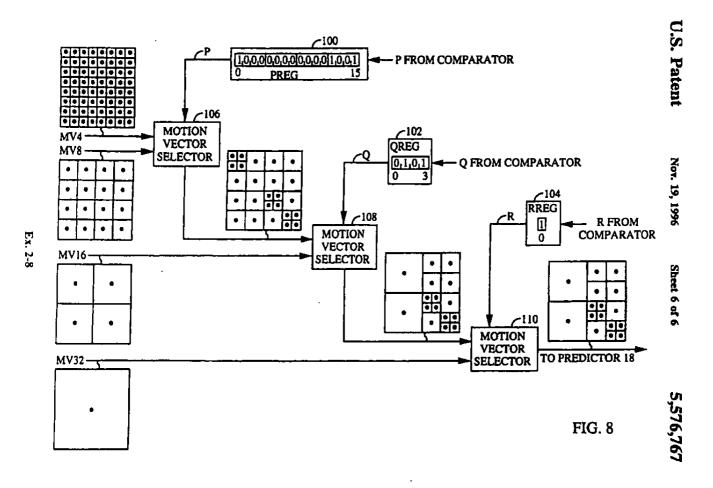

input to multiplexer 96. At the other input of multiplexer 96 the dummy value x is again provided. Multi-