# Case 3:02-cv-02002-B-JFS Document 127 Filed 06/17/04 Page 1 of 152 USDC SCAN INDEX SHEET

RYC 6/18/04 15:48

3:02-CV-02002 QUALCOMM INC V. CONEXANT SYSTEMS INC

\*127\*

\*AMDCMP.\*

Gerald L. McMahon (36050) 1 David J. Zubkoff (149488) SELTZER CAPLAN McMAHON VITEK 2 2100 Symphony Towers, 750 B Street San Diego, CA 92101 (619) 685-3003 3 4 Lloyd R. Day (90875) James R. Batchelder (136347) 5 Christopher E. Stretch (166752) DAY CASEBEER MADRID & BATCHELDER LLP 6 20300 Stevens Creek Blvd., Suite 400 Cupertino, CA 95014 7 (408) 873-0110 8 Louis M. Lupin (120846) Alexander H. Rogers (131879) 9 Roger Martin (195003) QUALCOMM INCORPORATED 10 5775 Morehouse Drive 11 San Diego, CA 92121 (858) 658-1121 12 Attorneys for Plaintiff and Counterdefendant **QUALCOMM INCORPORATED** 13 UNITED STATES DISTRICT COURT 14 SOUTHERN DISTRICT OF CALIFORNIA 15 16 QUALCOMM INCORPORATED, 02 CV 2002 B (JFS) 17 Plaintiff, SECOND AMENDED COMPLAINT FOR PATENT INFRINGEMENT, MISAPPROPRIATION OF TRADE 18 SECRETS, AND BREACH OF CONTRACT CONEXANT SYSTEMS, INC. 19 and SKYWORKS SOLUTIONS, INC., **DEMAND FOR JURY TRIAL** 20 Defendants. 21 CONEXANT SYSTEMS, INC. 22 and SKYWORKS SOLUTIONS, INC., 23 Counterclaimants. 24 25 QUALCOMM INCORPORATED, 26 ORIGINAL Counterdefendant. 27 28

98893\_1

2<sup>ND</sup> AMD. COMP. FOR PATENT INFRINGEMENT, MISAPPROPRIATION OF TRADE SECRETS, & B OF K

CASE No. 02 CV 2002 B (JFS)

| 1  |  |

|----|--|

| 2  |  |

| 3  |  |

| 4  |  |

| 5  |  |

| 6  |  |

| 7  |  |

| 8  |  |

| 9  |  |

| 10 |  |

| 11 |  |

| 12 |  |

| 13 |  |

| 14 |  |

| 15 |  |

| 16 |  |

| 17 |  |

| 18 |  |

| 19 |  |

| 20 |  |

| 21 |  |

| 22 |  |

1. Plaintiff QUALCOMM Incorporated ("QUALCOMM"), for its complaint against defendants Conexant Systems, Inc. and Skyworks Solutions, Inc. ("Defendants"), alleges as follows:

#### THE PARTIES

QUALCOMM is a Delaware corporation that maintains its principal place of business at 5775 Morehouse Drive, San Diego, California, 92121. QUALCOMM develops, manufactures, markets, licenses and operates advanced communications systems based on proprietary technology.

- On information and belief, defendant Conexant Systems, Inc. ("Conexant") is a

Delaware corporation having its principal place of business at 4311 Jamboree Road, Newport Beach,

California, 92660-3095.

- 3. On information and belief, defendant Skyworks Solutions, Inc. ("Skyworks") is a Delaware corporation having its principal place of business at 20 Sylvan Road, Woburn, Massachusetts, 01801. On information and belief, Skyworks was formed in June 2002 as a result of a merger between Conexant's wireless business and Alpha Industries, Inc.

#### **JURISDICTION AND VENUE**

- 4. This Court has jurisdiction over QUALCOMM's patent infringement claim pursuant to the patent laws of the United States, 35 U.S.C. §§ 1 et seq., and pursuant to 28 U.S.C. § 1338. This Court has supplemental jurisdiction over QUALCOMM's related misappropriation of trade secrets and breach of contract claims pursuant to 28 U.S.C. § 1367.

- 5. Venue is proper in this judicial district pursuant to 28 U.S.C. §§ 1391(b), 1391(c) and 1400(b) because Defendants have regularly conducted business in this judicial district, and certain of the acts complained of herein occurred in this judicial district.

#### **FACTS**

6. This action arises out of Defendants' infringement of eight patents assigned to QUALCOMM, Defendants' misappropriation of certain trade secrets owned by QUALCOMM, and defendant Conexant's breach of a nondisclosure agreement with QUALCOMM.

#### PATENT INFRINGEMENT

7. On March 12, 1996, U.S. Patent No. 5,499,280, entitled "CLOCK SIGNAL GENERATION," ("the '280 patent") was duly and legally issued to inventors Nathaniel B. Wilson

1

23

24

25

26

27

and Gene H. McAllister. A copy of the '280 patent is attached hereto as Exhibit A.

- 8. On April 1, 1997, U.S. Patent No. 5,617,060, entitled "METHOD AND APPARATUS FOR AUTOMATIC GAIN CONTROL AND DC OFFSET CANCELLATION IN QUADRATURE RECEIVER," ("the '060 patent") was duly and legally issued to inventors Nathaniel B. Wilson, Peter J. Black, and Paul E. Peterzell. A copy of the '060 patent is attached hereto as Exhibit B.

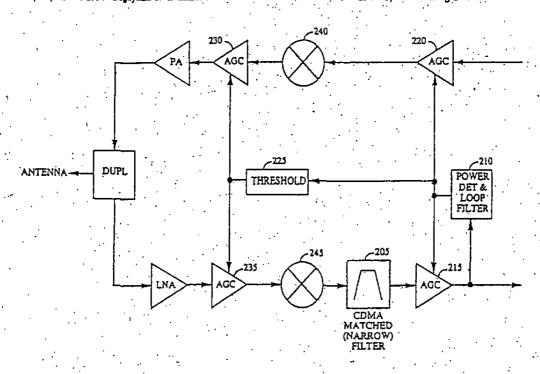

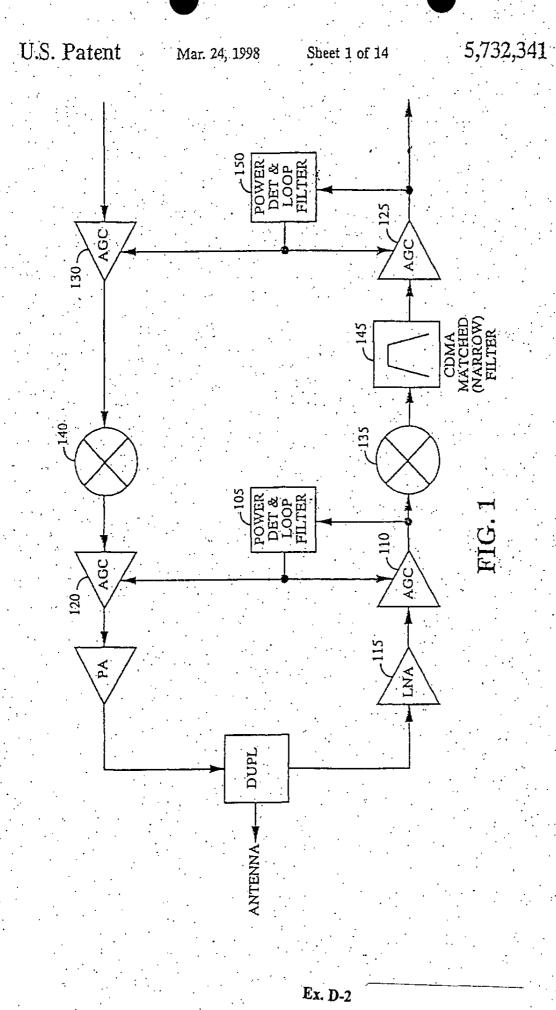

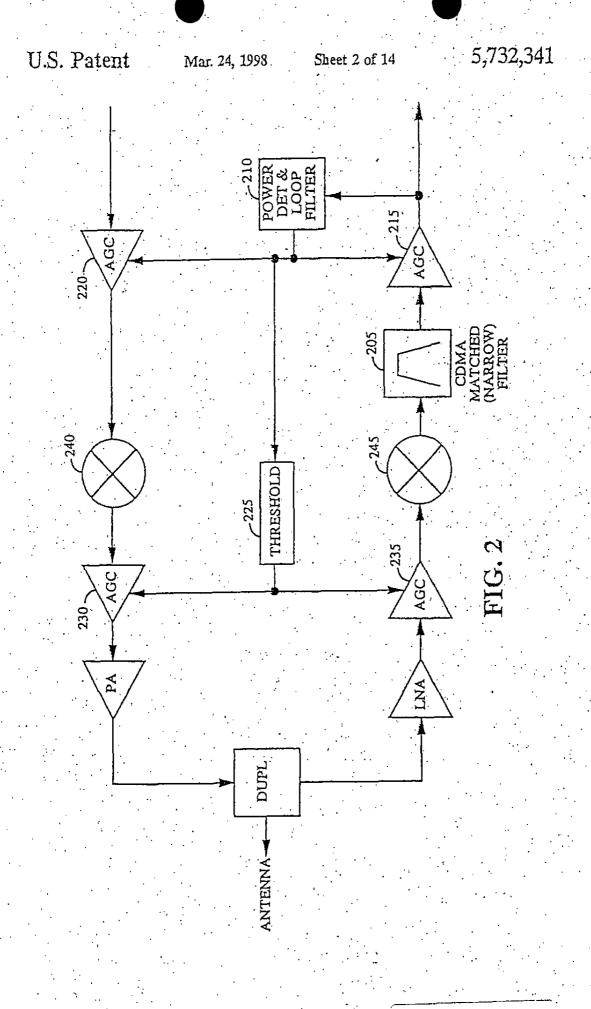

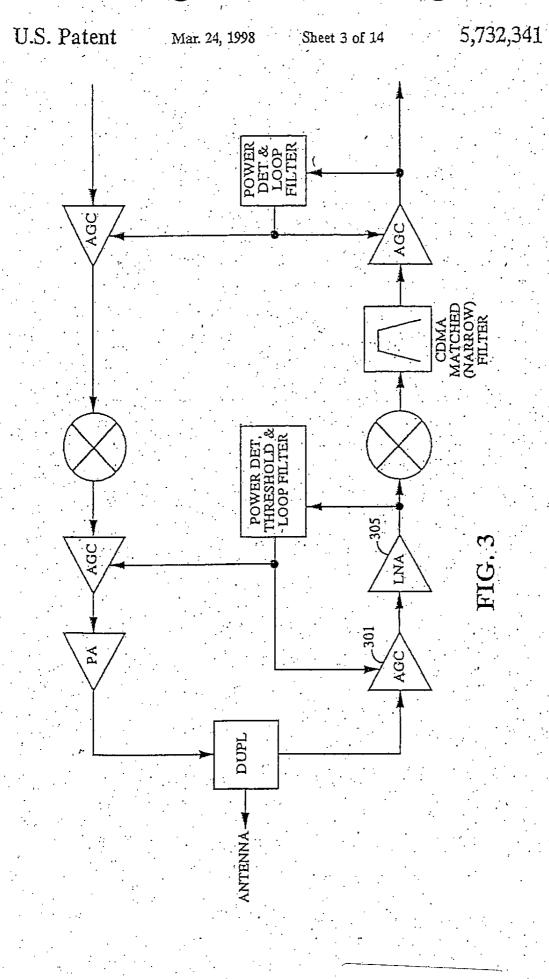

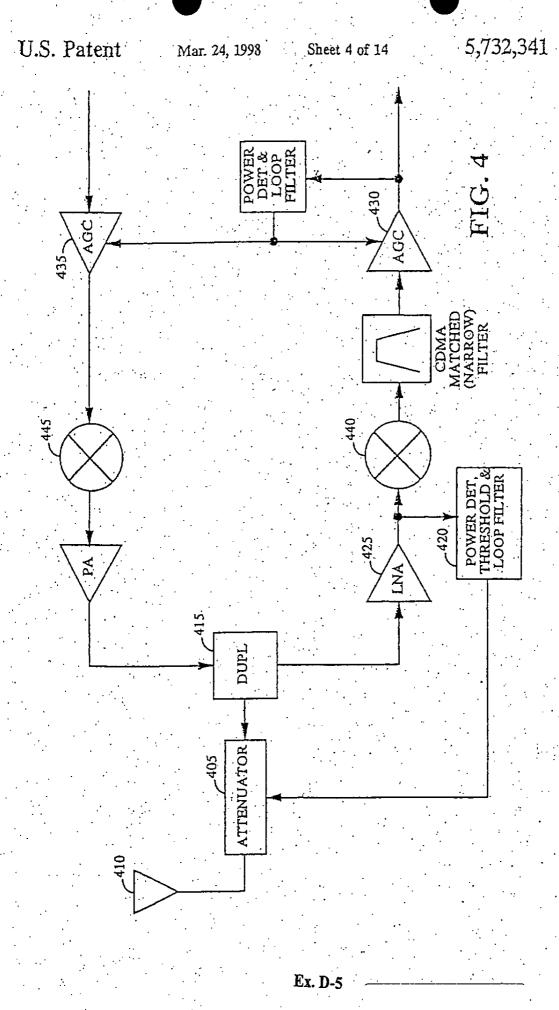

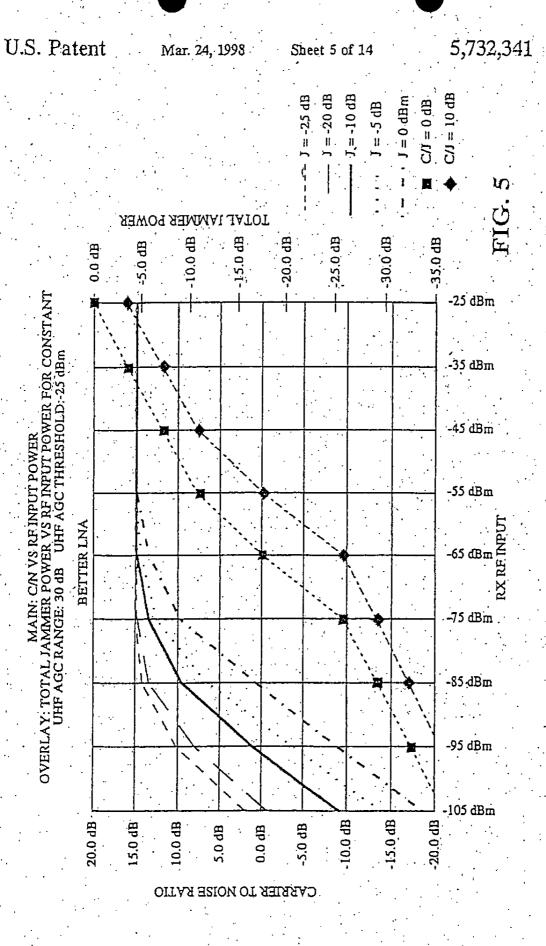

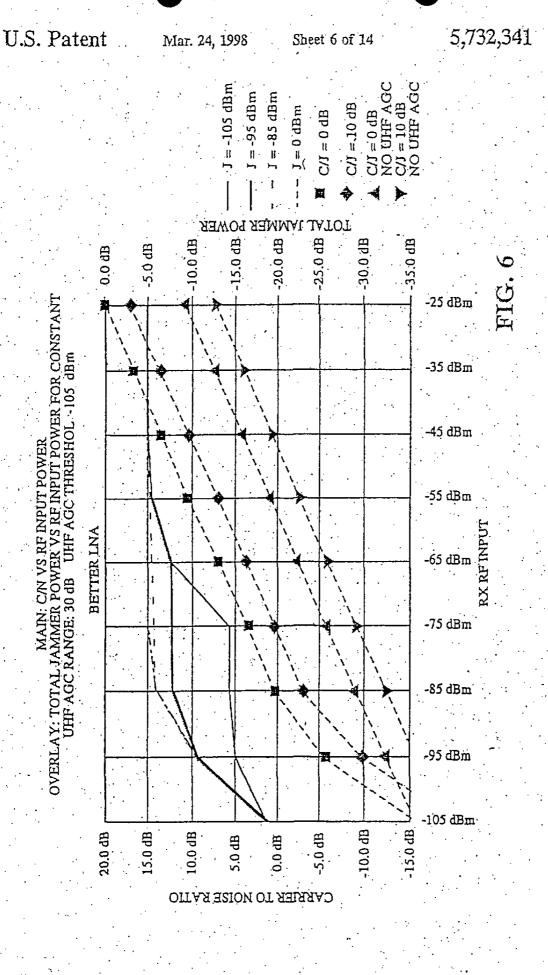

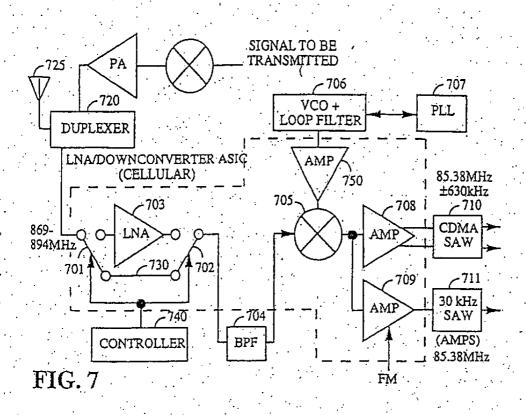

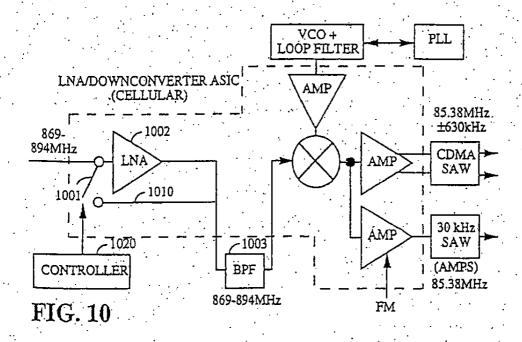

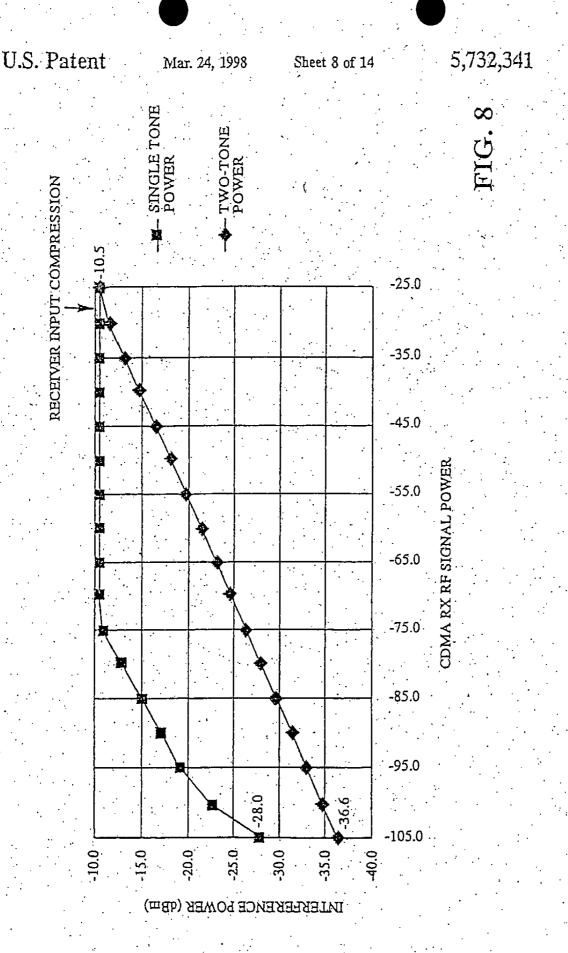

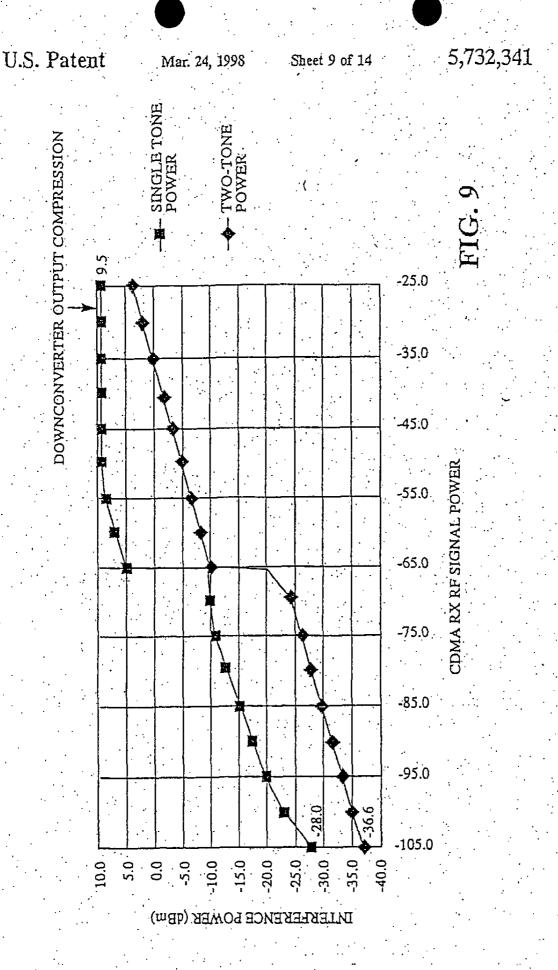

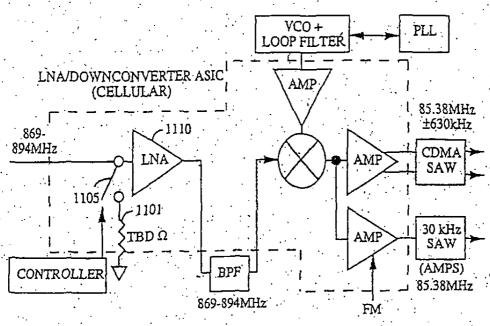

- 9. On March 24, 1998, U.S. Patent No. 5,732,341, entitled "METHOD AND APPARATUS FOR INCREASING RECEIVER IMMUNITY TO INTERFERENCE," ("the '341 patent") was duly and legally issued to inventor Charles E. Wheatley, III. A copy of the '341 patent is attached hereto as Exhibit C.

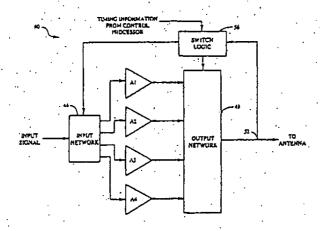

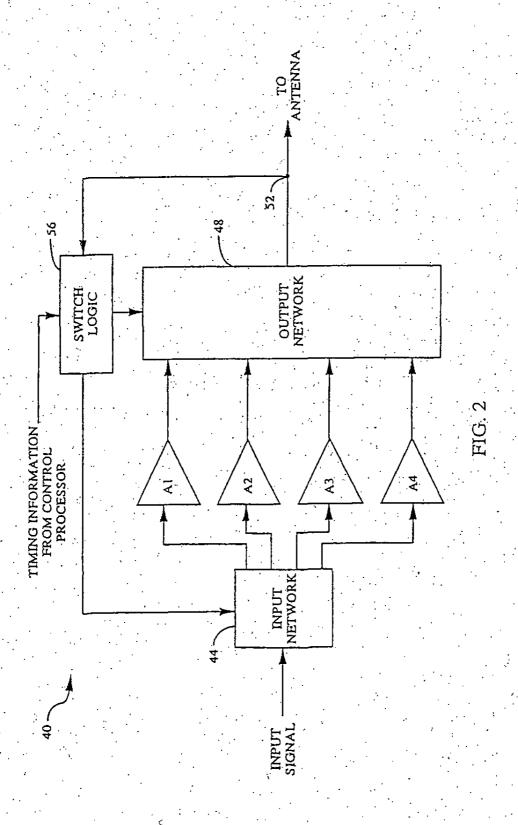

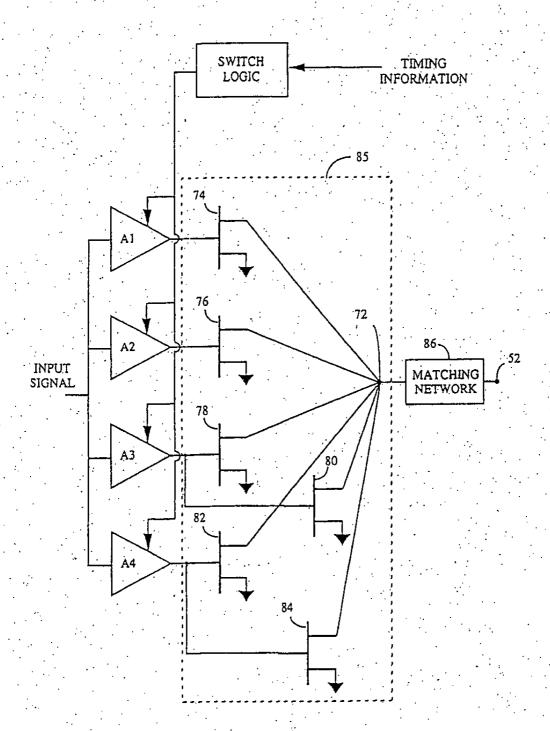

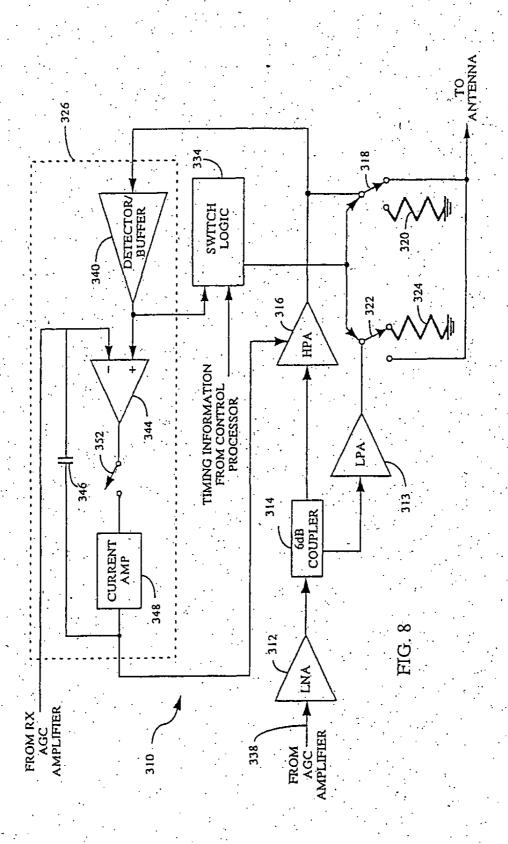

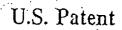

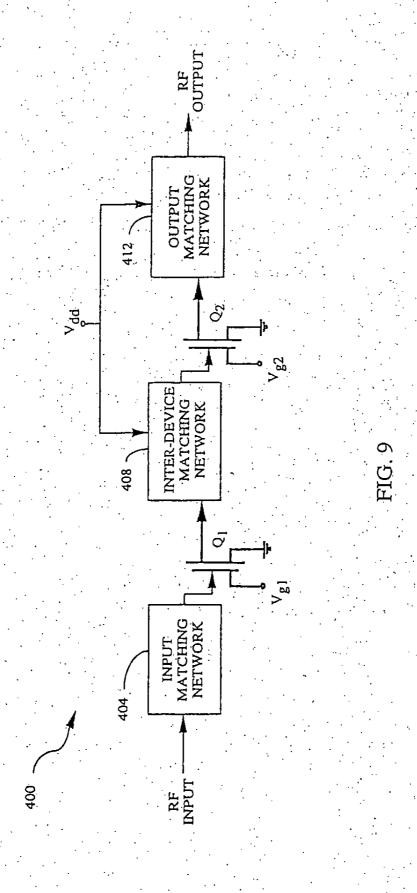

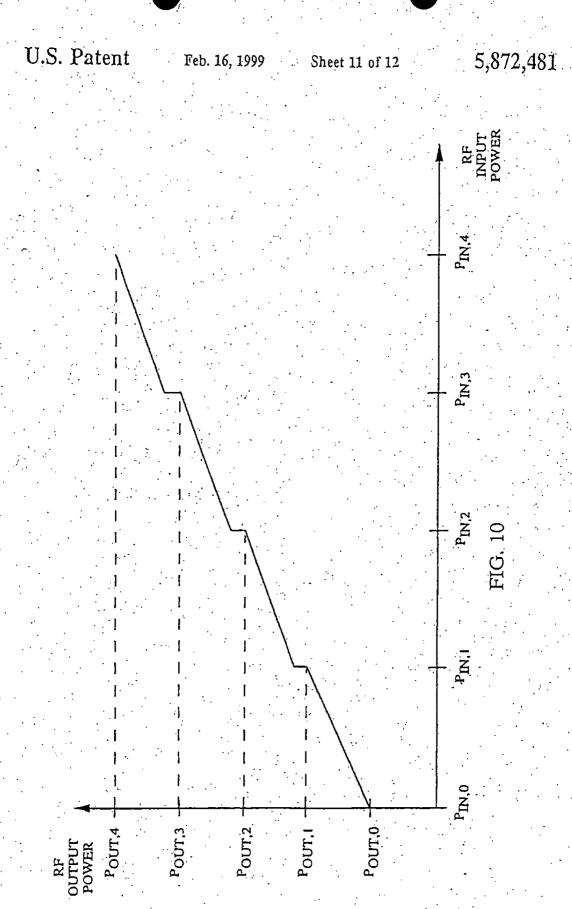

- 10. On February 16, 1999, U.S. Patent No. 5,872,481, entitled "EFFICIENT PARALLEL-STAGE POWER AMPLIFIER," ("the '481 patent") was duly and legally issued to inventors John F. Sevic and Richard J. Camarillo. A copy of the '481 patent is attached hereto as Exhibit D.

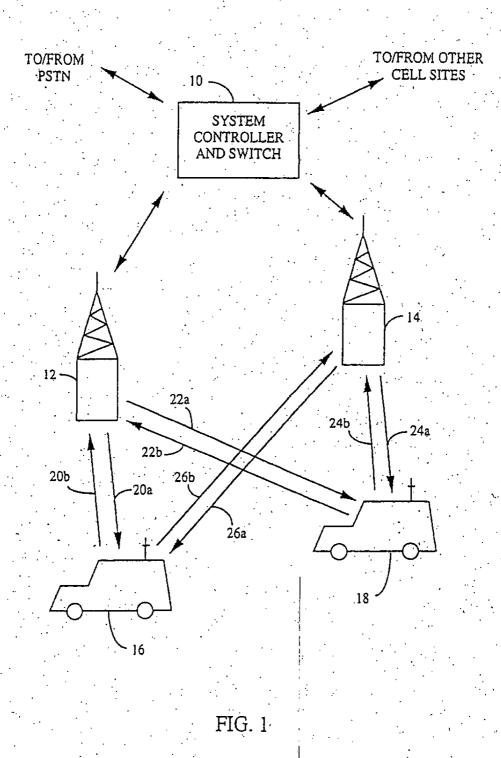

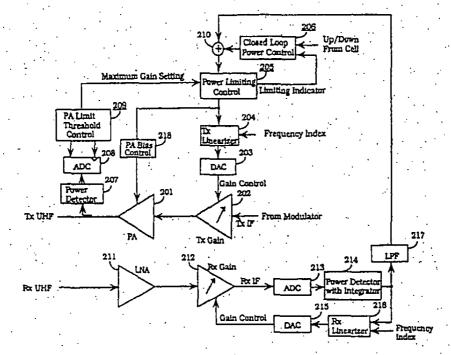

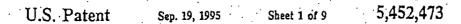

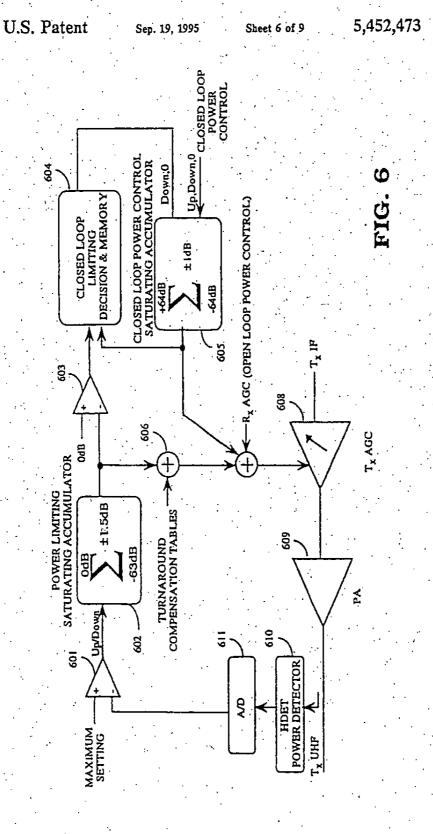

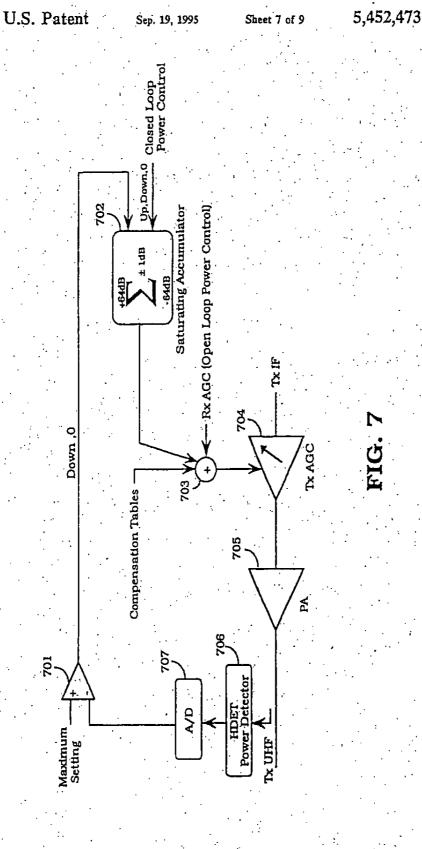

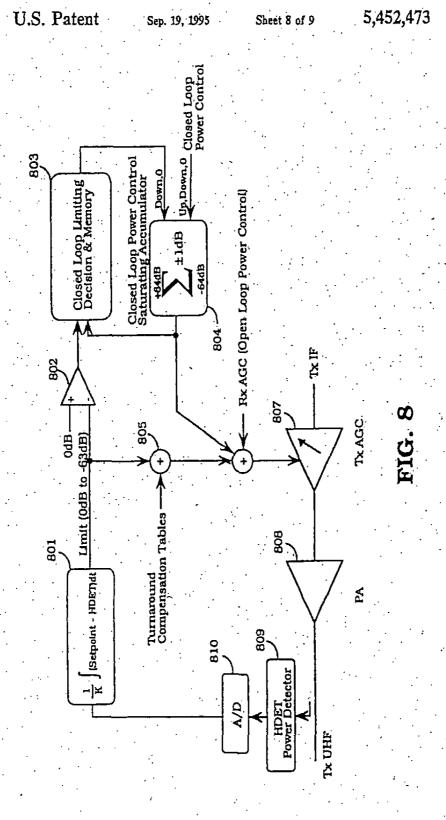

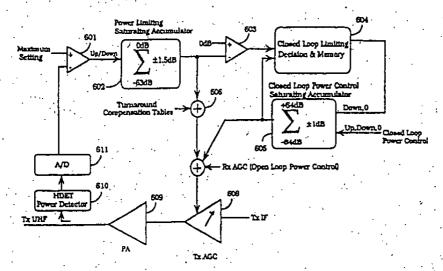

- 11. On September 19, 1995, U.S. Patent No. 5,452,473, entitled "REVERSE LINK, TRANSMIT POWER CORRECTION AND LIMITATION IN A RADIOTELEPHONE SYSTEM," ("the '473 patent") was duly and legally issued to inventors Ana L. Weiland, Richard K. Kornfield, Richard J. Kerr, John E. Maloney, and Nathaniel B. Wilson. A copy of the '473 patent is attached hereto as Exhibit E.

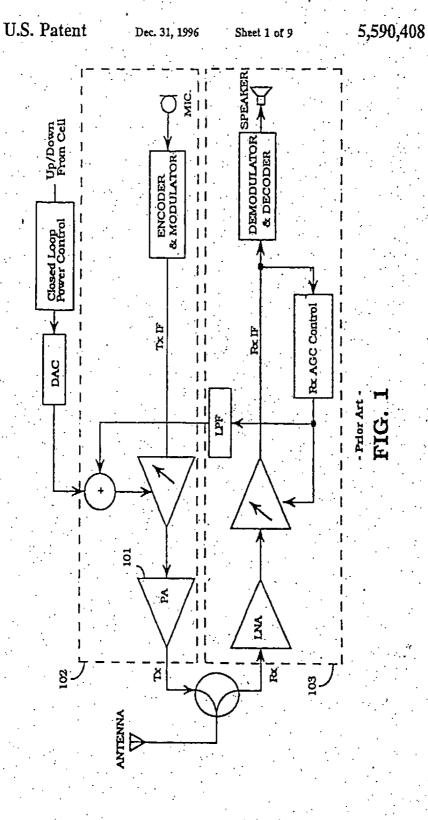

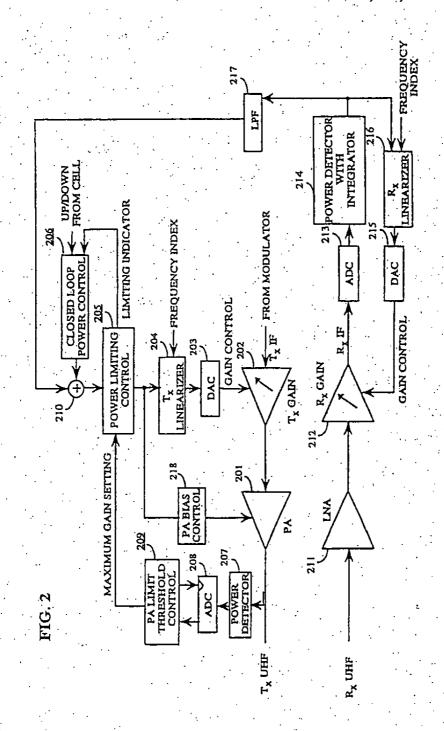

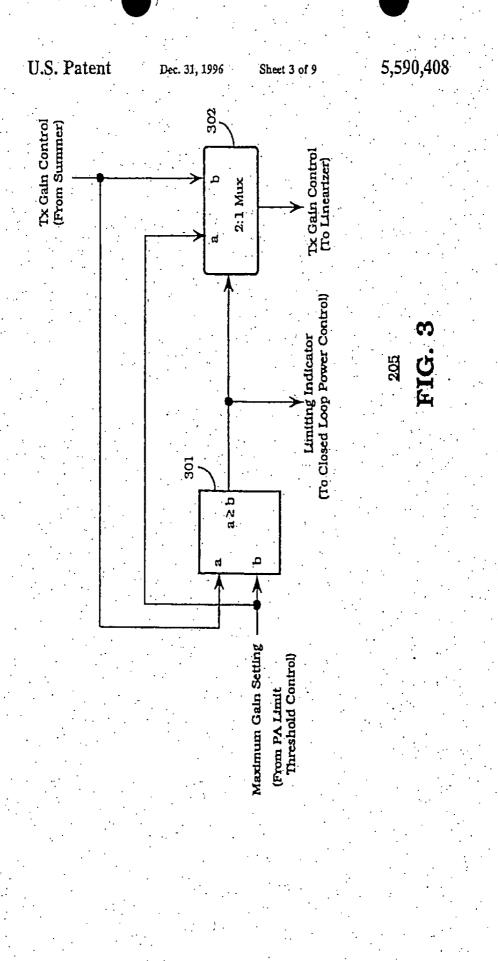

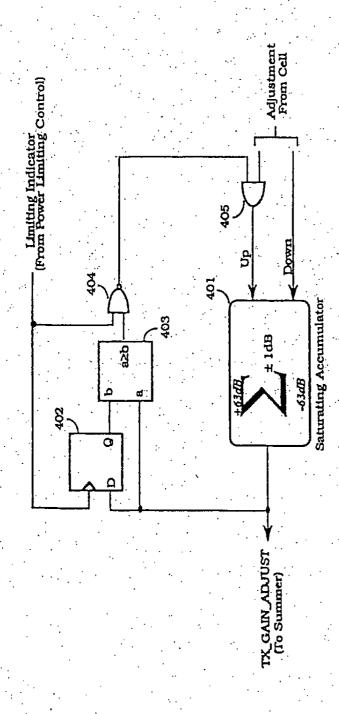

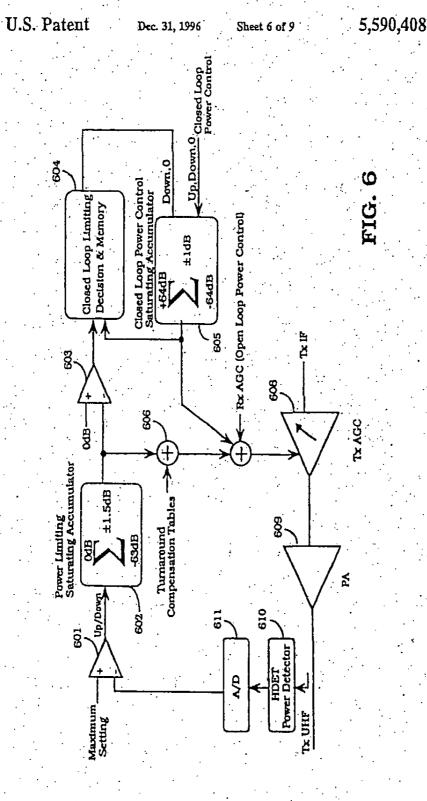

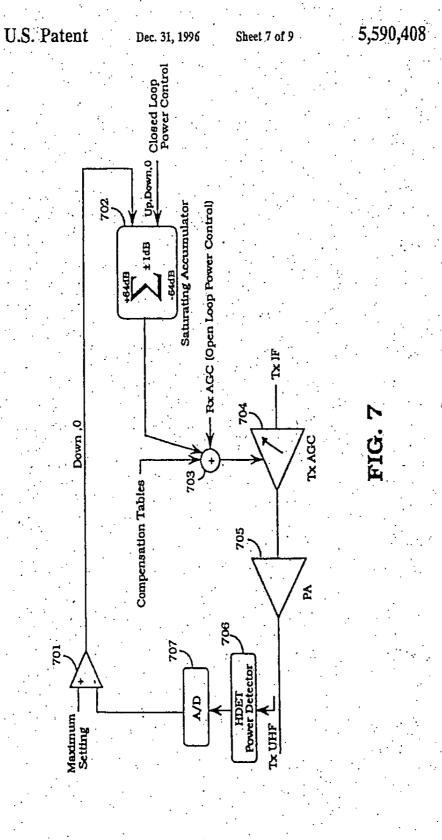

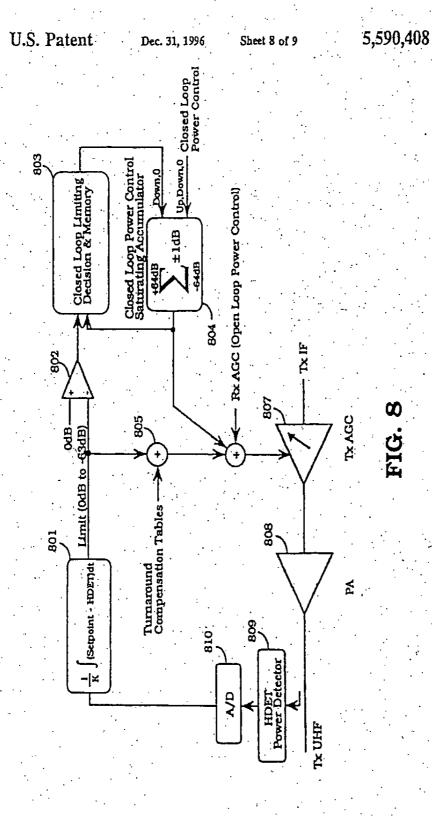

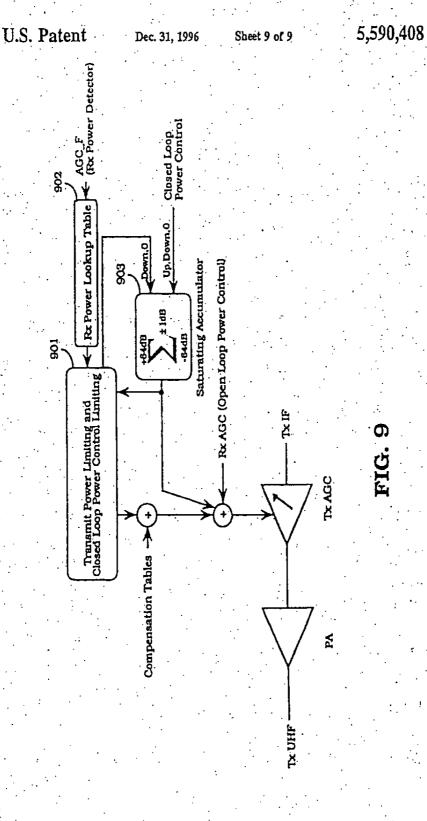

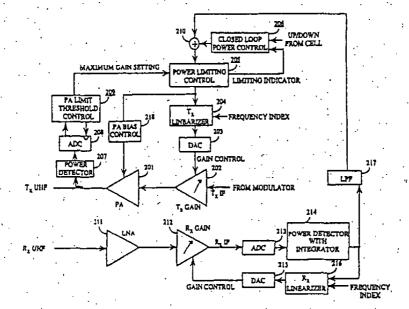

- 12. On December 31, 1996, U.S. Patent No. 5,590,408, entitled "REVERSE LINK, TRANSMIT POWER CORRECTION AND LIMITATION IN A RADIOTELEPHONE SYSTEM," ("the '408 patent") was duly and legally issued to inventors Ana L. Weiland, Richard K. Kornfield, and John E. Maloney. A copy of the '408 patent is attached hereto as Exhibit F.

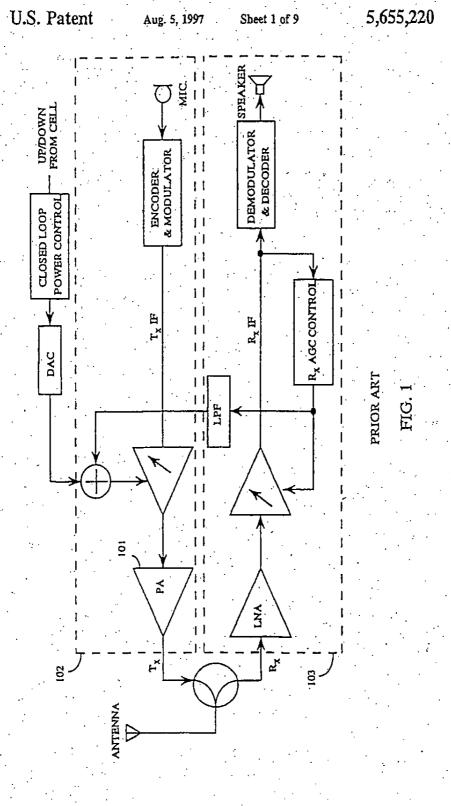

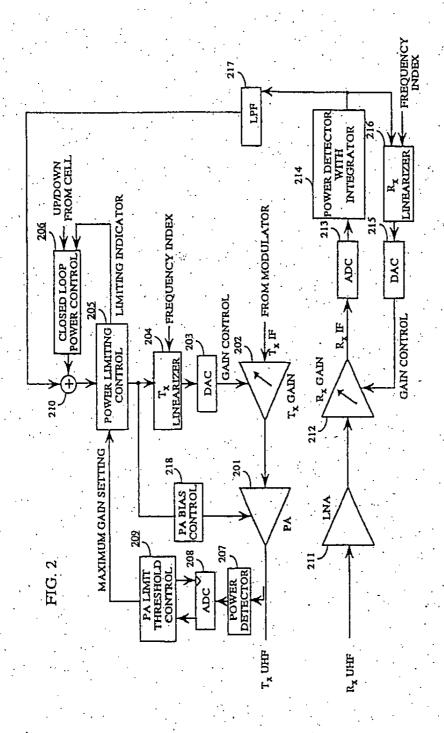

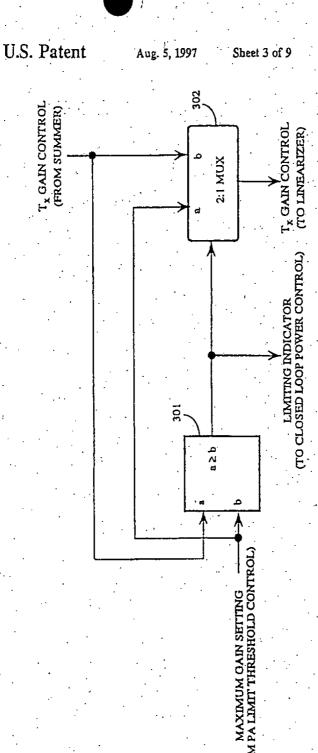

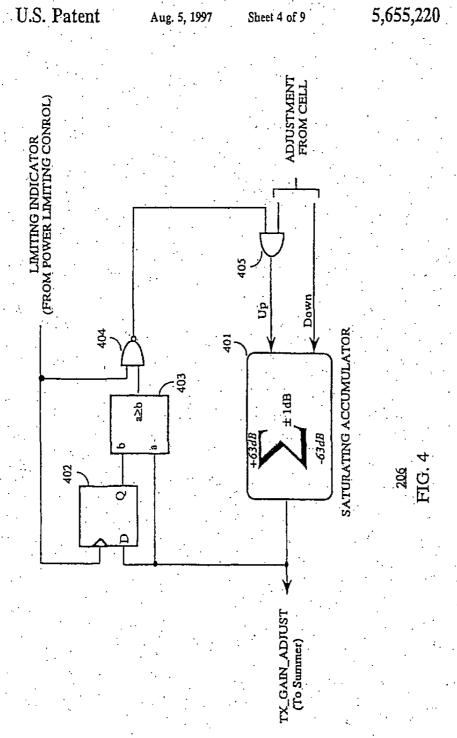

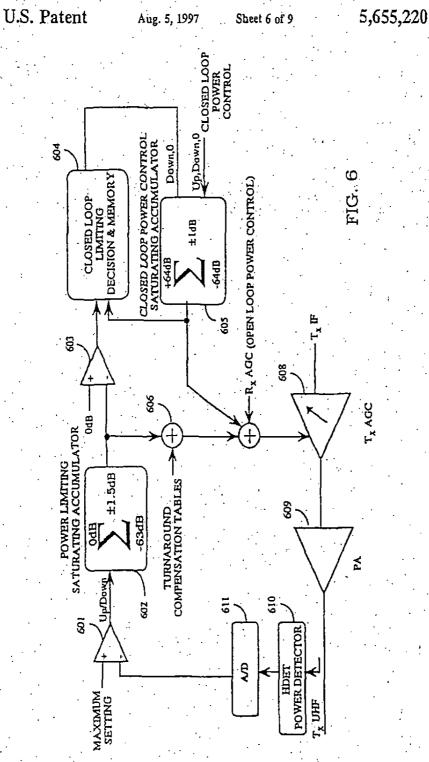

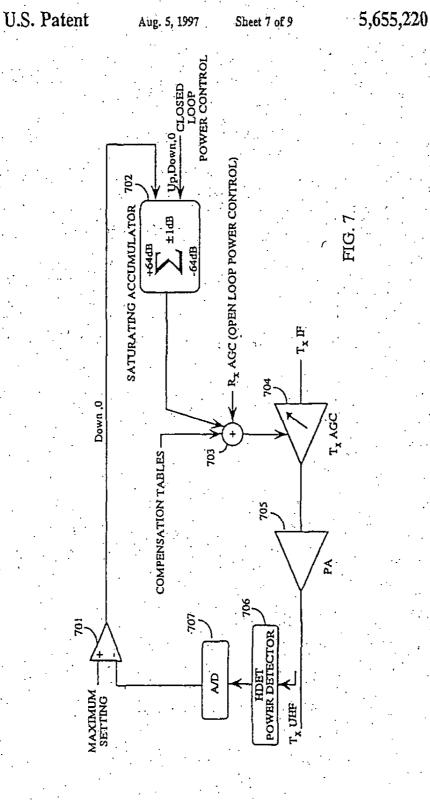

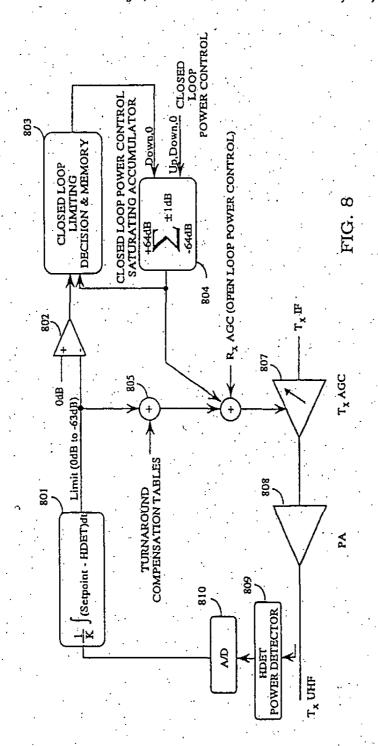

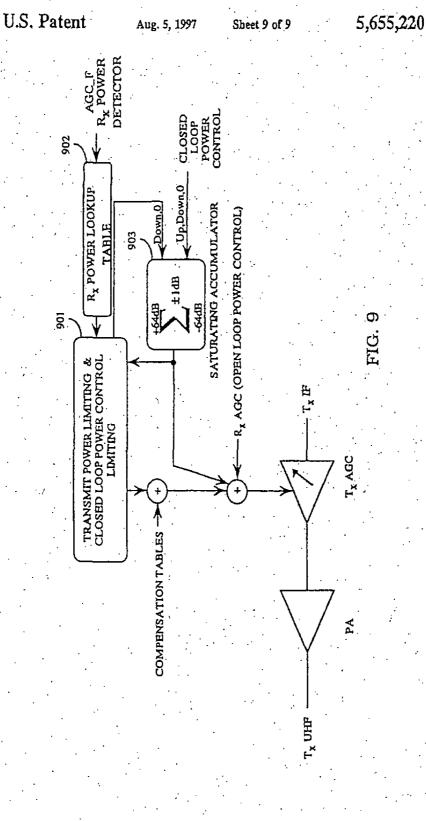

- 13. On August 5, 1997, U.S. Patent No. 5,655,220, entitled "REVERSE LINK, TRANSMIT POWER CORRECTION AND LIMITATION IN A RADIOTELEPHONE SYSTEM," ("the '220 patent") was duly and legally issued to inventors Ana L. Weiland, Richard K. Kornfield, and John E. Maloney. A copy of the '220 patent is attached hereto as Exhibit G.

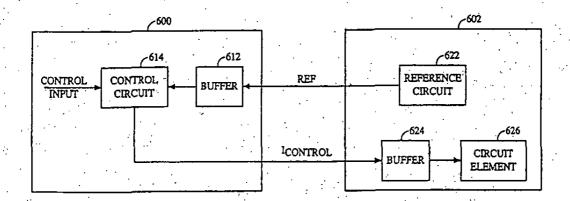

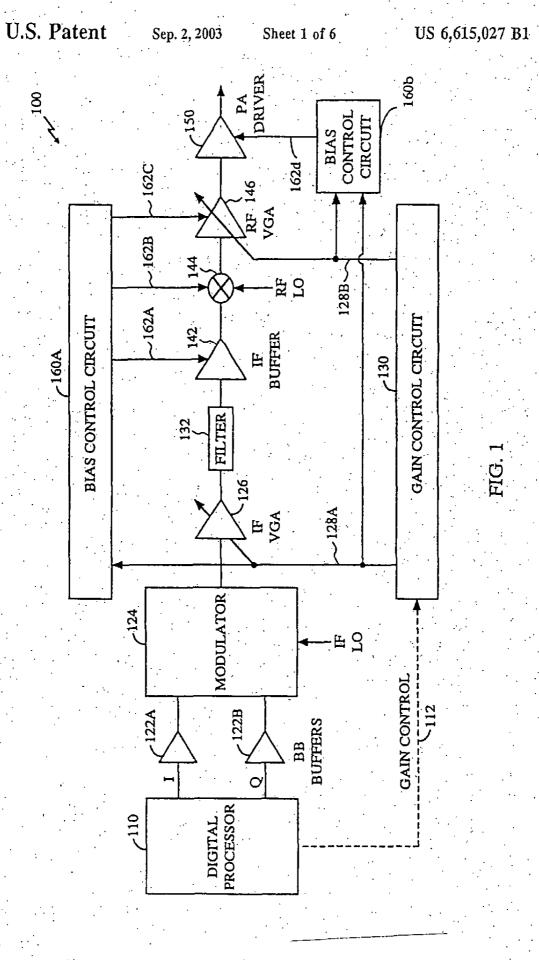

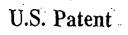

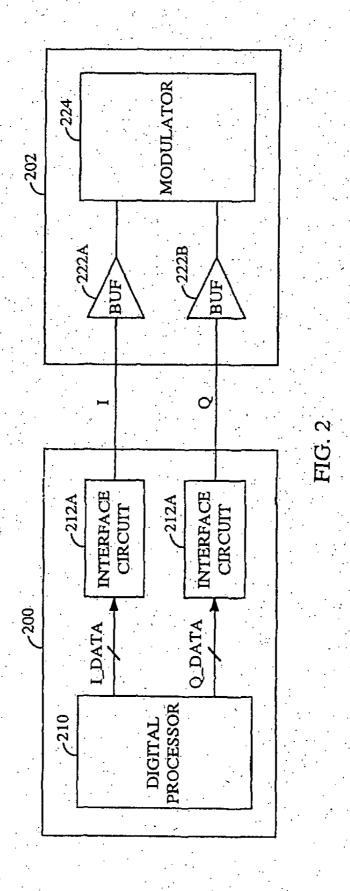

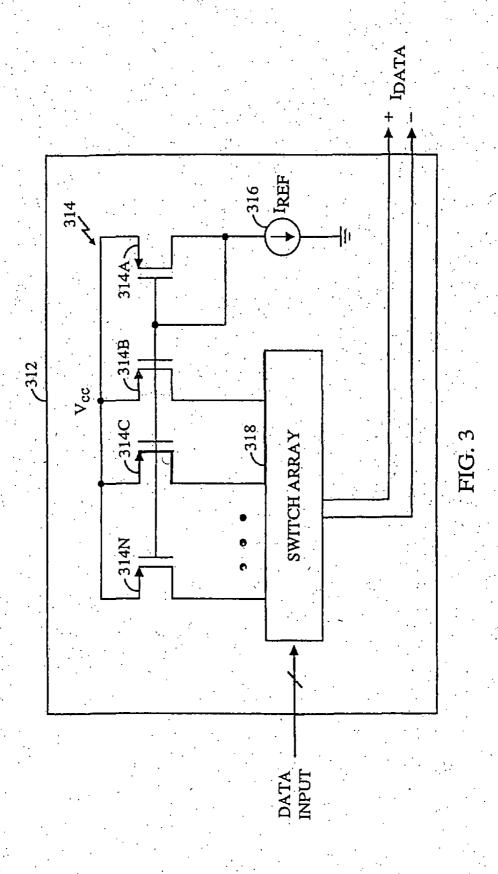

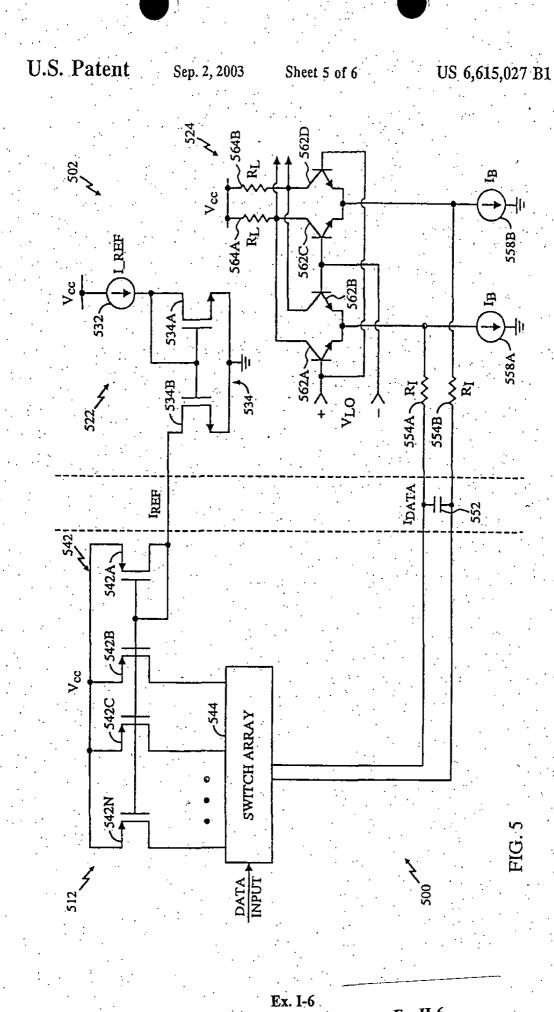

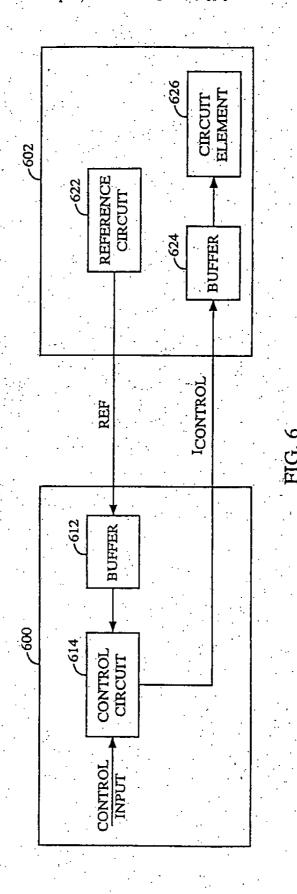

- 14. On September 2, 2003, U.S. Patent No. 6,615,027, entitled "METHOD AND

CIRCUIT FOR PROVIDING INTERFACE SIGNALS BETWEEN INTEGRATED CIRCUITS," ("the '027 patent") was duly and legally issued to inventors Gurkanwal Sahota, Mehdi H. Sani, and Sassan Shahrokhinia. A copy of the '027 patent is attached hereto as Exhibit H.

- 15. QUALCOMM is the owner of the '280, '060, '341, '481, '473, '408, '220, and '027 patents by assignment, with full and exclusive right to bring suit to enforce these patents.

- 16. The '280, '060, '341, '481, '473, '408, '220, and '027 patents relate generally to the transmission, reception and processing of radio signals by wireless telephones.

- 17. On information and belief, Defendants have been and are still infringing, contributing to infringement, and/or inducing others to infringe the '280, '060, '341, '481, '473, '408, '220, and '027 patents by making, using, offering for sale, selling, or importing integrated circuits and modules for use in wireless telephones. Defendants' acts of infringement have occurred within this district and elsewhere throughout the United States.

- 18. On information and belief, Defendants have willfully infringed the '280, '060, '341, '481, '473, '408, '220, and '027 patents by continuing in their acts of infringement after learning of these patents and of their infringement of these patents.

#### MISAPPROPRIATION OF TRADE SECRETS AND BREACH OF CONTRACT

- 19. In early 2000, QUALCOMM began discussions with Conexant regarding a possible joint business relationship between the two companies. As part of these discussions, QUALCOMM and Conexant entered into a written nondisclosure agreement ("the NDA") in July 2000. Under the NDA, QUALCOMM and Conexant agreed that any confidential information disclosed by a party in the course of the discussions would be used by the other party only for the purpose of evaluating the potential joint business relationship. A copy of the NDA is attached hereto as Exhibit I.

- 20. QUALCOMM has at all times complied with its material duties under the terms of the NDA.

- 21. On or about September 6, 2000, representatives from QUALCOMM and Conexant met to discuss the parties' potential joint business relationship. During the course of the meeting, QUALCOMM disclosed certain confidential, proprietary information regarding the design of certain interfaces for certain of its integrated circuits. In particular, QUALCOMM described a new,

optimized interface between the most recent generation of QUALCOMM's Mobile Station Modem ("MSM") and the transmit chain. At the meeting, QUALCOMM identified this information as confidential and proprietary and therefore subject to the terms of the NDA.

- 22. The information regarding the design of the interfaces for QUALCOMM's integrated circuits was not publicly known at that time. QUALCOMM maintained the confidentiality of its integrated circuit interface design by preventing the disclosure of this information to third parties other than disclosure covered by a nondisclosure agreement or disclosure at a later point in time through a published patent application or issued patent.

- 23. QUALCOMM invested substantial amounts of money and resources into the design of its integrated circuit interfaces. The interface design was inventive, and of great commercial importance to QUALCOMM as a trade secret pending any publication of a patent application or issued patent. If competitors learned of the information maintained by QUALCOMM as a trade secret, they could undermine the competitive advantages rightfully belonging to QUALCOMM and unfairly undermine QUALCOMM's position in the market.

- 24. By the end of 2000, QUALCOMM and Conexant decided not to pursue a joint business relationship.

- 25. Around May 2001, QUALCOMM discovered that Conexant was manufacturing and selling integrated circuits based on the interface design information obtained from QUALCOMM in September 2000.

- 26. By using QUALCOMM's design information in this manner, Conexant violated the NDA's requirement that this information be used solely for the purposes of evaluating the parties' potential joint business relationship. QUALCOMM subsequently informed Conexant that it was using QUALCOMM's proprietary and trade secret information in violation of the NDA, and demanded that Conexant cease its unauthorized activities.

- 27. Despite being on notice that it was in violation of the NDA, Conexant continued to manufacture and sell integrated circuits based on QUALCOMM's proprietary interface design.

- 28. On information and belief, Skyworks manufactures and sells integrated circuits based on QUALCOMM's proprietary interface design, and has acquired this design information through

Conexant. As a successor corporation to Conexant, Skyworks knew or reasonably should have known that this design information was proprietary and trade secret information owned by QUALCOMM that should not have been used for commercial purposes under the NDA.

#### **COUNT ONE**

#### (PATENT INFRINGEMENT)

- 29. QUALCOMM repeats and re-alleges the allegations of paragraphs 1 through 28 above as if fully set forth herein.

- 30. In violation of 35 U.S.C. § 271, Defendants have infringed and are continuing to infringe, literally and/or under the doctrine of equivalents, the '280, '060, '341, '481, '473, '408, '220, and '027 patents by practicing one or more claims of each of the '280, '060, '341, '481, '473, '408, '220, and '027 patents in their manufacture, use, offering for sale, sale, and/or importation of integrated circuits and modules for use in wireless telephones, and/or by inducing or contributing to the infringement of the '280, '060, '341, '481, '473, '408, '220, and '027 patents by others.

- 31. QUALCOMM has been damaged by Defendants' infringement and, unless Defendants secure a license to the '280, '060, '341, '481, '473, '408, '220, and '027 patents from QUALCOMM or are enjoined by this Court, Defendants will continue their infringing activity and QUALCOMM will continue to be damaged.

#### **COUNT TWO**

#### (MISAPPROPRIATION OF TRADE SECRETS)

- 32. QUALCOMM repeats and re-alleges the allegations of paragraphs 1 through 28 above as if fully set forth herein.

- 33. QUALCOMM adopted reasonable measures as described herein to maintain the secrecy of the interface design at issue.

- 34. QUALCOMM has invested substantial amounts of money and resources in the development of the interface design for its integrated circuits. The interface design is of great commercial importance to QUALCOMM.

- 35. Defendants knew or should have known when they manufactured and sold products incorporating QUALCOMM's proprietary interface design that they were misusing confidential,

proprietary trade secret information belonging to QUALCOMM.

- 36. Defendants' manufacture and sale of products incorporating QUALCOMM's proprietary interface design with full knowledge of their duty not to make commercial use of that information constitutes misappropriation of QUALCOMM's trade secrets under California Civil Code § 3426 et seq.

- 37. Defendants' misappropriation of QUALCOMM's trade secrets was willful and malicious.

- 38. QUALCOMM has been damaged by Defendants' misappropriation of its trade secrets and, unless Defendants are enjoined by this Court, Defendants will continue their misappropriation of QUALCOMM's trade secrets by continuing to manufacture and sell products incorporating QUALCOMM's proprietary interface design.

#### COUNT THREE

#### (BREACH OF CONTRACT)

- 39. QUALCOMM repeats and re-alleges the allegations of paragraphs 1 through 28 and 32 through 38 above as if fully set forth herein.

- 40. In default of its obligations under the NDA, defendant Conexant has used confidential, proprietary trade secret information belonging to QUALCOMM and covered by the NDA for purposes other than evaluating the possibility of a joint business relationship between QUALCOMM and Conexant.

- 41. QUALCOMM has performed all of its material obligations under the NDA.

- 42. QUALCOMM has been damaged as a result of Conexant's breach of the NDA and, unless Conexant is enjoined by this Court, Conexant will continue to breach the NDA by continuing to manufacture and sell products incorporating QUALCOMM's proprietary interface design.

#### PRAYER FOR RELIEF

WHEREFORE, plaintiff QUALCOMM prays for the following relief against Defendants:

(a) A preliminary and permanent injunction against Defendants, their officers, agents, servants, employees, attorneys, all parent and subsidiary corporations, all assignees and successors in interest, and those persons in active concert or participation with Defendants, including distributors

- (b) An award of damages under 35 U.S.C. § 284 for Defendants' infringement of QUALCOMM's '280, '060, '341, '481, '473, '408, '220, and '027 patents, including damages based on lost profits, lost royalties, and price erosion, together with pre-judgment and post-judgment interest;

- (c) A trebling of said damages pursuant to 35 U.S.C. § 284;

- (d) An award of attorneys' fees pursuant to 35 U.S.C. § 285;

- (e) An injunction against Defendants, their officers, agents, servants, employees, attorneys, all parent and subsidiary corporations, all assignees and successors in interest, and those persons in active concert or participation with Defendants, enjoining them from manufacturing or selling products incorporating QUALCOMM's proprietary integrated circuit interface design;

- (f) An award of damages for Defendants' misappropriation of QUALCOMM's trade secrets, together with pre-judgment and post-judgment interest;

- (g) A doubling of such damages pursuant to Cal. Civ. Code § 3426.3(c);

- (h) An award of recovery of Defendants' unjust enrichment pursuant to Cal. Civ. Code § 3426.3(a);

- (i) An award of attorneys' fees for Defendants' misappropriation of QUALCOMM's trade secrets pursuant to Cal. Civ. Code § 3426.4;

- (j) An award of damages for defendant Conexant's breach of the NDA, together with pre-judgment and post-judgment interest;

///

///

///

///

///

///

///

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

23

24

25

26

27

- (k) An award of attorneys' fees for defendant Conexant's breach of the NDA, pursuant to section 12 of the NDA;

- (l) Any such other relief that this Court deems just and proper.

Dated: June 9, 2004

DAY CASEBEER MADRID & BATCHELDER LLP

James R. Batchelder

Attorneys for Plaintiff and Counterdefendant QUALCOMM Incorporated

### **DEMAND FOR JURY TRIAL**

Pursuant to Rule 38 of the Federal Rules of Civil Procedure, QUALCOMM demands a trial by jury on all issues triable of right by a jury.

Dated: June 1, 2004

DAY CASEBEER MADRID & BATCHELDER LLP

James R. Batchelder

Attorneys for Plaintiff and Counterdefendant QUALCOMM Incorporated

:

.

## United States Patent [19]

Wilson et al.

[11] Patent Number:

5,499,280

[45] Date of Patent:

Mar. 12, 1996

| [54] | CLOCK | SIGNAL | GENERATION |

|------|-------|--------|------------|

|------|-------|--------|------------|

[75] Inventors: Nathaniel B. Wilson, San Diego; Gene H. McAllister, La Mesa, both of Calif.

[73] Assignce: QUALCOMM Incorporated, San Diego, Calif.

[21] Appl. No.: 382,770

[22] Filed: Feb. 2, 1995

[51] Int. Cl.<sup>d</sup> \_\_\_\_\_ H03K 23/48

[52] U.S. Cl. 377/108; 377/48; 327/115 [58] Field of Search 377/48, 108; 327/115.

[58] Field of Search \_\_\_\_\_\_377/48, 108; 327/115; 327/160

[56] References Cited

#### U.S. PATENT DOCUMENTS

|   | 4,573,176 | 2/1986  | Yeager Baca | . 377/48 |

|---|-----------|---------|-------------|----------|

|   | 4,942,595 | 7/1990  | Baca        | . 377/48 |

|   | 5,077,764 | 12/1991 | Yamashita   | . 377/48 |

| , | 5.365.119 | 11/1994 | Kiyari      | 327/115  |

Primary Examiner—John S. Heyman

Attorney, Agent, or Firm—Russell B. Miller, Roger W.

Manin

#### [57] ABSTRACT

The clock signal generator of the present invention divides a higher frequency clock down to a frequency that is an uneven sub-multiple of the higher frequency. The input clock to be divided down clocks an 11-bit counter (105-110) that outputs an overflow signal to a D flip-flop (125). The D flip-flop generates a load signal that resets the counter after 1025 clock periods. The load signal also suppresses, after 1025 clock periods, the toggling of another toggle flip-flop (120) that provides a divide by two clock. By suppressing a clock pulse in the divide by two clock, every 1025 clock pulses of the higher frequency clock, the average clock frequency of the divide by two clock is reduced to an uneven sub-multiple of the higher clock frequency.

12 Claims, 3 Drawing Sheets

5,499,280

Ex. A-2

Ex. A-2

U.S. Patent

Mar. 12, 1996 Sheet 3 of 3

5,499,280

| CLOCK OSCILLATOR FREQ.   | M/N FOR 9.8304 MHz |

|--------------------------|--------------------|

| 9.84 MHz (2 x 4.92 MHz)  | 1/1                |

| 14.76 MHz (3 x 4.92 MHz) | 2/3                |

| 19.68 MHz (4 x 4.92 MHz) | 1/2                |

| 24.6 MHz (5 × 4.92 MHz)  | 2/5                |

| 29.52 MHz (6 x 4.92 MHz) | 1/3                |

|                          |                    |

FIG. 5

5,499,280

1

#### CLOCK SIGNAL GENERATION

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to clock signals. More particularly, the present invention relates to the generation of a clock signal.

#### 2. Description of the Related Art

Cellular radiotelephones are rapidly decreasing in size and cost. In order to accomplish these reductions, the number of parts contained in a radiotelephone are reduced. This reduces the cost of the total number of radiotelephone parts, the manufacturing costs and also reduces the weight of the unit. In order to continue these reductions in cost and weight, the radiotelephone parts count must be reduced further.

Radiotelephones require multiple clock frequencies to operate due to the different requirements of circuits within the radiotelephone. For example, a microprocessor may use a different clock than the RF circuits. Some of these clock frequencies are obtained by dividing one clock signal into sub-multiples of that frequency. This technique reduces the number of oscillators needed to generate the various clock signals.

In a code division multiple access radiotelephone, a master clock frequency of eight times the chip rate of 1.2288 MHz is used for various digital circuits. For cellular use, this frequency, 9.8304 MHz, or its double of 19.6608 MHz, are 30 not suitable master frequencies for the RF components of the radiotelephone since neither is an even multiple of the 30 kHz RF channel spacing required for cellular radio in the United States.

In this case, multiple oscillators are needed to generate the 35 different clock signals required by both the digital hardware and the RF circuitry. There is a resulting need for a clock generator that can produce a clock frequency that is an uneven multiple of another frequency, thus reducing the number of clock synthesizers required.

#### SUMMARY OF THE INVENTION

The clock generator of the present invention generates a clock signal having a frequency that is an uneven submultiple of a higher frequency input clock signal. The clock generator is comprised of a counter that is clocked by the input clock signal. The counter generates a count overflow indication in response to a predetermined number of input clock signal pulses. A data latch is coupled to the count overflow indication. The input clock signal latches the count overflow indication into the data latch, thus generating a load signal. A toggle flip-flop is coupled to the input clock signal and the load signal. The toggle flip-flop divides down the input clock signal to a lower frequency while the load signal adjusts this lower frequency to the frequency that is an uneven submultiple of the frequency of the input clock signal.

#### BRIEF DESCRIPTION OF THE DRAWINGS

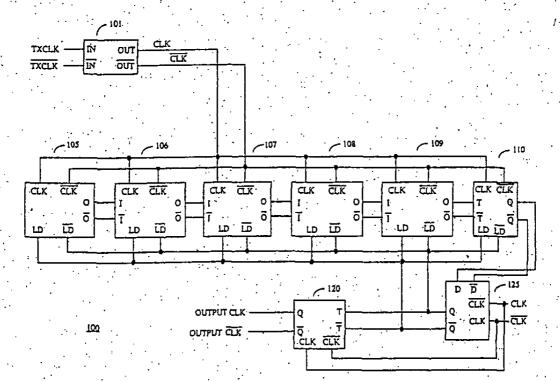

FIG. 1 shows a circuit diagram of the preferred embodiment of the clock generator of the present invention.

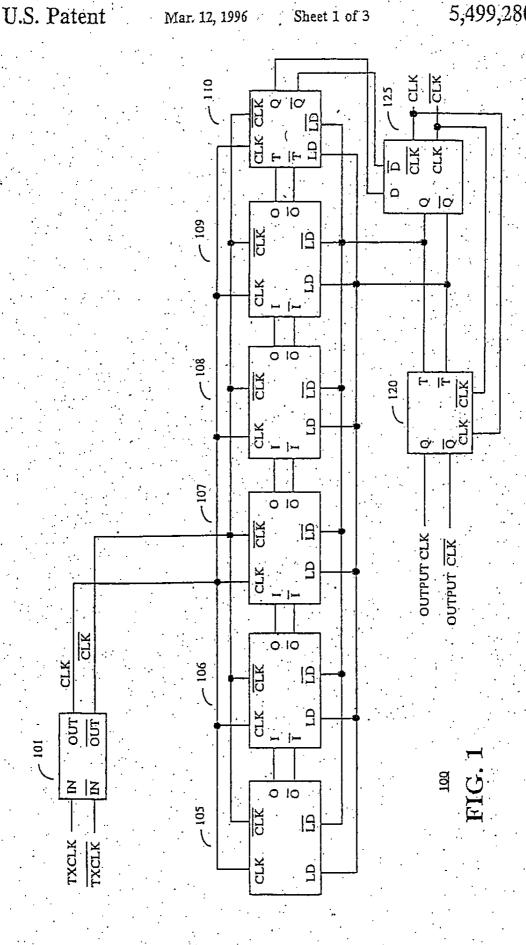

FIG. 2 shows a timing diagram in accordance with the clock generator of FIG. 1.

FIG. 3 shows a block diagram of a clock generation circuit incorporating the clock generator of FIG. 1.

2

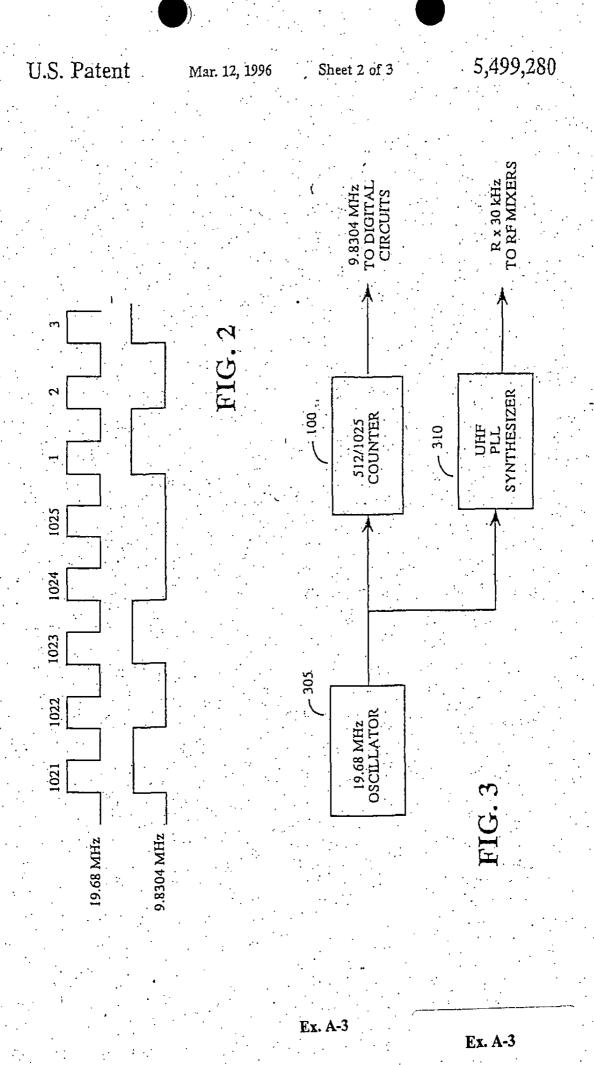

FIG. 4 shows a block diagram of the clock generator of the present invention.

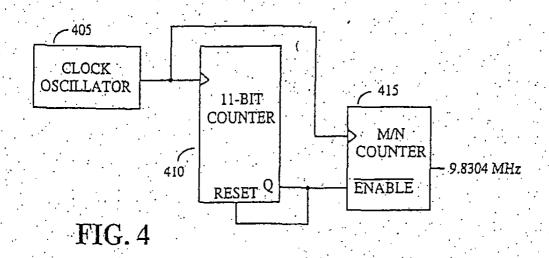

FIG. 5 shows a table of clock oscillator frequencies and divide ratios in accordance with the block diagram of FIG.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

The clock generator of the present invention divides a higher frequency clock signal down to an uneven multiple; lower frequency clock signal. In the preferred embodiment, the clock generator provides an output to input ratio of \$12/1025. The clock generator thus eliminates the need for an analog synthesizer to generate the lower clock frequency.

The clock generator of the present invention is illustrated in FIG. 4. The clock generator is comprised of a clock oscillator (405) that generates an input clock signal for an 11-bit counter (410) and an  $^{M}/_{N}$  counter (415). The divide ratio of the  $^{M}/_{N}$  counter (415) is different for alternate embodiments to accommodate different input clock signal frequencies. The divide ratio is changed by implementing the  $^{M}/_{N}$  counter (415) in different ways. The 11-bit counter (410) enables and disables the M/N counter (415), thus altering the average frequency of the clock signal output from the  $^{M}/_{N}$  counter.

In the preferred embodiment, the input clock is a multiple of 4.92 MHz. 19.68 MHz (4x4.92 MHz=656x30 kHz) and 24.6 MHz (5x4.92 MHz =820x25 kHz) are particularly convenient values. In CDMA cellular telephones with a spread spectrum chip rate of 1.2288 MHz, this selection of the input clock is especially advantageous.

An input clock that is an even multiple of 30 kHz is required for the RF phase locked loop synthesizer in phones for U.S. cellular (or a multiple of 25 kHz for some countries). 4.92 MHz is the closest multiple of 30 kHz that is greater than 4×1.2288 MHz. For this reason, the telephone can use analog to digital converters (ADC) and digital to analog converters (DAC) that are clocked by the generator of the present invention, without a significant performance penalty due to the resulting clock jitter.

For example, for the case of an input clock of 19.68 MHz and a signal bandwidth of 614 kHz being clocked out of a DAC, the clock jitter results in about -25dBc of in-band noise being added to the DAC's output spectrum. However, the out of band noise (at greater than 750 kHz) is down below -40 dBc. Both the in-band and out of band noise is acceptable for spread spectrum cellular. If an input clock such as 19.8 MHz, which is farther from a multiple of 4.92 MHz, was selected to drive the M/N counter for the DAC's, the out of band noise that results from the clock jitter would be unacceptably large.

The table of FIG. 5 illustrates some possible clock oscillator frequencies and the respective dividing ratios for the  $M_N$  counter to generate the desired 9.8304 MHz signal. The preferred embodiment of the clock generator uses a 19.68 MHz clock frequency with a dividing ratio of  $M_N$ .

The preferred embodiment of the clock generator of the present invention is illustrated in FIG. 1. This embodiment is comprised of five 2-bit counters (105-109) and a 1-bit counter (110) connected in a 6 stage configuration. These counters taken together form the 11-bit counter (410) of FIG. 4. In the preferred embodiment, the 1-bit counter (110) is a toggle flip-flop.

The counters each have count overflow outputs that become true when the counter overflows from the logical

The count overflow output and the inverse count overflow output of one stage (105) are coupled to the count input and inverse count input, respectively, of the next counter stage (106). These outputs cause the clock pulse count to ripple through, the 5 counters. The count overflow output and inverse count overflow output of the last 2-bit counter stage (109) is input to the toggle and inverse toggle inputs of the flow flow output as a 1-bit counter.

The input clock signal, from the clock oscillator, is input to a clock driver (101) that increases the drive current of the clock. The clock driver (101) increases the number of gates that the clock signal can drive. In the preferred embodiment, the clock signal is comprised of a clock and an inverse clock.

The counters (105-110) are clocked by the clock signal from the clock driver (101). The clock and the inverse clock are input to the counters respective clock and inverse clock inputs. In the preferred embodiment, the counters (105-110) increment on the rising edge of the clock pulse and the falling edge of the clock pulse.

The most significant bit from the final stage of the counter (110); goes true on the 1024th input clock cycle. This bit is quitput ties D flip-flop (125) where it is latched in by the inverse input clock signal to generate a latched load signal.

The latched load signal is used to load logical O's into the counter. This effectively resets the counter to zero so that the count begins from there. The load occurs on the 1025 input 30 clock cycle. In the preferred embodiment, the load signal is comprised of a load and inverse load signal.

The output clock signal, 9.8304; MHz in the preferred embodiment, is generated by a divide-by-two toggle flip-flop (120) that serves as the "h, counter (415) from FIG. 4, 35 The latched load and inverse load signals are input to the toggle inputs of the flip-flop (120). The clock and inverse clock signals are input to the respective clock inputs of the flip-flop (120). When the latched load signals are false, the toggle flip-flop (120) changes state on the rising edge of the 40 clock signal pulses. This toggling divides the clock signal by

The divide by two state exists for 1024 input clock periods; producing 512 output clock pulses. During the 1025 input clock period, the load signal disables the toggle input forcing the flop-flop (120) to hold its current state. The toggle flip flop (120); therefore, produces 512 clock periods for each 1025 input clock periods.

The output clock does not have a constant cycle time. The long term average frequency (or the average over \$12 cycles) is 9.8304 MHz. The resulting litter is within tolerable limits for the preferred embodiment of a cellular radiotelephone. The divided down clock also benefits from low spectral noise;

FIG. 2 illustrates, a timing diagram of the higher frequency input clock signal in comparison to the output clock signal.

It can be seen that the output clock toggles on the leading edge of each input clock pulse. This continues until the 1025th clock pulse where the divide by two toggle flip-flop 60 is disabled by the load signal.

FIG. 3 illustrates a typical cellular radiotelephone application for the clock generator of the present invention. This clock generation circuit uses a 19:68 MHz oscillator (305) to generate the input clock signal. The clock generator (100) of 65 the present invention then produces the 9.8304 MHz clock. A phase locked loop synthesizer (310) generates another 4 :

clock having a higher frequency that is an integer multiple, R, of 30 kHz. This clock, in the preferred embodiment, is used by the RF mixers of the radio.

As is evident from FIG. 5, additional embodiments of the clock generator, of the present invention can use different input clock signals to generate the 9.8304 MHz output clock. These alternate embodiments implement the My counter in different ways to generate the output clock:

A first alternate embodiment generates the output clock signal using an input clock signal of 9:84 MHz (2x4.92 MHz). In this embodiment, the M/x counter is an asynchrounous clock gating circuit.

A second embodiment generates the output clock signal using an input clock signal having a frequency of 14.76. MHz (3x4.92 MHz). In this embodiment, a 2-bit state machine with asynchronous clock gating is used as the 4%, counter.

A third embodiment generates the output clock signal using an input clock signal having a frequency of 24.6 MHz (5x4.92 MHz). This embodiment uses a 3-bit state machine as the M/2 counter.

A fourth embodiment generates the output clock signalusing an input clock signal having a frequency of 29.52 MHz (6x4.92 MHz). This embodiment uses a 2-bit state machine as the M<sub>N</sub> counter.

Other embodiments of the clock generator of the present invention can be implemented using other types of Marcounters. The embodiments presented above are only a narrow sampling of such embodiments.

The preferred embodiment of the present invention also uses both a signal and an inverse of the signal. Alternate embodiments may use only the signal, and not the inverse signal, depending on the technology in which the present invention is implemented; i.e., CMOS, bipolar, etc.

As can be seen above, the clock generator of the present invention generates an uneven multiple, clock frequency without additional analog frequency synthesizers, thus saving cost and weight in an electronic device. Without the clock generator of the present invention, additional phase locked loop synthesizers would be required.

We claim:

- 1. A clock generator for generating an output clock signal baving a first frequency from an input clock signal having a second frequency, the first frequency being an uneven submultiple of the second frequency, the clock generator comprising:

- a counter having a clock input coupled to the input clock signal and a reset input coupled to a latched load signal, the counter generating a count overflow indication in response to a predetermined number of input clock signal pulses and resetting in response to the latched load signal.

- a data latch having an input coupled to the count overflow indication, the data latch generating the latched load signal in response to the input clock signal and the count overflow indication; and

- a toggle flip-flop having a first input coupled to the input clock signal and a second input coupled to the latched load signal, the toggle flip-flop generating the output clock signal in response to the latched load signal and the input clock signal

- 2. The clock generator of claim I wherein said counter further comprises:

- a plurality of 2 bit counters each having an input coupled to the input clock signal, the plurality of 2 bit counters.

each generating a 2-bit count overflow indication, each 2-bit count overflow indication being coupled to a next stage 2-bit counter of the plurality of 2-bit counters, a final stage 2-bit counter of the plurality of 2-bit counters generating a final stage 2-bit count overflow 5 indication; and

a 1-bit counter having a first input coupled to the final stage 2-bit count overflow indication and a second input coupled to the input clock signal.

3. The clock generator of claim 2 wherein said data latch 10

is a D flip-flop.

- 4. A clock generator for generating an output clock signal having a first frequency from an input clock signal having a second frequency, the first frequency being an uneven submultiple of the second frequency, the clock generator comparing:

- a plurality of counters each having a clock input coupled to the input clock signal and each having a reset input coupled to a latched load signal, the plurality of counters each generating a count overflow indication 20 and each resetting in response to the latched load signal, each count overflow indication being coupled to a next stage counter of the plurality of counters, a final stage counter of the plurality of counters generating a predetermined maximum count indication;

- a D flip-flop having a first input coupled to the predetermined maximum count indication and a second input coupled to the input clock signal, the D flip-flop generating the latched load signal in response to the predetermined maximum count indication and the input 30 clock signal; and

- a toggle flip-flop having a first input coupled to the input clock signal and a second input coupled to the latched load signal, the toggle flip-flop generating the output clock signal in response to the latched load signal and 35 the input clock signal.

- 5. A clock generator for generating an output clock signal having a first frequency from an input clock signal having a second frequency, the first frequency being an uneven submultiple of the second frequency, the clock generator comprising:

- a plurality of 2-bit counters each having an input coupled to the input clock signal, the plurality of 2-bit counters each generating a count overflow indication, each count overflow indication being coupled to a next stage counter of the plurality of 2-bit counters, a final stage 2-bit counter of the plurality of counters generating a 2-bit count overflow indication;

- h first toggle flip-flop having a first input coupled to the 2-bit count overflow indication and a second input coupled to the input clock signal, the first toggle flip-flop generating a predetermined maximum count indication;

- a D flip-flop having a first input coupled to the predetermined maximum count indication and a second input coupled to the input clock signal, the D flip-flop generating a latched load signal in response to the predetermined maximum count indication and the input clock signal; and

- a second toggle flip-flop having a first input coupled to the input clock signal and a second input coupled to the latched load signal, the second toggle flip-flop generating the output clock signal in response to the latched load signal and the input clock signal.

- 6. A method for generating an output clock signal having a first frequency from an input clock signal having a second

frequency in a circuit having a counter, the first frequency being an uneven sub-multiple of the second frequency, the method comprising the steps of:

- generating by the counter a maximum count indication after a predetermined number of clock pulses of the input clock signal;

- generating a latched load signal in response to the maximum count indication and the input clock signal;

- generating the output clock signal, when the latched load signal is false, in response to the input clock signal;

- disabling the output clock signal when the latched load signal is true; and

resetting the counter when the latched load signal is true.

7. A clock generation circuit for generating a first clock signal having a first frequency and a second clock signal having a first frequency and a second clock signal having a first frequency and a second clock signal having a first frequency and a second clock signal having a first frequency and a second clock signal having a first frequency and a second clock signal in the second clock

signal having a first frequency and a second clock signal having a second frequency both from an input clock signal having a third frequency, the first frequency being an uneven sub-multiple of the third frequency, the clock generator comprising:

- an oscillator for generating the input clock signal having the third frequency of N×4.92 MHz;

- a clock generator for generating the first clock signal, the clock generator having an output to input ratio of (1024/1025)×(2/N), the clock generator comprising:

- a counter having a clock input coupled to the input clock signal

- and a reset input coupled to a latched load signal, the counter generating a count overflow indication in response to a predetermined number of input clock signal pulses and resetting in response to the latched load signal:

- a data latch having an input coupled to the count overflow indication, the data latch generating the latched load signal in response to the input clock signal and the count overflow indication; and

- a toggle flip-flop having a first input coupled to the input clock signal and a second input coupled to the latched load signal, the toggle flip-flop generating the output clock signal in response to the latched load signal and the input clock signal; and a phase locked loop synthesizer for generating the second clock signal.

- 8. The clock generation circuit of claim 7 wherein N is an integer and N≥2.

- 9. The clock generator of claim 7 wherein said counter further comprises:

- a plurality of 2-bit counters each having an input coupled to the input clock signal, the plurality of 2-bit counters each generating a 2-bit count overflow indication, each 2-bit count overflow indication being coupled to a next stage 2-bit counter of the plurality of 2-bit counters, a final stage 2-bit counter of the plurality of 2-bit counters generating a final stage 2-bit count overflow indication; and

- a 1-bit counter having a first input coupled to the final stage 2-bit count overflow indication and a second input coupled to the input clock signal.

10. The clock generator of claim 9 wherein said data latch is a D flip-flop.

11. A clock generator for generating an output clock signal having a first frequency from an input clock signal having a second frequency, the first frequency being an uneven submultiple of the second frequency, the clock generator comprising:

5,499,280

a first counter having a clock input coupled to the input clock signal and a reset input coupled to a count overflow indication, the counter generating the count overflow indication in response to a predetermined number of input clock signal pulses, the first counter being reset by the count overflow indication; and a second counter having a first angut coupled to the input clock signal and a second input coupled to the count overflow indication; the second counter generating the dutput clock signal from the input clock signal and 10 modifying the dutput clock, signal and 10 count overflow indication.

12. The clock generator of claim 11 wherein said first counter further comprises:

- a plurality of 2-bit counters each having an input coupled to the input clock signal, the plurality of 2-bit counters each generating a 2-bit count overflow indication, each 2-bit count overflow indication being coupled to a next stage 2-bit counter of the plurality of 2-bit counters, a final stage 2-bit counter of the plurality of 2-bit counters generating a final stage 2-bit counter of the plurality of 2-bit counters generating a final stage 2-bit count overflow indication, and

Ex. A-8

Ex. A-8

# US005617060A

## United States Patent [19]

Wilson et al.

[11] Patent Number:

5,617,060

[45] Date of Patent:

Apr. 1, 1997

[54] METHOD AND APPARATUS FOR

AUTOMATIC GAIN CONTROL AND DC

OFFSET CANCELLATION IN QUADRATURE

RECEIVER

[75] Inventors: Nathaniel B. Wilson, San Diego, Calif.; Peter J. Black, St. Lucia, Australia; Paul E. Peterzell, San Diego, Calif.

[73] Assignee: QUALCOMM Incorporated, San Diego, Calif.

[21] Appl. No.: 423,332

[22] Filed: Apr. 13, 1995

#### Related U.S. Application Data

| [63] Continuati              | ion of Ser. No. 235,812, | Apr. 28 | , 199 | 4, abandon   | ed |

|------------------------------|--------------------------|---------|-------|--------------|----|

| [51] - Int. Cl. <sup>6</sup> |                          | ,<br>   | , '   | H03G 3/      | 20 |

| - 11.15                      |                          |         | _ :   | . : <b>_</b> |    |

[56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,653,117 | 3/1987 | Heck                    | /209 |

|-----------|--------|-------------------------|------|

| 4,944,025 | 7/1990 | Gehring et al 455       | /207 |

|           |        | Wheatley, III et al 330 |      |

|           |        | Weiland et al 330/12    |      |

#### FOREIGN PATENT DOCUMENTS

| 0305603 | 9/1987  | European Pat. Off H03D 1/22 |  |

|---------|---------|-----------------------------|--|

| 0482927 | 10/1991 | European Pat. Off H04B 1/30 |  |

Primary Examiner—Steven Mottola

Attorney, Agent, or Firm—Russell B. Miller, Roger W. Martin

57] ABSTRACT

An automatic gain control (AGC) and D.C. offset correction method and apparatus for controlling signal power of a received RF signal within a dual mode quadrature receiver is disclosed herein. In a preferred implementation the automatic gain control apparatus may be adjusted to provide a desired control response to various fading characteristics of a received FM, FSK, GMSK, QPSK, or BPSK signal. The AGC apparatus includes an adjustable gain amplifier having an input port for receiving an input signal, a control port for receiving a gain control signal, and an output port for providing an output signal. A quadrature downconverter coupled to the output port serves to translate the frequency of the output signal to a baseband frequency, thereby producing baseband signals. In a preferred implementation the downconverter is operative to map the carrier frequency of the output signal to a baseband frequency offset by a predetermined margin from D.C. Two high gain active lowpass filters provide out-of-band signal rejection for the baseband signals. A D.C. feedthrough suppression loop, disposed to receive said baseband signal, suppresses D.C. offsets produced by the downconverter and lowpass filters, hence providing a compensated baseband signal. The AGC apparatus is further disposed to generate a received power signal based on the power of the output signal. A saturating integrator compares the received power signal to a reference signal and produces the gain control signal by integrating or by refraining from integration based on values of the reference, received power signal, and gain control signals, thereby extending the usable dynamic range of the receiver for FM mode.

#### 21 Claims, 10 Drawing Sheets

Ex. B-2

U.S. Patent

Apr. 1, 1997

Sheet 2 of 10

5,617,060

FIG. 2

Ex. B-3

Ex. B-3

Ex. B-4.

Ex. B-4

U.S. Patent Apr. 1, 1997

Sheet 4 of 10

5,617,060

FIG. 4A

FIG. 4B

Ex. B-5

Ex. B-5

FIG. 5

Ex. B-6

Ex. B-7

Ex. B-8

Ex. B-8

U.S. Patent Apr. 1, 1997 Sheet 8 of 10 5,617,060

FIG. 8

Ex. B-9

Ex. B-9

Ex. B-10

U.S. Patent Apr. 1, 1997 Sheet 10 of 10

5,617,060

Ex. B-11

Ex. B-11

5,617,060

1

METHOD AND APPARATUS FOR AUTOMATIC GAIN CONTROL AND DC OFFSET CANCELLATION IN QUADRATURE RECEIVER

This is a Continuation of application Ser. No. 08/235, 812, filed Apr. 28, 1994 now abandoned.

#### BACKGROUND OF THE INVENTION

I. Field of the Invention

The present invention relates generally to RF receivers using quadrature demodulation. More particularly, the present invention relates to a novel method and apparatus for providing automatic gain control, out-of-band signal rejection, and D.C. offset cancellation within a digital receiver.

II. Description of the Related Art

In analog receivers, such as are used in narrowband FM cellular communication systems, FM demodulators are 20 employed to extract information encoded in the phase of an incident waveform. Existing FM demodulators often include an analog frequency discriminator preceded by an analog limiter, with the limiter serving to constrain the input signal power to a constant level. In this way maximum signal to 25 noise ratio is maintained at the input to the frequency discriminator over the full dynamic range of the FM input signal. However, such an analog signal processing technique generally involves extensive signal filtening, and frequently is implemented using a large number of discrete components. Moreover, it has been demonstrated that improved performance may be achieved using linear digital waveform demodulation rather than analog demodulation. Unfortunately, conventional demodulation techniques are often not applicable to digital receivers, since clipping of the received signal would result in corruption of the data derived therefrom.

A digital receiver for receiving a digitally modulated information signal will generally include a variable gain . amplifier with a gain adjusted by a control signal. The 40 process of adjusting the gain of a received signal using a control signal is called Automatic Gain Control (AGC). Typically in digital receivers, the AGC process involves measurement of an output signal power of the variable gain amplifier. The measured value is compared with a value 45 representing the desired signal power and an control signal for the variable gain amplifier is generated. The error value is then used to control amplifier gain so as to adjust the signal strength to coincide with the desired signal power. To effect digital demodulation with an optimal signal to aoise 50 ratio, automatic gain control is used to hold the magnitude of the baseband waveforms dose to the full dynamic range of the baseband analog to digital converters. This generally requires, however, that automatic gain control be provided over the full dynamic range of the received signal power. 55

In the cellular environment, a digital receiver may receive a signal which experiences rapid and-wide variations in signal power. In digital receivers such as are used in a code division multiple access (CDMA) and Time Division Multiple Access (TDMA) mobile cellular telephone, it is necessary to control the power of the demodulated signal for proper signal processing. However, in digital receivers to be both CDMA or TDMA compatible and conventional FM compatible, i.e., dual-mode digital/FM receivers, it is necessary to provide power control of both wideband CDMA 65 (or TDMA) signals and narrowband FM signals. The control process is complicated by the differing dynamic ranges

2

associated with the received FM and CDMA signal power. That is, the magnitude of received FM signals may vary over a dynamic range greater than 100 dB, whereas CDMA systems typically result in a more limited dynamic range, i.e., approximately 80 dB.

The provision of separate AGC circuitry for each mode increases the hardware complexity and expense of such receivers. Accordingly, it would be desirable to provide AGC circuitry capable of operating both upon narrowband, wide-dynamic range FM signals, as well as upon wideband CDMA signals of more limited dynamic range.

It would also be desirable to provide digital AGC in inexpensive receivers utilizing analog to digital (A/D) converters with limited dynamic range. Again, because FM signals within cellular systems may vary more than 100 dB and relatively inexpensive 8-bit A/D's are limited to a dynamic range of approximately 48 dB, a cost effective AGC implementation should be capable of controlling the gain of the portion of the receiver preceding the A/D converters so as to control the signal's dynamic range at the A/D converter. The alternative is to employ expensive A/D converters having greater dynamic range, thereby increasing the cost of the receiver or to increase the AGC range of the analog portion of the radio which is very difficult and costly.

It is therefore an object of the present invention to provide a povel and improved AGC circuit which incorporates the desirable features mentioned above, and which, as is described hereinafter, also realizes certain other advantages relative to conventional AGC techniques.

In standard FM cellular telephones, the AGC function is performed by a circuit called a limiter. When a limiter is used, out-of-band signal rejection can only be done using intermediate frequency (IF) filters. Although the requisite signal rejection capability may be achieved through the use of ceramic IF filters, these tend to be relatively large and expensive. Smaller and less expensive IF filters are generally incapable of being realized so as to possess the desired signal rejection characteristics, and hence are generally not employed in FM cellular telephone receivers.

As is well known, recent advances in integrated circuit (IC) technology have made possible the realization of active baseband filters which are quite small and inexpensive compared to IF filters. It follows that it would be desirable to employ active IC baseband filters to effect significant out-of-band signal suppression, thereby allowing smaller and less expensive IF filters to be used to provide any additional required signal rejection. In an active filter, the higher the gain—the better rejection that is possible. But the higher the gain, the more susceptible the system to unwanted D.C. offsets. Suppression of such D.C. offsets is desirable to maximize the available signal dynamic range, minimize offset induced distortion in the baseband demodulated signal and minimize offset induced errors in baseband signal strength estimates.

In standard digital communications systems such as quadrature phase shift keying (QPSK), used in standard CDMA communication systems (and some TDMA systems), or binary phase shift keying (BPSK), information from the waveform is recovered by downconversion of the signal to baseband frequency centered about D.C. In this case D.C. offsets are easily removed, since for QPSK and BPSK, the carrier is generally suppressed by the transmitter anyway. Hence at baseband, a D.C. notch can be used.

However, for constant amplitude modulations such as FM and continuous phase FSK (which are used in FM cellular telephone systems such as AMPS) and Gaussian Minimum

Shift Keying (GMSK) (used in some TDMA systems), the carrier must be preserved in order to demodulate the received signal.

The employment of active baseband IC filters leads to the necessity of providing some mechanism for suppression of undesired D.C. offsets. The IF processing chain of conventional digital cellular telephone receivers typically includes a local oscillator (L.O.) having a frequency selected such that the carrier frequency is downconverted to D.C., and a simple D.C. notch filter is used to remove unwanted D.C. offsets: If an FM, FSK, or GMSK signal is processed by such an IF processing chain, then the D.C. offset suppression will not only remove unwanted D.C. components, but also critical phase and amplitude information at the carrier frequency. That is, in FM cellular telephone systems significant amplitude and phase information is present at the carrier frequency, and performance will be adversely affected if such information is destroyed.

However, there are two narrow bands of frequencies in between the carrier frequency  $F_e$  and  $F_e+F_1$  and between  $F_e$  and  $F_e-F_i$  (where  $F_i$  is the lowest frequency expected in the demodulated spectrum, typically  $F_i=300$  Hz for FM cellular) which can be suppressed without adversely affecting the demodulated signal. Although minimal voice information is carried at intermodulation products at frequencies close to the carrier frequency, such products are uncommon and of relatively short duration. Accordingly, the suppression of only the low-frequency intermodulation products after baseband downconversion does not usually result in the loss of appreciable voice information. Similarly, in FSK and GMSK systems, very little signal power is present below  $F_e$ (symbol rate)/100, so again the frequency band between  $F_e$  and  $F_e+F_f$  may be suppressed without degradation of the digital data

It is therefore a further object of the present invention to provide quadrature receiver in which high-gain/highly selective active baseband filters may be employed without causing the loss of carrier frequency information.

#### SUMMARY OF THE INVENTION

The present invention is a novel automatic gain control method and apparatus for controlling signal power of a received RF signal over a wide dynamic range. In a preferred implementation the automatic gain control apparatus may be adjusted to provide a desired control response to various fading characteristics of the received RF signal. In applications where the signal of interest is a suppressed carrier digital format such as BPSK or QPSK (for CDMA 50 Digital Cellular) or a constant envelope continuous-phase format such as GMSK, FSK, or FM (used in AMPS cellular phase system), the apparatus of the present invention is capable of providing the necessary gain control, out-of-band signal rejection, and downconversion to baseband, with no D.C. offset.

In accordance with the present invention an automatic gain control (AGC) apparatus for a dual mode receiver is disclosed. The AGC apparatus includes an adjustable gain amplifier having an input port for receiving an input signal, 60 a control port for receiving a gain control signal, and an output port for providing an output signal. A downconverter coupled to the output port serves to translate the frequency of the output signal to a baseband frequency, thereby producing a baseband signal. In a preferred implementation the 65 downconverter is operative to map the carrier frequency of the received signal of the output signal to a baseband

frequency offset by a predetermined margin from D.C. A. D.C. feedthrough suppression loop, disposed to receive said baseband signal, suppresses D.C. feedthrough signals produced by the downconverter, hence providing a compensated baseband signal.

The AGC apparatus further comprises means for generating a received power signal based on the power of the output signal. A saturating integrator compares the received power signal to a reference signal and produces the gain control signal by integrating or by refraining from integration based on values of the reference, received power signal, and gain control signals.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The features, objects, and advantages of the present invention will become more apparent from the detailed description set forth below when taken in conjunction with the drawings in which like reference characters identify correspondingly throughout and wherein:

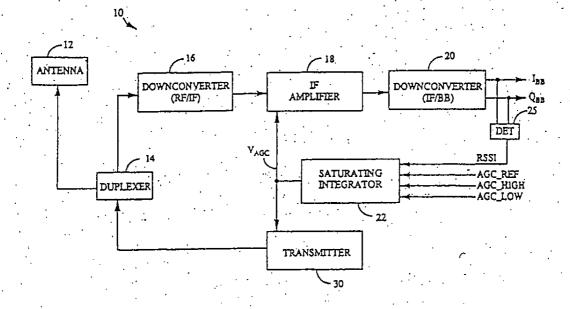

FIG. 1 illustrates in block diagram form an exemplary application of the automatic gain control apparatus (AGC) of the present invention;

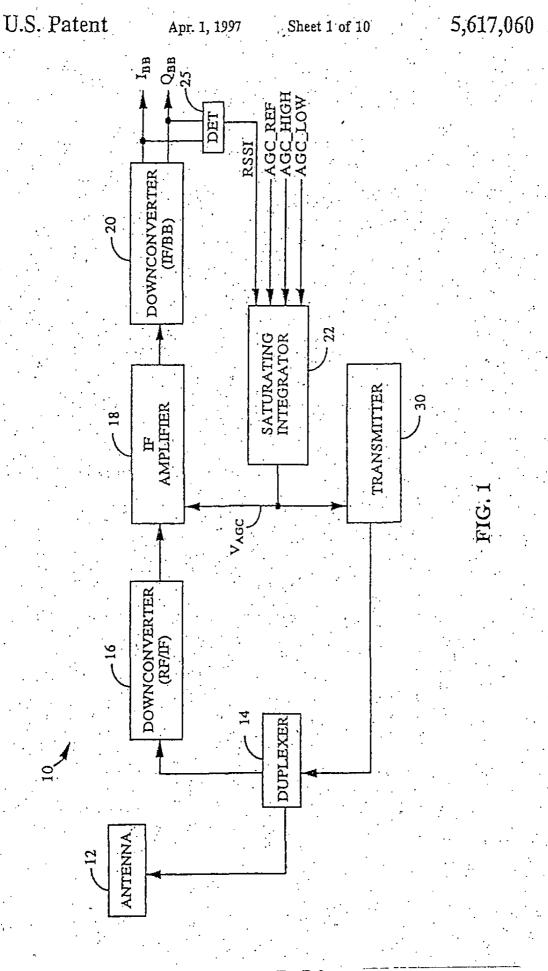

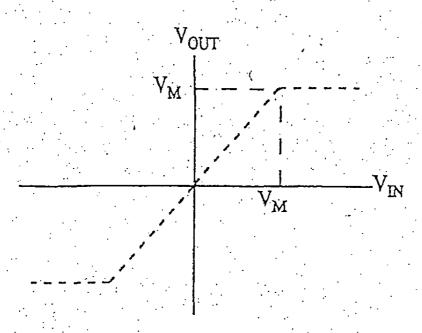

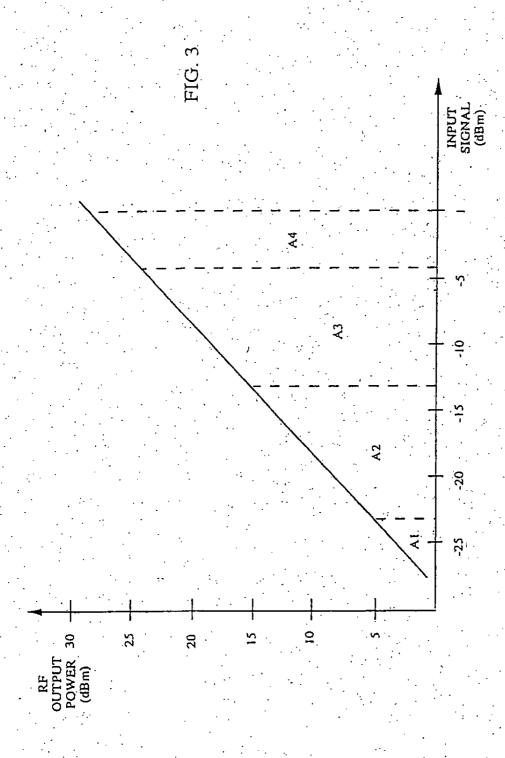

FIG. 2 illustratively represents the gain of an AGC amplifier as a function of the gain control voltage;

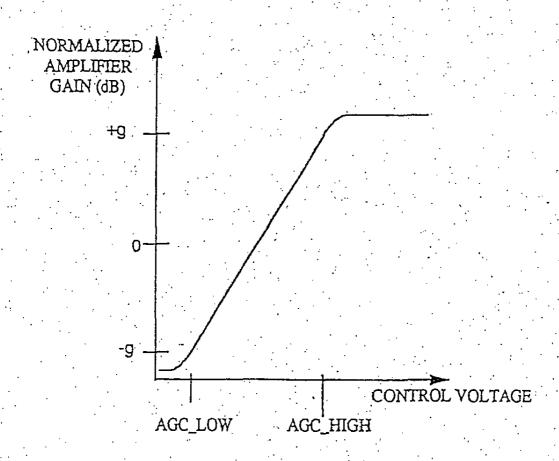

FIG. 3 shows an exemplary embodiment of the automatic gain control apparatus of the invention which includes a control loop implemented in analog form;

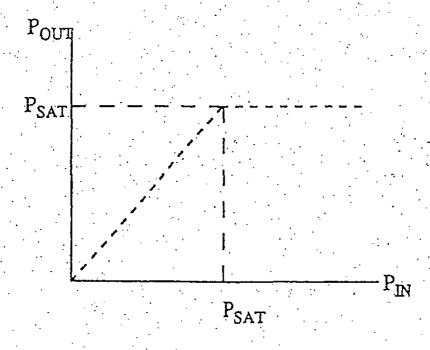

FIGS. 4A and 4B illustratively represent the voltage and power transfer characteristics, respectively, associated with an exemplary implementation of a signal limiter included within the inventive gain control apparatus;

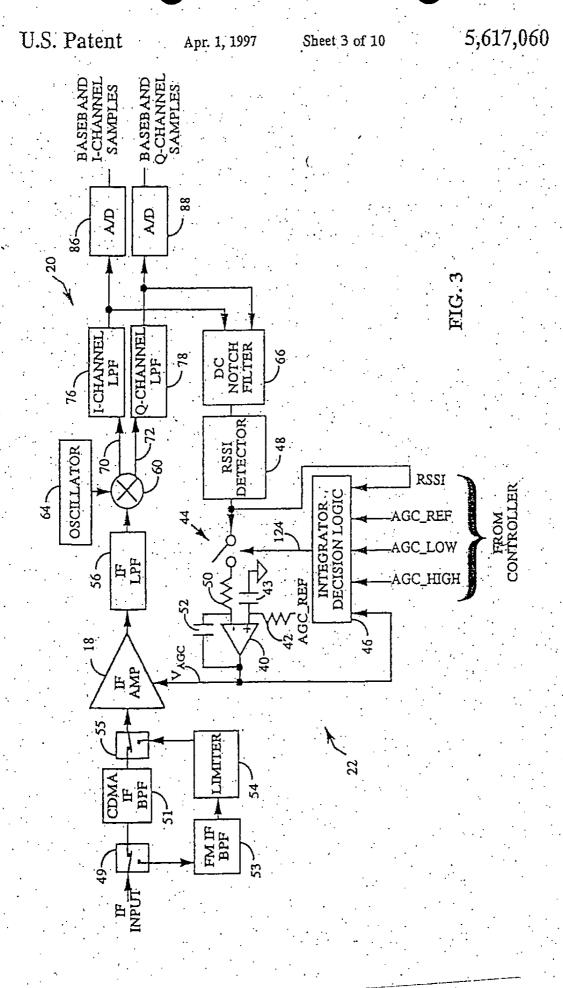

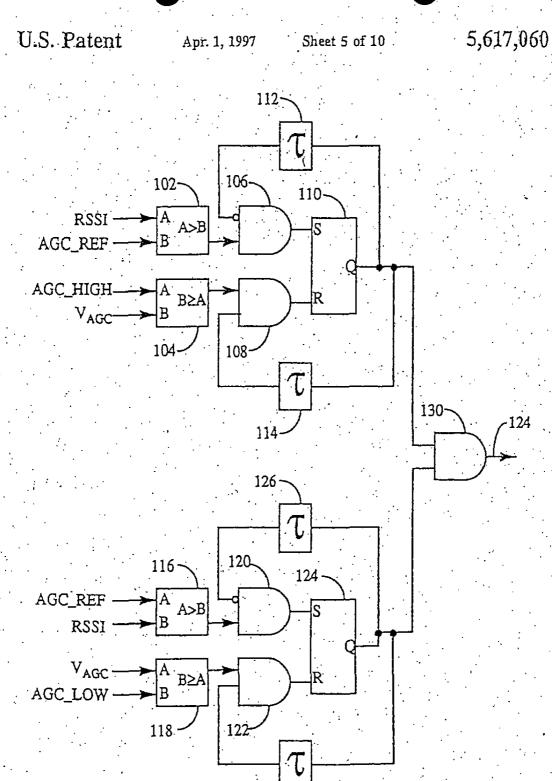

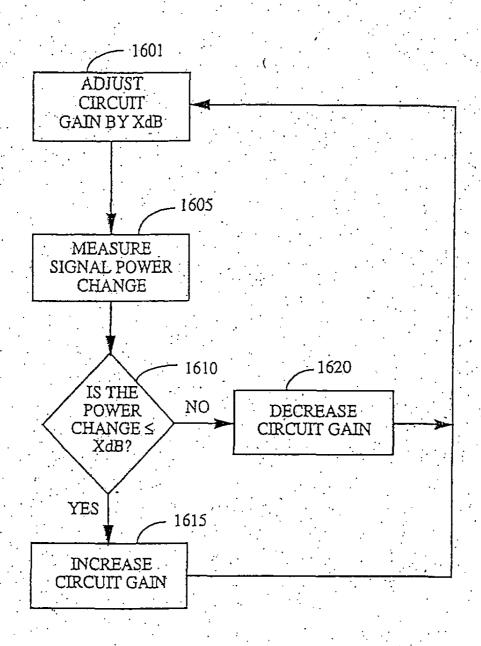

FIG. 5 depicts an exemplary implementation of decision

logic used to govern operation of an integration control switch;

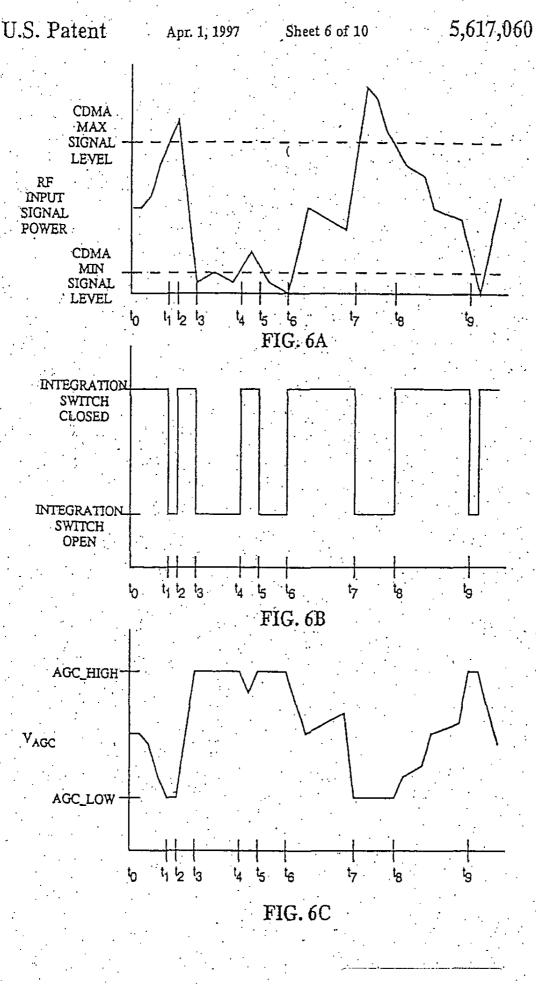

FIGS. 6A-6C are timing diagrams illustrative of the operation of the AGC apparatus of the invention;

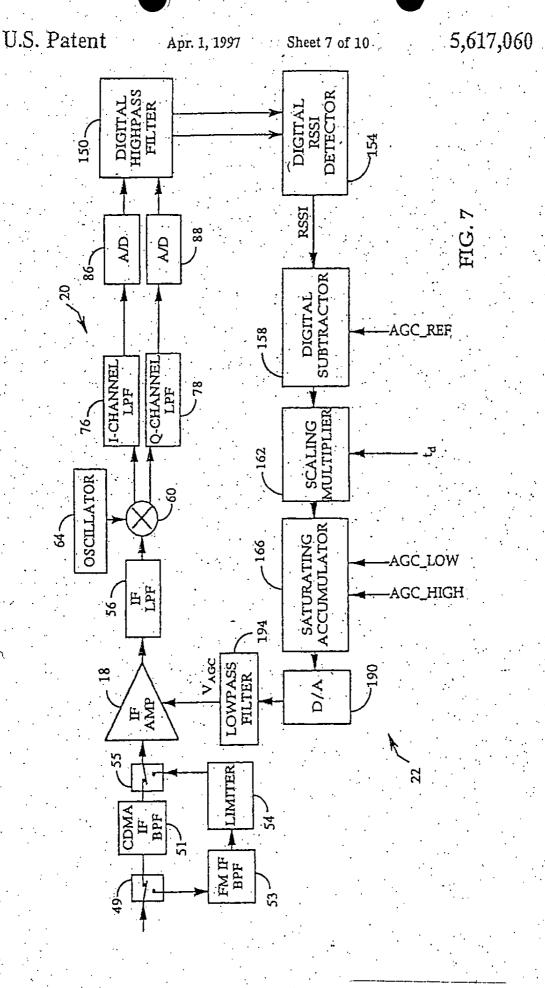

FIG. 7 shows a preferred embodiment of the AGC apparatus of the invention including a digital realization of the control loop;

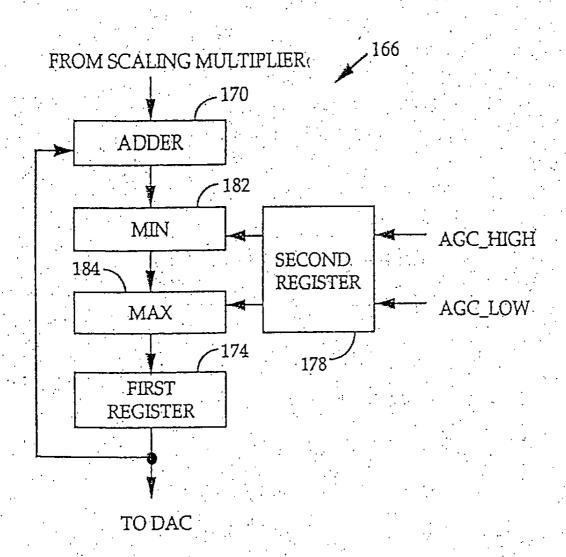

FIG. 8 depicts an exemplary implementation of a digital saturating accumulator included within the integrator of FIG. 7;

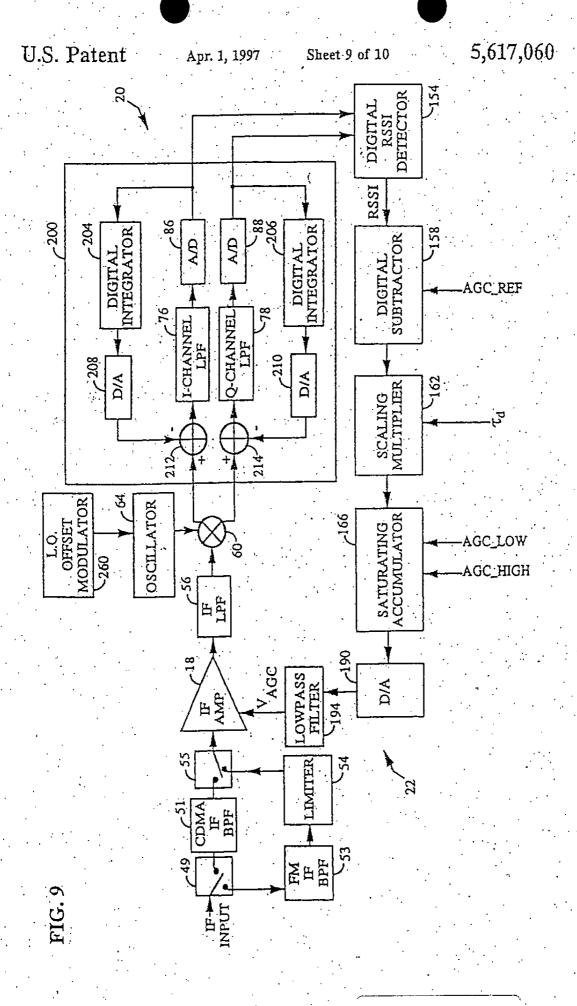

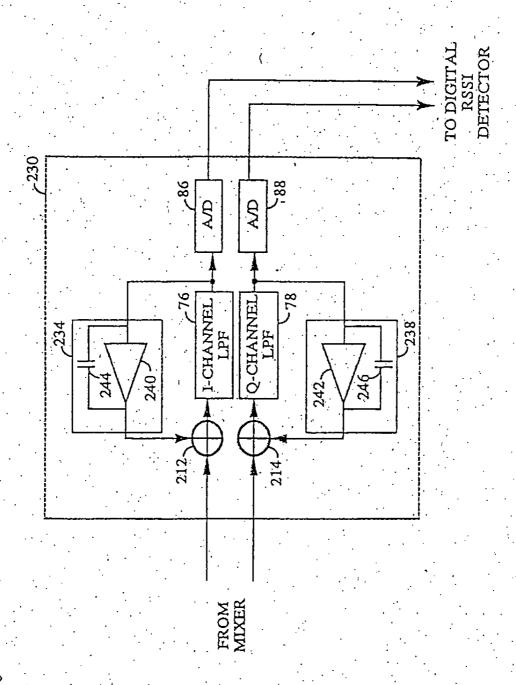

FIG. 9 shows an alternately preferred embodiment of the AGC loop of invention which includes a D.C. feedthrough suppression loop; and

FIG. 10 provides a block diagram representation of an analog D.C. feedthrough suppression loop.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

In a digital receiver, such as used in a code division multiple access (CDMA) portable cellular communications device, it is necessary to set the power of the processed signal to a constant level. In the cellular environment, a receiver may receive a signal which experiences rapid and wide variations in signal power. In order to properly process the digital data contained within the received signal the signal power must be controlled within the receiver capable of processing both CDMA (or TDMA) and standard FM signals, the received signal dynamic range will vary as a function of the selected operative mode. Accordingly, an automatic gain control apparatus for a digital receiver is

5,617,060

5

disclosed which is capable, in each of its operative modes, of compensating for variation in received signal power in either environment.

FIG. 1 illustrates in block diagram form an exemplary application of the automatic gain control apparatus of the present invention. In FIG. 1, the automatic gain control apparatus is implemented in the transceiver of a CDMA portable cellular telephone 10. Telephone 10 may be a dual mode, i.e. CDMA (or TDMA) and conventional FM compatible. The automatic gain control apparatus of the present to invention is capable of providing power control of both wideband CDMA (or TDMA) signals and narrowband FM signals. The compatibility of such circuitry to operate on both wideband and narrowband signals provides cost, component and power savings for the receiver.

Telephone 10 includes antenna 12 for receiving RF signals, including CDMA or FM communication signals, transmitted from a base station. Antenna 12 couples the received signals to duplexer 14 which provides the received signals to the receiver portion of telephone 10. Duplexer 14 also 20 receives CDMA or FM communication signals from a transmitter portion of telephone 10 for coupling to antenna 12 and transmission to a base station.

The received signals are output from duplexer 14 to downconverter 16 where the RF signals are converted to a 2 lower frequency range and are provided as corresponding intermediate frequency (IF) signals. The IF signals from downconverter 16 are provided to automatic gain controlled IF amplifier 18. The IF signals are amplified at a gain level determined by an AGC signal (V<sub>AGC</sub>) which is also provided 30 to amplifier 18. Amplifier 18 is capable of providing linear control of gain over a high dynamic range, such as in excess of 80 dB, on the basis of V<sub>AGC</sub>. Amplifier 18 may be of a design described in, for example, U.S. Pat. No. 5,099,204, entitled "LINEAR GAIN CONTROL AMPLIFIER", and assigned to the Assignee of the present invention.

In the above-referenced U.S. Pat. No. 5,099,204, a compensation circuit is employed to achieve a desired dynamic range of linear control. In particular implementations such control may be provided by the amplification circuit in the absence of assistance from a compensation circuit. Included among such implementations are those, for example, in which several amplification stages are arranged in cascade. Similarly, the availability of a high-voltage power supply may eliminate the need for a compensation circuit.

The gain controlled IF signals are output from amplifier 18 to a second frequency downconverter, downconverter 20, where the IF signals are converted to a lower frequency range and are provided as corresponding in-phase and quadrature-phase baseband signals  $I_{BB}$  and  $Q_{BB}$ . In the embodiment shown in FIG. I, the baseband signals in the CDMA mode of operation are I and Q samples of encoded digital data which are output for further phase demodulation and correlation. In a dual mode receiver, downconverter 20 also frequency downconverts FM signals so as to provide baseband FM in-phase and quadrature-phase signals, which are further phase/frequency demodulated into an audio output signal.

Detector 25 measures the strength of the signals output by 60 downconverter 20 and generates a corresponding received signal strength indication (RSSI) signal. The RSSI signal, along with an AGC reference signal (AGC\_REF) supplied by a controller (not shown), are provided to a saturating integrator 22. The AGC\_REF signal corresponds to a 65 desired signal strength level for the baseband signals. The controller also provides AGC limit low (AGC\_LOW) and

AGC limit high (AGC\_HIGH) reference signals to saturating integrator 22. The AGC\_HIGH and AGC\_LOW signals correspond to limits on the magnitude of a gain control signal (VAGC) provided to a control port of amplifier 18 by saturating integrator 22.

FIG. 2 illustratively represents the gain of amplifier 18 at a function of the gain control voltage. Referring to FIG. 2, the gain of amplifier 18 is seen to nonlinearly taper to relatively constant values for control voltages exceeding AGC\_HIGH and less than AGC\_LOW. In general, it will be desired to constrain the value of Vacc to within the linear range between AGC\_HIGH and AGC\_LOW in order that the corresponding time constant of the control loop remain within an acceptable range. Deviation of the loop time constant from the acceptable range could result in significant loop control errors. In accordance with the invention, amplifier 18 is constrained to operate within a region of linear gain by saturating integrator 22 in order to prevent the performance degradation introduced by such loop control errors.

As is described below, saturating integrator 22 is operative to integrate the difference between the RSSI and AGC\_REF signals when VAGC is between AGC\_HIGH and AGC\_LOW. When presented with an input which would cause VAGC to exceed AGC\_HIGH or fall below AGC\_LOW integrator 22 stops integrating and the gain control signal VAGC is held constant at either AGC\_HIGH or AGC\_LOW, thereby improving control loop response as described above.

Referring again to FIG. 1, saturating integrator 22, receives the RSSI signal from detector 25, along with the AGC\_REF signal from the controller. In order to provide accurate power control, in general it is necessary for the difference between the RSSI signal and the AGC\_REF signal to be minimized. Saturating integrator 22 is used to provide this function in the AGC loop by forcing the difference to zero. For example, if the gain of the signal is too high, the RSSI signal will also be high as compared to AGC\_REF. Until these signals are of equivalent magnitude, the integrator output signal VAGC will continue to decrease the gain of amplifier 18.

It should be understood that the RSSI measurement can be made at various points in the processing of the received signal. Although FIG. 1 illustrates that the measurement is made after frequency downconversion by downconverter 20, the measurement can be made at any point in the signal processing chain following IF amplifier 18. The RSSI measurement will preferably be made subsequent to completion of signal filtering, thereby minimizing the measured spunous interference power. In using analog power control techniques for both the wideband and narrowband signals, the same power control circuitry can be used for both modes of operation.

With respect to a transmitter portion 30 of the portable telephone of FIG. 1, transmit power is also controlled. The  $V_{AGC}$  signal is again used to provide instantaneous control of transmit power in CDMA mode. The  $V_{AGC}$  signal is provided to the transmitter portion 30, along with various other control signals from the controller (not shown).

Referring now to FIG. 3, there is shown an exemplary embodiment of the automatic gain control apparatus of the invention which includes a partially analog implementation of saturating integrator 22. In FIG. 3, the saturating integrator includes operational amplifier (op amp) integrator 40 baving a capacitive feedback network. In particular, integrator 40 receives the AGC\_REF signal through resistor 42 at its non-inverting input, to which is also connected capaci-

tor 43. When switch 44 is dosed in response to control information provided by integrator decision logic 46, an RSS1 signal output by RSSI detector 48 is received by integrator 40 through resistor 50. When switch 44 is held in an open position in response to control information from integrator decision logic 46, a capacitor 52 serves to hold the output  $(V_{AGC})$  of integrator 40 constant at either AGC\_HIGH or AGC\_LOW. This prevents saturation of amplifier 18 when the magnitude of the IF input signal departs from a predefined dynamic range.

Again referring to FIG. 3, an embodiment of a switching arrangement is shown using RF switches 49 and 55. RP switches 49 and 55 couple CDMA IF bandpass filter 51 to IF amplifier 18 during CDMA mode as shown by the setting of the switches in FIG. 3. In FM mode, the position of RF switches 49 and 55 changes to couple FM IF bandpass filter 53 and limiter 54 to IF amplifier 18. FM IF bandpass filter 53 for rejecting out-of-channel interference defines the bandwidth of the FM signals provided through limiter 54 to amplifier 18. For example, in FM mode operation the FM IF filter 53 is designed to have a passband spanning approximately one cellular channel (e.g., 30 kHz), and a stopband extending significantly beyond (e.g., ±60 kHz) the IF center frequency. During CDMA mode operation the CDMA IF filter 51 is designed to reject out-of-channel interference and defines the bandwidth of the CDMA signals provided to 25 amplifier 18. For example during CDMA mode, CDMA IF bandpass filter 51 may provide a passband commensurate with the chip rate of the baseband portion of the receiver (c.g. 1.26 MHz), and provide a predefined rejection bandwidth (e.g. 1.8 MHz). In an alternative embodiment, limiter 54 could be in the common path before IF amplifier 18.

Limiter 54 attenuates high power RF signals, which are principally received during FM mode operation. FM signals may exceed the maximum power of signals encountered during CDMA mode operation. In a preferred embodiment limiter 54 limits the input power to amplifier 18 to within the dynamic range, e.g., 80 dB, characteristic of CDMA operation. Limiter 54 allows the control range of the automatic gain control (AGC) loop of FIG. 3 to be designed on the basis of the expected CDMA dynamic range, thereby eliminating the need to provide separately calibrated AGC control loops for FM and CDMA mode operation.

FIG. 4A and 4B illustratively represent the voltage and power transfer characteristic, respectively, associated with an exemplary implementation of limiter 54. Referring to FIG. 4A and 4B, limiter 54 does not altenuate signals having voltage magnitudes less then a predefined maximum voltage Vm. The saturated power may be quantified as P<sub>5A7</sub>=Vm<sup>2</sup>/ 2R, where R, denotes the input load impedance of ampli- 50 fier 18. For input power in excess of  $P_{SAT}$ , the output signals power produced by limiter 54 is made to remain constant at approximately  $P_{SAF}$  by clipping the peak signal voltage to the voltage Vm. The value of P<sub>SAT</sub> will be selected based on the maximum expected CDMA input power level. Accordingly, for example, high-power sinusoidal IF input signals (Pin>P<sub>SAT</sub>), the output waveform produced by limiter 54 is truncated to a fixed amplitude but the fundamental frequency and phase information is not lost. The limiter induced harmonic distortion is removed by lowpass filter 56. 60

Low-pass filter 56, included within the downconverter 20, is designed to have a cut-off frequency larger than the frequency of the IF signal output by amplifier 18 in either CDMA mode or FM mode. As noted above, low-pass filter 56 is designed to attenuate harmonics of the IF signal output 65 by amplifier 18 prior to downconversion to baseband in-phase (I) and quadrature phase (Q) components. High-power

waveforms clipped by limiter 54 create unwanted harmonics. IF lowpass filter 56 removes the unwanted harmonics so that they are not converted to baseband along with the desired IF signal information. In an exemplary embodiment the type, order, and passband edge of filter 56 are selected to

attenuate in the amplified IF signal produced by amplifier

The filtered IF signal is provided to a first input of a mixer 60, while the other input of mixer 60 receives a locally generated reference signal from oscillator 64. Mixer 60 mixes the filtered IF signal with the reference signal to produce the I and Q baseband (quadrature) components on output lines 70 and 72, respectively. The mixer 60 is designed to map a frequency which is offset from the IF center frequency by a predefined margin, e.g. from 3 to 300 Hz, to the baseband D.C. frequency, Such a D.C. offset margin allows the automatic gain control loop of FIG. 3 to distinguish between an unmodulated FM signal (i.e., a continuous wave (CW) signal) from an input D.C. offset error. Specifically, mixer 60 will preferably be operative to produce an output frequency of approximately 100 Hz in response to an input CW signal at the mid-band IF frequency. In this way input D.C. offset errors tending to corrupt RSSI power measurements are removed by a D.C. notch filter 66 without attenuating CW signal information.

Referring again to FIG. 3, output lines 70 and 72 are respectively connected to baseband I and Q-channel lowpass filters (LPFs) 76 and 78. I and Q-channel LPFs 76 and 78 will preferably each be implemented to as to provide lowpass transfer functions exhibiting cutoff frequencies of 13 kHz and 630 kHz, respectively, during FM and CDMA mode operation. In an exemplary embodiment filters 76 and 78 each include a pair of I and Q-channel, one of which is employed during CDMA mode operation and the other during FM mode operation. The individual filters included within I and Q-channel LPFs 76 and 78 are switched into the baseband I and Q signal paths; respectively, in accordance with the selected mode of operation. In the preferred embodiment the system controller includes means for switching the filters included within the filter networks in accordance with the operative mode selected.

In addition to performing an anti-aliasing function for A/D converters 36 and 88, I and Q-channel LPFs 76 and 78 also provide out-of-band signal rejection. In the preferred embodiment, filters 76 and 78 have high gain, and high stop-band rejection. As a result, IF bandpass filter 51 and 53 can have less stop-band rejection, and therefore can be less expensive.

After filtering by the I and Q-channel LPFs 76, 78 and by D.C. notch filter 66, the resulting baseband I and Q signals are provided to RSSI detector 48, RSSI detector 48 provides an output RSSI signal indicative of measured signal power (in dB). The difference between the RSSI signal output by RSSI detector 48 and AGC\_REF is integrated within saturating integrator 22 so as to produce the control voltage VAGC.

Again referring to FIG. 3, the I and Q outputs of the I and Q-channel LPFs 76 and 78 are also provided to I and Q analog to digital (A/D) converters 86 and 88, respectively. A/D converters 86 and 88 operate to quantize the baseband I and Q signals for digital demodulation in the selected operative mode, i.e., either CDMA or FM. In the preferred embodiment the dynamic range of A/D converters 86 and 88 is selected to be sufficient to accommodate signals that exceed the control range of the AGC apparatus of IF amplifier 18. As was noted above with reference to FIGS. 2

Ex. B-15

5,617,060

and 3, decision logic 46 within saturating integrator 22 constrains the control voltage V acc to within the range AGC\_LOW-Y/Acc-AGC\_HIGH, This prevents amplifier 18 from saturating in a nonlinear operating region.

Accordingly, A/D converters 36 and 88 are designed to 5 quantize input signals, without excessive distortion, whether or not integrator 40 is saturated. In the preferred embodimest, each of A/D conveners 86 and 88 provides 6 to 8 bits of dynamic range. This dynamic range is sufficient to prevent degradation in the signal to noise ratio of the input 10 to A/D converters 86 and 88 as compared to the signal to noise ratio of the quantized digital output of A/D converters 86 and 88 for any RF input level. For example, when Vice reaches AGC LOW, limiter 54 constrains the amplitude of the IF signal. In this way, the signal level at the input of A/D conveners 86 and 88 may exceed the level indicated by 15 AGC REF by only some fixed amount. Therefore, AD conveners 86 and 88 will continue to accurately quantize the baseband signals at the increased level.

Likewise the dynamic range of A/D conveners 86 and 88 is sufficient to prevent degradation of the signal to noise ratio at low RF input signal levels. For example when Vice reaches AGC\_HIGH and switch 44 opens, if the input RF signal continues to fall, the baseband signal level at the input of A/D conventers 86 and 88 falls below the level indicated by AGC REP. The decreased level of the signal input to A/D converters 86 and 88 results in Jess than full utilization of the device, i.e., some of the bits of the output of the A/D converters 36 and 88 are not used. For larger RF input signals, the entire dynamic range of the A/D converters 36 and 88 is utilized during the conversion process. Hence, the AGC apparatus of the invention enables a limited tange AGC control loop to be used in demodulating signals spanning a substantially larger dynamic range than the control range of the IF amplifier 1s.

FIG. 5 depicts an exemplary implementation of decision logic 46 operative to control the position of the switch 44. As shown in FIG. 5, the AGC\_HIGH and Vace signals are presented to logical comparator 104. When Vice exceeds the level of AGC\_HIGH, the output of comparator 164 becomes a logic level one (1). The output of comparator 104 is logically AND ed with the output of dip-dop 110, which is at a logic level I due to the closed position of switch 44. The output of Sip-flop 118 is delayed through delay element 114 to prevent excessive, spurious toggling of the position of 43 switch 44. AND gate 108 and delay element 114 operate to prevent switch 44 from being opened until after a fixed period of time following its closure. The output of AND gate 108 transitions from low to high thus resetting the output of flip-flop 110 to a logic level 0 and producing a logic level 0 30 at the output of AND gate 130 and opening switch 44. When switch 44 is opened, the RSSI signal and AGC\_REF signal are no longer forced by the loop to be equivalent In the case when AGC\_HIGH has been exceeded and the loop is opened, the RSSI signal indicates a smaller signal than AGC REF and the cusput of logical comparator 102 becomes a logic level 0. When the RSSI signal exceeds the level of AGC\_REF, the output of comparator 102 transitions high and the output of AND gate 106 also transitions high, thus seeing the output of this Bop 110 to logic level 1 60 and closing switch ed, Delay clement 112 and AND gate 106 function similarly to delay 114 and AND gate 108, and prevent closure of switch 44 until it has been open for a predefined time period.

An analogous sequence of logical operations is executed 61 when the level of the RF input signal exceeds the AGC range. When Vacc fails below the level of AGC\_LOW, the

output of comparator 118 becomes a logic level 1. The output of comparator 118 is logically AND of with the output of hip-flop 124, which is at a logic level 1 when switch 44 is closed. The output of AND gate 122 then transitions from low to high, thus reseming the output of flip-flop 124 to a logic level 0. This causes a logic level 0 to appear at the output of AND gate 130, which results in the opening of switch 44. When switch 44 is opened, the RSSI signal is no longer forced by the loop to be equal to AGC REF. Upon the loop being opened in this manner the RSSI signal will be larger than AGC REF and the output of logical comparator 116 will be at logical level 0. When the RSSI signal becomes smaller than AGC REF, the outputs of comparator 116 and AND gate 120 transition high. The transition sets the output of Rig-Rop 124 to logic level 1 and closes switch 44. Delay elements 126 and 128 and AND gates 120 and 122 function similarly to delay 114 and AND gate 103, and serve to prevent rapid toggling of switch 44 between open and closed positions.