Charles K. Verhoeven (Bar No. 170151) 1 charlesverhoeven@quinnemanuel.com Sean S. Pak (Bar No. 219032) seanpak@quinnemanuel.com John M. Neukom (Bar No. 275887) 3 johnneukom@quinnemanuel.com 4 OUINN EMANUEL UROUHART & SULLIVAN, LLP 50 California Street, 22nd Floor San Francisco, California 94111-4788 (415) 875-6600 Telephone: 6 Facsimile: (415) 875-6700 7 Michael D. Powell (Bar No. 202850) mikepowell@quinnemanuel.com QUINN EMANUEL URQUHART & SULLIVAN, LLP 555 Twin Dolphin Drive, Fifth Floor Redwood Shores, CA 94065 (650) 801-5000 Telephone: 10 Facsimile: (650) 801-5100 11 Thomas D. Pease\* thomaspease@quinnemanuel.com 12 QUINN EMANUEL URQUHART & SULLIVAN, LLP 51 Madison Avenue, 22nd Floor 13 New York, New York 10010 Telephone: (212) 849-7000 14 Facsimile: (212) 849-7100 \*pro hac vice application to be filed 15 Attorneys for STMicroelectronics, Inc. 16 UNITED STATES DISTRICT COURT 17 NORTHERN DISTRICT OF CALIFORNIA 18 CASE No. 3STMICROELECTRONICS, INC., 19 COMPLAINT FOR PATENT Plaintiff, 20 **INFRINGEMENT** VS. 21 **DEMAND FOR JURY TRIAL** INVENSENSE, INC., 22 Defendant. 23 24 25 26 27 28

Case3:13-cv-01116-JCS Document1 Filed03/12/13 Page1 of 31

Plaintiff STMicroelectronics, Inc. ("STI") alleges for its complaint against Defendant

InvenSense, Inc. ("InvenSense") as follows:

INTRODUCTION

1. This is an action for patent infringement brought before this Court pursuant to 28 U.S.C. §§ 1331 and 1338(a). STI seeks remedies for InvenSense's infringement of one or more claims of each of United States Patents Nos. 6,370,954 (the "'954 patent") and 6,034,419 (the "'419 patent") (collectively, "the Asserted Patents"). True and correct copies of the Asserted Patents are attached hereto as Exhibits A and B.

#### **PARTIES**

- 2. STMicroelectronics, Inc. is a corporation organized and existing under the laws of the State of Delaware, having its corporate headquarters and principal place of business at 750 Canyon Drive, Coppell, Texas 75019. STI is a subsidiary of STMicroelectronics NV, a Netherlands corporation, and does business in the Northern District of California. STI, STMicroelectronics N.V., and their various subsidiaries and affiliates are hereinafter referred to as "ST."

- 3. On information and belief, InvenSense: (i) is a corporation organized under the laws of the State of Delaware, having its corporate headquarters and principal place of business here in the Northern District of California at 1197 Borregas Avenue, Sunnyvale, CA 94089; (ii) may be served with process by serving its Delaware registered agent The Corporation Trust Company, The Corporation Trust Center, 1209 Orange Street, Wilmington, Delaware 19801; and (iii) does business in the Northern District of California.

#### JURISDICTION AND VENUE

- 4. This lawsuit is a civil action for patent infringement arising under the patent laws of the United States, 35 U.S.C. § 101, et seq. Accordingly, this Court has subject matter jurisdiction pursuant to 28 U.S.C. §§ 1331 and 1338(a).

- 5. This Court has personal jurisdiction over InvenSense for at least the following reasons: (i) on information and belief, InvenSense's corporate headquarters and principal place

11

12

13

14 15

16

17 18

19

20

21 22

23 24

25

26 27

28

of business are located in the Northern District of California; (ii) InvenSense has committed acts of patent infringement, and/or contributed to or induced acts of patent infringement by others, in this District and elsewhere in California and the United States; (iii) InvenSense regularly does business or solicits business, engages in other persistent courses of conduct, and/or derives substantial revenue from products and/or services provided to individuals in this District and in this State; and (iv) InvenSense has purposefully established substantial, systematic, and continuous contacts with this District and expects or should reasonably expect to be sued here. Thus, this Court's exercise of jurisdiction over InvenSense will not offend traditional notions of fair play and substantial justice.

Venue is proper in this judicial district pursuant to 28 U.S.C. §§ 1391(b)-(c) and 6. 1400(b) because InvenSense does business in the State of California, has committed acts of infringement in this State and in this District, a substantial part of the events or omissions giving rise to this complaint occurred in this District, and InvenSense is subject to and has previously subjected itself to personal jurisdiction in this District. Moreover, InvenSense's corporate headquarters are located in this District.

#### INTRADISTRICT ASSIGNMENT

7. This is an Intellectual Property Action to be assigned on a district-wide basis pursuant to Civil Local Rule 3-2(c).

#### BACKGROUND

## ST's MEMS Innovations

8. ST is a global leader in the semiconductor market serving customers across the spectrum of sense and power technologies and multimedia convergence applications. Since its inception, ST has maintained an unwavering commitment to research and development ("R&D"). STI and the other ST companies make a substantial investment in the research and development of inventions and other intellectual property. Almost one quarter of the world-wide employees of ST work in R&D and/or product design, and ST has advanced R&D centers around the world including in the United States. Today, STI and the other ST companies own over

21,500 patents and pending patent applications worldwide, including over 7,500 issued U.S. patents and 2,500 pending U.S. patent applications.

- One area in which ST has made a substantial and long-term R&D investment is in 9. the field of Micro-Electro-Mechanical Systems ("MEMS"). ST launched the consumer MEMS revolution through the combination of innovative product design, manufacturing know-how, deep application expertise, and bold and timely infrastructure investments. ST was the first major manufacturer in the world to start producing MEMS on 8-inch silicon wafers. ST also developed the THELMA (Thick Epi-Poly Layer for Microactuators and Accelerometers) surface micro-machining process for use in manufacturing both accelerometers and gyroscopes. In addition, ST introduced the world's first high-performance 3-axis MEMS gyroscope. ST's patents and products reflect its innovations in MEMS manufacturing, packaging, circuit design, electrical contacts, device integration, actuation and sensing technologies, and component layout.

- ST is the leading supplier by revenue of MEMS devices for consumer and mobile 10. MEMS. Building on its track record of success, ST continues to invest in MEMS R&D and innovative applications for MEMS.

#### The Asserted Patents

- 11. STI is the owner by assignment of all rights, title, and interest in the Asserted Patents, including the right to bring this suit for injunctive relief and damages.

- U.S. Patent No. 6,034,419, entitled "Semiconductor Device With A Tungsten 12. Contact," was duly and legally issued by the United States Patent and Trademark Office on March 7, 2000.

- U.S. Patent No 6,370,954, entitled "Semiconductor Integrated Inertial Sensor 13. With Calibration Microactuator," was duly and legally issued by the United States Patent and Trademark Office on January 25, 2005.

25

26

27

28

#

## **InvenSense Infringes STI's Patents**

- 14. On information and belief, InvenSense was incorporated in California in June 2003 and reincorporated in Delaware in January 2004.

- 15. InvenSense competes, or seeks to compete, with STI in the United States and other ST companies around the world in the MEMS market.

- 16. InvenSense has infringed, and continues to infringe, the Asserted Patents. As of April 3, 2011, InvenSense claims to have sold over 110 million units of MEMS products.

- 17. InvenSense's infringing MEMS products are sold by InvenSense with the expectation that they will be incorporated into consumer electronic products that are purchased, used and/or sold in, or imported to, the United States, including in the Northern District of California. As stated on its website, InvenSense's MEMS gyroscopes "have been designed into digital still cameras and camera phones for image stabilization; GPS devices for dead reckoning; and 3D peripherals such as 3D mice, TV remote controls, and game controllers. There are millions of consumer electronic products and applications incorporating the Company's integrated dual-axis gyros."

- 18. On information and belief, InvenSense designs its MEMS products in the United States and particularly in the Northern District of California.

- 19. InvenSense's Registration Statement, as amended, for its initial public offering ("Registration Statement") further touted that "in 2011, its ITG/IMU/MPU-3000 family of products started high volume shipments for the portable gaming, digital television and set-top box remote control, smart phone and tablet markets." In a September 14, 2011 press release, InvenSense announced that "it is shipping in volume the MPU-6050 product to handset and tablet OEMs and ODMs." On information and belief, by way of example, InvenSense's infringing products are intended for use in, and are incorporated into, devices such as the following in order to enable motion-based applications:

- Gaming devices, such as Nintendo Wii MotionPlus Accessory, Nintendo Wii Remote Plus Controller, Nintendo 3DS and Roku 2 XS (which incorporate, by way of example, InvenSense's ITG-3205, IDG-600, ITG-3270 and/or IMU-3000)

- Toys with motion sensing capabilities, such as the A.R. Drone and A.R. Drone 2 by Parrot (which incorporates, by way of example, InvenSense's IMU-3000);

- Smart phones, such as LG's Optimus Black P970 (which incorporates, by way of example, InvenSense's MPU-3050); and

- Other electronic devices such as Black & Decker's motion-sensing screwdriver (which incorporates, by way of example, InvenSense's ISZ-650) and the Amazon Kindle Fire HD (which incorporates, by way of example, InvenSense's MPU-6050).

- 20. In addition, InvenSense indirectly infringes the Asserted Patents. InvenSense induces distributors, consumers, and end-users to directly infringe the Asserted Patents by selling or using its MEMS products, including those identified above and herein. InvenSense's marketing, sales, and customer support materials instruct customers to use infringing features of its MEMS products in an infringing manner. For example, InvenSense's website provides customers and potential customers with product specifications, technical papers and other marketing materials for InvenSense's MEMS products that tout their infringing features and instruct customers to use them in an infringing manner. On information and belief, InvenSense also provides verbal and written instructions, including sales support and technical know-how, to its distributors and customers that intentionally aid, assist, and encourage infringement.

- 21. InvenSense's MEMS products which it sells directly, as well as through its distribution partners, to consumers and assemblers are designed to be used (and are used by said parties) in an infringing manner. Additionally, on information and belief, InvenSense's MEMS products were especially designed, made, and/or adapted for use in an infringing manner. InvenSense's MEMS products either embody the claimed inventions on their own or are material, non-staple components of end-user products that embody the claimed inventions, which components have no substantial non-infringing uses. In fact, as part of its Registration Statement, InvenSense touted its "direct customer engagement model": "We work directly with

large original equipment manufacturer (OEM) customers to assist them in developing solutions and applications that may lead to more demand for our products. . . . For our larger OEM customers, we believe that our direct customer engagement approach, ecosystem partnerships and adoption of our APIs into major software operating systems provides us with significant differentiation in the customer sales process by aligning us more closely with the changing needs of these OEM customers and their end markets. We actively utilize field application engineers as part of our sales process to better engage the customer with our products. . . . Our direct customer engagement model extends to service and support."

# InvenSense Knowingly Induced And Contributed To The Infringement Of Others

Asserted Patents and its infringement thereof since at least February 2012. In or around December 2011, the parties engaged in license negotiations during which ST identified particular patents that InvenSense was infringing. In or around February 2012, ST made various presentations to InvenSense that demonstrated how certain InvenSense products infringed certain patent claims of various ST patents, including the '954 and '419 patents. Despite such notice, InvenSense has failed to cease its infringement. Instead, InvenSense continues to sell its infringing products and encourage its customers to use InvenSense products in an infringing manner.

# InvenSense's Infringement Harms STI

- 23. STI is harmed by InvenSense's use of STI's patented technologies in a way that cannot be remedied by monetary damages alone. InvenSense has received substantial revenue and increased its market share by selling products that incorporate STI's technology without having to incur the costs of developing or licensing this technology.

- 24. On information and belief, InvenSense's infringement has caused STI to suffer irreparable harm due to, among other things, lost business opportunities, lost market share, and price erosion. Even if InvenSense were to subsequently pay past due royalties, lost profits, or other damages, there is no reason to believe that InvenSense would stop infringing, and it would

still enjoy the market share it has developed while infringing upon the Asserted Patents. Due to the difficulty in predicting whether, if at all, STI can recover this market share, STI's harm cannot be compensated by payment of monetary damages alone.

## **COUNT I: INFRINGEMENT OF U.S. PATENT NO. 6,370,954**

- 25. STI incorporates by reference the preceding averments set forth in paragraphs 1-24.

- 26. InvenSense has infringed and continues to infringe, has contributed to and continues to contribute to acts of infringement, and/or has actively and knowingly induced and continues to actively and knowingly induce the infringement of the '954 patent by making, using, offering for sale and selling in the United States, and by importing into the United States without authority, and/or by causing others to make, use, offer for sale and sell in the United States, and import into the United States without authority, MEMS products and services, including but not limited to InvenSense's ISZ-650, IMU-3000, ITG-3050, MPU-3050, ITG-3200, MPU-6000, MPU-6050, and MPU-9150 product lines.

- 27. On information and belief, InvenSense's infringement, contributory infringement, and/or inducement of infringement is literal infringement or, in the alternative, infringement under the doctrine of equivalents.

- 28. InvenSense's infringing activities have caused and will continue to cause STI irreparable harm, for which it has no adequate remedy at law, unless InvenSense's infringing activities are enjoined by this Court in accordance with 35 U.S.C. § 283.

- 29. STI has been and continues to be damaged by InvenSense's infringement of the '954 patent in an amount to be determined at trial.

- 30. On information and belief, InvenSense's infringement of the '954 patent was willful and deliberate, entitling STI to enhanced damages and attorneys' fees.

# COUNT II: INFRINGEMENT OF U.S. PATENT NO. 6,034,419

31. STI incorporates by reference the preceding averments set forth in paragraphs 1-30.

- 32. InvenSense has infringed and continues to infringe, has contributed to and continues to contribute to acts of infringement, and/or has actively and knowingly induced and continues to actively and knowingly induce the infringement of the '419 Patent by making, using, offering for sale and selling in the United States, and by importing into the United States without authority, and/or by causing others to make, use, offer for sale and sell in the United States, and import into the United States without authority, MEMS products and services, including but not limited to InvenSense's IMU-3000, ITG-3050, MPU-3050, ITG-3200, MPU-6050, and MPU-9150 product lines.

- 33. On information and belief, InvenSense's infringement, contributory infringement, and/or inducement of infringement is literal infringement or, in the alternative, infringement under the doctrine of equivalents.

- 34. InvenSense's infringing activities have caused and will continue to cause STI irreparable harm, for which it has no adequate remedy at law, unless InvenSense's infringing activities are enjoined by this Court in accordance with 35 U.S.C. § 283.

- 35. STI has been and continues to be damaged by InvenSense' infringement of the '419 patent in an amount to be determined at trial.

- 36. On information and belief, InvenSense's infringement of the '419 patent was willful and deliberate, entitling STI to enhanced damages and attorneys' fees.

## REQUEST FOR RELIEF

WHEREFORE, Plaintiff STMicroelectronics, Inc. respectfully requests that:

- (a) Judgment be entered that InvenSense has infringed one or more claims of each of the Asserted Patents;

- (b) Judgment be entered permanently enjoining InvenSense, its directors, officers, agents, servants, and employees, and those acting in privity or in concert with them, and their subsidiaries, divisions, successors, and assigns, from further acts of infringement, contributory infringement, or inducement of infringement of the Asserted Patents;

| - 1                             | i               |                                                                     |               |                                |                      |                 |  |

|---------------------------------|-----------------|---------------------------------------------------------------------|---------------|--------------------------------|----------------------|-----------------|--|

| 1                               | (c)             | Judgment be                                                         | entered awa   | rding STI all damages          | adequate to compe    | ensate it for   |  |

| 2                               | InvenSense's    | infringement of                                                     | of the Assert | ed Patents including al        | l pre-judgment and   | i post-judgment |  |

| 3                               | interest at the | interest at the maximum rate permitted by law and enhanced damages; |               |                                |                      |                 |  |

| 4                               | (d)             | Judgment be                                                         | entered that  | this is an exceptional         | case and awarding    | STI attorneys'  |  |

| 5                               | fees and costs  | s; and                                                              |               |                                |                      |                 |  |

| 6                               | (e)             | Judgment be                                                         | entered awa   | rding STI such other a         | nd further relief as | this Court may  |  |

| 7                               | deem just and   | l proper.                                                           |               |                                |                      |                 |  |

| 8                               |                 |                                                                     |               |                                |                      |                 |  |

| 9                               | DATED: Ma       | rch 12, 2013                                                        |               | QUINN EMANUEL<br>SULLIVAN, LLP | URQUHART &           |                 |  |

| 10                              |                 |                                                                     |               | SOLLI VAIV, LLI                |                      |                 |  |

| 11                              |                 |                                                                     |               | 111.                           | IDD                  | ell Mac         |  |

| 12                              |                 |                                                                     |               | By Michael D. Pov              |                      |                 |  |

| 13                              |                 |                                                                     |               | Attorneys for S                | STMicroelectronics   | , Inc.          |  |

| 14                              |                 |                                                                     |               |                                |                      |                 |  |

| 15                              |                 |                                                                     |               |                                |                      |                 |  |

| 16                              |                 |                                                                     |               |                                |                      |                 |  |

| 17                              |                 |                                                                     |               |                                |                      |                 |  |

| 18                              |                 |                                                                     |               |                                |                      |                 |  |

| 19                              |                 |                                                                     |               |                                |                      |                 |  |

| 20                              |                 |                                                                     |               |                                |                      |                 |  |

| 21                              |                 |                                                                     |               |                                |                      |                 |  |

| 22                              |                 |                                                                     |               |                                |                      |                 |  |

| <ul><li>23</li><li>24</li></ul> |                 |                                                                     |               |                                |                      |                 |  |

| 25                              |                 |                                                                     |               |                                |                      |                 |  |

| 26                              |                 |                                                                     |               |                                |                      |                 |  |

| 27                              |                 |                                                                     |               |                                |                      |                 |  |

| 28                              |                 |                                                                     |               |                                |                      |                 |  |

| -                               | I .             |                                                                     |               |                                |                      |                 |  |

| 1        | UNITED STATES DISTRICT COURT                                    |                                                     |  |  |  |

|----------|-----------------------------------------------------------------|-----------------------------------------------------|--|--|--|

| 2        | NORTHERN DISTRICT OF CALIFORNIA                                 |                                                     |  |  |  |

| 3        |                                                                 |                                                     |  |  |  |

| 5        | STMICROELECTRONICS, INC., Plaintiff,                            | Case No.                                            |  |  |  |

| 6        | vs.                                                             | DEMAND FOR JURY TRIAL                               |  |  |  |

| 7        | INVENSENSE, INC.,                                               |                                                     |  |  |  |

| 8        | Defendant.                                                      |                                                     |  |  |  |

| 9        |                                                                 |                                                     |  |  |  |

| 10       |                                                                 |                                                     |  |  |  |

| 11       | TO EACH PARTY AND TO THE O                                      | COUNSEL OF RECORD FOR EACH PARTY:                   |  |  |  |

| 12       | Plaintiff STMicroelectronics, Inc. here                         | eby demands a jury trial in the above-titled action |  |  |  |

| 13       | pursuant to Rule 38(b) of the Federal Rules of Civil Procedure. |                                                     |  |  |  |

| 14       |                                                                 |                                                     |  |  |  |

| 15       |                                                                 |                                                     |  |  |  |

| 16       | DATED: March 12, 2013                                           | Respectfully submitted,                             |  |  |  |

| 17<br>18 |                                                                 | QUINN EMANUEL URQUHART & SULLIVAN, LLP              |  |  |  |

| 19       |                                                                 | MILL OF TO MAC                                      |  |  |  |

| 20       |                                                                 | By: Wichael D. + Evell Michael D. Powell            |  |  |  |

| 21       |                                                                 | Attorneys for STMicroelectronics, Inc.              |  |  |  |

| 22       |                                                                 |                                                     |  |  |  |

| 23       |                                                                 |                                                     |  |  |  |

| 24       |                                                                 |                                                     |  |  |  |

| 25       |                                                                 |                                                     |  |  |  |

| 26       |                                                                 |                                                     |  |  |  |

| 27       |                                                                 |                                                     |  |  |  |

| 28       |                                                                 |                                                     |  |  |  |

|          | l e                                                             |                                                     |  |  |  |

# **EXHIBIT A**

# (12) United States Patent Zerbini et al.

(10) Patent No.:

US 6,370,954 B1

(45) Date of Patent:

Apr. 16, 2002

# (54) SEMICONDUCTOR INTEGRATED INERTIAL SENSOR WITH CALIBRATION MICROACTUATOR

(75) Inventors: Sarah Zerbini, Fontanellato; Benedetto

Vigna, Pietrapertosa; Massimo Garavaglia, Robecchetto; Gianluca Tomasi, Vigevano, all of (IT)

(73) Assignee: STMicroelectronics S.r.l., Agrate

Brianza (IT)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 09/659,168

(22) Filed: Sep. 11, 2000

(30) Foreign Application Priority Data

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,251,484 A | ٠ | 10/1993 | Mastache 73/514.02 |

|-------------|---|---------|--------------------|

| 5,621,157 A | ٠ | 4/1997  | Zhao et al 73/1.38 |

6,257,062 B1 \* 7/2001 Rich ...... 73/514.32

#### FOREIGN PATENT DOCUMENTS

| EP | 0 840 092 A2 | 5/1998  |

|----|--------------|---------|

| wo | 89/10567     | 11/1989 |

| wo | 95/34798     | 12/1995 |

| wo | 96/39615     | 12/1996 |

\* cited by examiner

Primary Examiner-Richard A. Moller

(74) Attorney, Agent, or Firm—Lisa K. Jorgenson; E. Russell Tarleton; SEED IP Law Group PLLC

#### (57) ABSTRACT

An inertial sensor having an inner stator and an outer rotor that are electrostatically coupled together by mobile sensor arms and fixed sensor arms. The rotor is connected to a calibration microactuator comprising four sets of actuator elements arranged one for each quadrant of the inertial sensor. There are two actuators making up each set. The actuators are identical to each other, are angularly equidistant, and each comprises a mobile actuator arm connected to the rotor and bearing a plurality of mobile actuator electrodes, and a pair of fixed actuator arms which are set on opposite sides with respect to the corresponding mobile actuator arm and bear a plurality of fixed actuator electrodes. The mobile actuator electrodes and fixed actuator electrodes are connected to a driving unit which biases them so as to cause a preset motion of the rotor, the motion being detected by a sensing unit connected to the fixed sensor

## 19 Claims, 3 Drawing Sheets

Apr. 16, 2002

Sheet 1 of 3

US 6,370,954 B1

Fig.1

Apr. 16, 2002

Sheet 2 of 3

US 6,370,954 B1

Fig. 2

Apr. 16, 2002

Sheet 3 of 3

US 6,370,954 B1

Fig. 3

Fig.4

## US 6,370,954 B1

#### 1 SEMICONDUCTOR INTEGRATED INERTIAL SENSOR WITH CALIBRATION **MICROACTUATOR**

#### TECHNICAL FIELD

The present invention regards a semiconductor integrated inertial sensor with calibration microactuator.

#### BACKGROUND OF THE INVENTION

As is known, the possibility of exploiting machinery and 10 manufacturing processes typical of the microelectronics industry enables semiconductor integrated inertial sensors to be manufactured at a low cost, at the same time guaranteeing high reliability in terms of performance.

Although these inertial sensors are advantageous from 15 various points of view, they present the drawback that their calibration is very complex, as well as costly, in that it is difficult to calibrate them at a wafer level.

In addition, the inertial sensors thus obtained have an offset and output/input sensitivity that depends upon the parameters of the process of fabrication, and consequently must be suitably calibrated.

In order to calibrate the sensor, one first known solution involves shaking of the inertial sensor, already inserted in its 25 own package, on an electrodynamic or piezoelectric actuator validated according to required standards. The choice of a particular type of actuator is assessed on the basis of the range of the operating frequencies of the inertial sensor that is to be calibrated. The calibration curve that is obtained is 30 then, generally, stored in a memory device formed in the die in which the inertial sensor itself is made. Even though this first known solution is advantageous from various points of view, it presents the drawback that it is extremely difficult to achieve at the wafer level.

A second known solution is described in U.S. Pat. No. 5,621,157, which envisages integration on one and the same wafer of the inertial sensor to be calibrated and of an electrostatic actuator, which simulates the unknown inertial

it is linear in the voltage applied;

it is precise; i.e., its operation is practically independent of the parameters of the integration process.

"Practically independent" means that the electrostatic 45 actuator has a configuration which is less sensitive than the inertial sensor is to the variations in the integration process adopted for the fabrication of the inertial sensor itself.

In addition, this second known solution is valid for all sensors, whether open loop sensors or closed loop sensors. 50

More in detail, the method and device described in U.S. Pat. No. 5,621,157 are implemented by means of an inertial sensor comprising one mobile electrode (rotor) and two fixed electrodes (stators), underneath which is set a service electrode (actuator also referred to as "ground plane"). By 55 varying the voltage applied to the service electrode and keeping the voltage applied to the mobile electrode at a fixed value, a lateral force is produced that acts upon the mobile electrode along a direction parallel to the plane in which the service electrode lies. This lateral force is independent of the 60 distance between the mobile electrode and the fixed electrodes, a distance which is markedly affected by the variations in the process of fabrication of the inertial sensor, and consequently it can be used as a reference force for the calibration of the inertial sensor itself.

Although this second solution is advantageous from a number of standpoints, it presents, however, the drawback

that, at each variation in the voltage applied to the service electrode, there is produced on the mobile electrode, in addition to the lateral force, also a vertical force in a direction orthogonal to the plane in which the service electrode is set. In addition, the lateral force has a value

other than zero only when different voltages are applied to the two fixed electrodes. Consequently, the method devised and the device made according to this second known solution are far from efficient in terms of conversion of electrical energy into mechanical energy, and are valid only for certain electrical configurations of the inertial sensor that is to be calibrated.

2

#### SUMMARY OF THE INVENTION

The technical problem that lies at the basis of the disclosed embodiments present invention is that of creating a semiconductor integrated inertial sensor with a calibration microactuator that is able to overcome the limitations and drawbacks referred to above in connection with the known

The technical problem is solved by an inertial sensor integrated in a body of semiconductor material and having a stator element and a rotor element that are electrostatically coupled together, the rotor element having a mobile mass, and a microactuator integrated in the body of semiconductor material, the microactuator connected to and coplanar with the mobile mass of the rotor element.

In accordance with another aspect of the present invention, the mobile mass is free to move in one direction and the microactuator has at least one first actuator element having at least one mobile actuator arm that is integral with the mobile mass and at least one first fixed actuator arm facing the mobile actuator arm, the mobile actuator arm and the first fixed actuator arm carrying respective multiple actuator electrodes and fixed actuator electrodes that are comb fingered together and extend in a direction substantially parallel to the first direction.

In accordance with yet another aspect of the invention, the mobile actuator electrodes extend on both sides of the quantity to be measured, and has the following characteris- 40 mobile actuator arm, and the microactuator includes a second fixed actuator arm carrying a plurality of second fixed actuator electrodes that are comb fingered with respective mobile actuator electrodes, the first and second fixed actuator arms set on opposite sides with respect to a corresponding mobile actuator arm.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The characteristics and advantages of the inertial sensor according to the embodiments invention will emerge from the ensuing description, which is given purely to provide a non-limiting illustration, with reference to the attached drawings, in which:

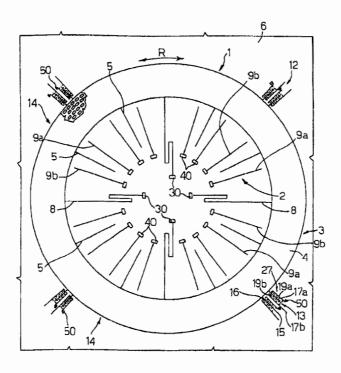

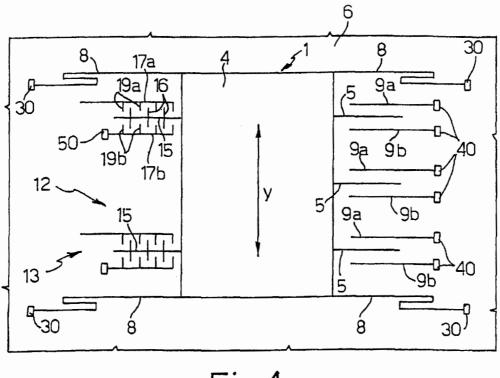

FIG. 1 schematically shows a first embodiment of an inertial sensor according to the present invention;

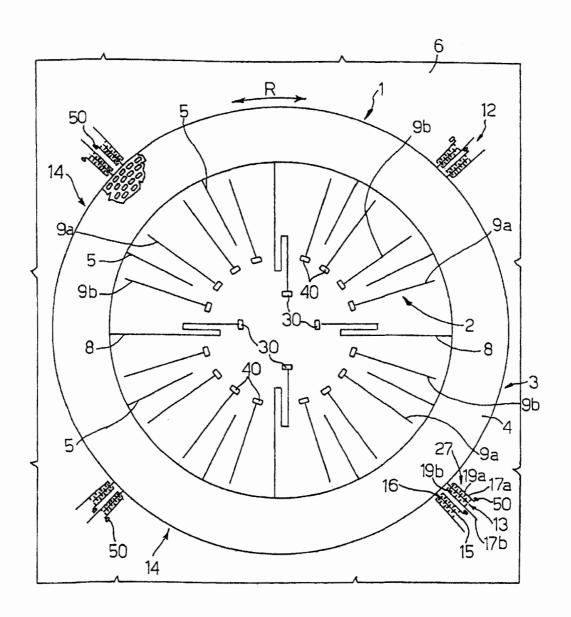

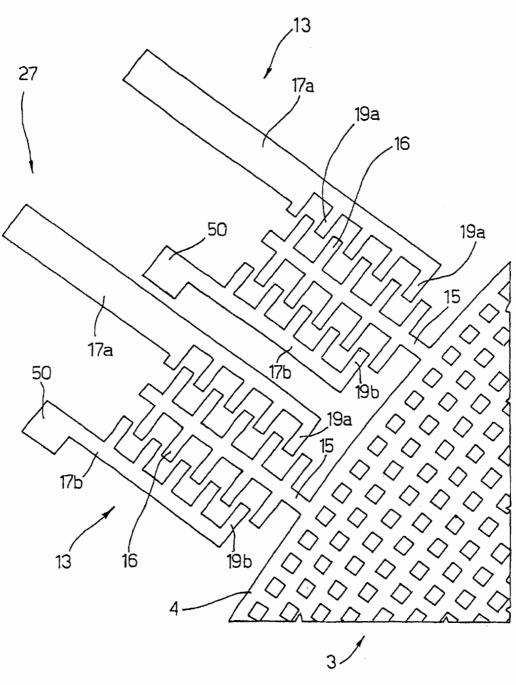

FIG. 2 shows an example of embodiment of a microactuator for calibrating the inertial sensor of FIG. 1;

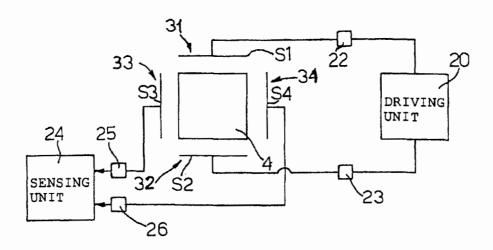

FIG. 3 shows the equivalent electrical diagram of the structure of FIG. 1; and

FIG. 4 is a schematic representation of a second embodiment of the inertial sensor according to the present inven-

#### DETAILED DESCRIPTION OF THE INVENTION

In FIG. 1, the reference number 1 designates an inertial sensor, for example an angular acceleration sensor, integrated in a semiconductor material, namely, silicon.

More in detail, the inertial sensor 1 comprises an inner stator 2, which is integral with a die 6 in which the sensor itself is made, and an outer rotor 3, capacitively coupled to the stator 2.

The rotor 3 comprises a mobile mass 4, which is suspended and has a basically annular shape, and a plurality of mobile sensor arms 5, which extend radially towards the stator 2 starting from the mobile mass 4, are identical to each other and are at the same angular distance apart, and elastic suspension and anchorage elements (springs 8) which elastically connect the mobile mass 4 to first anchoring and biasing regions 30, through which the rotor 3 and the mobile sensor arms 5 are biased at a biasing voltage Vr, typically of the value of 1.5 V.

The stator 2 comprises a plurality of pairs of fixed sensor arms 9a, 9b, one for each mobile sensor arm 5 of the rotor 3, which extend inside the mobile mass 4 itself, between the mobile sensor arms 5, and are fixed to second anchoring and biasing regions 40. The pairs of fixed sensor arms 9a, 9b are arranged in such a way that one mobile sensor arm 5 of the rotor 3 is set between a first fixed sensor arm 9a and a second fixed sensor arm 9b of a pair of fixed sensor arms 9a, 9b.

Typically, the stator 2 and the fixed sensor arms 9a, 9b are biased, through the second anchoring and biasing regions 40, at a biasing voltage Vs, which assumes values of between 1.5 V and 2.2 V.

Consequently, in the presence of angular stresses, the mobile mass 4 and the respective mobile sensor arms 5 rotate, in a micrometric way, either clockwise or counterclockwise, as indicated by the double headed arrow R.

A pair of fixed sensor arms 9a, 9b and the respective mobile sensor arm 5 set between them can be modeled as a capacitive divider made up of two variable capacitors connected in series together, in which the two outer plates are 35 defined by the fixed sensor arms 9a and 9b of the stator 2, and the inner plates are defined by the mobile sensor arms 5 of the rotor 3. In addition, the capacitive dividers made up of all the pairs of fixed sensor arms 9a, 9b and of the respective mobile sensor arms 5 are connected together in 40 parallel, with the intermediate nodes of the dividers connected together by means of the mobile mass 4. Consequently, the entire inertial sensor 1 may be represented in the way shown in FIG. 3, where the electrode SI represents the set of fixed sensor arms 9a and makes up a first variable capacitor 31, and the electrode S2 represents the set of fixed sensor arms 9b and makes up a second variable

The inertial sensor 1 also comprises an integrated microactuator 12 connected to the rotor 3.

More in detail, as shown in FIGS. 1 and 2 the microactuator 12 comprises four sets 27 of actuator elements 13 connected to and coplanar with the rotor 3. The sets 27 are arranged one for each quadrant 14 of the inertial sensor 1 and are angularly equidistant.

In particular, there are two actuator elements 13 for each set 27, which are identical to each other, and each of which comprises a mobile actuator arm 15 which is connected to the mobile mass 4 of the rotor 3 and extends radially outwards, starting from the mobile mass 4 itself. Each 60 mobile actuator arm 15 carries a plurality of mobile actuator electrodes 16, which extend on either side of the respective mobile actuator arm 15 in a basically circumferential direction, the mobile actuator electrodes 16 being positioned equidistantly along the respective mobile actuator arm 15. 65

Each actuator element 13 moreover includes a pair of fixed actuator arms 17a, 17b, which extend radially, each

pair of fixed actuator arms 17a, 17b being made up of a first fixed actuator arm 17a and a second fixed actuator arm 17b which are set on opposite sides with respect to the corresponding mobile actuator arm 15. The first fixed actuator arm 17a carries a plurality of first fixed actuator electrodes 19a, and the second fixed actuator arm 17b carries a plurality of second fixed actuator electrodes 19b.

4

The fixed actuator arms 17a, 17b are constrained to third anchoring and biasing regions 50, through which they are biased at a biasing voltage Vb, which assumes values of between 1.5 V and 5 V.

The fixed actuator electrodes 19a, 19b extend in a basically circumferential direction towards the respective mobile actuator arm 15 and are interspaced or comb fingered with the mobile actuator electrodes 16. In practice, the fixed actuator electrodes 19a, 19b and the respective mobile actuator electrodes 16, like the fixed sensor arms 9a, 9b and the mobile sensor arms 5, the fixed actuator electrodes 19a, 19b and the respective mobile actuator electrodes 16 of each actuator element 13, may be modeled as a capacitive divider made up of two capacitors connected in series together, in which the two outer plates are defined by the fixed actuator electrodes 19a, 19b, and the two inner plates are defined by the mobile actuator electrodes 16. In addition, the capacitive dividers made up of all the actuator elements 13 are connected together in parallel, with the intermediate nodes of the dividers connected together via the mobile mass 4. Consequently, the microactuator 12 may be represented in the way shown in FIG. 3, where the electrode S3 represents the set of fixed actuator electrodes 19a and forms a first actuation capacitor 33, and the electrode S4 represents the set of fixed actuator electrodes 19b and forms a second actuation capacitor 34.

FIG. 3 moreover shows a calibration circuit for calibrating the inertial sensor 1, which comprises a driving unit 20 having output terminals 22 and 23 coupled, respectively, to the fixed actuator arms 17a and 17b, and hence to the electrodes S1 and S2, and a sensing unit 24 having input terminals 25 and 26 coupled, respectively, to the fixed sensor arms 9a and 9b of the stator 2, and hence to the electrodes S3 and S4. The driving unit 20, as described more in detail in what follows, generates driving voltages V1(t) and V2(t) oscillating in opposition with respect to a constant mean value Vd(t).

Operation of the inertial sensor 1 is as follows: The driving voltages V1(t) and V2(t), equal to

V1(t)=Vb+Vd(t), and

V2(t)=Vb-Vd(t)

50 where Vb is a constant biasing voltage and Vd(t) is an alternating voltage, for example square wave or sinusoidal wave, are applied, respectively, to the fixed actuator electrodes 19a and 19b by the driving unit 20.

The voltages V1(t) and V2(t) alternately generate, on the mobile mass 4, a transverse force proportional to the number of fixed actuator electrodes 19a, 19b and to the number of interacting mobile actuator electrodes 16. In addition, given that the voltages V1(t) and V2(t) are in counterphase, this transverse force is directed first in one direction and then in the opposite direction.

In particular, this transverse force tends to move each mobile actuator electrode 16 away from the fixed actuator electrodes 19a, 19b, with respect to which the mobile actuator electrode 16 has a lower potential difference, and to bring the mobile actuator electrode 16 closer to the fixed actuator electrodes 19b, 19a, with respect to which it has a higher potential difference. In this way, the mobile mass 4

### US 6,370,954 B1

5

undergoes a rotary motion having a twisting moment  $\tau$  proportional to the biasing voltage Vb of the fixed actuator arms 17a, 17b and to the alternating voltage Vd(t), according to the following relation:

#### $\tau = \alpha * Vb * Vd(t)$

where the parameter  $\alpha$  is the precision of the microactuator 12 and depends upon the number of pairs of electrodes, their thickness and relative distance, according to the following relation:

#### $\alpha=4*\epsilon_0*N*R_m*t/g$

where  $\epsilon_0$  is the electric constant, N is the number of 15 electrodes,  $R_m$  is the distance of the electrodes from the center of rotation, t is the thickness of the electrodes (which coincides with the thickness of the polysilicon used for making them on the wafer), and g is the distance between the electrodes.

The twisting moment  $\tau$  is independent of the relative displacement between the fixed actuator electrodes 19a, 19b and the mobile actuator electrodes 16 in that it depends only upon the distance g of the pairs of mobile/fixed electrodes, which is constant, and does not depend upon the area of 25 mutual facing, which is variable, given that the electrodes extend substantially parallel to the direction of motion R of the rotor 3, and hence of the mobile electrodes 15.

The twisting moment  $\tau$ , to which the mobile mass 4 is subjected, thus determines a modulation in phase opposition 30 of the capacitances of the two variable capacitors 31, 32, the two outer plates of which are defined by the fixed sensor arms 9a, and 9b of the stator 2, and the two inner plates of which are defined by the mobile sensor arms 5 of the rotor 3. Of these two variable capacitors 31, 32, the one defined 35 by the mobile sensor arms 5 and by the fixed sensor arm 9a, 9b that is at a smaller distance makes up the effective capacitor, which determines the generation of the sensing signal that indicates the twisting moment  $\tau$  to which the mobile mass 4 is subjected.

This sensing signal is then sent to the input terminals 25 and 26 of the sensing unit 24, which uses it as a reference signal for calibrating the inertial sensor 1.

The advantages that may be obtained with the inertial sensor described herein are the following: In the first place, 45 the actuator elements 13 are defined on silicon together with the mobile mass 4, and consequently do not require additional fabrication phases. In addition, the inertial sensor 1 is more efficient as regards the conversion of electrical energy into mechanical energy, because the microactuator 12 does 50 not generate any force that acts perpendicularly on the mobile mass 4. Furthermore, since the transverse force that acts on the mobile mass 4 is independent of the biasing voltages applied to the rotor 3 and the stator 2 of the inertial sensor 1, calibration of the inertial sensor 1 is independent 55 of its own operating voltage. The last two advantages described are very important in that they render the inertial sensor 1 less costly in terms of energy and, above all, render the circuit configuration of the microactuator 12 independent of the circuit configuration of the inertial sensor 1 (for 60 example, sigma delta, frequency modulation). In addition, the comb finger configuration chosen for the fixed actuator electrodes 19a, 19b and mobile actuator electrodes 16 is not affected by the problem of electrostatic softening (i.e., reduction in the rigidity of the system). Consequently, the 65 characteristics of the actuator are not modified, and the latter may exert a force independent of the displacement.

Furthermore, for the fabrication of the inertial sensor 1 any type of micromachining technology may be used (for example, surface or epitaxial micromachining, metal electroplating, etc.).

6

Finally, it is clear that numerous modifications and variations may be made to the inertial sensor described and illustrated herein, all falling within the scope of the inventive idea as defined in the attached claims and the equivalents thereof.

For example, the number of sets 27 of actuator elements 13 and the number of actuator elements 13 in each set 27 could be different from what has been described; in particular, it would be possible to envisage even a single actuator element 13 connected to the mobile mass 4 of the rotor 3, or else two actuator elements 13 could be envisaged, set on diametrically opposite sides of the mobile mass 4.

In addition, the inertial sensor 1 may be of a linear type, as shown in FIG. 4, in which the various parts of the inertial sensor are indicated by the same reference numbers as those used in FIG. 1. In this case, the microactuator 12 is driven so as to impress on the mobile mass 4 a vibratory motion along a direction Y, and the mobile actuator electrodes 16 and fixed actuator electrodes 19a, 19b are parallel to the direction Y.

What is claimed is:

- 1. An inertial sensor integrated in a body of semiconductor material, comprising: a stator element and a rotor element that are electrostatically coupled together, said rotor element comprising a mobile mass, and microactuator means integrated in said body of semiconductor material, said microactuator means connected to and coplanar with said mobile mass of said rotor element.

- 2. The inertial sensor of claim 1, wherein said mobile mass is free to move in one direction and said microactuator means comprise at least one first actuator element having at least one mobile actuator arm that is integral with said mobile mass and at least one first fixed actuator arm facing said mobile actuator arm, said mobile actuator arm and said first fixed actuator arm carrying respective mobile actuator electrodes and first fixed actuator electrodes that are comb fingered together and extend in a second direction substantially parallel to said one direction.

- 3. The inertial sensor of claim 2, wherein in that said mobile actuator electrodes extend on both sides of said mobile actuator arm and said microactuator means comprise a second fixed actuator arm carrying a plurality of second fixed actuator electrodes which are comb fingered with respective mobile actuator electrodes, said first and second fixed actuator arms being set on opposite sides with respect to a corresponding mobile actuator arm.

- 4. The inertial sensor of claim 3, wherein said mobile mass has an annular shape; said mobile actuator arm extends radially outwards from said mobile mass; said first and second fixed actuator arms extend radially towards said mobile mass; said mobile actuator electrodes extend in a substantially circumferential direction and are set equidistantly apart from one another along said mobile actuator arm; and said first and second fixed actuator electrodes extend in a substantially circumferential direction.

- 5. The inertial sensor of claim 3, wherein said rotor element moreover comprises a plurality of mobile sensor arms that extend from said mobile mass, and said stator element comprises a plurality of pairs of fixed sensor arms facing said mobile sensor arms, each pair of fixed sensor arms comprising a first fixed sensor arm and a second fixed sensor arm that are set on opposite sides with respect to the corresponding mobile sensor arm.

#### US 6,370,954 B1

10

7

6. The inertial sensor of claim 4, wherein the inertial sensor constitutes an angular acceleration sensor.

7. The inertial sensor of claim 3, wherein said one direction is a rectilinear direction, and said sensor constitutes a sensor of rectilinear motion.

8. The inertial sensor of claim 3, further comprising a driving unit having output terminals coupled to said fixed actuator arms and a sensing unit having input terminals coupled to said fixed sensor arms.

9. The inertial sensor of claim 2, wherein said microactuator means comprise further actuator elements that are identical to said at least one first actuator element, said at least one first actuator element and further actuator elements being set symmetrically with respect to said mobile mass.

10. The inertial sensor of claim 1, wherein said microactuator means comprise at least one set of actuator elements, each set of actuator elements comprising at least two actuators that are identical to one another and angularly equidistant from one another.

11. An inertial sensor system formed in a body of semiconductor material, comprising:

a stator and a rotor electrostatically coupled together by mobile sensor arms and fixed sensor arms;

a calibration device coupled to the rotor;

- a drive unit coupled to the calibration device, the calibration device and the drive unit configured to cause a 25 preset motion of the rotor; and

- a sensing unit coupled to the stator and configured to sense the motion of the rotor.

- 12. The system of claim 11, wherein the calibration device comprises a microactuator comprising at least one first 30 actuator element having at least one mobile actuator arm that is integral with the rotor and at least one fixed actuator arm facing the mobile actuator arm, the mobile actuator arm and the fixed actuator arm having mobile actuator electrodes and fixed actuator electrodes, respectively, that are comb fingered together.

- 13. The system of claim 11, wherein the calibration device comprises a microactuator that comprises four sets of actuator elements arranged one for each quadrant of the inertial sensor.

8

14. The system of claim 13, wherein each set of the four sets of actuator elements comprises first and second actuators that are identical to each other and are angularly equidistant apart.

15. The system of claim 14, wherein each actuator comprises a mobile actuator arm connected to the rotor and having a plurality of mobile actuator electrodes, and a pair of fixed actuator arms formed on opposite sides of the mobile actuator arm and having a plurality of fixed actuator electrodes.

16. The system of claim 15, wherein the mobile actuator electrodes and the fixed actuator electrodes are connected to the driving unit, and the driving unit is configured to bias the mobile actuator electrodes and the fixed actuator electrodes to cause the preset motion of the rotor.

17. The system of claim 13, wherein the microactuator is coupled to and coplanar with the rotor.

18. The system of claim 17, wherein the rotor comprises a mobile mass that is free to move in a first direction, and the microactuator comprises at least one actuator having at least one mobile actuator arm that is integral with the mobile mass and first and second fixed actuator arms facing the mobile actuator arm, the mobile actuator arm and the first and second fixed actuator arms carrying respective mobile actuator electrodes and fixed actuator electrodes that are comb fingered together and extend in a second direction substantially parallel to the first direction.

19. The system of claim 18, wherein the mobile mass has an annular shape, and the mobile actuator arm extends radially outwards from the mobile mass; the first and second fixed actuator arms extend radially towards the mobile mass; the mobile actuator electrodes extend in a substantially circumferential direction and are set equidistantly apart from one another along the mobile actuator arm; and the first and second fixed actuator electrodes extend in a substantially circumferential direction.

\* \* \* \* \*

# **EXHIBIT B**

Case3:13-cv-01116-JCS Document1 Filed03/12/13 Page22 of 31

# United States Patent [19]

Nicholls et al.

[11] Patent Number:

6,034,419

[45] Date of Patent:

Mar. 7, 2000

#### [54] SEMICONDUCTOR DEVICE WITH A TUNGSTEN CONTACT

[75] Inventors: Howard Charles Nicholls; Michael

John Norrington, both of Cardiff; Michael Kevin Thompson, Newport,

all of United Kingdom

[73] Assignee: Inmos Limited, Bristol, United

Kingdom

[21] Appl. No.: 08/161,604

[22] Filed: Dec. 6, 1993

[56]

#### Related U.S. Application Data

[62] Division of application No. 07/739,381, Aug. 1, 1991, abandoned, which is a continuation of application No. 07/502,526, Mar. 30, 1990, abandoned.

### [30] Foreign Application Priority Data

| Αp   | r. 7, 1989 | [GB]   | United Kingdom |            | 8907898  |

|------|------------|--------|----------------|------------|----------|

| [51] | Int. Cl.7  |        |                | Но         | 1L 23/58 |

| [52] | U.S. Cl.   |        | 257/641        | ; 257/649; |          |

| _    |            | _      |                |            | 257/763  |

| [58] | Fleld of   | Search |                |            |          |

|      |            |        | 257            | /649, 760. | 763. 369 |

#### References Clted

#### U.S. PATENT DOCUMENTS

| 4,028,717 | 6/1977  | Joy et al           | 257/404 |

|-----------|---------|---------------------|---------|

| 4,169,270 | 9/1979  | Hayes               |         |

| 4,271,582 | 6/1981  | Shirai et al        |         |

| 4,385,308 | 5/1983  | Uchida              | 357/59  |

| 4,507,853 | 4/1985  | McDavid             | 357/54  |

| 4,520,041 | 5/1985  | Aoyama et al        | 357/54  |

| 4,560,582 | 12/1985 | Ichikawa            | 427/88  |

| 4,592,802 | 6/1986  | Deleonibus et al    | 156/644 |

| 4,710,241 | 12/1987 | Komatsu             | 437/162 |

| 4,764,248 | 8/1988  | Bhattacherjee et al | 357/54  |

| 4,782,037 | 11/1988 | Tomozawa et al      | 257/640 |

| 4,878,096 | 10/1989 | Shirai et al        | 357/42  |

| 4,964,143 | 10/1990 | Haskell             | 257/640 |

| 4,981,550 | 1/1991 | Huttemann et al 156/643 |

|-----------|--------|-------------------------|

| 4,990,467 | 2/1991 | Lee et al 437/192       |

| 5,143,861 | 9/1992 | Turner 437/52           |

#### FOREIGN PATENT DOCUMENTS

| 8928     | 3/1980  | European Pat. Off         |

|----------|---------|---------------------------|

| 1208030  | 10/1970 | United Kingdom .          |

| 1574 582 | 9/1980  | United Kingdom H01L 21/18 |

| 2206234A | 12/1988 | United Kingdom H01L 21/28 |

#### OTHER PUBLICATIONS

C. Kaanta, et. al., "Submicron Wiring Technology with Tungston and Planarization", IEDM Conference Proceedings, *IEEE*, 9.3, pp. 209-212 (1987).

R. Blewer, et al., "Conditions for Tunnel Formation in

R. Blewer, et al., "Conditions for Tunnel Formation in LPCVD Tungston Films on Single Crystalsilicon", *Materials Research Society*, pp. 115–122 (1988).

E. Broadbent, et al. "Some Recent Observations on Tunnel Defect Formation During High Temperature Post-Deposition Anneal of CVD W on SI", Materials Research Society, pp. 111-113 (1988).

(List continued on next page.)

Primary Examiner—J. Carroll

Attorney, Agent, or Firm—McDermott, Will & Emery

#### 57] ABSTRACT

A method of fabricating a tungsten contact in a semiconductor device comprises providing an oxide layer on a region of a silicon substrate; depositing a sealing dielectric layer over the oxide layer; and depositing an interlevel dielectric layer over the sealing layer. The interlevel dielectric layer, the sealing dielectric layer and the oxide layer are then etched through as far as the substrate thereby to form a contact hole and to expose the said region. A dopant is implanted into the said region whereby the implanted dopant is self-aligned to the contact hole. The substrate is thermally annealed. Tungsten is selectively deposited in the contact hole and an interconnect layer is deposited over the deposited tungsten contact. The invention also provides a semiconductor device which incorporates a tungsten contact and which can be fabricated by the method.

### 13 Claims, 3 Drawing Sheets

# 6,034,419

Page 2

#### OTHER PUBLICATIONS

R. Blewer, et al., "Detrimental Effects of Residual Silicon Oxides on LPCVD Tungsten Depositions in Shallow Junction Devices", *Materials Research Society*, pp. 235-246 (1987).

J.T. Clemens, "NMOS Technology-A Review", The Electrochemical Society, *Extended Abstracts*, vol. 79-2, pp. 812-814 (1979).

812-814 (1979). V. Wells, "Tungston and Other Refractory Metals for VLSA Applications" 1985 Matt. Res. Soc., (Pittsburg, PA, USA). V.V.S. Rana, et al. "Selective Tungston Plugs on Silicon for Advanced CMOS Devices" *Technical Digest of the International Electron Devices Meeting*, Dec. 6, 1987, IEEE, Washington DC, pp. 862–864.

S. Sachdev et al. Blanket Tungston Applications in VLSI Processing, 1985 Material Research Society, pp. 475-482.

S.M. Sze, "Semiconductor Devices Physics and Technology", John Wiley & Sons, New York (1985) pp. 113, 360-361.

Mar. 7, 2000

Sheet 1 of 3

6,034,419

Fig.1. PRIOR ART

Fig.2.

Fig. 3.

Fig. 4.

Mar. 7, 2000

Sheet 2 of 3

6,034,419

Fig.5.

Fig.6.

Fig.7.

Fig.8.

Mar. 7, 2000

Sheet 3 of 3

6,034,419

Fig.9.

Fig.10

Fig.11.

# SEMICONDUCTOR DEVICE WITH A TUNGSTEN CONTACT

This patent is a divisional application of Ser. No. 07/739, 381, filed on Aug. 1, 1991, now abandoned, which is a 5 Continuation of U.S. Ser. No. 07/502,526 filed Mar. 30, 1990, now abandoned.

#### BACKGROUND OF THE INVENTION

The present invention relates to semiconductor devices 10 and fabrication thereof. In particular, the present invention relates to a method of fabricating a tungsten contact in a semiconductor device and to a semiconductor device incorporating such a tungsten contact.

In the manufacture of the semiconductor devices it is 15 necessary to provide electrically conductive contacts and interconnect layers in order to connect electrically various parts of the device to each other and to external circuitry. Manufacturers of semiconductor devices have appreciated that there is a need further to reduce the size of the devices 20 by, inter alia, reducing the size of the electrical contacts and also the interconnect pitch, without reducing the reliability of the devices and while still keeping the surface planar so that subsequent interconnect layers can be formed. Conventional methods of depositing metal contacts, such as by 25 sputtering, have great difficulty in depositing enough material into the contact holes in order to form reliable electrical connections between the substrate silicon and the metal contact. In addition, the resulting topology is non-planar and can place severe constraints on the complexity of the inter- 30 connect layers. These technical problems are particularly encountered in the manufacture of CMOS devices which may require multiple interconnect layers.

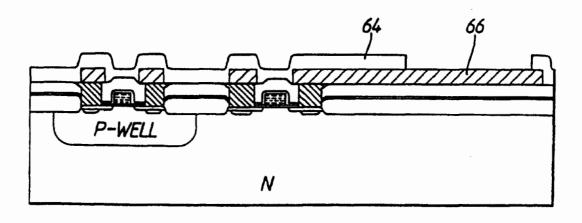

A typical conventional CMOS device as shown in FIG. 1 which is a cross-section through a CMOS device. In this 35 known device 2, metal contacts 4 are provided to connect the sources and drains 6,8 of the device 2 to interconnect layers such as metal interconnect layer 10 which defines a bonding pad 12 for connection to external circuitry. The metal contacts 4 are disposed in contact holes 14 defined in the 40 dielectric layers comprised of the field oxide layer 16 the interlevel dielectric layer 18, and the gate oxide layer 22. The method of manufacturing this known device has the limitation that the contact hole 14 must be wide enough and have the correct profile (i.e. it is wider at the top than at the 45 bottom) to allow a limited amount of metal to enter the contact hole 14 thereby to form the contact 4. The obtainable reduction in size of the contact hole is limited by the step coverage capability of conventional sputtering systems. In addition, the metal line width has to be large enough to cover 50 the contact by at least the possible misalignment of the pattern so that the contact is protected during plasma etching of the metal to form the desired patterning of the interconnect layer. Furthermore, by making the contact hole large, any subsequent dielectric layer not only has to be capable of 55 covering the non-planar surface resulting from previous interconnect layers but also has to cover the profile of the metal when it goes down into a contact hole. This requires an involved technique for planarising the next dielectric layer which must be used if further interconnect layers are 60 required. From FIG. 1 it will be seen that in the resultant structure the upper surface of the top dielectric layer 20 is non-planar in the region of the metal contacts 4 and it will also be seen that the width of the metal contacts formed is substantially greater than the width of the corresponding 65 source and drain regions of the semiconductor device which are not covered by the gate and field oxide layers 22,16.

2

It has been proposed to use tungsten plug technology as a means to enhance semiconductor device planarization and to reduce interconnect pitch design rules. For example, in a paper entitled "Submicron wiring technology with tungsten and planarization" (by C. Kaanta, W. Cote, J. Cronin, K. Holland, P. Lee, and T. Wright, IEDM Conference Proceedings, 9.3, p. 209, 1987) it is disclosed that vercial contact studs can be formed from tungsten. However, it is known that such tungsten plug technology suffers substantial technical problems which are related to the agressive chemistry of the selective tungsten deposition process. In this process, tungsten is deposited by chemical vapour deposition (CVD) and the deposition is auto-catalyzed on silicon or metal surfaces and hence tungsten only deposits in contact holes which have silicon (or tungsten) exposed and not on the dielectric itself. The agressive flourine chemistry can also cause significant damage to the silicon interface and to the source/drain junction. It is well known that particular problems which can occur in the known tungsten plug technology are the phenomenon of tunnelling (which is the formation of microscopic filamentary voids in the silicon beneath the chemically vapour deposited tungsten); encroachment of the tungsten underneath the silicon/ dielectric interface; consumption of the silicon by the tungsten thereby lowering the tungsten/silicon interface; and high contact resistances (especially for p+-doped silicon substrates) in the source/drain regions. A paper entitled "Conditions for tunnel formation in LPCVD tungsten films on single crystal silicon" (by R. Blewer, T. Headley and M. Tracy, Tungsten and Other Refractory Metals for VLSI Applications, ed. V. Wells, MRS Pittsburgh Pa., p.115, 1987), a paper entitled "Some recent observations on tunnel defect formation during high temperature post-deposition anneal of CVD W on Si" (by E. Broadbent, D. Sadana, A. Morgan, J. Flanner and R. Ellwanger, Workshop on Tungsten and Other Refractory Metals for VLSI Applications, ed. V. Wells, MRS Pittsburgh Pa., P. 111, 1987) and a paper entitled "Detrimental effects of residual silicon oxides on LPCVD tungsten depositions in shallow junction devices" (by R. Blewer and M. Tracy, Workshop on Tungsten and Other Refractory Metals for VLSI Applications, ed. E. Broadbent, MRS Pittsburgh Pa., P. 235, 1986) all disclose specific problems which can be encountered in the deposition of tungsten on silicon. These articles suggest procedures for reducing the occurrence of the defects in the silicon which can occur on CVD tungsten deposition. For example, it has been suggested carefully to choose the operating regimes in the CVD reactor and to control the gas purity. It has also been noted that pre-cleaning of the silicon surface can reduce the occurrence of defects in the silicon. However, the prior art fails to teach a method of fabricating a tungsten contact in the semiconductor device which can properly control the occurrence of defects such as tunnelling, encroachment of tungsten underneath the silicon/dielectric interface, consumption of the silicon and high contact resistances without compromising the inherent advantages of tungsten plug processing in a viable manufacturing technique.

British Patent Specification No. 2206234 discloses a multi-layer metallisation method for integrated circuits in which a metal sandwich structure of refractory metal/aluminium/refractory metal or alloy is deposited onto a semiconductor substrate. The refractory metal is titanium or an alloy of titanium and tungsten. Portions of the sandwich structure are removed to form interconnect and bonding pad conductors.

British Patent Specification No. 1574582 discloses a method of making a surface barrier connection to a piece of

semiconductor material in which a contact metal layer is deposited over an oxide layer on a silicon substrate. The oxide layer has a window exposing the silicon substrate. The contact metal is reacted with the silicon to form a silicide.

British Patent Specification No. 1208030 discloses a 5 semiconductor device having metal layers contacting regions of a silicon substrate. The metal layers extend through holes in an insulating film including a lower insulating layer, a middle glass layer and an upper insulating layer. The glass layer is composed of phosphorus oxide.

#### SUMMARY OF THE INVENTION

The present invention aims at least partially to overcome the above specified problems of the prior art.

The present invention accordingly provides a method of fabricating a tungsten contact in a semiconductor device, which method comprises the steps of:

- (a) providing an oxide layer on a region of a silicon substrate;

- (b) depositing a sealing dielectric layer over the oxide layer;

- (c) depositing an interlevel dielectric layer over the sealing layer;

- (d) etching through the interlevel dielectric layer, the sealing dielectric layer and the oxide layer as far as the substrate thereby to form a contact hole and to expose the said region;

- (e) implanting a dopant into the said region whereby the implanted dopant is self-aligned to the contact hole;

- (f) thermally annealing the substrate;

- (g) selectively depositing tungsten in the contact hole; and

- (h) depositing an interconnect layer over the deposited tungsten contact.

Preferably, the semiconductor device is a CMOS device, and a plurality a method according to any foregoing claim wherein the semiconductor device is a CMOS device, and wherein a plurality of the tungsten contacts are fabricated over a corresponding number of the said regions, the said regions being divided into pairs of such regions, each pair of regions defining a source and a drain for a respective semiconductor element, and wherein a polysilicon gate is deposited on the said oxide layer between each pair of source and drain regions.

Here onto respective gat tively doped regions of oxide;

FIG. 3 shows a struct an interlevel dielectric layer;

FIG. 5 shows the structure of the said regions of oxide;

FIG. 5 shows a struct an interlevel dielectric layer.

More preferably a first pair of source and drain regions is initially doped with an N+ dopant and is disposed in a P-doped well in the substrate which is N-doped, and during the implantation step (e) an N-dopant is implanted into the first pair of source and drain regions, and a second pair of source and drain regions is initially doped with a P+ dopant and is disposed in the N-doped substrate, and during the implantation step (e) a P-dopant is implanted into the second pair of source and drain regions.

The present invention also provides a semiconductor 55 device incorporating a tungsten contact, the device including a silicon substrate having a region doped with a dopant; a tungsten contact disposed on the region and extending upwardly away therefrom, the tungsten contact being disposed in a contact hole which is defined in a series of 60 dielectric layers comprising a bottom layer of oxide on the substrate, a sealing layer on the oxide layer, the sealing layer acting to seal the underlying oxide layer, and an interlevel layer on the sealing layer; and an interconnect layer which is disposed over the tungsten contact.

The said region may constitute part of a field effect transistor.

4

Preferably, the semiconductor device is a CMOS device and the device incorporates a plurality of the tungsten contacts which are each disposed on a respective one of a corresponding plurality of the regions, the said regions being divided into pairs of such regions, each pair of regions defining a source and a drain for a respective semiconductor element, and wherein a polysilicon gate is disposed on the said oxide layer between each pair of source and drain regions.

The present invention further provides a method of fabricating a tungsten contact in a semiconductor device, which method comprises the steps of:

- (a) providing an oxide layer on a region of a silicon substrate;

- (b) depositing a dielectric layer over the oxide layer;

- (c) etching through the dielectric layer and the oxide layer as far as the substrate thereby to form a contact hole and to expose the said region;

- (d) implanting a dopant into the said region whereby the implanted dopant is self-aligned to the contact hole;

- (e) thermally annealing the substrate;

- (f) selectively depositing tungsten in the contact hole; and

- (g) depositing an interconnect layer over the deposited tungsten contact.

#### BRIEF DESCRIPTION OF THE DRAWINGS

An embodiment of the present invention will now be described by way of example only with reference to the accompanying drawings in which:

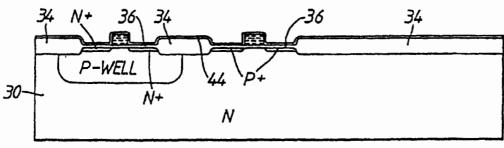

FIG. 1 is a section through a known CMOS semiconductor device;

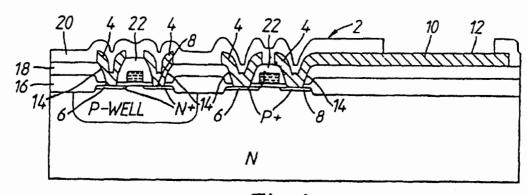

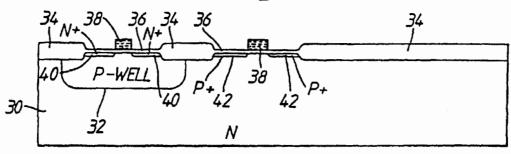

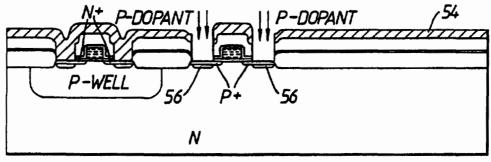

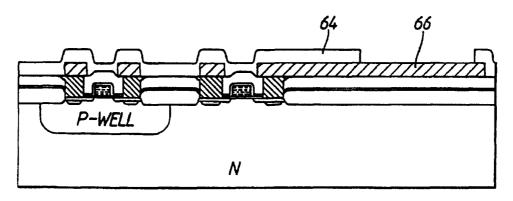

FIG. 2 shows a section through a silicon wafer structure in a CMOS process after polysilicon gates have been deposited onto respective gate oxide layers which cover respectively doped regions of the silicon between regions of field oxide:

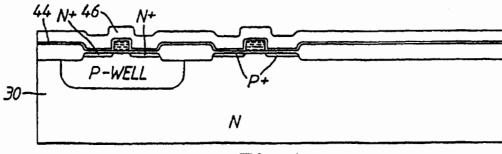

FIG. 3 shows a structure of FIG. 2 after deposition of a sealing dielectric layer;

FIG. 4 shows a structure of FIG. 3 after the deposition of an interlevel dielectric layer over the sealing layer;

FIG. 5 shows the structure of FIG. 4 after reflow of the interlevel dielectric layer and the etching of contact holes;

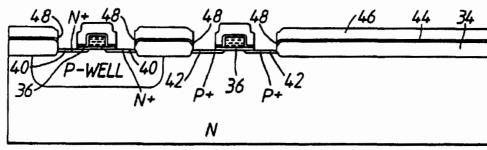

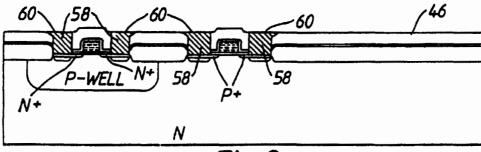

FIG. 6 shows the structure of FIG. 5 after the deposition of a photoresist pattern and during implantation of an N-dopant into N+-doped sources and drains;

FIG. 7 shows the structure of FIG. 6 after removal of the photoresist pattern of FIG. 6 and subsequent application of a second photoresist pattern and during implantation of a P-dopant into P+-doped regions of the silicon;

FIG. 8 shows the structure of FIG. 7 after removal of the second photoresist pattern, a rapid thermal anneal, and selective CVD tungsten deposition in the contact holes;

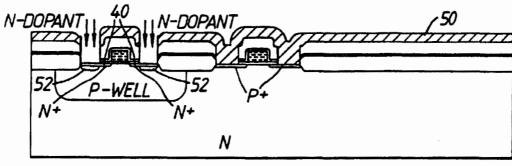

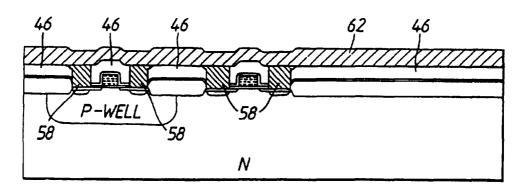

FIG. 9 shows the structure of FIG. 8 after deposition of a metal interconnect layer;

FIG. 10 shows the structure of FIG. 9 after patterned etching of the interconnect layer; and

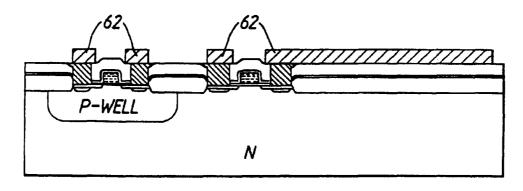

FIG. 11 shows the structure of FIG. 10 after subsequent deposition of a patterned dielectric layer over the metal interconnect layer.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Referring to FIG. 2, there is shown a section through a silicon wafer structure after conventional CMOS processing.

•

The structure comprises a substrate 30 of N-doped silicon in which a P-well 32 has been defined by implantation and well drive in of a p-dopant such as boron. Regions 34 of field oxide are grown on the silicon layer 30 and a gate oxide layer 36 is grown over the silicon layer 30 between the field oxide regions 34. Subsequently, polysilicon gates 38 are formed on the gate oxide layer 36. A sequence of masking and dopant implantation steps is carried out to define N+-source and drain regions 40 in the P-well 32 and P+-source and drain regions 42 in the N-doped substrate 30. 10 The gates 38 are also doped with the appropriate N- or P-dopant as the case may be. It should be noted that this conventional CMOS processing is independent of the choice of CMOS structure, which may be N-well, P-well or twinwell, and is independent of the transistor formation and the 15 isolation formation.