US 20150108525A1

### (19) United States

## (12) Patent Application Publication

Chae et al.

(10) Pub. No.: US 2015/0108525 A1 (43) Pub. Date: Apr. 23, 2015

# (54) LIGHT EMITTING DIODE FOR SURFACE MOUNT TECHNOLOGY, METHOD OF MANUFACTURING THE SAME, AND METHOD OF MANUFACTURING LIGHT EMITTING DIODE MODULE

(71) Applicant: Seoul Viosys Co., Ltd., Ansan-si (KR)

(72) Inventors: Jong Hyeon Chae, Ansan-si (KR); Jong Min Jang, Ansan-si (KR); Won Young Roh, Ansan-si (KR); Dae Woong Suh, Ansan-si (KR); Min Woo Kang, Ansan-si (KR); Joon Sub Lee, Ansan-si (KR); Hyun A. Kim, Ansan-si (KR)

(21) Appl. No.: 14/585,125

(22) Filed: Dec. 29, 2014

#### Related U.S. Application Data

(63) Continuation-in-part of application No. PCT/ KR2013/005254, filed on Jun. 14, 2013.

#### (30) Foreign Application Priority Data

Jun. 28, 2012 (KR) ...... 1020120070129

#### **Publication Classification**

(51) Int. Cl.

H01L 33/62 (2006.01)

H01L 33/48 (2006.01)

H01L 33/60 (2006.01)

(52) U.S. Cl.

#### (57) ABSTRACT

Provided are a light emitting diode (LED) in which a conductive barrier layer surrounding a reflective metal layer is defined by a protective insulating layer, and a method of manufacturing the same. A reflection pattern including a reflective metal layer and a conductive barrier layer is formed on an emission structure in which a first semiconductor layer, an active layer, and a second semiconductor layer are formed. The conductive barrier layer prevents diffusion of a reflective metal layer and extends to a protective insulating layer recessed under a photoresist pattern having an overhang structure during a forming process. Accordingly, a phenomenon where the conductive barrier layer is in contact with sidewalls of the photoresist pattern having an over-hang structure and the reflective metal layer forms points is prevented. Thus, LED modules having various shapes may be manufactured.

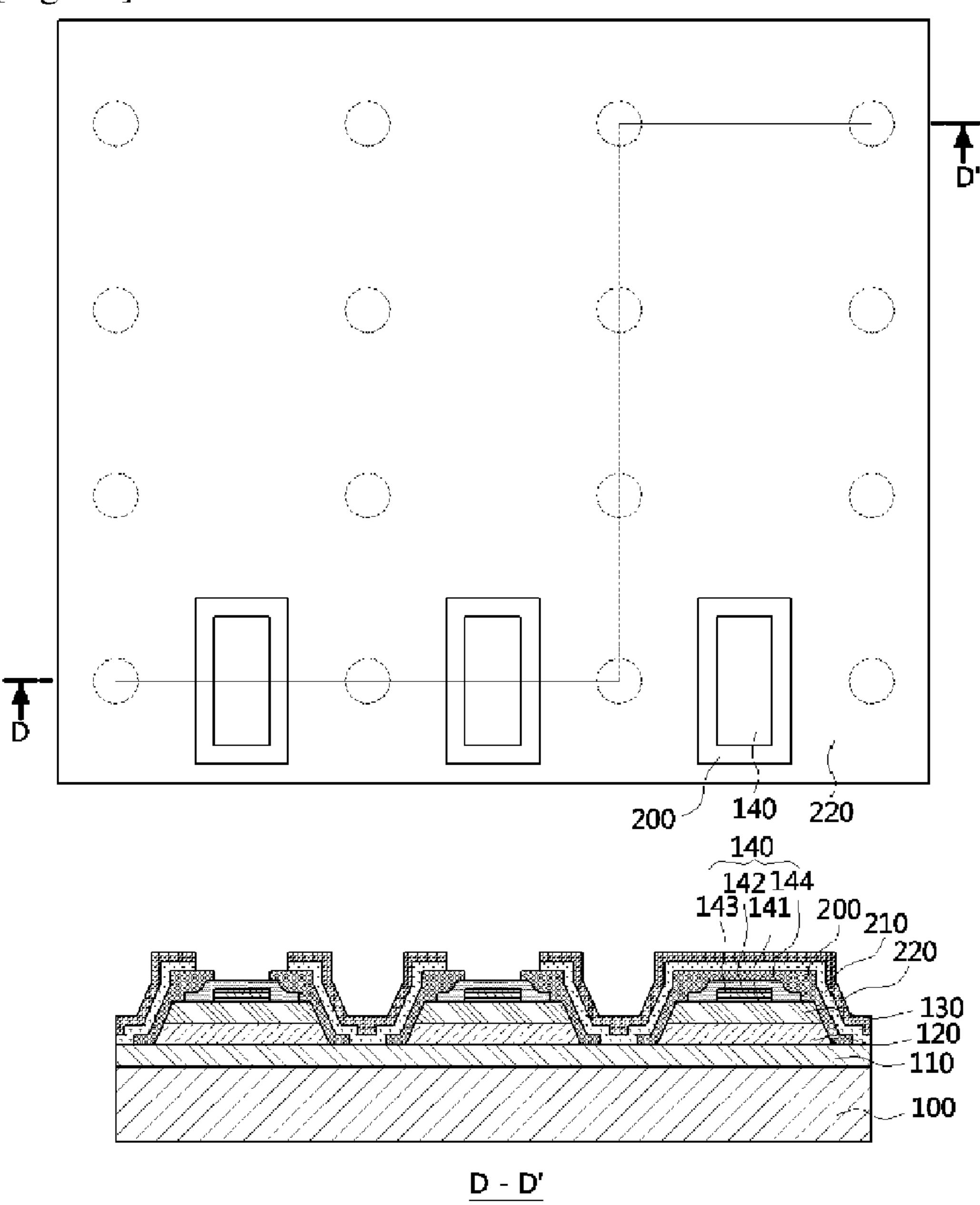

[Fig. 23]

[Fig. 24]

[Fig. 25]

[Fig. 26]

Fig. 28]

110

140 200

140

142 144

143 1411 200

130

130

130

130

130

D - D'

[Fig. 29]

[Fig. 30] 200~ 230 110 100

## LIGHT EMITTING DIODE FOR SURFACE MOUNT TECHNOLOGY, METHOD OF MANUFACTURING THE SAME, AND METHOD OF MANUFACTURING LIGHT EMITTING DIODE MODULE

### CROSS-REFERENCES TO RELATED APPLICATIONS

[0001] This patent document is a continuation-in-part application under 35 U.S.C. 111(a), 120 and 365(c) and claims priority to, and benefits of prior PCT application number PCT/KR2013/005254 filed on Jun. 14, 2013 which further claims the priority and benefits of prior Korean application number 10-2012-0070129 filed on Jun. 28, 2012. This patent document incorporates by reference the above two patent filings in their entirety.

#### TECHNICAL FIELD

[0002] The present patent document relates to a light emitting diode (LED), including an LED for surface mounting.

#### **BACKGROUND**

[0003] A light emitting diode (LED) is a device including an n-type semiconductor layer, a p type semiconductor layer, and an active layer interposed between the n type and p type semiconductor layers. When a forward electric field is applied to the n type and p type semiconductor layers, electrons and holes may be injected into the active layer and re-combine in the active layer to emit light.

[0004] In addition, an LED may include a reflection layer according to the type of a chip. For example, a flip-chip type is characterized by emitting light through a substrate. Accordingly, after a semiconductor layer is formed on the substrate, a reflection layer formed of or includes a metal is introduced on the semiconductor layer or a current spreading layer, and light is reflected by the reflection layer. Also, a barrier layer is provided on the reflection layer. The barrier layer is provided to prevent diffusion of the metal forming the reflection layer.

#### **SUMMARY**

[0005] Examples of implementations of the disclosed technology include light emitting diodes (LEDs) and associated methods of fabricated the LEDs and LED modules that include a conductive barrier layer defined by a protective insulating layer.

[0006] In some implementations, the disclosed technology can provide an LED including: a substrate, a first semiconductor layer formed on the substrate, an active layer formed on the first semi-conductor layer and configured to generate light, a second semiconductor layer formed on the active layer and having a complementary conductive type to the first semi-conductor layer, and a reflection pattern formed between protective insulating layers formed on the second semiconductor layer and configured to reflect light generated in the active layer, the reflection pattern having a conductive barrier layer contacting the protective insulating layer.

[0007] In some implementations, a method of manufacturing an LED can include: forming a first semiconductor layer, an active layer, a second semiconductor layer, and a protective insulating layer on a substrate, etching the protective insulating layer, the second semiconductor layer, and the active layer and forming a mesa region exposing a surface of the first semiconductor layer, forming photoresist patterns

having an overhang structure on the mesa region and etching the protective insulating layer exposed through a space between the photoresist patterns, forming a reflective metal layer on a surface of the second semiconductor layer that is exposed by etching the protective insulating layer, and forming a conductive barrier layer on the reflective metal layer, the conductive barrier layer extending to the protective insulating layer remaining under the photoresist pattern.

[0008] In some implementations, a method of manufacturing an LED can include: sequentially forming a first semiconductor layer, an active layer, and a second semiconductor layer on a substrate, etching the second semiconductor layer and the active layer and forming a mesa region exposing a surface of the first semi-conductor layer, forming a protective insulating layer on the mesa region and the exposed second semiconductor layer, forming photoresist patterns having an overhang structure on the mesa region and etching the protective insulating layer exposed through a space between the photoresist patterns, forming a reflective metal layer on a surface of the second semiconductor layer that is exposed by etching the protective insulating layer, and forming a conductive barrier layer on the reflective metal layer, the conductive barrier layer extending to the protective insulating layer remaining under the photoresist pattern.

[0009] In some implementations, a method of manufacturing an LED module can include: coating a first insulating layer on a structure in which a first semi-conductor layer, an active layer, a second semiconductor layer, and a reflection pattern are formed on a substrate and exposing the reflection pattern and the first semiconductor layer, forming a conductive reflection layer and a reflective barrier layer on the first insulating layer, the reflective barrier layer electrically connected to the first semiconductor layer through the conductive reflection layer and configured to expose the reflection pattern, coating a second insulating layer on the reflective barrier layer to expose the reflection pattern and exposing the reflective barrier layer electrically connected to the first semiconductor layer, and forming a first pad on the reflective barrier layer and forming a second pad on the reflection pattern.

[0010] According to the disclosed technology, protective insulating layers are formed on an emission structure including a first semiconductor layer, an active layer, and a second semiconductor layer, and a reflection pattern including a conductive barrier layer is formed between protective insulating layers.

[0011] The reflection pattern can include a reflective metal layer, a stress relaxation layer, and a conductive barrier layer. The conductive barrier layer penetrates into a lower portion of a photoresist pattern having an overhang structure during a forming process. Accordingly, the conductive barrier layer is in contact with a protective insulating layer recessed to a portion of the lower portion of the photoresist pattern. Thus, protrusion of the conductive barrier layer is prevented. Thus, process contamination caused by generation of metal particles and a drop in yield can be prevented.

[0012] In addition, a reflective barrier layer can be configured to prevent diffusion of a metallic substance formed on a conductive reflection layer during manufacture of an LED module. The reflective barrier layer can be electrically connected to a first semiconductor layer and electrically connected to a first pad that can be subsequently formed.

[0013] Furthermore, a pad barrier layer can be formed on each of pads. Accordingly, permeation or diffusion of metal

atoms during a soldering process or a bonding process is inhibited, and the pads can ensure a high conductivity.

#### BRIEF DESCRIPTION OF DRAWINGS

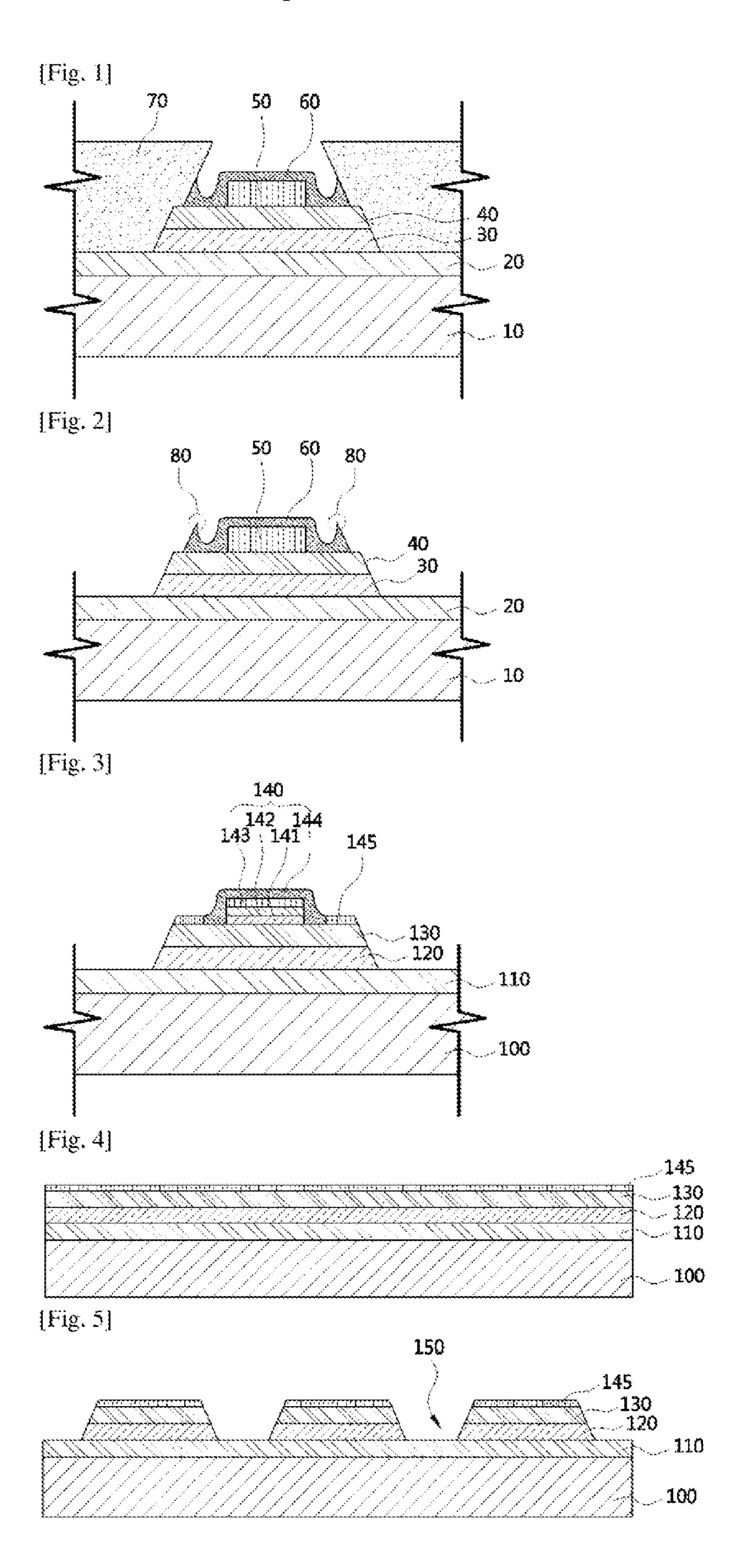

[0014] FIGS. 1 and 2 are cross-sectional views of an exemplary light emitting diode (LED) including a reflection layer and a barrier layer.

[0015] FIG. 3 is a cross-sectional view of an LED according to a first exemplary embodiment of the disclosed technology.

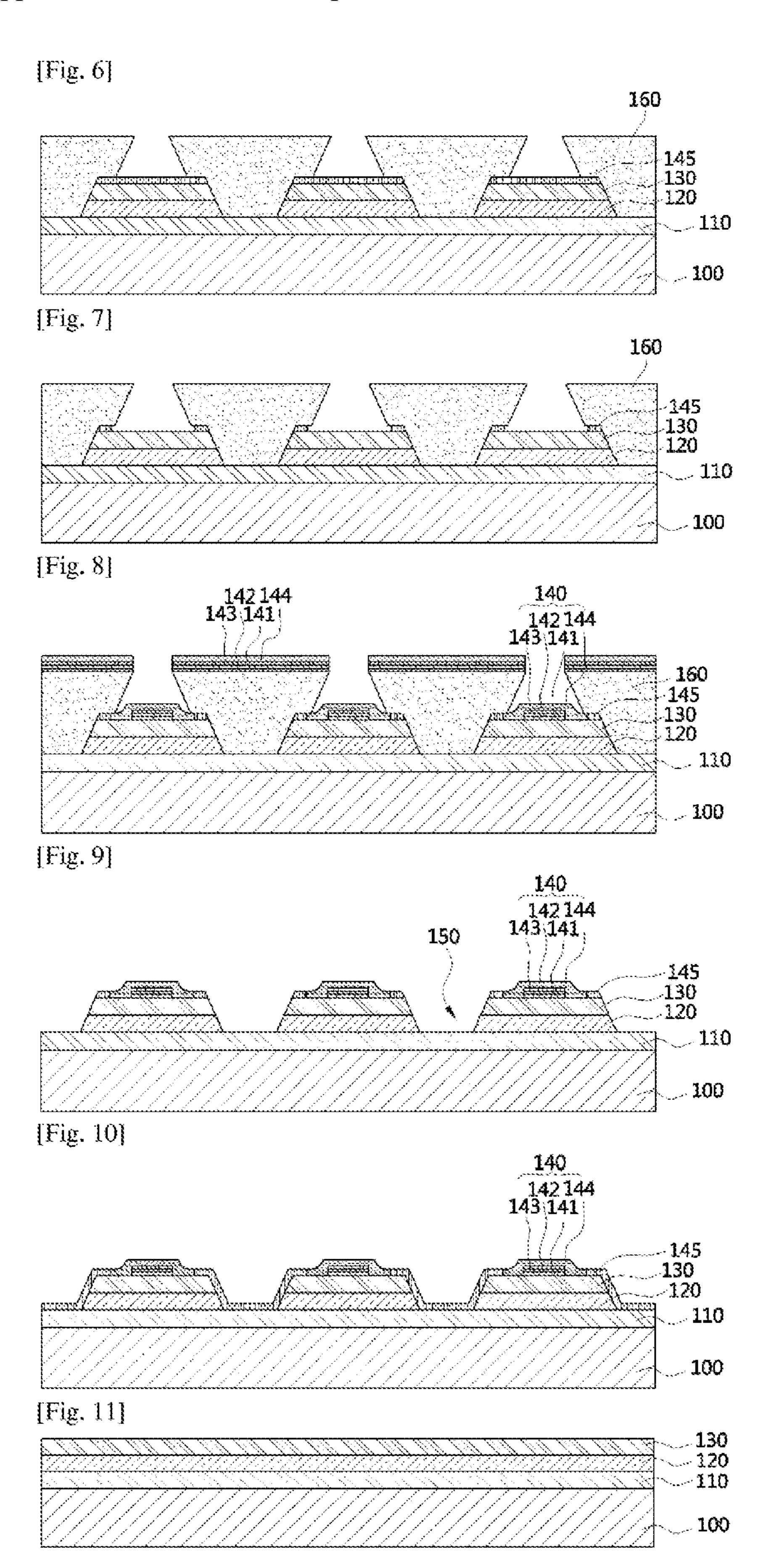

[0016] FIGS. 4 through 9 are cross-sectional views illustrating a method of manufacturing the LED of FIG. 3, according to the first exemplary embodiment of the disclosed technology.

[0017] FIG. 10 is a cross-sectional view of an LED according to a second exemplary embodiment of the disclosed technology.

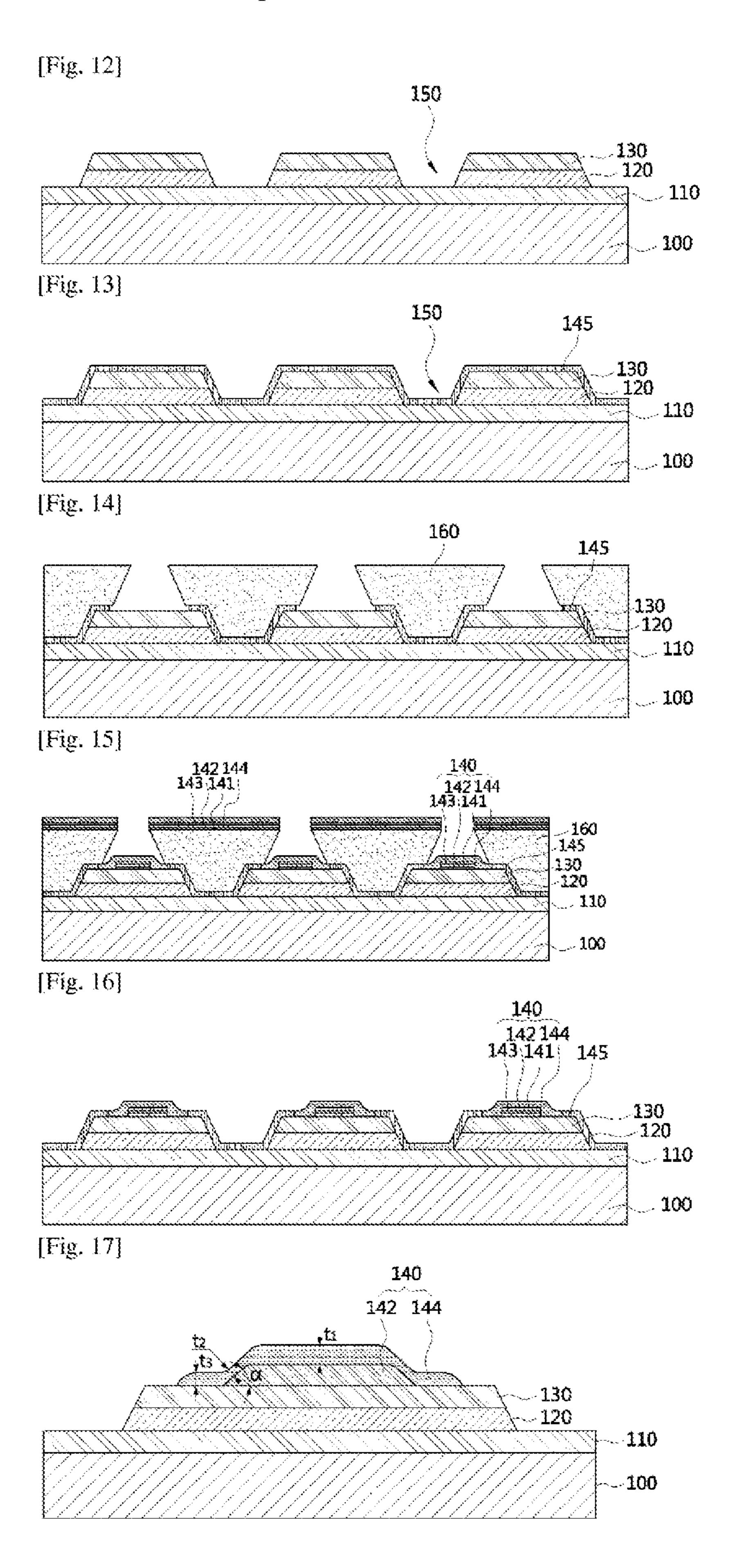

[0018] FIGS. 11 through 16 are cross-sectional views illustrating a method of manufacturing the LED of FIG. 10, according to the second exemplary embodiment of the disclosed technology.

[0019] FIG. 17 is a cross-sectional view of an LED according to a third exemplary embodiment of the disclosed technology.

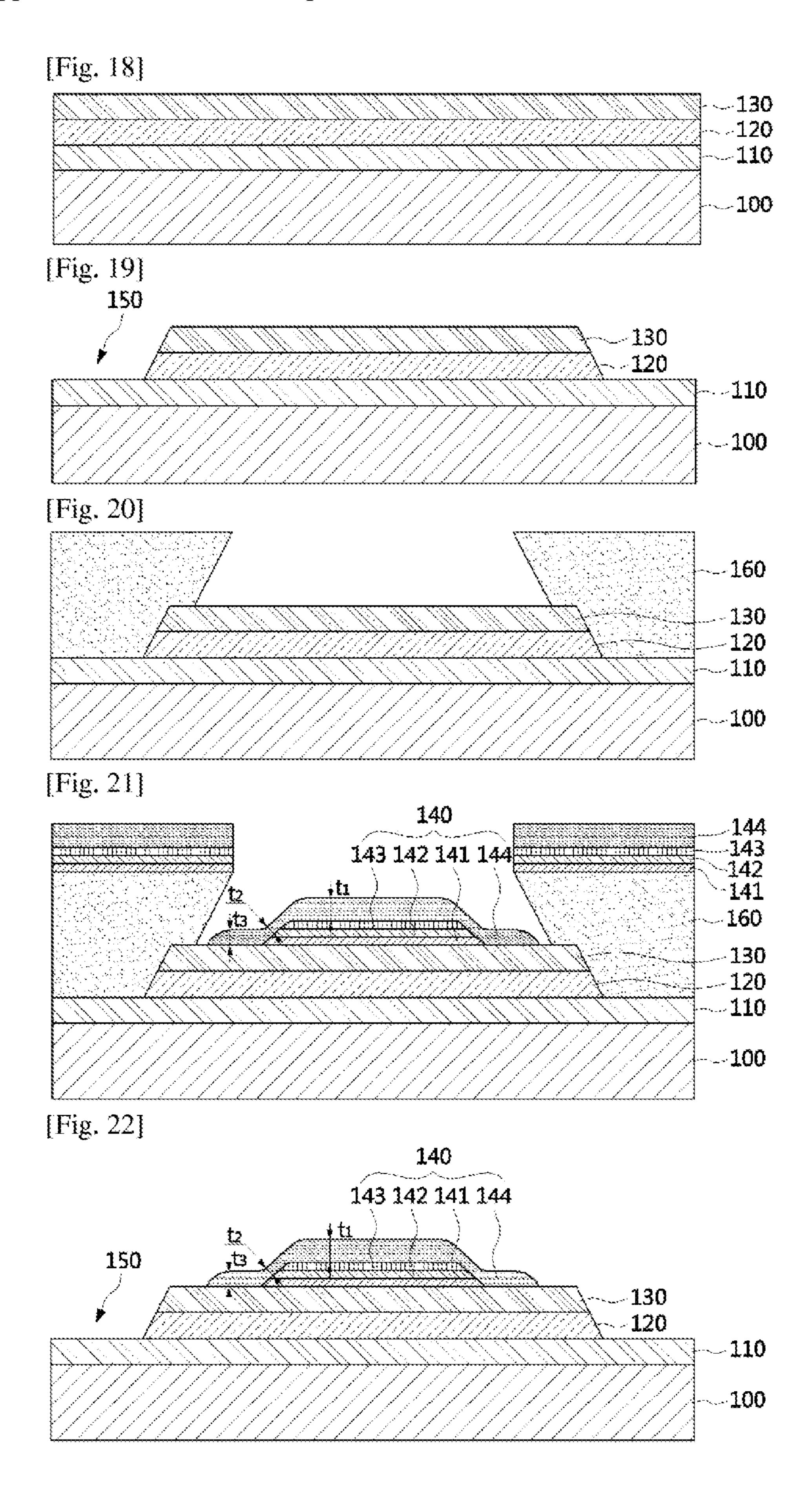

[0020] FIGS. 18 through 22 are cross-sectional views illustrating a method of manufacturing the LED of FIG. 17, according to the third exemplary embodiment of the disclosed technology.

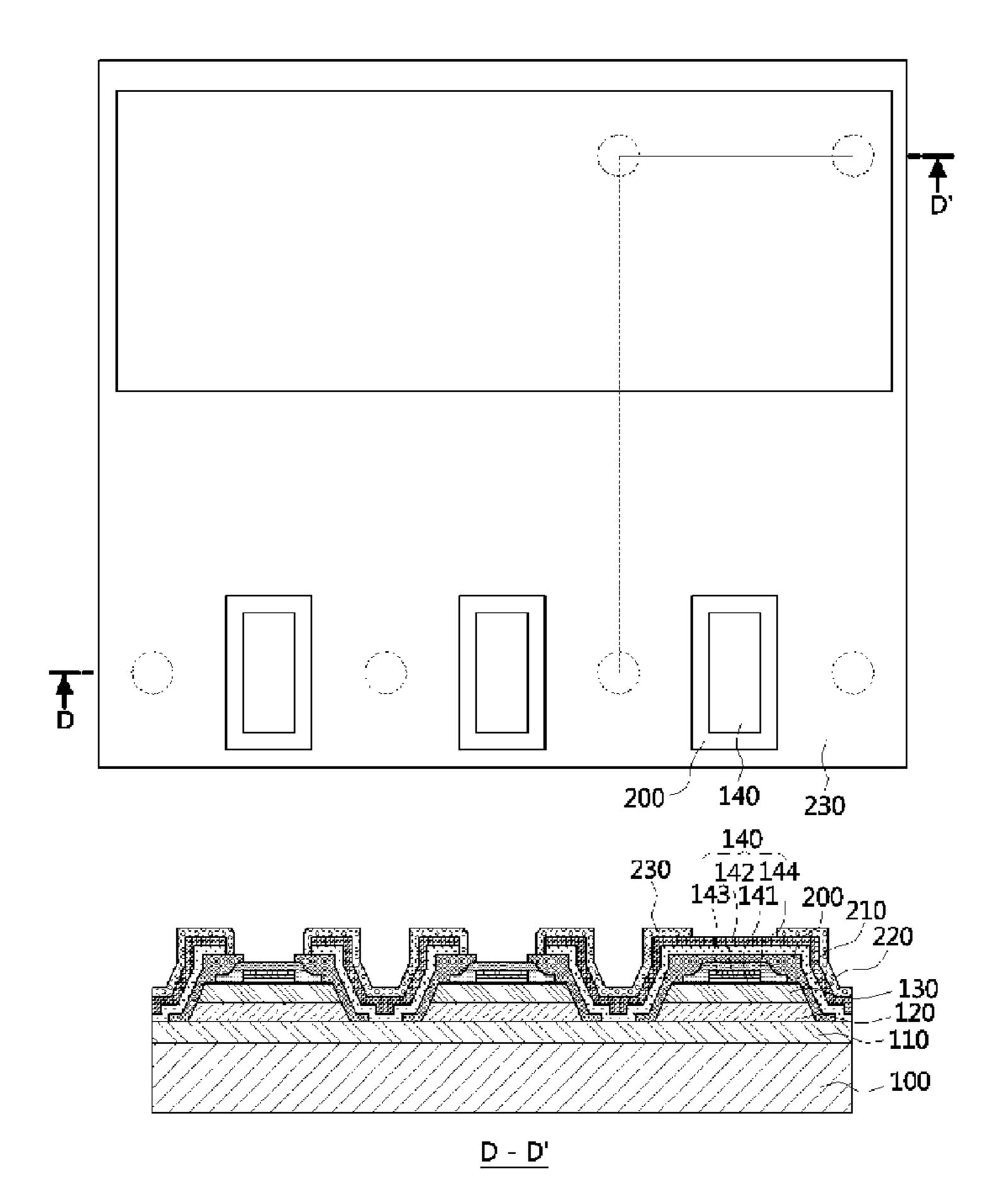

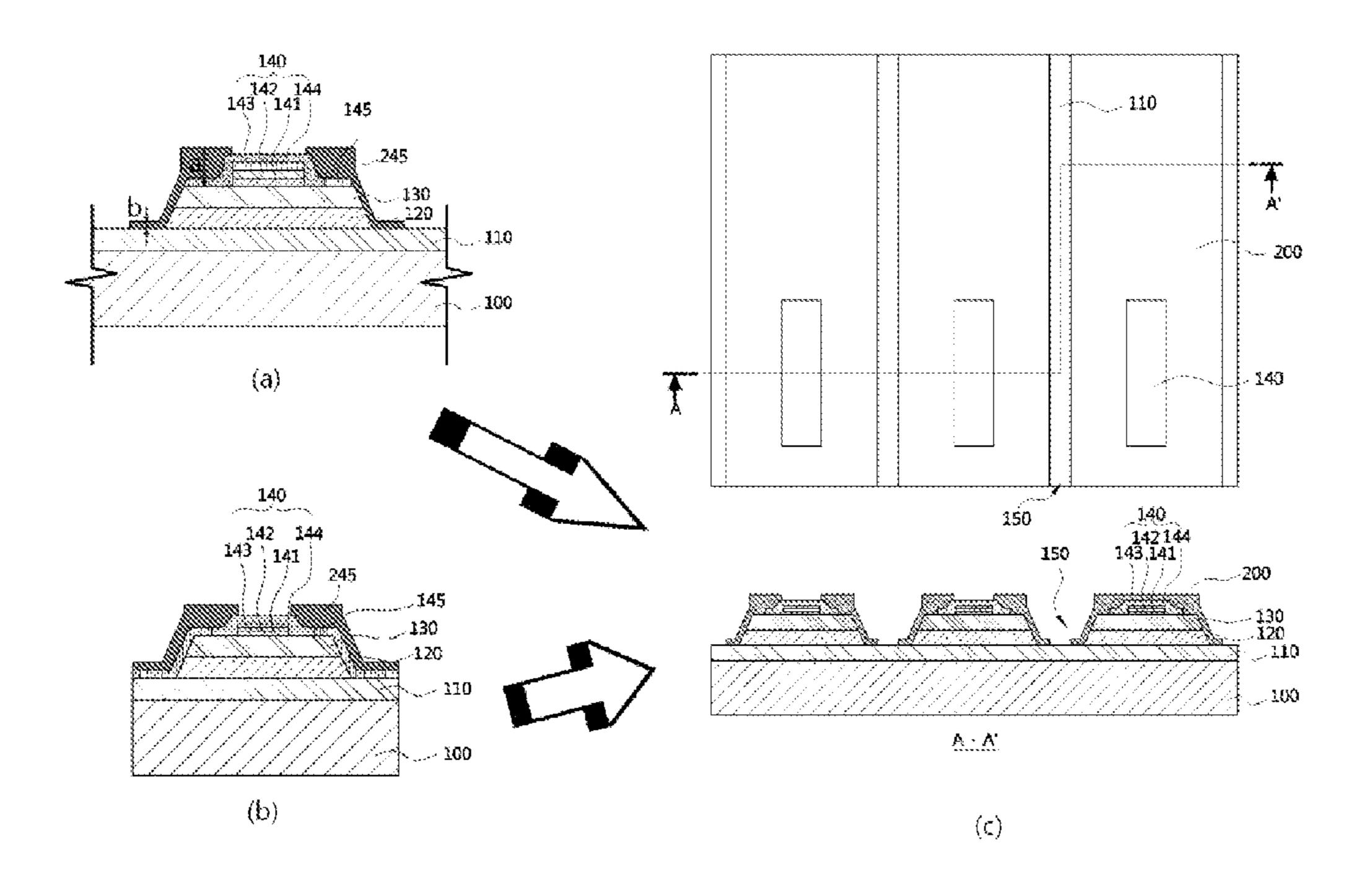

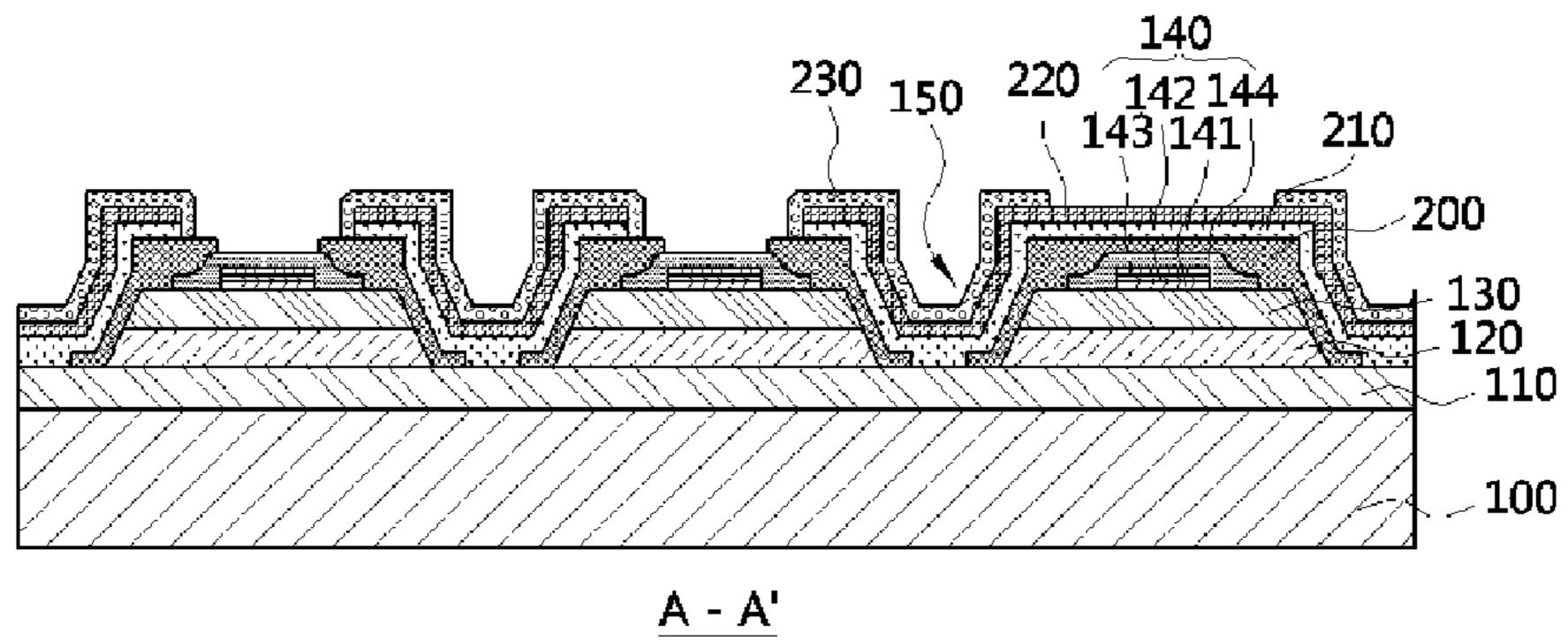

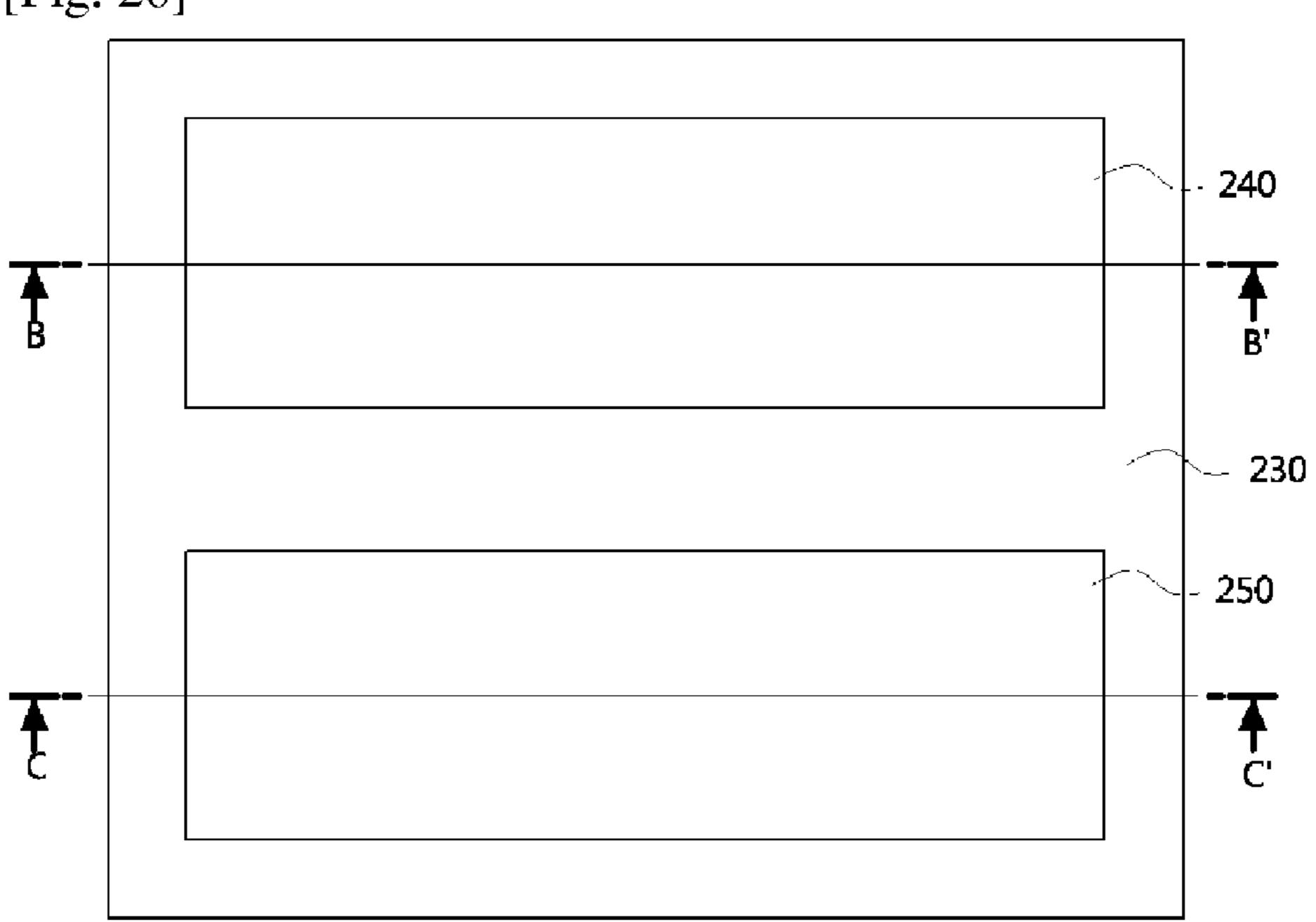

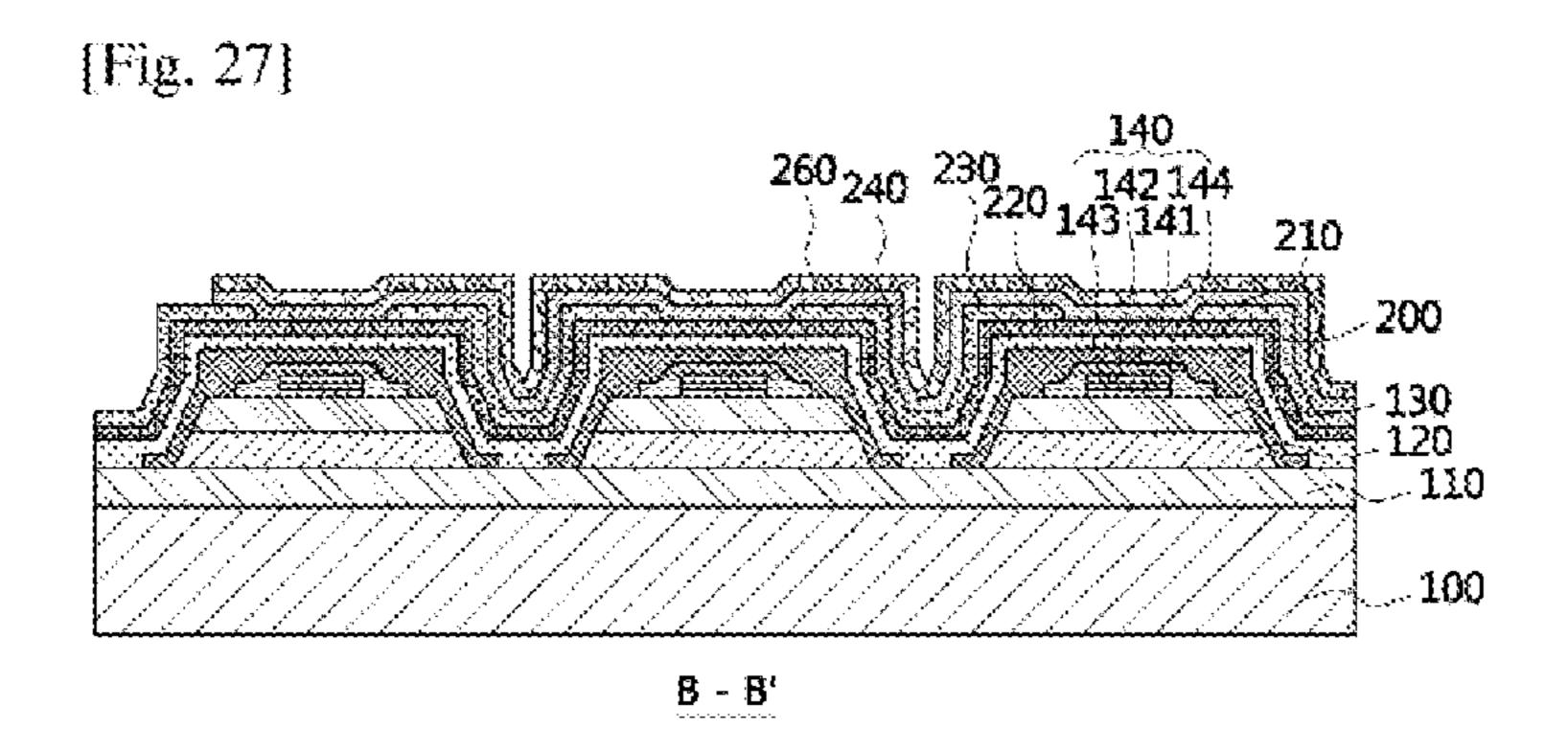

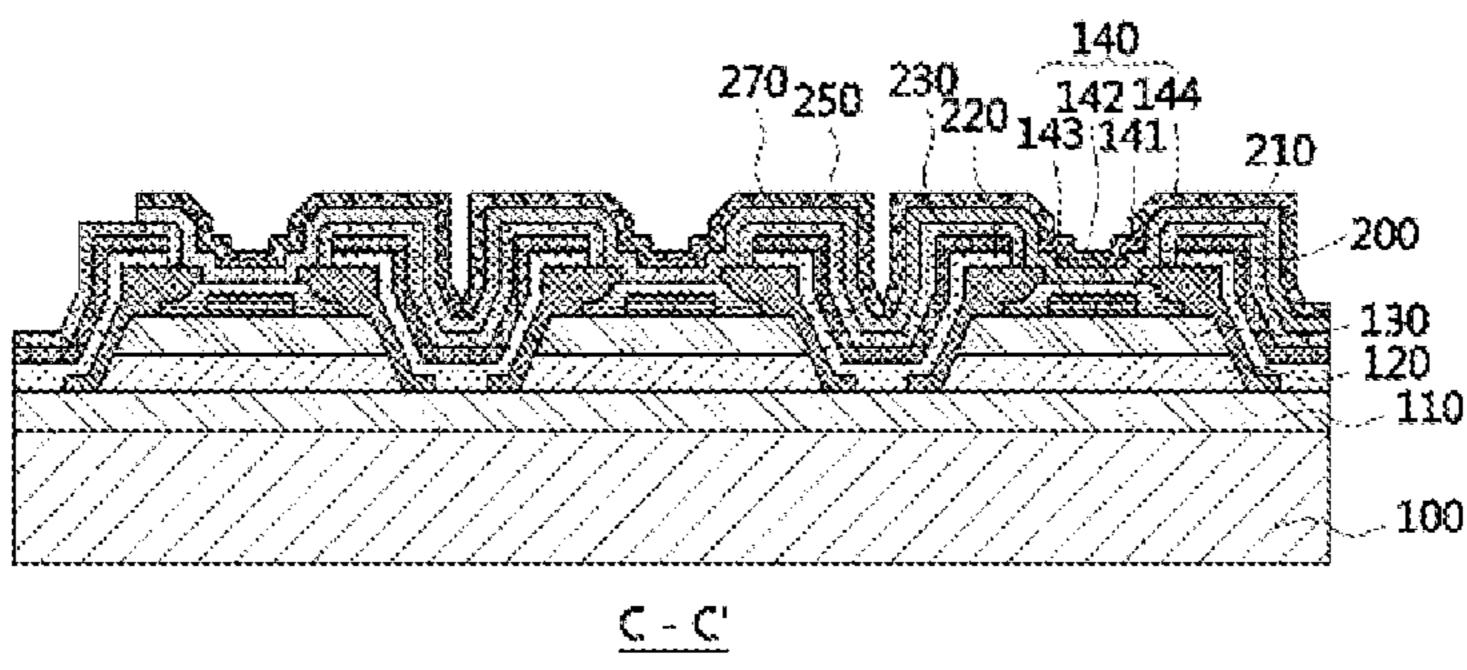

[0021] FIGS. 23 through 27 illustrate plan views and cross-sectional views of LED modules to which the structure of FIG. 3 or FIG. 10 is applied, according to a fourth exemplary embodiment of the disclosed technology.

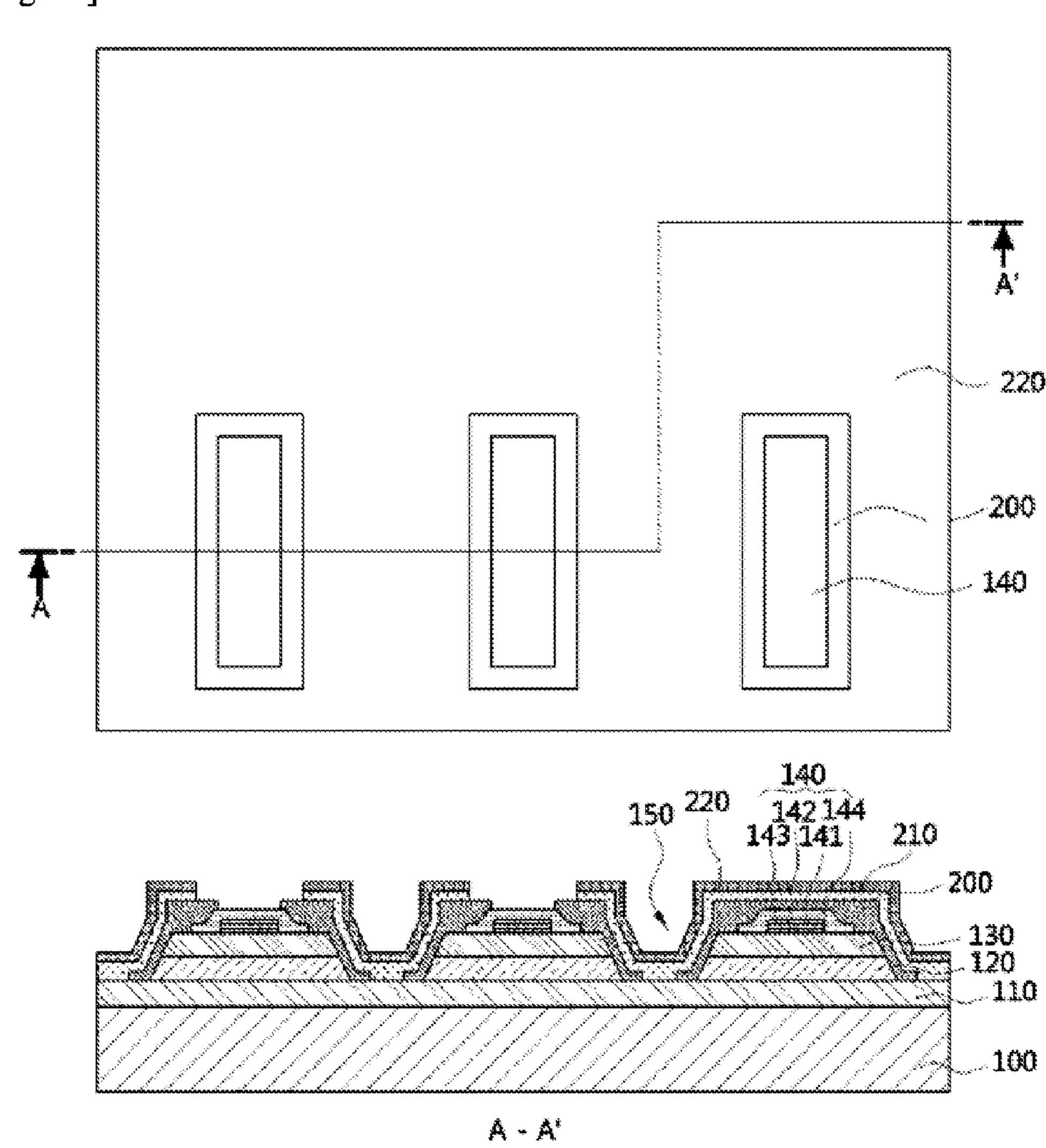

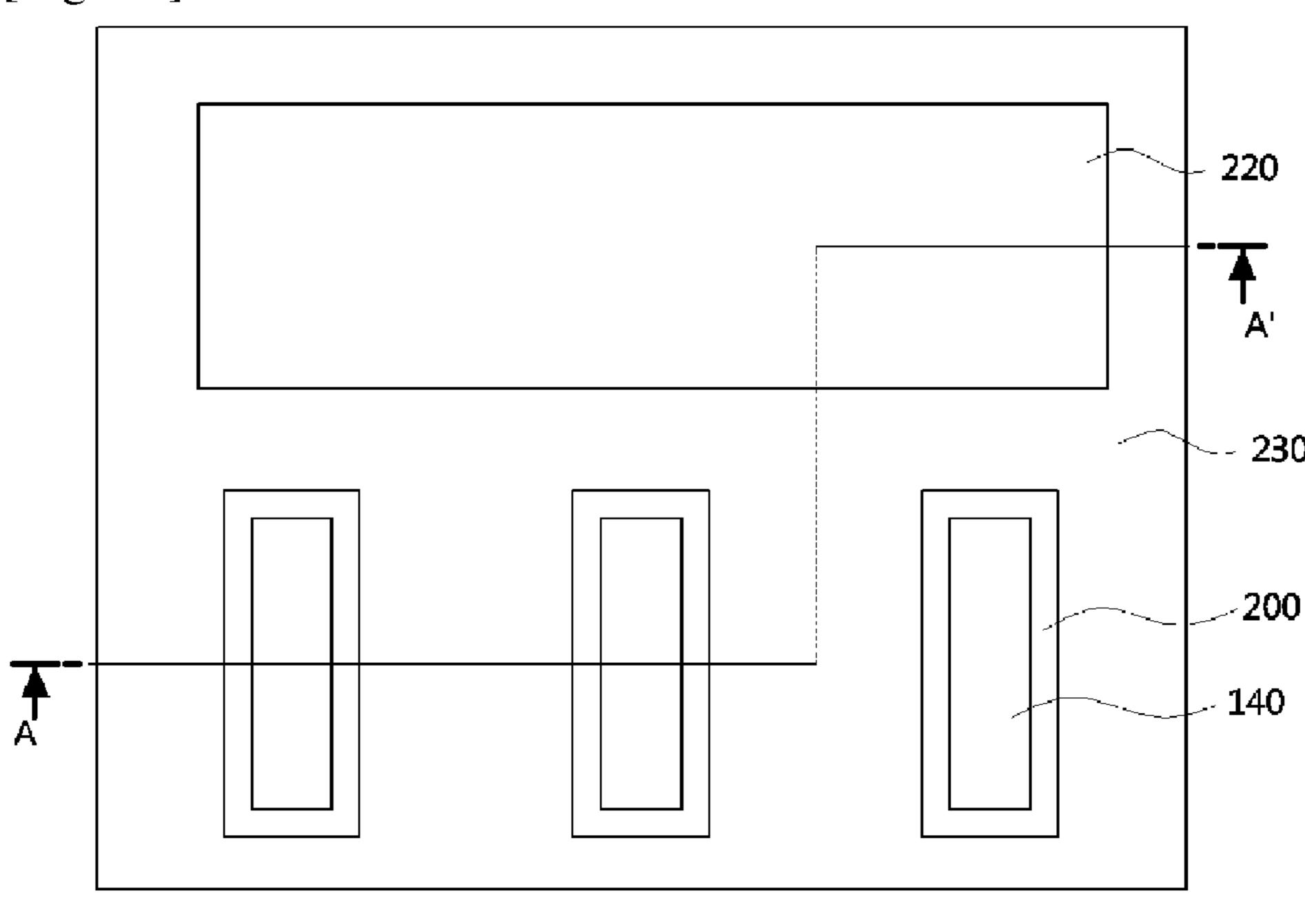

[0022] FIGS. 28 through 30 illustrate plan views and cross-sectional views of LED modules to which the structure of FIG. 3 or FIG. 10 is applied, according to a fifth exemplary embodiment of the disclosed technology.

#### DETAILED DESCRIPTION

[0023] FIGS. 1 and 2 are cross-sectional views of an LED including a reflection layer and a barrier layer.

[0024] Referring to FIG. 1, a first semiconductor layer 20, an active layer 30, a second semi-conductor layer 40, a reflection layer 50, and a barrier layer 60 are formed on a substrate 10.

[0025] The substrate 10 is generally formed of or includes a sapphire material, and the first semi-conductor layer 20 is or includes an n type. The active layer 30 having a typical multiquantum well (MQW) structure is formed on the first semi-conductor layer 20. Also, the p type second semiconductor layer 40 is formed on the active layer 30.

[0026] The LED having the above-described structure is mesa-etched to expose a top surface of the first semiconductor layer 20. Also, photoresist patterns 70 having an overhang structure is formed on the top surface of the first semiconductor layer 20, which is exposed by mesa-etching.

[0027] The second semiconductor layer 40 is exposed in a space in which the photoresist patterns 70 are spaced apart from each other, and the reflection layer 50 is formed on the exposed surface of the second semiconductor layer 40. The reflection layer 50 is or can be formed or disposed using a fabrication process, such as a sputtering process, on the surface of the second semiconductor layer 40 through the space in which the photoresist patterns 70 are spaced apart from

each other. Furthermore, an ohmic contact layer may be additionally formed under the reflection layer **50**. The ohmic contact layer may be formed of or include a material selected so as to form an ohmic contact between the reflection layer **50** and the second semiconductor layer **40**.

[0028] Thereafter, the barrier layer 60 is formed to surround top and side surfaces of the reflection layer 50. The barrier layer 60 may be formed using a sputtering process. The barrier layer 60 functions to prevent diffusion of metal atoms forming the reflection layer 50, and is formed of or include a conductive metal. Since the barrier layer 60 has predetermined diffusivity or isotropic diffusivity due to the sputtering process, the barrier layer 60 surrounds the top and side surfaces of the reflection layer 50 and is also formed on the exposed surface of the second semiconductor layer 40. Also, the barrier layer 60 is accumulated on edge portions of the photoresist patterns 70 having an overhang structure. The barrier layer 60 is adhered to sidewalls of the photoresist pattern 70 and deposited in pointed shapes on the edge portions of the photoresist patterns 70.

[0029] Referring to FIG. 2, the photoresist patterns disclosed in FIG. 1 are removed to perform subsequent processes. By removing the photoresist patterns, points 80 of the barrier layer 60 having the pointed shapes are exposed. The exposed points 80 of the barrier layer 60 form fine particles during subsequent processes. Metallic particles increase contamination during subsequent processes and reduce yield.

[0030] The disclosed technology provides for a technique of removing the points 80 during the formation of the barrier layer 60 and increasing the yield.

[0031] In this patent document when a layer is referred to as being on or over another layer or substrate, the layer can be directly on or over the other layer or substrate or intervening layers may also be present. Terms that describe spatial relationships, such as "on", "upper", "top surface", "under", "lower", "bottom surface" and the like, may be used herein for ease of description to describe one element or feature's relationship to another element(s) or feature(s) as illustrated in the Figures. Such terms can represent different orientations of the device in use or operation in addition to the orientation (s) depicted in the Figures. For example, when the device in the Figures is turned over, elements described as "below" or "beneath" other elements or features would then be oriented "above" the other elements or features. Thus, the term "below" can encompass both an orientation of above and below based on a corresponding reference point. The orientation of the device may be changed in other ways (e.g., rotated 90 degrees or some other angle) and spatial relationships described herein should be interpreted within the context of the changed orientation.

[0032] It will be understood that, although the terms first, second, etc. may be used herein to describe various elements, these elements should not be limited by these terms and a specific order of the elements is not required.

[0033] In the drawings, the thicknesses of layers and regions may be exaggerated for clarity. Like reference numerals refer to like elements throughout.

#### Embodiment 1

[0034] FIG. 3 is a cross-sectional view of a light emitting diode (LED) according to a first exemplary embodiment of the disclosed technology.

[0035] Referring to FIG. 3, a first semiconductor layer 110, an active layer 120, a second semiconductor layer 130, and a reflection pattern 140 are formed or disposed on or over a substrate 100.

[0036] The substrate 100 may be formed of any material capable of inducing the first semi-conductor layer 110 to be grown. Accordingly, the substrate 100 may include sapphire (Al2O3), silicon carbide (SiC), gallium nitride (GaN), indium gallium nitride (InGaN), aluminum gallium nitride (AlGaN), aluminum nitride (AlN), gallium oxide (Ga2O3), or silicon. Specifically, the substrate 100 may be a sapphire substrate.

[0037] Also, the substrate 100 may be a substrate on which surface treatment is not performed. The substrate 100 may be a patterned substrate.

[0038] In addition, the first semiconductor layer 110 is provided on the substrate 100. The first semiconductor layer 110 preferably is an n type but can be any conductivity type. [0039] Furthermore, the active layer 120 formed on the first semiconductor layer 110 may have a single quantum well (SQW) structure in which a well layer and a barrier layer are stacked, or an MQW structure in which well layers and barrier layers are alternately stacked.

[0040] The second semiconductor layer 130 is provided on the active layer 120. The second semiconductor layer 130 preferably is a p type but can be any conductivity type.

[0041] Furthermore, the first semiconductor layer 110, the active layer 120, and the second semiconductor layer 130 may include Si, GaN, AlN, InGaN, or AlInGaN. When the first semiconductor layer 110 includes GaN, the active layer 120 and the second semi-conductor layer 130 preferably include GaN. However, since the second semi-conductor layer 130 has a complementary or a different conductivity type to the first semiconductor layer 110, a different dopant from that of the first semiconductor layer 110 is introduced into the second semiconductor layer 130. That is, when a dopant serving as a donor is introduced into the first semiconductor layer 110, a dopant serving as an acceptor is introduced into the second semiconductor layer 130. Also, the active layer 120 preferably includes a material on which bandgap engineering is performed to form barrier layers and well layers.

[0042] The reflection pattern 140 is formed on or over the second semiconductor layer 130.

[0043] The reflection pattern 140 includes an ohmic contact layer 141, a reflective metal layer 142, a stress relaxation layer 143, or a conductive barrier layer 144.

[0044] The ohmic contact layer 141 may be formed of or include any material capable of enabling an ohmic contact between the reflective metal layer 142 and the second semiconductor layer 130. Accordingly, the ohmic contact layer 141 may include a metal including nickel (Ni) or platinum (Pt), or include a conductive oxide, such as indium tin oxide (ITO) or zinc oxide (ZnO). However, the ohmic contact layer 141 may be omitted in some embodiments.

[0045] The reflective metal layer 142 is formed on or over the ohmic contact layer 141. The reflective metal layer 142 reflects light generated by the active layer 120. Accordingly, the reflective metal layer 142 is formed by selecting a material having conductivity and a high optical reflectance. The reflective metal layer 142 includes Ag, an Ag alloy, Al, or an Al alloy.

[0046] In addition, the stress relaxation layer 143 may be formed on the reflective metal layer 142. The stress relaxation layer 143 preferably has a coefficient of thermal expansion

equal to or higher than that of the conductive barrier layer 144, and equal to or lower than that of the reflective metal layer 142. Thus, stress caused due to a difference in coefficient of thermal expansion between the reflective metal layer 142 and the conductive barrier layer 144 may be reduced. Accordingly, a material forming the stress relaxation layer 143 may be differently selected according to selected materials forming the reflective metal layer 142 and the conductive barrier layer 144.

[0047] However, the ohmic contact layer 141 or the stress relaxation layer 143 may be omitted in some embodiments. [0048] A conductive barrier layer 144 is formed on the reflective metal layer 142 or the stress relaxation layer 143. For example, when the stress relaxation layer 143 is omitted, the conductive barrier layer 144 is formed on or over the reflective metal layer 142. When the stress relaxation layer 143 is formed, the conductive barrier layer 144 is formed on or over the stress relaxation layer 143. The conductive barrier layer 144 is formed to surround at least side surfaces of the reflective metal layer 142 and top and side surfaces of the stress relaxation layer 143. Accordingly, diffusion of metal atoms or ions constituting the reflective metal layer 142 is prevented. Also, stress caused due to a difference in coefficient of thermal expansion between the conductive barrier layer 144 and the reflective metal layer 142 is absorbed in the stress relaxation layer 143.

[0049] For example, when the reflective metal layer 142 includes Al or an Al alloy, and the conductive barrier layer 144 includes tungsten (W), titanium tungsten (TiW), or molybdenum (Mo), the stress relaxation layer 143 may be a single layer formed of silver (Ag), copper (Cu), nickel (Ni), platinum (Pt), titanium (Ti), rhodium (Rh), palladium (Pd), or chromium (Cr), or a combination formed of Cu, Ni, Pt, Ti, Rh, Pd or Au. Also, when the reflective metal layer 142 includes Al or an Al alloy, and the conductive barrier layer 144 includes Cr, Pt, Rh, Pd, or Ni, the stress relaxation layer 143 may be a single layer formed of Ag or Cu, or a combination formed of Ni, Au, Cu, or Ag.

[0050] Furthermore, when the reflective metal layer 142 includes Ag or an Ag alloy, and the conductive barrier layer 144 includes W, TiW, or Mo, the stress relaxation layer 143 may be a single layer formed of Cu, Ni, Pt, Ti, Rh, Pd, or Cr, or a combination formed of Cu, Ni, Pt, Ti, Rh, Pd, Cr, or Au. Also, when the reflective metal layer 142 includes Ag or an Ag alloy, and the conductive barrier layer 144 includes Cr or Ni, the stress re-laxation layer 143 may be a single layer formed of Cu, Cr, Rh, Pd, TiW, or Ti, or a combination formed of Ni, Au, or Cu.

[0051] In addition, the conductive barrier layer 144 is formed to coat at least a portion of a surface of the second semiconductor layer 130 and extend to side surfaces of a protective insulating layer 145. However, the conductive barrier layer 144 is or can be preferably formed to contact the side surfaces of the protective insulating layer 145 but not in such a shape as to coat a top surface of the protective insulating layer 145.

[0052] FIGS. 4 through 9 are cross-sectional views illustrating a method of manufacturing the LED of FIG. 3, according to a first exemplary embodiment of the disclosed technology.

[0053] Referring to FIG. 4, a first semiconductor layer 110, an active layer 120, a second semiconductor layer 130, and a protective insulating layer 145 are sequentially formed or stacked on or over a substrate 100.

[0054] The substrate 100 may include sapphire (Al2O3), silicon carbide (SiC), gallium nitride (GaN), indium gallium nitride (InGaN), aluminum gallium nitride (AlGaN), aluminum nitride (AlN), gallium oxide (Ga2O3), or silicon. Specifically, the substrate 100 may be a sapphire substrate. Also, the substrate 100 may be a patterned substrate.

[0055] Also, the first semiconductor layer 110 is provided on the substrate 100. The first semiconductor layer 110 preferably includes an n conductivity type but can include any conductivity type layer.

[0056] In addition, the active layer 120 formed on the first semiconductor layer 110 may have an SQW structure in which a well layer and a barrier layer are stacked, or an MQW structure in which well layers and barrier layers are alternately stacked.

[0057] The second semiconductor layer 130 is provided on the active layer 120. The second semiconductor layer 130 preferably includes a p conductivity type but can include any conductivity type layer.

[0058] Furthermore, materials and constructions of the first semiconductor layer 110, the active layer 120, and the second semiconductor layer 130 are or can be the same as described with reference to FIG. 3, and thus a description thereof is omitted.

[0059] In addition, in some implementations, the first semi-conductor layer 110, the active layer 120, and the second semiconductor layer 130 are formed using an epitaxial growth process. Accordingly, the first semiconductor layer 110, the active layer 120, and the second semiconductor layer 130 are preferably formed using a metal organic chemical vapor deposition (MOCVD) process.

[0060] Also, the protective insulating layer 145 is formed on the second semiconductor layer. The protective insulating layer may be formed of any insulating material. Accordingly, the protective insulating layer 145 may be formed of silicon oxide or silicon nitride. In addition, the protective insulating layer 145 may be formed of any insulating material having an etch selectivity with respect to the underlying second semiconductor layer 130, active layer 120, or first semiconductor layer 110 and an insulating characteristic.

[0061] In addition, the protective insulating layer 145 may be formed using various methods, such as a spin coating process, a physical vapor deposition (PVD) process, a CVD process, or an atomic layer deposition (ALD) process.

[0062] Referring to FIG. 5, portions of the active layer 120, the second semiconductor layer 130, and the protective insulating layer 145 are removed using an ordinary etching process. Thus, a portion of the first semiconductor layer 110 is exposed. Due to the etching process, at least a portion of a top surface of the first semiconductor layer 110 is exposed, at least a portion of side surfaces of the active layer 120 and the second semiconductor layer 130 are exposed, and at least a portion of top and side surfaces of the active layer 120 and the second semiconductor layer 130 are exposed, and at least a portion of top and side surfaces of the protective insulating layer 145 are exposed. Accordingly, a trench or a hole may be formed by removing the portions of the active layer 120, the second semiconductor layer 130, and the protective insulating layer 145 using the etching process. For example, one or more mesa regions 150 etched from the surface of the protective insulating layer 145 of FIG. 5 to the surface of the first semiconductor layer 110 may be a stripe type having a trench shape or a hole type.

[0063] In addition, when the mesa region(s) 150 is the stripe type, the mesa region(s) 150 may have a vertical profile or inclined profile with respect to the surface of the first semi-conductor layer 110. Preferably, the mesa region(s) 150 has a profile inclined at an angle of about 20° to about 70° with respect to the surface of the first semiconductor layer 110. Also, when the mesa region 150 is a hole type having a roughly circular shape, the mesa region(s) 150 may have a vertical profile or inclined profile with respect to the surface of the first semiconductor layer 110. Preferably, the mesa region(s) 150 has a profile inclined at an angle of about 20° to about 70° with respect to the surface of the first semiconductor layer 110. When the profile is inclined at an angle of less than 20°, a width of the mesa region 150 greatly increases upward. Accordingly, convergence of light generated is degraded due to an emission structure. Also, when the profile is inclined at an angle of more than 70°, the mesa region(s) 150 has an approximately vertical profile. Accordingly, the effect of reflection of generated light by sidewalls of layers become immaterial.

[0064] Referring to FIG. 6, a photoresist pattern 160 is formed on the first semiconductor layer 110 exposed by forming a bottom surface of the mesa region(s) 150. The photoresist pattern 160 may have a vertical profile with respect to the surface of the first semiconductor layer 110. In some embodiments, the photoresist pattern 160 may be formed to have an overhang structure having a bottom surface with a smaller width than a top surface thereof. The photoresist pattern 160 is preferably a negative type. Accordingly, exposed portions are cross-linked. To form the overhang structure, the photoresist pattern 160 is preferably exposed at a predetermined angle. In the case of the overhang structure, a distance between bottom surfaces of the photoresist patterns 160 is preferably set to be at least about 1 m greater than a distance between top surfaces thereof.

[0065] Furthermore, the photoresist pattern 160 is preferably provided to cover a portion of the surface of the protective insulating layer 145. Accordingly, the portion of the top surface of the protective insulating layer 145 may remain shielded or protected by the photoresist pattern 160.

[0066] Referring to FIG. 7, an etching process is performed on the protective insulating layer 145 exposed by a space between the photoresist patterns 160. Although the etching process may be performed using a wet process or a dry process, the etching process is preferably performed using a wet etching process. Also, due to the etching process, a large portion of the protective insulating layer 145 formed on the surface of the second semiconductor layer 130 may be removed, and a portion of the surface of the second semiconductor layer 130 is exposed. However, the protective insulating layer 145 formed at corners disposed under the photoresist pattern 160 remains in a recessed space. Accordingly, the recessed space is formed between a lower portion of the photoresist pattern 160 and the second semiconductor layer 130 due to the etching process, and the protective insulating layer 145 remains at an end of the space. Since the wet etching process has isotropic etching characteristics, it may take a considerable amount of time or be troublesome to etch the protective insulating layer 145 formed on the corners disposed under the photoresist pattern 160. Accordingly, the protective insulating layer 145 exposed by the photoresist pattern 160 due to the anisotropic etching process is mostly removed, while only the protective insulating layer 145 recessed under the photoresist pattern 160 remains.

[0067] Referring to FIG. 8, a reflective metal layer 142 and a stress relaxation layer 143 are sequentially stacked on the second semiconductor layer 130.

[0068] The reflective metal layer 142 includes Al, an Al alloy, Ag, or an Ag alloy. The reflective metal layer 142 may be formed using an ordinary metal deposition process. However, the reflective metal layer 142 is preferably formed using an electronic beam (e-beam) evaporation process capable of moving most metal atoms or ions onto the surface of the second semiconductor layer 130 in a vertical direction. Thus, the metal atoms or ions may have anisotropic etching characteristics and enter a space between the photoresist patterns 160 to form the reflective metal layer 142.

[0069] The reflective metal layer 142 preferably has a thickness of about 100 nm to about 1 um. When the reflective metal layer 142 has a thickness of less than about 100 nm, light generated by the active layer 120 is not smoothly reflected. Also, when the reflective metal layer 142 has a thickness of more than about 1 um, process loss may occur due to an excessive process time.

[0070] The ohmic contact layer 141 may be formed before forming the reflective metal layer 142, as needed. The ohmic contact layer 141 may include Ni, Pt, ITO, or ZnO. Also, the ohmic contact layer 141 is preferably formed to a thickness of about 0.1 nm to about 20 nm. When the ohmic contact layer 141 has a thickness of less than about 0.1 nm, sufficient ohmic characteristics cannot be ensured due to a very small layer thickness. Also, when the ohmic contact layer 141 has a thickness of more than about 20 nm, the transmitted amount of light is reduced to reduce the quantity of light reflected by the reflective metal layer 142 disposed on the ohmic contact layer 141.

[0071] The stress relaxation layer 143 is formed on the reflective metal layer 142.

[0072] The stress relaxation layer 143 may be formed using an ordinary metal deposition process, but is preferably formed using an e-beam evaporation method having a high directionality during a deposition process. That is, metal atoms or ions evaporated due to e-beams may have directionality and have anisotropy in a space between the photoresist patterns 160, and the stress relaxation layer 143 may be formed of a metal layer. Also, the stress relaxation layer 143 may have a lower coefficient of thermal expansion than the reflective metal layer 142 and a higher coefficient of thermal expansion than the conductive barrier layer 144 of FIG. 3. Accordingly, a material forming the stress relaxation layer 143 may be differently selected according to selected materials forming the reflective metal layer 142 and the conductive barrier layer 144. The material forming the stress relaxation layer 143 will be described later.

[0073] When the reflective metal layer 142 and the stress relaxation layer 143 are formed using an e-beam evaporation method, a side surface of the reflective metal layer 142 and a side surface of the stress relaxation layer 143 are exposed. Also, the reflective metal layer 142 and the stress relaxation layer 143 corresponding to an open upper region of the photoresist pattern 160 are formed using an anisotropic deposition process.

[0074] Subsequently, a conductive barrier layer 144 is formed through the opened region of the photoresist pattern 160.

[0075] The conductive barrier layer 144 includes W, TiW, Mo, Cr, Ni, Pt, Rh, Pd, or Ti. In particular, a material forming the conductive barrier layer 144 may be differently selected

according to selected materials forming the reflective metal layer 142 and the stress relaxation layer 143.

[0076] The conductive barrier layer 144 is formed on the stress relaxation layer 143 and shields at least side surfaces of the reflective metal layer 142 and the stress relaxation layer 143. Accordingly, a metal forming the reflective metal layer 142 is prevented from diffusing into the second semiconductor layer 130 due to lateral diffusion. The formation of the conductive barrier layer 144 is performed using an ordinary metal de-position process. However, the conductive barrier layer 144 is preferably formed using an isotropic etching process. This is because the conductive barrier layer 144 is configured to surround at least the side surfaces of the stress relaxation layer 143 and the reflective metal layer 142. For example, the conductive barrier layer 144 may be formed using a sputtering process.

[0077] In addition, the conductive barrier layer 144 may be a single layer formed to a thickness of about 100 nm or more by selecting a specific metal. Also, the conductive barrier layer 144 may be formed by alternately selecting at least two metal materials, and each of layers forming the conductive barrier layer 144 may be formed to a thickness of about 20 nm or more. For example, the conductive barrier layer 144 may be formed by alternately depositing a TiW layer having a thickness of about 50 nm and a Ni layer or Ti layer having a thickness of about 50 nm.

[0078] Furthermore, a Ni/Au/Ti layer may be additionally formed on the conductive barrier layer 144 to enable a stable contact of the conductive barrier layer 144 with a subsequent material.

[0079] As described above, a material forming the stress relaxation layer 143 may be selected based on materials forming the reflective metal layer 142 and the conductive barrier layer 144. This is at least because a coefficient of thermal expansion of the stress re-laxation layer 143 is higher than that of the conductive barrier layer 144 and lower than that of the reflective metal layer 142. Accordingly, when the reflective metal layer 142 includes Al or an Al alloy, and the conductive barrier layer 144 includes W, TiW, or Mo, the stress relaxation layer 143 may be a single layer formed of Ag, Cu, Ni, Pt, Ti, Rh, Pd, or Cr, or a combination formed of Cu, Ni, Pt, Ti, Rh, Pd or Au. Also, when the reflective metal layer 142 includes Al or an Al alloy, and the conductive barrier layer 144 includes Ti, Cr, Pt, Rh, Pd, or Ni, the stress relaxation layer 143 may be a single layer formed of Ag or Cu, or a combination formed of Ni, Au, Cu, or Ag.

[0080] Furthermore, when the reflective metal layer 142 includes Ag or an Ag alloy, and the conductive barrier layer 144 includes W, TiW, or Mo, the stress relaxation layer 143 may be a single layer formed of Cu, Ni, Pt, Ti, Rh, Pd, or Cr, or a combination formed of Cu, Ni, Pt, Ti, Rh, Pd, Cr, or Au. Also, when the reflective metal layer 142 includes Ag or an Ag alloy, and the conductive barrier layer 144 includes Cr or Ni, the stress re-laxation layer 143 may be a single layer formed of Cu, Cr, Rh, Pd, TiW, or Ti, or a combination formed of Ni, Au, or Cu.

[0081] In addition, since the conductive barrier layer 144 is formed using a deposition process, such as a sputtering process, the conductive barrier layer 144 is formed to fill an edge region of the photoresist pattern 160. That is, the conductive barrier layer 144 is formed to fill a space between the photoresist pattern 160 and the second semi-conductor layer 130. By filling the space, the protective insulating layer 145 and the conductive barrier layer 144 are physically in contact with

each other. Also, due to the deposition process, the conductive barrier layer 144 may be formed along shapes of surfaces of the second semiconductor layer 130, the reflective metal layer 142, and the stress relaxation layer 143.

[0082] The ohmic contact layer 141, the reflective metal layer 142, the stress relaxation layer 143, and the conductive barrier layer 144 may be formed also on the photoresist pattern 160.

[0083] Referring to FIG. 9, a lift-off process is performed on the photoresist pattern 160 to remove the photoresist pattern 160 and the layers disposed thereon. Accordingly, the underlying second semiconductor layer 130 and the reflection pattern 140 disposed thereon are exposed. Also, the mesa region(s) 150 is exposed by removing the photoresist pattern 160. As described above, the mesa region(s) 150 may be a stripe type or a hole type. Also, a protective insulating layer 145 is provided on side surfaces of the re-flection pattern 140. The conductive barrier layer 144 of the reflection pattern 140 may be defined by the protective insulating layer 145.

[0084] Due to the above-described processes, the reflection pattern 140 is formed on the second semiconductor layer 130. The reflection pattern 140 includes a reflective metal layer 142, a stress relaxation layer 143, and a conductive barrier layer 144. The stress relaxation layer 143 has a lower coefficient of thermal expansion than the reflective metal layer 142 and a higher coefficient of thermal expansion than the conductive barrier layer 144. Accordingly, stress caused due to a difference in coefficient of thermal expansion between the reflective metal layer 142 and the conductive barrier layer 144 is absorbed in the stress relaxation layer 143.

[0085] In addition, formation of protruding points shown in FIGS. 1 and 2 is excluded from the conductive barrier layer 144 formed on the reflective metal layer 142 or the stress relaxation layer 143. Accordingly, generation of metal particles is inhibited in subsequent processes to maintain a high yield.

#### Embodiment 2

[0086] FIG. 10 is a cross-sectional view of an LED according to a second exemplary embodiment of the disclosed technology.

[0087] Referring to FIG. 10, a first semiconductor layer 110, an active layer 120, a second semiconductor layer 130, a reflection pattern 140, and a protective insulating layer 145 are formed on a substrate 100.

[0088] The substrate 100 may be formed of any material capable of inducing the first semi-conductor layer 110 to be grown. Accordingly, the substrate 100 may include sapphire (Al2O3), silicon carbide (SiC), gallium nitride (GaN), indium gallium nitride (InGaN), aluminum gallium nitride (AlGaN), aluminum nitride (AlN), gallium oxide (Ga2O3), or silicon. Specifically, the substrate 100 may be a sapphire substrate.

[0089] Also, the substrate 100 may be a substrate on which surface treatment is not performed. The substrate 100 may be a patterned substrate.

[0090] In addition, the first semiconductor layer 110 is provided on the substrate 100. The first semiconductor layer 110 preferably includes an n conductivity type but can include any conductivity type layer.

[0091] Furthermore, the active layer 120 formed on the first semiconductor layer 110 may have an SQW structure in

which a well layer and a barrier layer are stacked, or an MQW structure in which well layers and barrier layers are alternately stacked.

[0092] The second semiconductor layer 130 is provided on the active layer 120. The second semiconductor layer 130 preferably has a p conductivity type but can include any conductivity type layer.

[0093] Furthermore, the first semiconductor layer 110, the active layer 120, and the second semiconductor layer 130 may include Si, GaN, AlN, InGaN, or AlInGaN. When the first semiconductor layer 110 includes GaN, the active layer 120 and the second semi-conductor layer 130 preferably include GaN. However, since the second semi-conductor layer 130 has a complementary conductivity type to the first semiconductor layer 110, a different dopant from that of the first semiconductor layer 110 is introduced into the second semi-conductor layer 130. That is, when a dopant serving as a donor is introduced into the first semiconductor layer 110, a dopant serving as an acceptor is introduced into the second semiconductor layer 130. Also, the active layer 120 preferably includes a material on which bandgap engineering is performed to form barrier layers and well layers.

[0094] The reflection pattern 140 is formed on the second semiconductor layer 130.

[0095] The reflection pattern 140 includes an ohmic contact layer 141, a reflective metal layer 142, a stress relaxation layer 143, or a conductive barrier layer 144.

[0096] The ohmic contact layer 141 may be formed of any material capable of enabling an ohmic contact between the reflective metal layer 142 and the second semiconductor layer 130. Accordingly, the ohmic contact layer 141 may include a metal including nickel (Ni) or platinum (Pt) or include a conductive oxide, such as indium tin oxide (ITO) or zinc oxide (ZnO). However, the ohmic contact layer 141 may be omitted in some embodiments.

[0097] The reflective metal layer 142 is formed on or over the ohmic contact layer 141. The reflective metal layer 142 reflects light generated by the active layer 120. Accordingly, the reflective metal layer 142 is formed by selecting a material having conductivity and a high optical reflectance. The reflective metal layer 142 includes Ag, an Ag alloy, Al, or an Al alloy.

[0098] In addition, the stress relaxation layer 143 may be formed on or over the reflective metal layer 142. The stress relaxation layer 143 preferably has a coefficient of thermal expansion equal to or higher than that of the conductive barrier layer 144, and equal to or lower than that of the reflective metal layer 142. Thus, stress caused due to a difference in coefficient of thermal expansion between the reflective metal layer 142 and the conductive barrier layer 144 may be reduced. Accordingly, a material forming the stress relaxation layer 143 may be differently selected according to selected materials forming the reflective metal layer 142 and the conductive barrier layer 144.

[0099] However, the ohmic contact layer 141 or the stress relaxation layer 143 may be omitted in some embodiments.

[0100] A conductive barrier layer 144 is formed on or over the reflective metal layer 142 or the stress relaxation layer

the reflective metal layer 142 or the stress relaxation layer 143. For example, when the stress relaxation layer 143 is omitted, the conductive barrier layer 144 is formed on the reflective metal layer 142. When the stress relaxation layer 143 is formed, the conductive barrier layer 144 is formed on the stress relaxation layer 143. The conductive barrier layer 144 is formed to surround at least side surfaces of the reflec-

tive metal layer 142 and top and side surfaces of the stress relaxation layer 143. Accordingly, diffusion of metal atoms or ions constituting the reflective metal layer 142 is prevented. Also, stress caused due to a difference in coefficient of thermal expansion between the conductive barrier layer 144 and the reflective metal layer 142 is absorbed in the stress relaxation layer 143.

[0101] For example, when the reflective metal layer 142 includes Al or an Al alloy, and the conductive barrier layer 144 includes W, TiW, or Mo, the stress relaxation layer 143 may be a single layer formed of Ag, Cu, Ni, Pt, Ti, Rh, Pd, or Cr, or a combination formed of Cu, Ni, Pt, Ti, Rh, Pd or Au. Also, when the reflective metal layer 142 includes Al or an Al alloy, and the conductive barrier layer 144 includes Cr, Pt, Rh, Pd, or Ni, the stress relaxation layer 143 may be a single layer formed of Ag or Cu, or a combination of Ni, Au, Cu, or Ag. [0102] Furthermore, when the reflective metal layer 142 includes Ag or an Ag alloy, and the conductive barrier layer 144 includes W, TiW, or Mo, the stress relaxation layer 143 may be a single layer formed of Cu, Ni, Pt, Ti, Rh, Pd, or Cr, or a combination formed of Cu, Ni, Pt, Ti, Rh, Pd, Cr, or Au. Also, when the reflective metal layer 142 includes Ag or an Ag alloy, and the conductive barrier layer 144 includes Cr or Ni, the stress re-laxation layer 143 may be a single layer formed of Cu, Cr, Rh, Pd, TiW, or Ti, or a combination of Ni, Au, or Cu.

[0103] In addition, the conductive barrier layer 144 is formed to coat a surface of the second semiconductor layer 130 and extend to at least side surfaces of a protective insulating layer 145. However, the conductive barrier layer 144 is preferably formed to contact the side surfaces of the protective insulating layer 145 but not in such a shape as to coat a top surface of the protective insulating layer 145.

[0104] In FIG. 10, the protective insulating layer 145 is formed to completely coat a portion of a top surface of the second semiconductor layer 130 and the mesa region 150. That is, the protective insulating layer 145 coats a surface of the first semiconductor layer 110 and portions of side and top surfaces of the active layer 120 and the second semi-conductor layer 130, which are exposed by mesa-etching.

[0105] FIGS. 11 through 16 are cross-sectional views illustrating a method of manufacturing the LED of FIG. 10, according to a second exemplary embodiment of the disclosed technology.

[0106] Referring to FIG. 11, a first semiconductor layer 110, an active layer 120, and a second semiconductor layer 130 are sequentially formed on a substrate 100.

[0107] Furthermore, materials and forming methods of the first semiconductor layer 110, the active layer 120, and the second semiconductor layer 130 are the same as described in Embodiment 1, and thus a description thereof is omitted.

[0108] Referring to FIG. 12, portions of the active layer 120 and the second semiconductor layer 130 are removed using an ordinary etching process. Thus, a portion of the first semiconductor layer 110 is exposed. Due to the etching process, a top surface of the first semiconductor layer 110 is exposed, and side surfaces of the active layer 120 and the second semiconductor layer 130 are exposed. Accordingly, a mesa region 150 or a hole may be formed by removing the portions of the active layer 120 and the second semiconductor layer 130 using the etching process. That is, the mesa region 150 etched from the surface of the second semiconductor layer 130 of FIG. 11 to the surface of the first semiconductor layer 110 may be a stripe type having a trench shape or a hole type.

In addition, when the mesa region 150 is the stripe type, the mesa region 150 may have a vertical profile or inclined profile with respect to the surface of the first semiconductor layer 110. Preferably, the mesa region 150 has a profile inclined at an angle of about 20° to about 70° with respect to the surface of the first semiconductor layer 110. Also, when the mesa region 150 is a hole type having a roughly circular shape, the mesa region 150 may have a vertical profile or inclined profile with respect to the surface of the first semiconductor layer 110. Preferably, the mesa region 150 has a profile inclined at an angle of about 20° to about 70° with respect to the surface of the first semiconductor layer 110. When the profile is inclined at an angle of less than 20°, a width of the mesa region 150 greatly increases upward. Accordingly, convergence of light generated is degraded due to an emission structure. Also, when the profile is inclined at an angle of more than 70°, the mesa region 150 has an approximately vertical profile. Accordingly, the effect of reflection of generated light by sidewalls of layers become immaterial.

[0110] Referring to FIG. 13, a protective insulating layer 145 is formed on the entire surface of the resultant structure shown in FIG. 12.

[0111] The protective insulating layer 145 may be formed of any insulating material. Accordingly, the protective insulating layer 145 may be formed of silicon oxide or silicon nitride. In addition, the protective insulating layer 145 may be formed of any insulating material having an etch selectivity with respect to the underlying second semi-conductor layer 130, active layer 120, or first semiconductor layer 110 and an insulating characteristic.

[0112] The protective insulating layer 145 may be formed using a spin coating process, a PVD process, a CVD process, or an ALD process according to a used material.

[0113] Referring to FIG. 14, a photoresist pattern 160 is formed on the exposed protective insulating layer 145, which forms a bottom surface of the mesa region 150. The photoresist pattern 160 may have a vertical profile with respect to the surface of the protective insulating layer 145 disposed on the mesa region. In some embodiments, the photoresist pattern 160 may be formed to have an overhang structure having a bottom surface with a smaller width than a top surface thereof. The photoresist pattern 160 is preferably a negative type. Accordingly, exposed portions are cross-linked. To form the overhang structure, the photoresist pattern 160 is preferably exposed at a predetermined angle. In the case of the overhang structure, a distance between bottom surfaces of the photoresist patterns 160 is preferably set to be at least about 1 um greater than a distance between top surfaces thereof.

[0114] Furthermore, the protective insulating layer 145 disposed on the second semi-conductor layer is exposed through the space between the photoresist patterns 160. Subsequently, an etching process is performed on the protective insulating layer 145 exposed through the space between the photoresist patterns 160.

[0115] Although the etching process may be performed using a wet process or a dry process, the etching process is preferably performed using a wet etching process. Also, due to the etching process, a large portion of the protective insulating layer 145 formed on or over the surface of the second semiconductor layer 130 may be removed, and a portion of the surface of the second semiconductor layer 130 is exposed. However, the protective insulating layer 145 formed at corners disposed under the photoresist pattern 160 remains.

Accordingly, a space is formed between a lower portion of the photoresist pattern 160 and the second semiconductor layer 130 due to the etching process, and the protective insulating layer 145 remains at an end of the space. Since the wet etching process has isotropic etching characteristics, it may take a considerable amount of time or be troublesome to etch the protective insulating layer 145 formed on the corners disposed under the photoresist pattern 160. Accordingly, the protective insulating layer 145 exposed by the photoresist pattern 160 due to the anisotropic etching process is mostly removed, while only the protective insulating layer 145 recessed under the photoresist pattern 160 remains.

[0116] Referring to FIG. 15, a reflective metal layer 142, a stress relaxation layer 143, and a conductive barrier layer 144 are sequentially stacked on the second semiconductor layer 130 exposed by etching.

[0117] The reflective metal layer 142 includes Al, an Al alloy, Ag, or an Ag alloy. The reflective metal layer 142 may be formed using an ordinary metal deposition process. However, the reflective metal layer 142 is preferably formed using an electronic beam (e-beam) evaporation process capable of moving most metal atoms or ions onto the surface of the second semiconductor layer 130 in a vertical direction. Thus, the metal atoms or ions may have anisotropic etching characteristics and enter a space between the photoresist patterns 160 to form the reflective metal layer 142.

[0118] The reflective metal layer 142 preferably has a thickness of about 100 nm to about 1 um. When the reflective metal layer 142 has a thickness of less than about 100 nm, light generated by the active layer 120 is not smoothly reflected. Also, when the reflective metal layer 142 has a thickness of more than about 1 um, process loss may occur due to an excessive process time.

[0119] The ohmic contact layer 141 may be formed before forming the reflective metal layer 142, as needed. The ohmic contact layer 141 may include Ni, Pt, ITO, or ZnO. Also, the ohmic contact layer 141 is preferably formed to a thickness of about 0.1 nm to about 20 nm. When the ohmic contact layer 141 has a thickness of less than about 0.1 nm, sufficient ohmic characteristics cannot be ensured due to a very small layer thickness. Also, when the ohmic contact layer 141 has a thickness of more than about 20 nm, the transmitted amount of light is reduced to reduce the quantity of light reflected by the reflective metal layer 142 disposed on the ohmic contact layer 141.

[0120] The stress relaxation layer 143 is formed on the reflective metal layer 142.

[0121] The stress relaxation layer 143 may be formed using an ordinary metal deposition process, but is preferably formed using an e-beam evaporation method having a high directionality during a deposition process. That is, metal atoms or ions evaporated due to e-beams may have directionality and have anisotropy in a space between the photoresist patterns 160, and the stress relaxation layer 143 may be formed of a metal layer. Also, the stress relaxation layer 143 may have a lower coefficient of thermal expansion than the reflective metal layer 142 and a higher coefficient of thermal expansion than the conductive barrier layer 144 of FIG. 3. Accordingly, a material forming the stress relaxation layer 143 may be differently selected according to selected materials forming the reflective metal layer 142 and the conductive barrier layer 144. The material forming the stress relaxation layer 143 will be described later.

[0122] When the reflective metal layer 142 and the stress relaxation layer 143 are formed using an e-beam evaporation method, a side surface of the reflective metal layer 142 and a side surface of the stress relaxation layer 143 are exposed. Also, the reflective metal layer 142 and the stress relaxation layer 143 corresponding to an open upper region of the photoresist pattern 160 are formed using an anisotropic deposition process.

[0123] Subsequently, a conductive barrier layer 144 is formed through the opened region of the photoresist pattern 160.

[0124] The conductive barrier layer 144 includes W, TiW, Mo, Cr, Ni, Pt, Rh, Pd, or Ti. In particular, a material forming the conductive barrier layer 144 may be differently selected according to selected materials forming the reflective metal layer 142 and the stress relaxation layer 143.

[0125] The conductive barrier layer 144 is formed on or over the stress relaxation layer 143 and shields at least side surfaces of the reflective metal layer 142 and the stress relaxation layer 143. Accordingly, a metal forming the reflective metal layer 142 is prevented from diffusing into the second semiconductor layer 130 due to lateral diffusion. The formation of the conductive barrier layer 144 is performed using an ordinary metal de-position process. However, the conductive barrier layer 144 is preferably formed using an isotropic etching process. This is at least because the conductive barrier layer 144 is configured to surround at least the side surfaces of the stress relaxation layer 143 and the reflective metal layer 142. For example, the conductive barrier layer 144 may be formed using a sputtering process.

[0126] In addition, the conductive barrier layer 144 may be a single layer formed to a thickness of about 100 nm or more by selecting a specific metal. Also, the conductive barrier layer 144 may be formed by alternately selecting at least two metal materials, and each of layers forming the conductive barrier layer 144 may be formed to a thickness of about 20 nm or more. For example, the conductive barrier layer 144 may be formed by alternately depositing a TiW layer having a thickness of about 50 nm and a Ni layer or Ti layer having a thickness of about 50 nm.

[0127] Furthermore, a Ni/Au/Ti layer may be additionally formed on the conductive barrier layer 144 to enable a stable contact of the conductive barrier layer 144 with a subsequent material.

[0128] As described above, a material forming the stress relaxation layer 143 may be selected based on materials forming the reflective metal layer 142 and the conductive barrier layer 144. This is at least because a coefficient of thermal expansion of the stress relaxation layer 143 is higher than that of the conductive barrier layer **144** and lower than that of the reflective metal layer 142. Accordingly, when the reflective metal layer 142 includes Al or an Al alloy, and the conductive barrier layer 144 includes W, TiW, or Mo, the stress relaxation layer 143 may be a single layer formed of Ag, Cu, Ni, Pt, Ti, Rh, Pd, or Cr, or a combination formed of Cu, Ni, Pt, Ti, Rh, Pd or Au. Also, when the reflective metal layer 142 includes Al or an Al alloy, and the conductive barrier layer 144 includes Ti, Cr, Pt, Rh, Pd, or Ni, the stress relaxation layer 143 may be a single layer formed of Ag or Cu, or a combination formed of Ni, Au, Cu, or Ag. Furthermore, when the reflective metal layer 142 includes Ag or an Ag alloy, and the conductive barrier layer 144 includes W, TiW, or Mo, the stress relaxation layer 143 may be a single layer formed of Cu, Ni, Pt, Ti, Rh, Pd, or Cr, or a combination formed of Cu, Ni,

Pt, Ti, Rh, Pd, Cr, or Au. Also, when the reflective metal layer 142 includes Ag or an Ag alloy, and the conductive barrier layer 144 includes Pt or Ni, the stress relaxation layer 143 may be a single layer formed of Cu, Cr, Rh, Pd, TiW, or Ti, or a combination formed of Ni, Au, or Cu.

[0129] In addition, since the conductive barrier layer 144 is formed using a deposition process, such as a sputtering process, the conductive barrier layer 144 is formed to fill an edge region of the photoresist pattern 160. That is, the conductive barrier layer 144 is formed to fill a space between the photoresist pattern 160 and the second semi-conductor layer 130. By filling the space, the protective insulating layer 145 and the conductive barrier layer 144 are physically in contact with each other. Also, due to the deposition process, the conductive barrier layer 144 may be formed along shapes of surfaces of the second semiconductor layer 130, the reflective metal layer 142, and the stress relaxation layer 143.

[0130] The ohmic contact layer 141, the reflective metal layer 142, the stress relaxation layer 143, and the conductive barrier layer 144 may be formed also on the photoresist pattern 160.

[0131] Referring to FIG. 16, a lift-off process is performed on the photoresist pattern 160 to remove the photoresist pattern and the layers disposed thereon. Accordingly, the protective insulating layer 145 coated on the mesa region(s) and the reflection pattern 140 disposed thereon are exposed. As described above, the mesa region(s) 150 may be a stripe type or a hole type. Also, a protective insulating layer 145 is provided on side surfaces of the reflection pattern 140 and the mesa region(s) 150. The conductive barrier layer 144 of the reflection pattern 140 may be defined by the protective insulating layer 145.

[0132] Due to the above-described processes, the reflection pattern 140 is formed on or over the second semiconductor layer 130. The reflection pattern 140 includes a reflective metal layer 142, a stress relaxation layer 143, and a conductive barrier layer 144. The stress relaxation layer 143 has a lower coefficient of thermal expansion than the reflective metal layer 142 and a higher coefficient of thermal expansion than the conductive barrier layer 144. Accordingly, stress caused due to a difference in coefficient of thermal expansion between the reflective metal layer 142 and the conductive barrier layer 144 is absorbed in the stress relaxation layer 143.

[0133] In addition, formation of protruding points shown in FIGS. 1 and 2 is excluded from the conductive barrier layer 144 formed on the reflective metal layer 142 or the stress relaxation layer 143. Accordingly, generation of metal particles is inhibited in subsequent processes to maintain a high yield.

#### Embodiment 3

[0134] FIG. 17 is a cross-sectional view of an LED according to a third exemplary embodiment of the disclosed technology.

[0135] Referring to FIG. 17, a first semiconductor layer 110, an active layer 120, a second semiconductor layer 130, and a reflection pattern 140 are formed on or over a substrate 100.

[0136] The substrate 100 may be formed of any material capable of inducing the first semiconductor layer 110 to be grown. Accordingly, the substrate 100 may include sapphire (Al2O3), silicon carbide (SiC), gallium nitride (GaN), indium gallium nitride (InGaN), aluminum gallium nitride

(AlGaN), aluminum nitride (AlN), gallium oxide (Ga2O3), or silicon. Specifically, the substrate 100 may be a sapphire substrate.

[0137] Also, the substrate 100 may be a substrate on which surface treatment is not performed. The substrate 100 may be a patterned substrate. Also, the substrate 100 may have a surface having a moth-eye structure. For example, the substrate may have a protrusion protruding in a roughly hemispherical shape, and pointed structures may be densely disposed on the protrusion.

[0138] In addition, the first semiconductor layer 110 is provided on the substrate 100. The first semiconductor layer 110 preferably includes an n conductivity type but can include any conductivity type layer.

[0139] Furthermore, the active layer 120 formed on the first semiconductor layer 110 may have an SQW structure in which a well layer and a barrier layer are stacked, or an MQW structure in which well layers and barrier layers are alternately stacked.

[0140] The second semiconductor layer 130 is provided on the active layer 120. The second semiconductor layer 130 preferably includes a p conductivity type but can include any conductivity type layer.

[0141] Furthermore, the first semiconductor layer 110, the active layer 120, and the second semiconductor layer 130 may include Si, GaN, AlN, InGaN, or AlInGaN. When the first semiconductor layer 110 includes GaN, the active layer 120 and the second semi-conductor layer 130 preferably include GaN. However, since the second semi-conductor layer 130 has a complementary or different conductivity type to the first semiconductor layer 110, a different dopant from that of the first semiconductor layer 110 is introduced into the second semiconductor layer 130. That is, when a dopant serving as a donor is introduced into the first semiconductor layer 110, a dopant serving as an acceptor is introduced into the second semiconductor layer 130. Also, the active layer 120 preferably includes a material on which bandgap engineering is performed to form barrier layers and well layers.

[0142] The reflection pattern 140 is formed on the second semiconductor layer 130.

[0143] The reflection pattern 140 includes a reflective metal layer 142 and a conductive barrier layer 144. Also, in some embodiments, an ohmic contact layer (not shown) may be formed under the reflective metal layer 142, and a stress relaxation layer (not shown) may be additionally formed between the reflective metal layer 142 and the conductive barrier layer 144.

[0144] An ohmic contact layer may be formed of any material capable of enabling an ohmic contact between the reflective metal layer 142 and the second semiconductor layer 130. Accordingly, the ohmic contact layer may include a metal including Ni or Pt or include a conductive oxide, such as ITO or ZnO. However, the ohmic contact layer may be omitted in some embodiments.

[0145] The reflective metal layer 142 is formed on or over the ohmic contact layer. The reflective metal layer 142 reflects light generated by the active layer 120. Accordingly, the reflective metal layer 142 is formed by selecting a material having conductivity and a high optical reflectance. The reflective metal layer 142 includes Ag, an Ag alloy, Al, or an Al alloy.

[0146] In addition, a stress relaxation layer may be formed on or over the reflective metal layer 142. The stress relaxation layer preferably has a coefficient of thermal expansion equal

to or higher than that of the conductive barrier layer 144, and equal to or lower than that of the reflective metal layer 142. Thus, stress caused due to a difference in coefficient of thermal expansion between the reflective metal layer 142 and the conductive barrier layer 144 may be reduced. Accordingly, a material forming the stress relaxation layer may be differently selected according to selected materials forming the reflective metal layer 142 and the conductive barrier layer 144.

[0147] However, the ohmic contact layer or the stress relaxation layer may be omitted in some embodiments.

[0148] In addition, an angle 'a' formed by the reflective metal layer 142 with a plane surface of the underlying second semiconductor layer 130 preferably ranges from about  $5^{\circ}$  to about  $45^{\circ}$ . When an angle 'a' formed by a side surface of the reflective metal layer 142 is less than about  $5^{\circ}$ , it is difficult to ensure a sufficient thickness of the reflective metal layer 142. When an angle  $\alpha$  formed by the side surface of the reflective metal layer 142 is more than about  $45^{\circ}$ , cracks occur in a side profile of the conductive barrier layer 144 formed on the reflective metal layer 142. When an ohmic contact layer is introduced, an inclination angle formed by the ohmic contact layer with the side surface of the reflective metal layer 142 should be within the above-described angle range.

[0149] The conductive barrier layer 144 is formed on or over the reflective metal layer 142 or the stress relaxation layer 143. For example, when a stress relaxation layer is omitted, the conductive barrier layer 144 is formed on or over the reflective metal layer 142, and when the stress relaxation layer is formed, the conductive barrier layer **144** is formed on or over the stress relaxation layer. The conductive barrier layer 144 is formed to surround at least the side surface of the reflective metal layer 142 and surround top and side surfaces of the stress relaxation layer. Accordingly, diffusion of metal atoms or ions constituting the reflective metal layer 142 is prevented. Also, stress caused due to a difference in coefficient of thermal expansion between the conductive barrier layer 144 and the reflective metal layer 142 may be absorbed in the stress relaxation layer. In particular, the conductive barrier layer 144 may be formed to a different thickness according to a surface state of the underlying reflective metal layer or stress relaxation layer. For example, assuming that the thickness of the conductive barrier layer 144 formed on a top surface of the reflective metal layer 142 is t1, the thickness of the conductive barrier layer 144 formed on the side surface of the reflective metal layer **142** is t2, and the thickness of the conductive barrier layer 144 formed on the surface of the second semiconductor layer 130 is t3, a relationship of t1>t3>t2 is preferably set.

[0150] In addition, the conductive barrier layer 144 is formed to completely shield the reflective metal layer 142 or the stress relaxation layer and extend to the surface of the second semiconductor layer 130.

[0151] In addition, when the reflective metal layer 142 includes Al or an Al alloy, and the conductive barrier layer 144 includes W, TiW, or Mo, the stress relaxation layer may be a single layer formed of Ag, Cu, Ni, Pt, Ti, Rh, Pd, or Cr, or a combination formed of Cu, Ni, Pt, Ti, Rh, Pd or An. Also, when the reflective metal layer 142 includes Al or an Al alloy, and the conductive barrier layer 144 includes Ti, Cr, Pt, Rh, Pd, or Ni, the stress relaxation layer may be a single layer formed of Ag or Cu, or a combination formed of Ni, An, Cu, or Ag.

[0152] Furthermore, when the reflective metal layer 142 includes Ag or an Ag alloy, and the conductive barrier layer

144 includes W, TiW, or Mo, the stress relaxation layer may be a single layer formed of Cu, Ni, Pt, Ti, Rh, Pd, or Cr, or a combination formed of Cu, Ni, Pt, Ti, Rh, Pd, Cr, or Au. Also, when the reflective metal layer 142 includes Ag or an Ag alloy, and the conductive barrier layer 144 includes Cr or Ni, the stress re-laxation layer may be a single layer formed of Cu, Cr, Rh, Pd, TiW, or Ti, or a combination formed of Ni, An, or Cu.

[0153] In addition, the conductive barrier layer 144 coats at least a portion of a surface of the second semi-conductor layer 130.

[0154] FIGS. 18 through 22 are cross-sectional views illustrating a method of manufacturing the LED of FIG. 17, according to a third exemplary embodiment of the disclosed technology.

[0155] Referring to FIG. 18, a first semiconductor layer 110, an active layer 120, and a second semiconductor layer 130 are sequentially formed or stacked on or over a substrate 100.

[0156] The substrate 100 may include sapphire (Al2O3), silicon carbide (SiC), gallium nitride (GaN), indium gallium nitride (InGaN), aluminum gallium nitride (AlGaN), aluminum nitride (AlN), gallium oxide (Ga2O3), or silicon. Specifically, the substrate 100 may be a sapphire substrate. Also, the substrate 100 may be a patterned substrate or a substrate having a surface with a moth-eye structure.

[0157] Also, the first semiconductor layer 110 is provided on the substrate 100. The first semiconductor layer 110 preferably includes an n conductivity type but can include any conductivity type layer.

[0158] In addition, the active layer 120 formed on or over the first semiconductor layer 110 may have an SQW structure in which a well layer and a barrier layer are stacked, or an MQW structure in which well layers and barrier layers are alternately stacked.

[0159] The second semiconductor layer 130 is provided on or over the active layer 120. The second semiconductor layer 130 preferably includes a p conductivity type but can include any conductivity type layer.

[0160] Furthermore, materials and constructions of the first semiconductor layer 110, the active layer 120, and the second semiconductor layer 130 are substantially the same as described with reference to FIG. 3, and thus a description thereof is omitted.

[0161] In addition, the first semiconductor layer 110, the active layer 120, and the second semiconductor layer 130 are formed using an epitaxial growth process. Accordingly, the first semiconductor layer 110, the active layer 120, and the second semiconductor layer 130 are preferably formed using an MOCVD process.

[0162] Referring to FIG. 19, portions of the active layer 120 and the second semiconductor layer 130 are removed using an ordinary etching process. Thus, a portion of the first semiconductor layer 110 is exposed. Due to the etching process, a top surface of the first semiconductor layer 110 is exposed, and side surfaces of the active layer 120 and the second semiconductor layer 130 are exposed. Accordingly, a trench or a hole may be formed by removing the portions of the active layer 120 and the second semi-conductor layer 130 using the etching process. That is, a mesa region(s) 150 etched from the surface of the second semiconductor layer 130 of FIG. 5 to the surface of the first semiconductor layer 110 may be a stripe type having a trench shape or a hole type.

[0163] In addition, when the mesa region(s) is the stripe type, the mesa region(s) may have a vertical profile or inclined profile with respect to the surface of the first semiconductor layer 110. Preferably, the mesa region(s) has a profile inclined at an angle of about 20° to about 70° with respect to the surface of the first semiconductor layer 110. Also, when the mesa region(s) 150 is or can include a hole type having a roughly circular shape, the mesa region(s) 150 may have a vertical profile or inclined profile with respect to the surface of the first semiconductor layer 110. Preferably, the mesa region(s) 150 has a profile inclined at an angle of about 20° to about 70° with respect to the surface of the first semi-conductor layer 110. When the profile is inclined at an angle of less than 20°, a width of the mesa region 150 greatly increases upward. Accordingly, convergence of light generated is degraded due to an emission structure. Also, when the profile is inclined at an angle of more than 70°, the mesa region 150 has an approximately vertical profile. Accordingly, the effect of reflection of generated light by sidewalls of layers become immaterial.

[0164] Referring to FIG. 20, a photoresist pattern 160 is formed on or over the first semiconductor layer 110 exposed by forming a bottom surface of the mesa region. The photoresist pattern 160 may have a vertical profile with respect to the surface of the first semi-conductor layer 110. In some embodiments, the photoresist pattern 160 may be formed to have an overhang structure having a bottom surface with a smaller width than a top surface thereof. The photoresist pattern 160 is preferably a negative type. Accordingly, exposed portions are cross-linked. To form the overhang structure, the photoresist pattern 160 is preferably exposed at a predetermined angle. In the case of the overhang structure, a distance between bottom surfaces of the photoresist patterns 160 is preferably set to be at least about 1 m greater than a distance between top surfaces thereof.

[0165] Furthermore, the photoresist pattern 160 is preferably provided to cover a portion of the surface of the second semiconductor layer 130. Accordingly, the portion of the top surface of the second semiconductor layer 130 may remain shielded by the photoresist pattern 160.

[0166] Referring to FIG. 21, a reflective metal layer 142 and a conductive barrier layer 144 are sequentially stacked on or over the second semiconductor layer 130 to form a reflection pattern 140. Also, in some embodiments, an ohmic contact layer 141 may be formed under the reflective metal layer 142, and a stress relaxation layer 143 may be additionally formed between the reflective metal layer 142 and the conductive barrier layer 144.

[0167] The reflective metal layer 142 includes Al, an Al alloy, Ag, or an Ag alloy. The reflective metal layer 142 may be formed using an ordinary metal deposition process. However, the reflective metal layer 142 is preferably formed using an electronic beam (e-beam) evaporation process capable of moving most metal atoms or ions onto the surface of the second semiconductor layer 130 in a vertical direction. Thus, the metal atoms or ions may have anisotropic etching characteristics and enter a space between the photoresist patterns 160 to form the reflective metal layer 142.

[0168] The reflective metal layer 142 preferably has a thickness of about 100 nm to about 1 um. When the reflective metal layer 142 has a thickness of less than about 100 nm, light generated by the active layer 120 is not smoothly reflected. Also, when the reflective metal layer 142 has a

thickness of more than about 1 um, process loss may occur due to an excessive process time.

[0169] The ohmic contact layer 141 may be formed before forming the reflective metal layer 142, as needed. The ohmic contact layer 141 may include Ni, Pt, ITO, or ZnO. Also, the ohmic contact layer 141 is preferably formed to a thickness of about 0.1 nm to about 20 nm. When the ohmic contact layer 141 has a thickness of less than about 0.1 nm, sufficient ohmic characteristics cannot be ensured due to a very small layer thickness. Also, when the ohmic contact layer 141 has a thickness of more than about 20 nm, the transmitted amount of light is reduced to reduce the quantity of light reflected by the reflective metal layer 142 disposed on the ohmic contact layer 141.

[0170] The stress relaxation layer 143 is formed on the reflective metal layer 142.

[0171] The stress relaxation layer 143 may be formed using an ordinary metal deposition process, but is preferably formed using an e-beam evaporation method having a high directionality during a deposition process. That is, metal atoms or ions evaporated due to e-beams may have directionality and have anisotropy in a space between the photoresist patterns 160, and the stress relaxation layer 143 may be formed of a metal layer. Also, the stress relaxation layer 143 may have a lower coefficient of thermal expansion than the reflective metal layer 142 and a higher coefficient of thermal expansion than the conductive barrier layer 144 of FIG. 3. Accordingly, a material forming the stress relaxation layer 143 may be differently selected according to selected materials forming the reflective metal layer 142 and the conductive barrier layer 144.

[0172] When the reflective metal layer 142 and the stress relaxation layer 143 are formed using an e-beam evaporation method, a side surface of the reflective metal layer 142 and a side surface of the stress relaxation layer 143 are exposed. Also, the reflective metal layer 142 and the stress relaxation layer 143 corresponding to an open upper region of the photoresist pattern 160 are formed using an anisotropic deposition process.