## US005537156A

# United States Patent [19]

# Katayama

[11] Patent Number:

5,537,156

[45] Date of Patent:

Jul. 16, 1996

| [54] | FRAME BUFFER ADDRESS GENERATOR     |

|------|------------------------------------|

|      | FOR THE MULITPLE FORMAT DISPLAY OF |

|      | MULTIPLE FORMAT SOURCE VIDEO       |

[75] Inventor: Andrew S. Katayama,

Cardiff-by-the-Sea, Calif.

[73] Assignee: Eastman Kodak Company, Rochester,

N.Y.

[21] Appl. No.: 217,408

[22] Filed: Mar. 24, 1994

[52] **U.S. Cl.** ...... **348/716**; 348/714; 395/166; 395/412; 364/245

245.5; 395/164, 165, 166, 400, 425, 139; H04N 5/76, 9/64

## [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,675,842 | 6/1987  | Normann, III | 364/900 |

|-----------|---------|--------------|---------|

| 4,755,810 | 7/1988  |              | 340/726 |

| 4,790,025 | 12/1988 |              | 382/41  |

| 4,872,001 | 10/1989 | Netter         | 340/721 |

|-----------|---------|----------------|---------|

| 4,928,253 | 5/1990  | Yamauchi et al | 364/521 |

| 4,951,229 | 8/1990  | DiNicola et al | 364/521 |

| 4,967,274 | 10/1990 | Somoda         | 358/160 |

| 5,134,695 | 7/1992  | Ikeda          | 395/425 |

| 5,140,436 | 8/1992  | Blessinger     | 358/335 |

Primary Examiner—James J. Groody

Assistant Examiner—Cheryl Cohen

Attorney, Agent, or Firm—William F. Noval

## [57] ABSTRACT

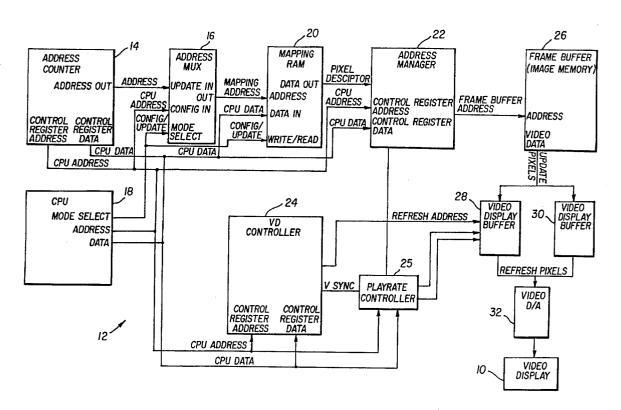

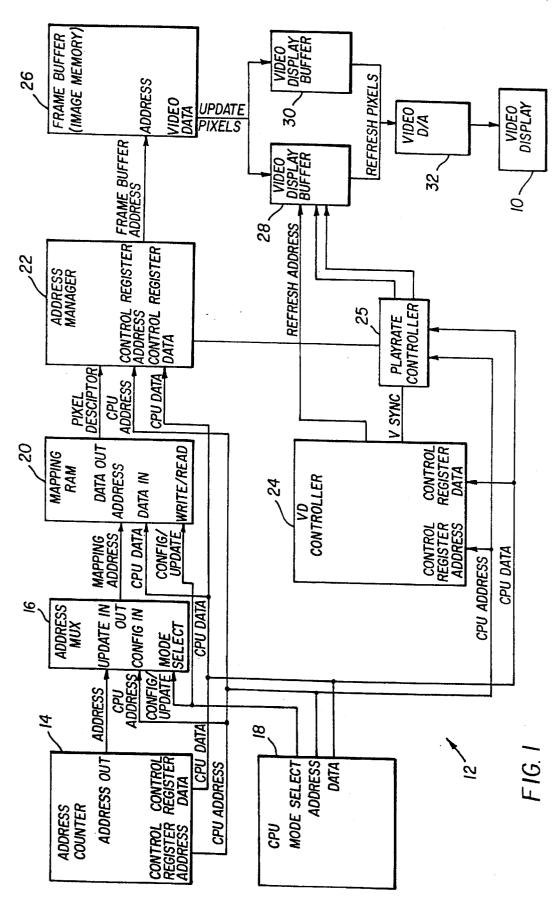

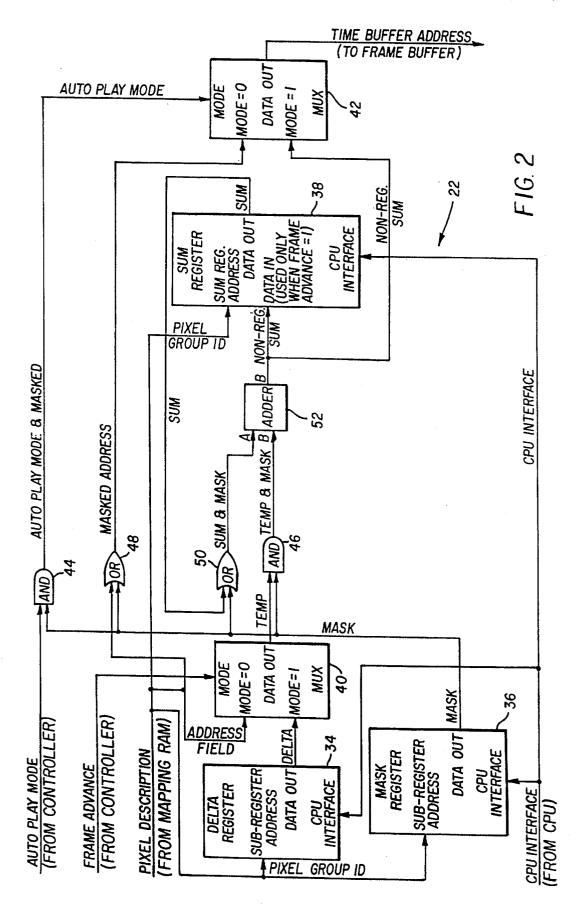

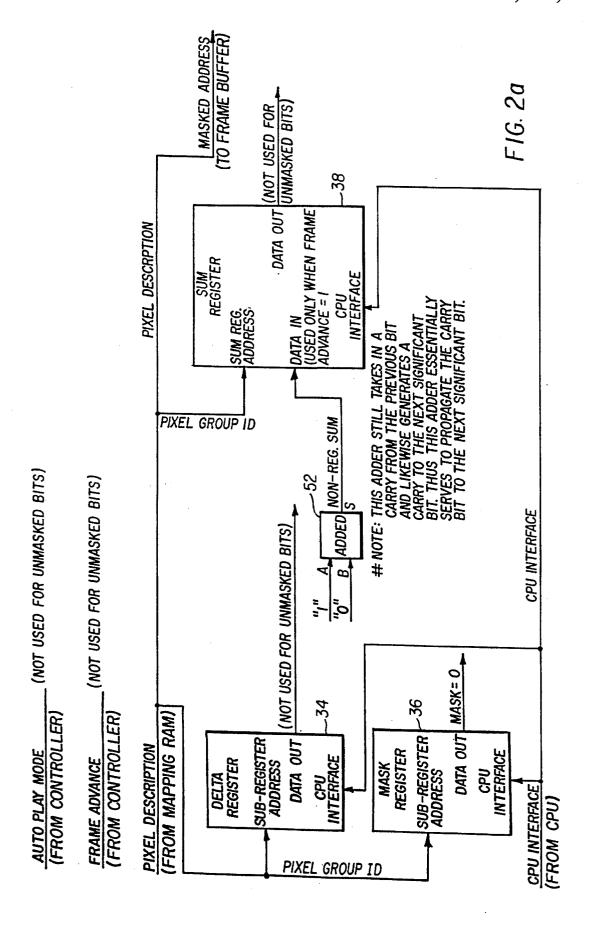

A video imaging system having an image memory for storing a plurality of image frames and a video display having a matrix of pixels. Apparatus generates addresses for accessing pixels stored in the image memory to be displayed on the video display. The address generating apparatus includes a programmable mapping memory for storing a pixel descriptor of each pixel to be displayed on the video display, each pixel descriptor including a pixel group identification field which identifies a group of pixels on the video display, and an address field which includes address information of the image memory of pixels to be displayed. An address manager and a control causes each pixel descriptor read out of the mapping memory to be processed according to its pixel group to effect multiple format display of multiple format source video.

# 4 Claims, 17 Drawing Sheets

|        | ADDR:P   | XEL:fr,x,y |          | ADDR:PIXEL:fr,x,y            |

|--------|----------|------------|----------|------------------------------|

|        | 000000   | 0,0,0      |          | 100000 2,0,0                 |

|        | 000001   | 0,1,0      |          | 100001 2,1,0                 |

|        | 000010   | 0,2,0      |          |                              |

|        | 000011   | 0,3,0      |          | -,-,-                        |

|        | 000100   | 0,0,1      |          |                              |

|        | 000101   | 0,1,1      |          |                              |

|        | 000110   | 0,2,1      |          |                              |

|        | 000111   | 0,3,1      |          | -',-',·                      |

|        | 001000   | 0,0,2      |          | 100111 2,3,1<br>101000 2,0,2 |

|        | 001001   | 0,1,2      | ÷        | 101001 2,1,2                 |

|        | 001010   | 0,2,2      |          | 101010 2,2,2                 |

|        | 001011   | 0,3,2      |          | 101011 2,3,2                 |

| ·      | 001100   | 0,0,3      |          | 101100 2,0,3                 |

|        | 001101   | 0,1,3      | FRAME    | 101101 2,1,3                 |

| FIG.74 | 001110   | 0,2,3      | BUFFER   | 101110 2,2,3                 |

|        | 001111   | 0,3,3      | CONTENTS | 101111 2,3,3                 |

|        | 010000   | 1,0,0      | (LINEAR) | 110000 3,0,0                 |

|        | 010001   | 1,1,0      |          | 110001 3,1,0                 |

|        | 010010   | 1,2,0      |          | 110010 3,2,0                 |

|        | 010011   | 1,3,0      |          | 110011 3,3,0                 |

|        | 010100   | 1,0,1      | •        | 110100 3,0,1                 |

|        | 010101   | 1,1,1      |          | 110101 3,1,1                 |

|        | 010110   | 1,2,1      |          | 110110 3,2,1                 |

|        | 010111   | 1,3,1      |          | 110111 3,3,1                 |

|        | 011000   | 1,0,2      |          | 111000 3,0,2                 |

|        | 011001   | 1,1,2      |          | 111001 3,1,2                 |

|        | 011010   | 1,2,2      |          | 111010 3,2,2                 |

|        | 011011   | 1,3,2      |          | 111011 3,3,2                 |

|        | 011100   | 1,0,3      |          | 111100 3,0,3                 |

|        | 011101   | 1,1,3      |          | 111101 3,1,3                 |

|        | 011110   | 1,2,3      |          | 111110 3,1,3                 |

| (      | 011111 [ | 1,3,3      |          |                              |

| `      |          | · /-       |          | 111111 [ 3,3,3               |

```

ADDR:PIXEL

ADDR:PIXEL

DESCRIPTOR:x,y

DESCRIPTOR:x,y

ID:ADDR FIELD

ID:ADDR FIELD

:0:000000

32

0,0

:3:000000 0.4

1

:0:000010

1,0

33

:3:010000

1.4

2

:1:000010

2,0

34

:3:100000

2.4

3

:1:000011

3,0

35

:3:110000

3,4

4

:2:000000

4,0

36

:4:000101

5

:2:000001

5,0

37

:4:000101

5,4

6

:2:000010

6,0

38

:4:000110

6,4

7

:2:000011

7,0

39

:4:000110

7,4

8

:0:001000

40

0,1

:3:000100

0,5

9

:0:001010

1,1

41

:3:010100

1,5

10

:1:000110

2,1

42

:3:100100

2,5

11

:1:000111

3,1

43

:3:110100

FIG. 9

3.5

12

:2:000100

4,1

44

:4:000101

4,5

13

:2:000101

5,1

45

:4:000101

5,5

14

:2:000110

6,1

46

:4:000110

6,5

15

:2:000111

7,1

47

:4:000110

7,5

16

:1:001000

0,2

48

:3:001000

0.6

17

:1:001001

1,2

49

:3:011000

1,6

18

:1:001010

2,2

50

:3:101000

2.6

19

:1:001011

3,2

51

:3:111000

3,6

20

:2:001000

4,2

52

:4:001001

4,6

21

:2:001001

5,2

53

:4:001001

5,6

22

:2:001010

6,2

54

:4:001010

6,6

23

:2:001011

7,2

55

:4:001010

7,6

24

:1:001100

0,3

56

:3:001100

0,7

25

:1:001101

1.3

57

:3:011100

1.7

26

:1:001110

2,3

58

:3:101100

2,7

27

:1:001111

3,3

59

:3:111100

3.7

28

:2:001100

4,3

60

:4:001001

4,7

29

:2:001101

5,3

61

:4:001001

5.7

30

:2:001110

6,3

62

:4:001010

6.7

31

:2:001111

7,3

63

:4:001010

```

|                | PIX<br>GRP 0 | PIX<br>GRP 1 | PIX<br>GRP 2 | PIX<br>GRP 3 | PIX<br>GRP 4 |

|----------------|--------------|--------------|--------------|--------------|--------------|

| MASK REGISTER  | 110000       | 110000       | 110000       | 000011       | 110000       |

| DELTA REGISTER | 010000       | 010000       | 000000       | 000001       | 110000       |

| SUM REGISTER   | 000000       | 000000       | 100000       | 000011       | 010000       |

F1G. 10

FIĞ. II

| DELTA REGISTER 010000 010000 000000 000001 110000 SUM REGISTER 000000 000000 100000 000011 010000 OOOOOO 000001 010000 OOOOOO 000001 010000 OOOOOO 000001 010000 OOOOOO 000001 110000 OOOOOO 000001 110000 OOOOOO 000001 110000 OOOOOO 000001 110000 OOOOOO 000000 OOOOOO 000000 OOOOOO OOOOOO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |        |          |              |        |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------|----------|--------------|--------|--------|

| GRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ORI                                   |        | REGISTER | VALUES       | 3      |        |

| MASK REGISTER 110000 110000 110000 000011 110000 000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |        |          |              |        |        |

| MASK REGISTER 110000 110000 110000 000001 110000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 010000 00000 010000 00000 010000 00000 010000 00000 010000 00000 00000 00000 00000 00000 00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |        |          |              |        | GRP    |

| DELTA REGISTER 010000 010000 000000 000001 110000 010000 000001 110000 010000 000001 0100000 000001 110000 010000 000001 1100000 010000 000001 110000 010000 010000 010000 010000 000001 110000 010000 010000 000001 110000 000001 110000 010000 000001 1100000 000001 000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       | 0      | 1        | 2            | 3      | 4      |

| DELTA REGISTER 010000 010000 000000 000001 110000 SUM REGISTER 000000 000000 100000 000011 110000 110000 110000 110000 110000 110000 000011 110000 110000 110000 000011 110000 010000 000001 110000 000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MASK REGISTER                         | 110000 | 110000   | 110000       | 000011 | 110000 |

| AFTER FRAME   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e e e e e e e e e e e e e e e e e e e | 010000 | 010000   |              |        | · · ·  |

| PIX   PIX   PIX   PIX   PIX   PIX   PIX   PIX   GRP    | SUM REGISTER                          | 000000 | 000000   | 100000       | 000011 | ·      |

| GRP GRP GRP GRP GRP GRP GRP O 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000 000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       | AFT    | ER FRAME | 1            | •      |        |

| GRP    |                                       | PIX    | PIX      | PIX          | PIX    | PIX    |

| MASK REGISTER 110000 110000 110000 000011 110000 110000 010000 010000 010000 000001 110000 000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       | GRP    | GRP      |              |        |        |

| DELTA REGISTER 010000 010000 000000 000001 110000 SUM REGISTER 010000 010000 100000 000011 0000000 O00000 O0000 O0000 O0000 O00000 O000 |                                       | 0      | 1        | 2            | 3      | 4      |

| DELTA REGISTER 010000 010000 000000 000001 110000 SUM REGISTER 010000 010000 100000 000011 0000000 O00000 O0000 O0000 O0000 O00000 O000 | MASK REGISTER                         | 110000 | 110000   | 110000       | 000011 | 110000 |

| AFTER FRAME 3 PIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DELTA REGISTER                        |        |          |              |        |        |

| AFTER FRAME 2  PIX PIX PIX PIX PIX PIX GRP GRP 0 1 2 3 4  MASK REGISTER 110000 110000 110000 0000011 110000 000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SUM REGISTER                          |        |          |              |        |        |

| PIX PIX PIX PIX PIX PIX PIX GRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       |        |          |              |        | 000000 |

| GRP GRP GRP GRP GRP GRP O 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000 000001 110000 000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       |        | _        | _            |        |        |

| MASK REGISTER 110000 110000 110000 000011 110000 110000 SUM REGISTER 110000 100000 100000 000000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 000011 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110000 110 |                                       |        |          |              |        |        |

| MASK REGISTER 110000 110000 110000 000011 110000 DELTA REGISTER 010000 010000 000000 000001 110000 SUM REGISTER 100000 100000 100000 000000 110000 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |        |          |              | •      |        |

| DELTA REGISTER 010000 010000 000000 000001 110000 SUM REGISTER 100000 100000 100000 000000 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |        | '        | 2            | 3      | 4      |

| AFTER FRAME 3 PIX PIX PIX PIX PIX PIX GRP GRP 0 1 2 3 4  MASK REGISTER 110000 110000 100000 000001 110000  SUM REGISTER 110000 110000 100000 000001 100000  AFTER FRAME 4 PIX PIX PIX PIX PIX PIX GRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |        | · ·      | 110000       | 000011 | 110000 |

| AFTER FRAME 3  PIX PIX PIX PIX PIX PIX  GRP GRP GRP GRP GRP  0 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000  DELTA REGISTER 010000 110000 100000 000001 100000  SUM REGISTER 110000 110000 100000 000001 100000  AFTER FRAME 4  PIX PIX PIX PIX PIX PIX  GRP GRP GRP GRP GRP  0 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000  DELTA REGISTER 110000 110000 110000 000001 110000  DELTA REGISTER 010000 010000 000000 000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |        |          | 000000       | 000001 | 110000 |

| PIX PIX PIX PIX PIX PIX GRP GRP GRP 0 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000 DELTA REGISTER 010000 110000 100000 000001 100000 SUM REGISTER 110000 110000 100000 000001 100000 AFTER FRAME 4  PIX PIX PIX PIX PIX PIX PIX GRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SUM REGISTER                          | 100000 | 100000   | 100000       | 000000 | 110000 |

| GRP GRP GRP GRP GRP GRP 0 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000  DELTA REGISTER 010000 010000 000000 000001 110000  SUM REGISTER 110000 110000 100000 000001 100000  AFTER FRAME 4  PIX PIX PIX PIX PIX PIX GRP GRP GRP 0 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000  DELTA REGISTER 010000 010000 000000 000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ·                                     | AFT    | ER FRAME | 3            |        |        |

| GRP GRP GRP GRP GRP GRP 0 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000  DELTA REGISTER 010000 010000 000000 000001 110000  SUM REGISTER 110000 110000 100000 000001 100000  AFTER FRAME 4  PIX PIX PIX PIX PIX PIX GRP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       | PIX    | PIX      | PIX          | PIX    | PIX    |

| MASK REGISTER 110000 110000 110000 000011 110000 DELTA REGISTER 010000 010000 000000 000001 110000 SUM REGISTER 110000 110000 100000 000001 100000  AFTER FRAME 4  PIX PIX PIX PIX PIX PIX GRP GRP GRP 0 1 2 3 4  MASK REGISTER 110000 110000 110000 000011 110000 DELTA REGISTER 010000 010000 000000 000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |        | GRP      | GRP          | GRP    |        |

| DELTA REGISTER 010000 010000 000000 000001 110000 SUM REGISTER 110000 110000 100000 000001 100000 AFTER FRAME 4  PIX PIX PIX PIX PIX PIX PIX GRP GRP GRP GRP GRP GRP 3 4  MASK REGISTER 110000 110000 110000 000001 110000 DELTA REGISTER 010000 010000 000000 0000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       | 0      | 1 .      | 2            | 3      | 4      |

| DELTA REGISTER 010000 010000 000000 000001 110000 SUM REGISTER 110000 110000 100000 000001 100000 AFTER FRAME 4  PIX PIX PIX PIX PIX PIX PIX GRP GRP GRP GRP GRP GRP 3 4  MASK REGISTER 110000 110000 110000 000001 110000 DELTA REGISTER 010000 010000 000000 0000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MASK REGISTER                         | 110000 | 110000   | 110000       | 000011 | 110000 |

| SUM REGISTER 110000 110000 100000 000001 100000  AFTER FRAME 4  PIX PIX PIX PIX PIX PIX  GRP GRP GRP GRP GRP  0 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000  DELTA REGISTER 010000 010000 000000 000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |        |          | <del>-</del> |        |        |

| AFTER FRAME 4  PIX PIX PIX PIX PIX  GRP GRP GRP GRP GRP  0 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000  DELTA REGISTER 010000 010000 000000 000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SUM REGISTER                          | 110000 |          |              | · -    |        |

| PIX PIX PIX PIX PIX PIX GRP GRP GRP GRP GRP 0 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000 DELTA REGISTER 010000 010000 000000 000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       | AFT    |          |              |        |        |

| GRP GRP GRP GRP GRP 0 1 2 3 4  MASK REGISTER 110000 110000 110000 000001 110000  DELTA REGISTER 010000 010000 000000 000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       |        | _        | -            | אום    | DIV    |

| 0 1 2 3 4  MASK REGISTER 110000 110000 110000 000011 110000  DELTA REGISTER 010000 010000 000000 000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |        | · -      |              |        |        |

| MASK REGISTER 110000 110000 110000 000011 110000<br>DELTA REGISTER 010000 010000 000000 000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |        | - '      |              |        |        |

| DELTA REGISTER 010000 010000 000000 000001 110000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MASK DECICED                          |        | -        |              |        |        |

| SUM DECISTED COORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                       | 110000 |          | ·            |        |        |